带隙基准电路ppt

带隙基准电路设计.

帯隙基准电路设计(东南大学集成电路学院)一.基准电压源概述基准电压源(Reference V oltage)是指在模拟电路或混合信号电路中用作电压基准的具有相对较高精度和稳定度的参考电压源,它是模拟和数字电路中的核心模块之一,在DC/DC ,ADC ,DAC 以及DRAM 等集成电路设计中有广泛的应用。

它的温度稳定性以及抗噪性能影响着整个电路系统的精度和性能。

模拟电路使用基准源,是为了得到与电源无关的偏置,或是为了得到与温度无关的偏置,其性能好坏直接影响电路的性能稳定。

在CMOS 技术中基准产生的设计,着重于公认的“帯隙”技术,它可以实现高电源抑制比和低温度系数,因此成为目前各种基准电压源电路中性能最佳、应用最广泛的电路。

基于CMOS 的帯隙基准电路的设计可以有多种电路结构实现。

常用的包括Banba 和Leung 结构带薪基准电压源电路。

在综合考虑各方面性能需求后,本文采用的是Banba 结构进行设计,该结构具有功耗低、温度系数小、PSRR 高的特点,最后使用Candence 软件进行仿真调试。

二.帯隙基准电路原理与结构1.工作原理带隙基准电压源的设计原理是根据硅材料的带隙电压与电源电压和温度无关的特性,通过将两个具有相反温度系数的电压进行线性组合来得到零温度系数的电压。

用数学方法表示可以为:2211V V V REF αα+=,且02211=∂∂+∂∂T V T V αα。

1).负温度系数的实现根据双极性晶体管的器件特性可知,双极型晶体管的基极-发射极电压BE V 具有负温度系数。

推导如下:对于一个双极性器件,其集电极电流)/(exp T BE S C V V I I =,其中q kT V T /=,约为0.026V ,S I 为饱和电流。

根据集电极电流公式,得到:SC T BE I I V V ln = (2.1) 为了简化分析,假设C I 保持不变,这样:TI I V I I T V T V S S T S C T BE ∂∂-∂∂=∂∂ln (2.2) 根据半导体物理知识可知:kT E bT I gm S -=+exp 4 (2.3)其中b 为比例系数,m ≈−3/2,Eg 为硅的带隙能量,约为1.12eV 。

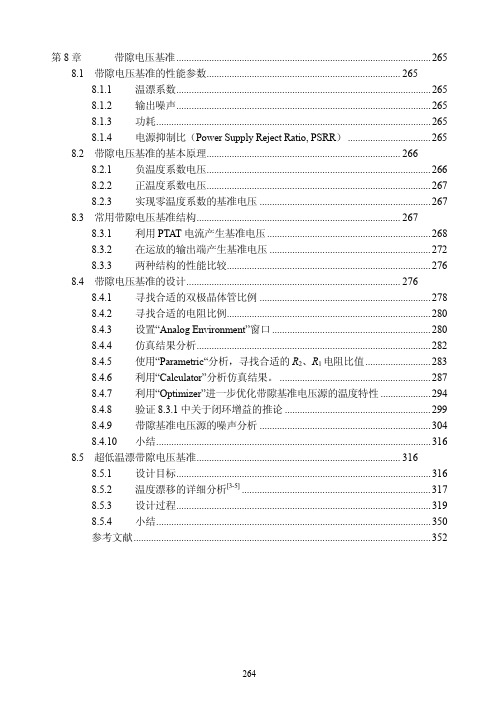

第8章 带隙基准

264

第8章 带隙电压基准

电压基准是模拟电路设计中不可或缺的一个单元模块。它为系统提供直流参考电压, 对电路性能,例如运算放大器的电压增益和噪声都有着显著的影响。在本章中,主要讨论 在 CMOS 技术中电压基准的产生,着重于通用的“带隙”技术。首先,将研究带隙电压基准 的基本原理,并介绍常用的带隙电压基准电路结构,以及衡量带隙电压基准性能的方法, 接着将针对其中的一种结构介绍带隙电压基准的设计流程,随后将分析带隙电压基准输出 噪声和仿真方法,最后将介绍一种低温漂带隙电压基准的结构和设计流程。

266

8.2.2

正温度系数电压

IS 为双极晶体管饱和电流)偏置的集电极电流分别为 如果两个同样的晶体管(IS1=IS2=IS, nI0 和 I0,并忽略它们的基极电流,那么它们基极-发射极电压差值 ΔVBE 为:

ΔVBE = VBE1 − VBE2 = VT ln nI 0 I − VT ln 0 I S1 I S2

α⋅

∂V+ ∂V +β⋅ − =0 ∂T ∂T

(8-3)

这样就得到具有零温度系数的基准电压,其原理如图 8- 1 所示。式(8-4)为基准电压的基 本表达式。

VREF = α ⋅ V+ + β ⋅ V−

(8-4)

图 8- 1 带隙电压基准的一般原理

由于双极型晶体管 (BJT) 有以下两个特性: 1)双极型晶体管的基极-发射极电压 (VBE) 电压与绝对温度成反比;2)在不同的集电极电流下,两个双极型晶体管的基极-发射级电压 的差值(ΔVBE)与绝对温度成正比。因此,双极晶体管可构成带隙电压基准的核心。 8.2.1 负温度系数电压 对于一个双极型晶体管,其集电极电流(IC)与基极-发射极电压(VBE)的关系为:

带隙基准电压源BandGap的调节与理论分析PPT课件

第5页/共21页

BandGap电路原理图

第6页/共21页

与电源无关的偏置电路

BandGap偏置电路主要通过改变电阻R1的 值使得电流稳定在18uA左右,NM12采用二极 管的连接方式得到一个对电源Vdd不敏感的偏 置电流Iref,通过NM13的尺寸比例将Iref自举到 Iout,使得Iref和Iout满足一定的比例关系并与 Vdd的变化无关。

第20页/共21页

感谢您的观看!

第21页/共21页

T q

VBE

第4页/共21页

零温度系数的基准电压

• 利用双极晶体管的正,负温度系数电压,可设计出一个零温度系数的基准。

• 令 =1,

=-1.5

VREF V对BE上式两(边VT分l别n n对)温度T求导,得到零温度系数的基准:

VBE T

mV 。K VT T 0.087

ln n 17.2 VREF VBE 17.2VT 1.25V

第14页/共21页

不同电压的温度扫描

图示为电源电压为3.0V, 3.3V,3.6V, restypical, captypical,diotypical, biotypical,ff的工艺模型下 的DC仿真。可以看出,输 出电压为1.255V到1.275V 之间,温漂系数为

第15页/共21页

不同电压的温度扫描

图示为电源电压为 3.3Vrestypical, captypical,diotypical, biotypical,(tt,ss,ff, sf,fs)的工艺模型下的 DC仿真。可以看出,输 出电压为1.235V到 1.265V之间。温漂系数均 小于20ppm,(ss情况下 为26ppm)

第19页/共21页

图示为电源电压为3.0V, 3.3V,3.6V, restypical, captypical,diotypical, biotypical,ss的工艺模型 下的DC仿真。可以看出, 输出电压为1.225V到 1.25V之间,温漂系数为

带隙基准电压源PPT课件

∑

VREF a1VBE a2VT

VREF T

a1

VBE T

a2

VT T

0

利用上面的正、负温度系数电压,我们可以设计出一个令人满 意的零温度系数带隙基准电压源:

因此令 a1 1

VREF VBE a2 (VT ln n)

原理

室温附近:

VBE / T 1.5mV / K VBE k ln n 0.087 ln n(mV / K )

而目前产业界用得最多的电压基准源就是带隙基准电压源,几乎在 绝大多数的芯片都能看到带隙基准电压源的身影!在模拟集成电路设计 的三大教材中也专门对此进行了讲解说明:

原理

半导体工艺中具有正温度系数和负温度系数的两种电压: • 负温度系数的PN结电压VBE • 正温系数的热电压VT

为了产生零温度系数电压基准信号可将负温度系数的PN结电压 VBE和正温度系数的热电压VT进行组合即可实现,这样就会得到零 温度系数(ZTC:Zero Temperature Coefficient)带隙电压基准源。

17.2 -17.1455

100 % 0.32%

误差很小,说明实验效果很好。 17.2

谢谢观看

廖方云 4031431807

SUCCESS

THANK YOU

2019/7/26

那么我们首先来回顾一下上面提到的两种随温度变化的电压:

• PN结结电压 • 热电压

原理

将与绝对温度呈正比例变化的电压VT 和与绝对温度呈反比例变化 的电压VBE进行线性组合从而产生带隙电压基准源。

与绝对温度呈反比电压

VBE VCTAT

a1

与绝对温度呈正比电压

VT VPTAT

《带隙基准电压源》课件

带隙基准电压源 的发展趋势与展 望

技术创新方向探讨

提高精度和稳定 性:通过改进电 路设计和材料选 择,提高基准电 压源的精度和稳 定性。

降低功耗:通过 优化电路设计和 采用低功耗器件, 降低基准电压源 的功耗。

集成化:将基准 电压源与其他电 路模块集成,提 高系统的集成度 和可靠性。

智能化:通过引 入智能控制算法, 提高基准电压源 的自适应能力和 抗干扰能力。

测试设备:包括电压源、电 流源、示波器、万用表等

测试步骤:按照测试标准进行, 包括设置参数、测量数据、分 析结果等

评估标准及流程详解

评估标准: 精度、稳 定性、温 度特性、 电源抑制 比等

评估流程: 测试准备、 测试实施、 数据分析、 结果评估 等

测试准备: 选择合适 的测试设 备、设置 测试条件 等

感谢您的观看

汇报人:PPT

案例一:用于ADC/DAC转换器的基准电压源设计

应用背景:ADC/DAC转换器需要稳定的基准电压源 设计要求:高精度、低噪声、低功耗 带隙基准电压源的优势:温度稳定性好、精度高、功耗低 设计方法:选择合适的带隙基准电压源芯片,进行电路设计和调试 应用效果:提高了ADC/DAC转换器的性能和稳定性

案例二:用于PLL锁相环的基准电压源设计

设计过程中需要注意电压源的稳定性和精度 优化建议:采用高精度的电阻和电容,提高电压源的稳定性 注意电源噪声对电压源的影响,采用滤波器进行抑制 优化建议:采用低噪声的电源,提高电压源的精度 注意温度对电压源的影响,采用温度补偿技术进行校正 优化建议:采用高精度的温度传感器,提高温度补偿的精度

带隙基准电压源 的应用案例分析

功耗:带隙基准电压源的功耗较低, 适合在低功耗系统中使用

《带隙基准电压源》课件

4. 优化电路参数

根据仿真结果和实际测试数据,对电路参数进行优化,以提高带隙基 准电压源的性能。

电路设计的优化方法

温度补偿

通过引入温度补偿元件或采用 温度补偿技术,减小温度对带 隙基准电压源输出电压的影响

。

噪声抑制

采用低噪声元件、优化布线方 式和滤波技术等手段,减小带 隙基准电压源输出电压中的噪 声成分。

温漂

02

带隙基准电压源的温漂是指其在一定温度范围内的输出电压变

化量,温漂越小,性能越好。

热稳定性

03

带隙基准电压源在高温下的稳定性,良好的热稳定性可以保证

其在高温环境下正常工作。

04

带隙基准电压源的实现方式

模拟实现方式

01

02

03

运算放大器

使用运算放大器来调整和 稳定带隙基准电压,以实 现高精度和低噪声的输出 。

电阻和电容

通过精密电阻和电容来构 建带隙基准电压源,以实 现温度补偿和稳定性。

差分放大器

使用差分放大器来提高带 隙基准电压的精度和线性 度,以减小温度和电源电 压变化的影响。

数字实现方式

查找表

使用查找表来存储不同温度下的带隙基准 电压值,通过查表方式实现温度补偿。

数字滤波器

使用数字滤波器来处理带隙基准电压的输 出,以提高其稳定性和精度。

数字控制环路

使用数字控制环路来调整带隙基准电压的 输出,以实现高精度和低噪声的性能。

混合实现方式

模拟与数字相结合

将模拟和数字技术相结合,以实现高性能的带隙基准电压源。例如,可以使用 模拟电路来实现温度补偿和稳定性,同时使用数字电路来实现高精度和低噪声 的性能。

带隙基准电压源课件

成本控制

通过改进工艺、提高设备利用率、降 低原材料消耗等方式降低成本。开发 新型材料和工艺,提高产品性能和降 低成本。

优化工艺参数和设备性能,提高工艺 稳定性和良品率。加强过程监控和数 据分析,及时发现并解决问题。

带隙基准电压源测试与评估

测试方法介绍

测试原理

基于带隙基准电压源的工作原理, 采用合适的测试方法对其性能进 行评估。

发展历程及现状

发展历程

自20世纪70年代起,随着半导体工艺和集成电路技术的发展,带隙基准电压源 逐渐得到了广泛应用。近年来,随着物联网、汽车电子等新兴领域的快速发展, 对带隙基准电压源的需求不断增加,推动了其技术的不断创新和进步。

现状

目前,带隙基准电压源已经形成了较为完善的理论体系和技术体系,各种高性能、 低功耗、小尺寸的带隙基准电压源产品不断涌现,满足了不同领域的应用需求。

带隙基准电压源在工作过程中可能会受到电源噪声、温度变化等因素的

影响,导致输出电压的不稳定,甚至产生较大的误差。因此,如何降低

噪声干扰、提高稳定性是亟待解决的问题。

02

精度与功耗的矛盾

高精度带隙基准电压源通常需要消耗较大的功耗,而低功耗设计又可能

导致精度的下降。因此,如何在保证精度的前提下降低功耗是一个重要

运算放大器选择

选用低噪声、高增益、低 失调电压的运算放大器, 以提高电路的性能指标。

电源电压选择

根据电路的工作电压范围, 选择合适的电源电压,以 保证电路的正常工作。

版图设计与实现

元器件布局

合理的元器件布局可以减 小电路中的寄生效应和噪 声干扰,提高电路的性能 指标。

电源线、地线设计

电源线、地线的设计要考 虑电流的大小和方向,以 避免电源噪声对电路的影响。

11 第十一章 带隙基准(1)

VREF ≈ VBE + 17.2VT ≈ 1.25V

现在设计一个电路使VBE增加至17.2VT。考虑图中的 电路,其中的基极电流被忽略,晶体管Q2由几个并联 的单元组成,Q1是一个单元的晶体管。设想我们以某 种方式使V01和V02相等。于是,VBE=RI+VBE2且

¾在忽略沟道长度调制效应时图(a)和(b)电路几乎不受电源的 影响。正因如此,该电路中所有的晶体管均采用等长的沟道长度。

Strictly Confidential - Do Not Distribute – Copyright 2010

10

启动问题

¾独立于电源偏置的一个重要问题:存在“退化”偏置点。

第十一章 带隙基准

金湘亮 博士 xiangliangjin@

Strictly Confidential - Do Not Distribute – Copyright 2010

1、概述 2、与电源无关的偏置 3、与温度无关的基准 4、PTAT 电流的产生

Strictly Confidential - Do Not Distribute – Copyright 2010

1

独立于电源的偏置(1)

如图(a)所示,如果IREF不 随VDD而变化,并且忽略 M2和M3的沟道长度调制效 应,那么ID2 和ID3就保持

与电源电压无关。问题就在 于:我们如何产生IREF?

(a)使用一个理想电流源作为偏置的电流镜, (b)使用一个电阻作为偏置的电流镜

图(b):作为电流源的近似,我们在VDD到M1的栅极之间接

¾ 除了电源、工艺和温度变化外,还有若干参数对于参 考源也很关键,包括输出阻抗、输出噪声和功耗。

带隙基准

电流和电源无关,和电阻有关。 当沟道长度效应很小时,电流和电源的依赖性很小。 电路有另一个稳定点: Iout = 0 必须加启动电路。 电路在上电时,启动电路驱动偏置电路摆脱“简并”偏置 点 如图:M3-M5-M2-Rs提供了一条电源 到地的通路,使M2和M3工作。 M2和M3导通后, Vgs5 < Vth M5被关断,不影响偏置电路的正常工作

∴Vout > Veff 2 +Veff1 = Veff + nVeff = (n +1)Veff

例如,取

n =1, ⇒Vout > 2Veff

显然,摆幅可以增加。

改进的电流源

注意M5的栅极偏置电压:

VG1 = VG4 = VG5 = (n +1)Veff +Vth

同时: VDS4 >Veff 4 = nVeff

QVDS4 = VG3 −Veff = (Vth +Veff ) −Veff = Vth Vth > Veff 4 = nVeff

是可以保证的

上述偏置使M2和M3处在饱和与线性区的边缘 若: Ibias ≥ Iin, 则,M5栅极电压足够使M3和M2处在饱和与区 若: Ibias = Iin, I ↑⇒Veff1 ↑⇒γ ≠ 0,Vth4 ↑⇒VDS3 < Veff ⇒ Rout ↓ 使

∂Vbe ∂VT = α1 +α2 lnn ∂T ∂T ∂T ∂V ∂VT k Q be = −1.5mV /o K = = 0.087 /o K mV ∂T ∂T q α1 =1 α2 = α ∂Vref ⇒α lnn =17.2时, =0 ∂T ∂Vref

Vref = α1Vbe +α2VT lnn = Vbe +17.2VT ≈1.25 V

低温漂低功耗带隙基准类电路

低温漂低功耗带隙基准类电路低温漂低功耗带隙基准电路,这名字听着就有点高深莫测,不是吗?不过别急,我们今天就轻松聊聊这个话题,把它拆得简单点,大家一起去看看这个看似复杂的东西到底怎么回事,能给我们的电子设备带来什么好处。

首先呢,带隙基准电路是啥?说白了,它就是一种能提供稳定电压的电路,哪怕环境温度变化或者电源电压波动,也能保持自己的稳定性。

这一点,就像是你在大夏天还坚持喝冰啤酒一样,哪怕外面热得像火炉,它始终冷得刚刚好,不受外界环境影响。

所以,带隙基准电路通常用在那些要求电压稳定的地方,比如精密测量仪器、传感器和微控制器等等。

不过,这个电路也并不是完美的。

就像人一样,虽然后天养成了钢铁般的耐性,但在不同的环境下,也有可能出现"低温漂"的情况。

什么叫低温漂呢?就是温度变化导致电路输出电压发生偏差。

哎呀,这可不是什么小问题!想象一下,如果一个电路在寒冷的环境下输出电压不稳定,那你的仪器就会出现误差,影响测量结果,甚至可能导致系统崩溃。

那可不得了!所以,在设计带隙基准电路的时候,低温漂问题可得好好考虑。

要是没有解决好这个问题,电路就像是根本站不住的沙堡,随时都会被风吹垮。

而说到低功耗,这就更重要了。

别看我们说的是电路设计,功耗控制可是个大难题。

在现代社会,尤其是移动设备满天飞的今天,大家都希望能有更长的电池寿命。

你想想看,如果你拿着一部手机,满电开始玩,结果不到几个小时就得找插座充电,那还真不如拿个砖头塞进包里省事儿。

所以低功耗成了设计中非常关键的一点。

带隙基准电路,如果能做到低功耗,那就不仅能保持电压稳定,还能不消耗太多电池电量,真是两全其美,谁不想要呢?那要怎么做到低温漂低功耗呢?说到底,设计者得在细节上下功夫。

带隙基准电路的核心是利用了“带隙电压”的特性。

这个电压和温度变化有关系,但如果设计得当,可以将温度的影响压到最小。

就像有个老大哥在你身边,不管外面风雨多大,他都能稳定住局面。

带隙基准电压源(Bandgap)设计范例

图 1.1

Bandgap 模块线路图

二. 等效架构图

(a)

(b)

(c) 图 1.2 Bandgap 模块等效原理图

三. 电路功能描述

正常工作时,Bandgap 模块为系统提供稳定、高精度的 1.28v 的基准电压, 并为其它电路模块提供稳定的偏置电流。

四. 输出、输入信号线功能描述

I = I S (e qVB E / kT − 1)

(1.1) 当 VBE >> kT / q 时, I ≈ I S e q.VBE / k .T

VBE = VT . ln( I ) IS

(1.2) 其中 VT = kT 为热电压,k 是 Boltzmann 常数,q 是电荷量。 q

图 1.2(b) 是参考电压产生的实际等效架构电路, R19 、R20 、R21 、Q11 和 Q12、Q19 构成带隙电压产生器的主题部分,由 Qx10 、Qx8 、 Q19、 Qx7 、 Q10 以及 Q18 组成了放大器及补偿电路,保证了参考电压输出的稳定。 由运算放大器的性质,得:

Q12 和 Q19 的电流相等;R19、R20、R21 和二极管连接的 Q11 组成分压网络, 将 Q12、Q19 产生的 ? VBE 放大(R19+R20+R21)/R21 倍后与 VBE11 相加,产 生基准电压 VREF ;放大管 QX7 、Q18 和负载管 Q10 组成符合放大电路,将 IC19 和 IC12 的差值放大,反馈到分压网路中的 R21,从而调整 Q12、Q19 的工作点, 保证 IC19 等于 IC12 ;电容 C2 和 R23 用来进行频率补偿。 电流偏置 IBias2 产生电路(图 2(c)) :由 P39、Q3、R8 组成。Q3 的基极连 接 VREF ,其射极电位即 R8 的一端电位 VEQ3=VREF -VBEQ3,与电源电压无关, 从而流过电阻 R8 的电流与电源无关,即 IBias2 与电源无关。 1.使能原理: ENB 高电平时,使能关断有效。当 ENB 为高电平时,使能管 N15、N18、 N17 工作,则 N19 的漏极电压、P8 的漏极电压、VREF 被拉到低电平,电路关 断。 BIAS_EN 低电平时,使能关断有效。当 BIAS2_EN 低电平时,使能管 P13 工作,P7、P1 的栅极即 Bias 为高电平,电流偏置为 0,同时,基准电压 VREF 为零电平。 BIAS2_EN 低电平时,使能关断有效。当 BIAS_EN 低电平时,使能管 P34 工作,Bias2 为高电平,电流偏置 IBias2 为 0。 2.启动原理 P14、R15、N19、N16 组成启动电路。启动过程:ENB 为低电平,当未启 动时,P7、P8 两支路的电流为 0,此时 P8 的漏极电压为 0 电位,N19 不通,N19 的漏极为高电位,此时 N16 管导通,形成从电源到地的通路 R12、P7、N16,使 P7 有电流流过,从而打破 0 电流的状态;之后 P8 漏极电位上升, N19 导通, N16 截止,启动过程结束。

带隙基准电压源(Bandgap)设计范例

REFERENCE

Book: [1] Paul R. Gray, Paul J. Hurst, Stephen H. Lewis et. Analysis and Design of Analog Integrated Circuits(4th Edition). John Wiley & Sons, Inc., 2001. 314-326. [2] Behzad Razavi. Design of Analog CMOS Integrated Circuit. The McGraw-Hill Companies,Inc. ,2001. P384~P390 [3] 比查德.拉扎维(著) ,陈贵灿,程军等(译). 模拟 CMOS 集成电路设计. 西 安交通大学出版社,2003,312-320

I1 I2 I 1 AE19 VR21 = ∆VBE = VBE19 − VBE12 = VT ln I − VT ln I = VT ln I A S12 S19 2 E12

(1.3) 式中, AE19、 AE12 是 Q19 、 Q12 管的发射区面积, 它们的比值为 N: 1。由于 VA=VB, I1=I2,代入(3)式得

VR 21 = VT ln ( N )

(1.4)

故 VREF 为 VREF = VBE11 + VR 21 + VR20 + VR19 = VBE11 + ( (1.5) 从上式中可得到基准电压只与 PN 结的正向压降、 电阻的比值以及 Q12 和 Q19 的发射区面积比有关,因此在实际的工艺制作中将会有很高的精度。当基准建立 之后,基准电压与输入电压无关。第一项 VEB 具有负的温度系数,在室温时大约 为-2mV/℃,第二项 VT 具有正的温度系数,在室温时大约为+0.087mV/℃,通过 设定合适的工作点,便 可以使两项之和在某一温度下达到零温度系数,从而得到 具有较好温度特性的电压基准。 图 2(a)中 IBIAS 是基准提供给其它模块的电流,它与微电流源产生的电流 Iref 成比例关系,I0 为提供给参考电压产生模块的电流源,它同微电流源同样成 一定的比例关系,而对于微电流源我们有: VBE 25 = VBE26 + Iref * Rnew1

(拉扎维)第十一章带隙基准(模拟cmos集成电路设计)

Bandgap Ref Ch. 11 # 10

华大微电子:模拟集成电路原理

与温度无关的偏置

正温度系数电压

VBE VBE1 VBE 2 VT ln

nI0 I VT ln 0 VT ln n I S1 IS2

VBE k ln n T q

Bandgap Ref Ch. 11 # 11

华大微电子:模拟集成电路原理

实例分析

Bandgap Ref Ch. 11 # 28

华大微电子:模拟集成电路原理

实例分析

Bandgap R11 # 4

华大微电子:模拟集成电路原理

本讲内容 • • • • • • 概述 与电源无关的偏置 与温度无关的基准 PTAT电流的产生 恒定Gm偏置 实例分析

Bandgap Ref Ch. 11 # 5

华大微电子:模拟集成电路原理

与电源无关的偏置

如何产生IREF?

Bandgap Ref Ch. 11 # 9

华大微电子:模拟集成电路原理

与温度无关的偏置

负温度系数电压

Eg VBE 4 mVT E g q VBE VT I C V ln 4 m T 2 VT T T IS T kT T

当VBE=750mV,T=300K,为-1.5mV/K

华大微电子:模拟集成电路原理

与温度无关的偏置

Bandgap Ref Ch. 11 # 18

华大微电子:模拟集成电路原理

本讲内容 • • • • • • 概述 与电源无关的偏置 与温度无关的基准 PTAT电流的产生 恒定Gm偏置 实例分析

Bandgap Ref Ch. 11 # 19

华大微电子:模拟集成电路原理

华大微电子:模拟集成电路原理

7 带运放的带隙基准设计

图 1.3 直流扫描曲线 1 第 3 页,共 9 页

ห้องสมุดไป่ตู้

带运放的带隙基准设计

图 1.4 直流扫描曲线 2

3、瞬态分析 给电源电压加一正弦信号,频率为 1k,峰峰值为 20mV,观察基准输出电压,基准电 压的输出波形如图 1.5 所示: 从两个波形的峰峰值仍然可以算电压灵敏度。 图 1.5 中电压源 的瞬态波形也打印出来了。从图可以看出,当电压源的峰峰值为 20mV 时,基准电压输出 的峰峰值仅为 1.56191967uV,这个值非常小,所以此电路的电源抑制比非常好。 4、工艺角分析 这里仅给出三种组合即 ttt, sss, fff 组合的情况, 其实一共有四十五中组合, 自己可以试着做 做看。波形如图 1.6 所示:

从图中可以看出, 当温度从负 40 度变化到 125 度时, 基准电压的最大值和最小值之差 仅为 1.5mV。 2、直流分析 ①扫描电源电压,vdd 从 0 变化到 5V,这样可以大致观察出 vdd 在多大范围内,电路 就可以正常工作, 波形如图 1.3 所示: 从图 1.3 可以看出当电源电压从 1.5V 变化到 3.4V 时, 基准电压几乎是一条平坦的曲线,也就是说在这个范围内,基准电路基本上都可以正常工 作。在此设计中我们用的是 simc18 库中的 1.8V 的模型。可以看出此电路的工作范围很宽, 即电源抑制比很大。在波形窗口中选择菜单栏的 Marker->Place->Trace Marker,然后再点 击你想看的波形中的某点,这样就可以标出他的横坐标和纵坐标,如图 1.3 所示。 ②使电源电压从 1.6V 变化到 2.1V,再做一次直流扫描,而这次扫描的目的是为了看 在正常的工作范围内,基准电压随电源电源的变化,并可以计算出电压灵敏度(或者叫电源 抑制比)。波形如图 1.4 所示:在波形窗口中选择菜单栏的 Trace->Delta Cursor,可以精确 观察曲线中两点的横坐标,纵坐标及其横坐标之差,纵坐标之差。

pnp带隙基准电路

pnp带隙基准电路摘要:一、引言二、PNP型晶体管的工作原理三、PNP带隙基准电路的构成四、PNP带隙基准电路的工作原理五、PNP带隙基准电路的应用领域六、总结正文:一、引言PNP带隙基准电路是一种基于PNP型晶体管的电路,具有稳定性好、精度高、结构简单等优点,广泛应用于各种电子设备和系统中。

本文将详细介绍PNP带隙基准电路的构成、工作原理及应用领域。

二、PNP型晶体管的工作原理PNP型晶体管是由p型半导体、n型半导体和p型半导体组成的,其中p 型半导体为基片,n型半导体为发射极,p型半导体为集电极。

当发射极施加正电压时,电子从发射极向基片扩散,空穴从基片向集电极扩散,从而形成电流。

三、PNP带隙基准电路的构成PNP带隙基准电路主要由两个PNP型晶体管、一个电容和一个电阻组成。

其中,两个PNP型晶体管分别为基准晶体管和调整晶体管,电容用于滤波,电阻用于限流。

四、PNP带隙基准电路的工作原理1.当基准晶体管的发射极电压达到其带隙电压时,基准晶体管进入导通状态,集电极电流达到最大值。

2.基准晶体管的集电极电流通过电容滤波后,形成稳定的基准电压。

3.调整晶体管的发射极电压通过电阻分压后,与基准电压进行比较。

4.当调整晶体管的发射极电压大于基准电压时,调整晶体管进入截止状态;反之,调整晶体管进入导通状态。

5.通过调整电阻分压,可以改变调整晶体管的发射极电压,从而实现对基准电压的调整。

五、PNP带隙基准电路的应用领域PNP带隙基准电路广泛应用于各种电子设备和系统中,如模拟电路、数字电路、通信电路等,作为基准电压源,为其他电路提供稳定的电压参考。

六、总结PNP带隙基准电路是一种基于PNP型晶体管的电路,具有稳定性好、精度高、结构简单等优点。

通过两个PNP型晶体管、一个电容和一个电阻的组合,实现了对基准电压的调整。

带隙基准电压源课件ppt

原理

半导体工艺中具有正温度系数和负温度系数的两种电压: • 负温度系数的PN结电压VBE • 正温系数的热电压VT

为了产生零温度系数电压基准信号可将负温度系数的PN结电压 VBE和正温度系数的热电压VT进行组合即可实现,这样就会得到零 温度系数(ZTC:Zero Temperature Coefficient)带隙电压基准源。

已知既定温漂系数 PPM为17.2,且n=7, 因为R1为26k,由公式

PPM R2 lnn R1

可推出R2,取整后暂 时R2设置为260k.

实验电路仿真

电阻R2初始值为260k时,输出电压随温度变化而变化的曲线。

实验电路仿真

为探究输出曲线的 最佳温度特性,设电阻 R2为变量R,并给其一 个变化范围,并缩小范 围找出同等温度范围内, 相对最好的温度特性的 输出曲线。右图为R设 置为200K到300K之间 的输出曲线。由图可知 R2为260k时,曲线较 为平缓,温度特性较好.

带隙基准电压源

意义

电压基准源通常要求具有较高的精度和稳定度:

• 不随电源电压变化 • 不随温度变化 • 不随半导体工艺变化

由于电压基准源的上述特性,其在集成电路的设计中扮演极其重要 的作用。尤其各种DAC,ADC,传感器芯片,检测芯片,电源管理类等 芯片中广泛使用!

而目前产业界用得最多的电压基准源就是带隙基准电压源,几乎在 绝大多数的芯片都能看到带隙基准电压源的身影!在模拟集成电路设计 的三大教材中也专门对此进行了讲解说明:

(3)

将(3)与 V R E FV B Ea2(V Tlnn)联立可得:

PPM= R2 lnn 17.2 R1

由此可设计电路,假设取n=7,令R1=26k,计算 得R2=260k

带隙基准电路基本原理

带隙基准电路的基本原理是基于半导体材料的能带结构。

在半导体中,存在一个禁带(能隙),用于区分导带和价带。

导带中的电子能够在半导体中自由移动,而价带中的电子处于固定位置。

当在半导体中施加电压时,电子能够从价带跃迁到导带中,从而形成电流。

带隙基准利用半导体材料特有的能带结构来生成稳定的电压参考。

具体原理如下:首先,在半导体材料中形成两个P-N结,其中一个为温度感应器,另一个是反向偏置的二极管。

当在这两个结之间施加偏置电压时,会形成一条叫做带隙电压(Bandgap Voltage)的电压参考。

该电压与半导体材料的能带隙相关,而与工作温度无关。

《带隙基准电路》课件

运放是带隙基准电路中的关键元件,其性能直接影响电路的性能。需要根据电路要求选择合适的运放,如带宽、噪声、失调等参数。

选择合适的运放

电源电压和功耗是带隙基准电路的重要参数,需要考虑在满足性能要求的同时,尽量减小功耗和电源电压。

考虑电源电压和功耗

1

2

3

利用CMOS工艺制作带隙基准电路,具有高集成度、低功耗等优点,是当前最常用的实现方法。

带隙基准电路

目录

带隙基准电路概述带隙基准电路的基本原理带隙基准电路的设计与实现带隙基准电路的性能测试与评估带隙基准电路的改进与发展趋势

01

CHAPTER

带隙基准电路概述

带隙基准电路是一种集成电路,用于产生一个与温度和电源电压无关的参考电压或电流。

它利用双极晶体管的基极-发射极电压差(ΔVBE)的正温度系数和硅的带隙电压(VBG)的负温度系数来产生一个零温度系数的电压或电流。

性能比较

将带隙基准电路的性能与其他同类电路进行比较,以评估其性能优劣。

数据分析

对测试数据进行统计分析,以评估带隙基准电路的性能指标是否满足设计要求。

改进建议

根据测试结果,提出改进带隙基准电路性能的建议和措施,以提高其性能。

03

02

01

05

CHAPTER

带隙基准电路的改进与发展趋势

温度补偿

01

通过分析电路的频率响应、噪声和温漂等特性,评估带隙基准源的稳定性。

稳定性分析

启动电路

线性调整率

带隙基准源在输入电压变化时,输出电压的变化率。

负载调整率

带隙基准源在不同负载条件下,输出电压的变化率。

03

CHAPTER

带隙基准电路的设计与实现

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SS

TT

FF

-

温度系数

5.79ppm/℃ 1.13ppm/℃ 0.74ppm/℃

4.功耗

3.4

图

功 耗 仿 真 图

SS

TT

FF

-

功耗

0.99mW 1.35mW 2.05mW

5.蒙特卡罗分析

输出电压

温度系数

-

电源抑制比 功耗

蒙特卡罗分析结果

输出电压(V) 电源抑制比(dB) 温度系数(ppm/℃) 功耗(uA)

基于0.35微米CMOS工艺的 带隙基准源设计

Based on 0.35um BCD Process BandGap reference design

-

第一章 概述

1.BCD工艺简介 BCD(Bipolar-CMOS-DMOS)功率集成电路器件, 通过MOS管的最高电压可达40V,最低为5V。

2.带隙基准源简介及其应用 模拟集成电路广泛地包含带隙基准电压源,由于带隙基准 电压源的输出电压与电源电压、工艺参数和温度的关系很 小,所以带隙基准电压源一直是集成电路中的一个重要的 基本模块,例如可应用于LDO或者电荷泵等。

核心电路

第三章 仿真结果

1.输出电压

3.1

图

输 出 电 压 仿 真 图

SS

TT

FF

-

输出电压 1.25V 1.23V 1.22V

2.电源抑制比(PSRR)

3.2

图

电 源 抑 制 比 仿 真 图

SS

TT

FF

-

PSRR

73dB 72dB 93dB

3.温度系数Leabharlann TC)3.3图温 度 系 数 仿 真 图

-

SS 1.356-1.041 98.54-51.226 105.78-1.337

218-182

TT 1.342-1.023 106.58-51.55 89.205-0.566

321-274

FF 1.332-1.013 95.71-48.64 78.72-2.183

441-383

-

参考文献: 1.高电源抑制比的CMOS带隙基准电压源_吴志明 2.模拟CMOS集成电路设计_毕查德拉扎维

当VBE 750mV ,T 300K时,VBE T -1.5mV / K

VBE

VT

ln

IC IS

,VT

KT

q

VBE2 VT ln n (R2 R3) R3 VREF

-

图1.2 基本的带隙基准源

第二章 BandGap电路设计

1.核心电路(含启动电路)

VREF

2VT ln R45

n

R43

VBEQ32

12

3

启动电路

-

图2.1 核心电路(含启动电路)

2.运放电路

三级运放 通过运放,使整个核心电路 的偏置电压独立于电源电压, 从而提高电源抑制比。

-

图2.2 运放电路

3.启动电路

2.3

图

保证运放正常工作,并提供偏置

启

动

电

路

-

启动电路

-

三级运放

此电路共计49个MOS管,5个三极管,8个电阻和1个电容 图2.4 整体电路