XDC约束技巧之时钟篇

xdc约束文件

xdc约束文件摘要:一、引言二、XDC约束文件概述1.定义与作用2.基本结构三、XDC约束文件的编写规范1.语法规则2.常用关键字3.注意事项四、XDC约束文件的应用场景1.硬件描述语言设计2.电子设计自动化(EDA)工具3.芯片验证五、实例分析1.XDC约束文件在FPGA设计中的应用2.XDC约束文件在芯片验证中的应用六、总结与展望正文:一、引言随着电子设计自动化(EDA)技术的不断发展,硬件描述语言(HDL)在电子设计中的应用越来越广泛。

XDC约束文件作为一种重要的设计约束工具,对于提高设计效率和可靠性具有重要意义。

本文将从XDC约束文件的定义、结构、编写规范、应用场景等方面进行详细介绍,并通过实例分析,帮助读者更好地理解和掌握XDC约束文件的使用。

二、XDC约束文件概述1.定义与作用XDC(Extended Design Constraints)约束文件是一种用于描述硬件设计约束的文件,它包含了设计中所需的时序、功耗、面积等约束信息。

在硬件设计过程中,XDC约束文件起到了约束和规范设计行为的作用,有助于确保设计满足预设的性能、功耗和面积目标。

2.基本结构XDC约束文件通常采用文本格式,包含了一系列的关键字和参数。

一个典型的XDC约束文件主要包括以下几个部分:(1)设计参数声明:声明设计中使用的参数,如时钟周期、频率等。

(2)目标约束:设定设计的性能、功耗、面积等目标。

(3)约束条件:描述设计中各模块之间的时序关系、资源占用等约束。

(4)设计规则:用于规范设计中信号、模块的行为,如不允许出现无限级反馈环等。

三、XDC约束文件的编写规范1.语法规则XDC约束文件遵循一定的语法规则,关键字和参数需要按照规定的方式进行声明和定义。

例如:```parameter CLK_PERIOD = 10;target DESIGN_SPEED = 100;constraint C_PATH = (CLK_PERIOD - 1) * DESIGN_SPEED;```2.常用关键字XDC约束文件中常用关键字包括:- parameter:声明设计参数。

Vivado集成开发环境时序约束介绍

Vivado时序约束本文主要介绍如何在Vivado设计套件中进行时序约束,原文出自Xilinx中文社区。

1Timing Constraints in Vivado -UCF to XDCVivado软件相比于ISE的一大转变就是约束文件,ISE软件支持的是UCF(User Constraints File),而Vivado软件转换到了XDC(Xilinx Design Constraints)。

XDC主要基于SDC(Synopsys Design Constraints)标准,另外集成了Xilinx的一些约束标准,可以说这一转变是Xilinx向业界标准的靠拢。

Altera从TimeQuest开始就一直使用SDC标准,这一改变,相信对于很多工程师来说是好事,两个平台之间的转换会更加容易些。

首先看一下业界标准SDC的原文介绍:Synopsys' widely-used design constraints format, known as SDC, describes the "design intent" and surrounding constraints for synthesis, clocking, timing, power, test and environmental and operating conditions. SDC has been in use and evolving for more than 20 years, making it the most popular and proven format for describing design constraints. Essentially all synthesized designs use SDC and numerous EDA companies have translators that can read and process SDC.Xilinx原先的自成一派(UCF)其实其实也算做的不错,相信使用过UCF的工程师也有同感,并没有什么不便。

XDC约束技巧之IO篇上

XDC约束技巧之I/O篇 (上)《XDC约束技巧之时钟篇》中曾对I/O约束做过简要概括,相比较而言,XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。

加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要讨论的I/O约束了。

I/O约束的语法XDC中可以用于I/O约束的命令包括set_input_delay / set_output_delay和set_max_delay / set_min_delay 。

其中,只有那些从FPGA管脚进入和/或输出都不经过任何时序元件的纯组合逻辑路径可以用set_max_delay / set_min_delay来约束,其余I/O时序路径都必须由set_input_delay / set_output_delay来约束。

如果对FPGA的I/O不加任何约束,Vivado会缺省认为时序要求为无穷大,不仅综合和实现时不会考虑I/O时序,而且在时序分析时也不会报出这些未约束的路径。

本文以下章节将会着重讨论XDC接口约束和时序分析的基础,介绍如何使用set_input_delay / set_output_delay对FPGA的I/O时序进行约束。

Input约束上图所示set_input_delay的基本语法中,<objects> 是想要设定input约束的端口名,可以是一个或数个port;-clock 之后的 <clock_name> 指明了对 <objects> 时序进行分析所用的时钟,可以是一个FPGA中真实存在的时钟也可以是预先定义好的虚拟时钟;-max之后的 <maxdelay> 描述了用于setup分析的包含有板级走线和外部器件的延时;-min之后的 <mindelay> 描述了用于hold分析的包含有板级走线和外部器件的延时。

让-XDC-时序约束为您效力

让-XDC-时序约束为您效力让XDC 时序约束为您效力作者:Adam Taylor e2v 公司首席工程师aptaylor@时序和布局约束是实现设计要求的关键因素。

本文是介绍其使用方法的入门读物。

完成RTL 设计只是FPGA 设计量产准备工作中的一部分。

接下来的挑战是确保设计满足芯片内的时序和性能要求。

为此,您经常需要定义时序和布局约束。

我们了解一下在基于赛灵思图1–时钟域CLK1 和CLK2 相互之间异步。

您可通过在约束文件中声明时钟组来管理时钟路径之间的关系。

当声明时钟组时,Vivado 工具不会对组内定义的时钟之间的任何方向执行时序分析。

为了有助于生成时序约束,Vivado 工具将时钟定义为三种类型:同步、异步或不可扩展。

•同步时钟具有可预测的时序/相位关系。

通常主时钟及其衍生时钟符合这种特性,因为它们具有公共的根起源和周期。

•异步时钟之间不具备可预测的时序/相位关系。

通常不同的主时钟(及其衍生时钟)符合这种特性。

异步时钟有不同的起源。

•如果超过1,000个周期后,仍无法确定公共周期,那么两个时钟就是不可扩展的。

如果是这种情况,将使用1,000 个周期内的最差建立时间关系。

不过,无法保证这就是实际的最差情况。

使用Vivado 生成的时钟报告来确定您所处理的时钟是哪种类型。

该报告可帮助您识别异步和不可扩展时钟。

声明多周期路径能实现更合适而且要求放松的时序分析,从而让时序引擎集中处理其它更关键的路径。

识别出这些时钟后,您就可利用“set clock group”约束禁止它们之间的时序分析。

Vivado 套件使用的是赛灵思设计约束(XDC),其基于广泛使用的Tcl 约束格式的Synopsys 设计约束(SDC)。

通过XDC 约束,您可使用以下命令定义时钟组:set_clock_groups -name-logically_exclusive -physically_exclusive -asynchronous -group-name 是为组赋予的名称。

Xilinx约束学习笔记(二)——定义时钟

Xilinx约束学习笔记(⼆)——定义时钟2. 定义时钟2.1 关于时钟为了获得最佳精度路径覆盖信息,必须正确定义时钟。

时钟要定义在时钟树的根 pin 或 port 上,称为 source point。

时钟的边缘应该由周期和波形进⾏组合描述。

周期使⽤纳秒做为单位进⾏定义。

它对应于波形重复的时间。

波形是⼀系列的上升沿和下降沿绝对时间列表,单位为纳秒,并且所有时间在⼀个时钟周期内。

列表必须包含偶数个值。

第⼀个值始终对应于第⼀个上升边缘。

如果没有指定波形,波形的默认占空⽐为 50%,相移为 0。

2.1.1 传播时钟周期和波形属性只展现出了时钟的理想特性。

当时钟进⼊ FPGA 并通过时钟树传播时,时钟边沿被延缓,并受噪声和硬件⾏为引影响。

这些特性称为时钟⽹络延迟和时钟不确定性。

时钟的不确定性包括:时钟抖动(clock jitter)相位错误⽤户指定添加的不确定性默认情况下,Vivado 在做时序分析时,始终将时钟视为传播时钟,即⾮理想时钟,以此提供准确的余量值,其中包括时钟树插⼊延迟和不确定性。

2.1.2 专⽤硬件资源FPGA 有⼤量专⽤的时钟管脚,这个管脚可以专门⽤来做时钟的输⼊。

FPGA 内部包含有 MMCM、PLL 和 BUR 之类的时钟资源。

2.2 基准时钟(Primary Clock)基准时钟是通过 FPGA 输⼊端⼝或千兆收发器输出引脚(例如,恢复时钟)进⼊设计的时钟。

基准时钟只能通过 create_clock 指令进⾏定义。

(为什么是千兆收发器?下⾯的话应该可以解释,7 系列的 GT 恢复时钟不能⾃动推导,必须⼿动定义。

⽽ US 和 USP 系列的可以⾃动推导,不需要⼈为定义)Primary clocks must be defined on a gigabit transceiver output only for Xilinx® 7 series FPGAs. For UltraScale and UltraScale+™ devices, the timer automatically derives clocks on the GT output ports.基准时钟必须附加到⽹表对象。

xdc管脚约束

xdc管脚约束

XDC(Xilinx Design Constraints)是Xilinx FPGA设计工具使用的约束文件格式,用于描述FPGA设计中的管脚约束。

XDC约束文件提供了一种灵活而强大的方式来规定FPGA设计中输入输出管脚的电气和时序要求。

以下是一些常见的XDC管脚约束:

1. IO标识:定义每个管脚的引脚名称和所在物理位置,例如使用LOC属性指定管脚的物理位号。

2. 约束引用时钟信号:使用create_clock约束指定输入时钟的频率和时钟延迟,以帮助实现时钟域划分。

3. 时序约束:使用set_input_delay和set_output_delay约束指定输入和输出信号的最大和最小延迟,以控制时序关系。

4. 约束时钟域与数据域:使用create_clock和

set_input_delay/receive_clock约束指定时钟域和数据域之间的时序要求。

5. 差分信号约束:对于差分信号,使用set_input_delay和

set_output_delay约束分别指定差分对的最大和最小延迟。

6. 禁用管脚约束:使用set_property约束禁用某些管脚,以保证设计的正确性。

这些约束将在FPGA布局时被综合软件使用,确保设计在时

序和电气上达到所需的目标。

在设计中正确使用XDC约束可以提高设计的性能和可靠性。

vivado异步时钟域约束

vivado异步时钟域约束在Vivado中,异步时钟域约束可以通过使用不同的异步时钟域目标约束和异步时钟域针对约束来实现。

以下是一些设置异步时钟域约束的步骤:1. 确定异步时钟边沿:首先,要确定异步时钟的边沿。

异步时钟通常是由外部信号引入的,因此您需要确定信号是在上升沿还是下降沿出现。

2. 创建异步时钟域:在Vivado的约束文件(.xdc文件)中,您可以使用`create_clock`命令创建异步时钟域。

例如,如果异步时钟是在上升沿出现的,您可以使用以下命令创建异步时钟域:```create_clock -name async_clk -period <异步时钟周期> [get_ports async_clk]```请注意,`async_clk`是异步时钟信号的端口名,并且`<异步时钟周期>`需要根据实际情况进行设置。

3. 添加异步时钟域目标约束:为了确保设计正确地处理异步时钟域中的数据,您需要为异步时钟域中的寄存器和其他目标添加约束。

您可以使用`set_false_path`或`set_clock_groups`命令来设置异步时钟域目标约束。

具体使用哪个命令取决于您的设计需求。

请参考Vivado用户指南中的相关章节来了解如何使用这些命令。

4. 添加异步时钟域针对约束:异步时钟域针对约束可以确保设计正确处理异步时钟域和其他时钟域之间的数据传输。

您可以使用`create_generated_clock`命令或`set_input_jitter`命令来设置异步时钟域针对约束。

具体使用哪个命令取决于您的设计需求。

请参考Vivado用户指南中的相关章节来了解如何使用这些命令。

以上是一些设置异步时钟域约束的基本步骤。

具体的配置方法和命令可能会因设计需求和环境而有所不同。

有关更详细的信息和指导,请参考Vivado用户指南中的相关章节。

vivado差分时钟管脚约束

Vivado差分时钟管脚约束1. 引言在FPGA设计中,时钟是一个关键因素。

时钟的稳定性和准确性对于设计的正确性和性能至关重要。

在Vivado工具中,差分时钟是一种常见的时钟类型,它可以提供更好的抗干扰能力和噪声容限。

本文将介绍如何在Vivado中进行差分时钟管脚约束的配置,以确保设计的正确性和稳定性。

2. 差分时钟概述差分信号由一对相互补偿的信号组成,其中一个信号是另一个信号的反相。

这种信号传输方式可以提供更好的抗干扰能力和噪声容限,因此在高速数据传输和时序要求严格的应用中广泛使用。

在FPGA设计中,差分时钟常用于数据接口、存储器接口、高速通信等场景。

为了正确地使用差分时钟,在设计过程中需要对其进行适当的约束设置。

3. Vivado工具约束设置流程步骤1:创建约束文件首先,在Vivado工程目录下创建一个新的约束文件(以.xdc为后缀),例如constraints.xdc。

步骤2:定义差分时钟在约束文件中,使用create_clock命令定义差分时钟。

语法如下:create_clock -period <period> -waveform {<rise_time><fall_time>} [get_pins <c lock_pins>]其中: - <period>表示时钟周期,单位为纳秒(ns); - <rise_time>和<fall_time>表示上升沿和下降沿的时间,单位为纳秒(ns); - <clock_pins>表示与差分时钟相关的管脚。

例如,定义一个50MHz的差分时钟:create_clock -period 20 [get_pins {clk_p clk_n}]步骤3:设置约束属性除了定义差分时钟周期外,还可以设置其他约束属性来进一步优化设计。

以下是一些常见的约束属性及其用法:•set_input_delay:设置输入延迟;•set_output_delay:设置输出延迟;•set_false_path:设置虚假路径(不进行时序优化);•set_max_delay:设置最大延迟。

xdc约束技巧

xdc约束技巧我们需要明确xdc的基本概念。

xdc使用“约束”来定义电路设计中的各种要求和限制。

这些约束可以包括时序要求、电气特性、布局要求等。

通过使用xdc约束技巧,设计师可以确保电路在满足特定要求的同时,能够实现设计目标。

在使用xdc约束技巧时,有几个注意事项需要注意。

首先,要合理使用时序约束。

时序约束是描述电路中各个时序要求的重要手段。

设计师需要了解电路中各个时序要求的来源和意义,然后通过使用xdc约束来定义这些要求。

合理设置时序约束可以提高电路的性能和可靠性。

要合理使用电气特性约束。

电气特性约束用于描述电路中各个信号的电气特性,如电压、电流等。

设计师需要了解电路中各个信号的电气特性要求,并通过使用xdc约束来定义这些要求。

合理设置电气特性约束可以确保电路在正常工作范围内运行。

要合理使用布局约束。

布局约束用于描述电路中各个元件的布局要求,如位置、方向等。

设计师需要了解电路中各个元件的布局要求,并通过使用xdc约束来定义这些要求。

合理设置布局约束可以提高电路的布局效果和可维护性。

还有一些其他的xdc约束技巧需要注意。

首先,要避免过度约束。

过度约束可能导致电路无法满足设计要求,或者增加设计的复杂度。

设计师需要根据实际情况,合理设置约束。

其次,要合理使用约束分组。

约束分组可以将相关的约束组织在一起,便于管理和维护。

设计师需要根据实际情况,将相关的约束进行合理的分组。

要进行约束验证。

在设计完成后,设计师需要对设计进行约束验证,以确保设计满足所有的约束要求。

约束验证可以通过使用xdc工具来完成。

xdc约束技巧是一种在使用xdc工具时非常重要的技巧。

通过合理使用xdc约束技巧,设计师可以确保电路设计满足各种要求和限制,提高设计的性能和可靠性。

希望本文介绍的xdc约束技巧对大家有所帮助。

vivado xdc约束的注释

vivado xdc约束的注释摘要:一、Vivado XDC 约束简介1.Vivado XDC 约束的概念2.Vivado XDC 约束的作用二、Vivado XDC 约束的注释1.注释的必要性2.注释的基本语法3.注释的实例三、Vivado XDC 约束注释的应用1.设计优化2.提高代码可读性3.协同开发四、总结1.Vivado XDC 约束注释的重要性2.展望Vivado XDC 约束注释的未来发展正文:一、Vivado XDC 约束简介Vivado 是一款由Xilinx 公司推出的FPGA 设计工具,它提供了一种名为XDC(Xilinx Design Constraints)的约束语言,用于描述FPGA 设计中时序、面积、功耗等方面的约束。

通过使用XDC 约束,设计人员可以更高效地优化FPGA 设计,提高设计质量。

二、Vivado XDC 约束的注释1.注释的必要性在编写Vivado XDC 约束时,为了更好地表达设计思路,提高代码可读性,需要在约束文件中添加注释。

注释可以帮助设计人员理解约束的意义,便于协同开发和后期维护。

2.注释的基本语法Vivado XDC 约束中的注释采用“/* */”或者“//”的形式。

例如:```/* 这是一个注释*/```或者```// 这也是一个注释```3.注释的实例下面是一个包含注释的Vivado XDC 约束示例:```/* 该约束用于设置时钟的周期*/set_property CLK_CYCLE 1000 [get_clock clk];/* 该约束用于禁止对时钟进行PLL 操作*/set_property PLL_DISABLE 1 [get_clock clk];```三、Vivado XDC 约束注释的应用1.设计优化通过在Vivado XDC 约束中添加注释,设计人员可以更好地理解约束的意义,从而优化设计方案。

例如,在上述示例中,通过注释可以知道时钟周期的设置和PLL 操作的禁止,有助于调整时序和功耗等方面的设计。

XDC约束技巧-CDC篇1.1

XDC约束技巧之CDC篇上一篇《XDC约束技巧之时钟篇》介绍了XDC的优势以及基本语法,详细说明了如何根据时钟结构和设计要求来创建合适的时钟约束。

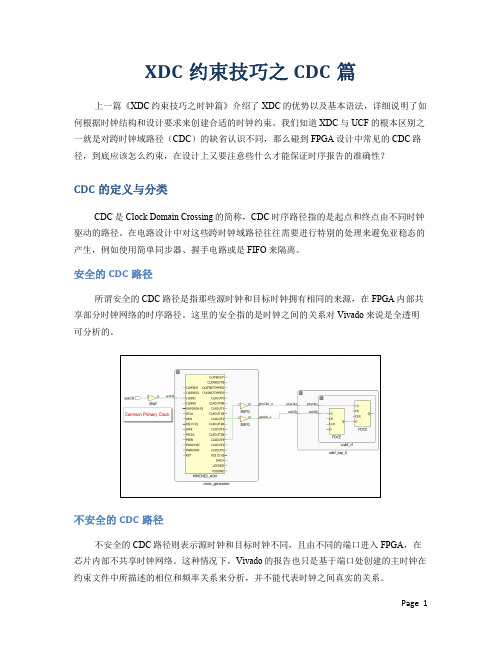

我们知道XDC与UCF的根本区别之一就是对跨时钟域路径(CDC)的缺省认识不同,那么碰到FPGA设计中常见的CDC路径,到底应该怎么约束,在设计上又要注意些什么才能保证时序报告的准确性?CDC的定义与分类CDC是Clock Domain Crossing的简称,CDC时序路径指的是起点和终点由不同时钟驱动的路径。

在电路设计中对这些跨时钟域路径往往需要进行特别的处理来避免亚稳态的产生,例如使用简单同步器、握手电路或是FIFO来隔离。

安全的CDC路径所谓安全的CDC路径是指那些源时钟和目标时钟拥有相同的来源,在FPGA内部共享部分时钟网络的时序路径。

这里的安全指的是时钟之间的关系对Vivado来说是全透明可分析的。

不安全的CDC路径不安全的CDC路径则表示源时钟和目标时钟不同,且由不同的端口进入FPGA,在芯片内部不共享时钟网络。

这种情况下,Vivado的报告也只是基于端口处创建的主时钟在约束文件中所描述的相位和频率关系来分析,并不能代表时钟之间真实的关系。

在Vivado中分析CDC在ISE中想要快速定位那些需要关注的CDC路径并不容易,特别是要找到不安全的CDC时,因为ISE缺省认为所有来源不同的时钟都不相关且不做分析,要报告出这类路径,需要使用ISE Timing Analyzer (TRCE),并加上“-u” (表示unconstrained)这个选项。

在Vivado中则容易许多,我们可以使用report_clock_interaction命令(GUI支持)来鉴别和报告设计中所有的时钟关系。

执行命令后会生成一个矩阵图,其中对角线上的路径表示源时钟与目标时钟相同的时钟内部路径,其余都是CDC路径。

Vivado还会根据网表和已读入的约束分析出CDC路径的约束情况,并分颜色表示。

vivado xdc约束的注释

vivado xdc约束的注释摘要:1.简介2.Vivado XDC约束注释的作用3.Vivado XDC约束注释的语法4.Vivado XDC约束注释的实例5.总结正文:1.简介Vivado是Xilinx公司推出的一款FPGA设计工具,它提供了丰富的功能,可以帮助设计人员快速地完成FPGA设计。

在Vivado中,XDC(Xilinx Design Constraints)约束是用于描述FPGA设计中时序、面积、功耗等约束的一种方式。

通过XDC约束,设计人员可以对FPGA设计进行优化,从而提高设计性能。

2.Vivado XDC约束注释的作用在Vivado中,XDC约束注释是对XDC约束的一种补充,它可以为设计人员提供关于约束的更多信息,以便更好地理解约束的意义和作用。

注释可以帮助设计人员更快地找到问题,更有效地进行调试和优化。

3.Vivado XDC约束注释的语法Vivado XDC约束注释使用C语言的注释语法,即在约束条件前加上“//”符号。

例如:```// This constraint sets the maximum frequency of the design to 100 MHzset_property MAX_FREQUENCY [get_design_handle] 100.0 MHz```在这个例子中,“//”符号后面的注释说明了该约束的作用,即设置设计的最大频率为100 MHz。

4.Vivado XDC约束注释的实例以下是一个关于时钟约束的XDC约束注释实例:```// This constraint sets the input clock to be 100 MHz and its phase to be 0 degreesset_property CLK_INPUT [get_ports {clk_in}] [get_design_handle]set_property CLK_FREQUENCY [get_ports {clk_in}] 100.0 MHzset_property CLK_PHASE [get_ports {clk_in}] 0.0 degrees```在这个例子中,注释说明了输入时钟的频率、类型和相位约束。

vivado xdc约束的注释

vivado xdc约束的注释摘要:1.概述Vivado XDC约束2.XDC约束的用途和优势3.如何使用XDC约束进行设计优化4.实例分析:应用XDC约束的步骤与结果5.总结与展望正文:随着现代数字电路设计复杂度的不断提高,对于设计约束的管理和优化变得越来越重要。

Vivado XDC约束是一种用于验证和优化数字电路设计的约束语言,它可以大大提高设计工程师的工作效率和设计质量。

本文将详细介绍Vivado XDC约束的用途、优势以及在实际设计中的应用方法。

一、概述Vivado XDC约束Vivado XDC约束是一种硬件描述语言,主要用于描述数字电路设计中的时序、功耗、面积等约束。

它具有较强的可读性和易用性,可以方便地与现有的EDA工具相结合,为设计工程师提供全面的约束管理解决方案。

二、XDC约束的用途和优势1.用途Vivado XDC约束可用于以下场景:- 约束优化:通过设置时序、功耗、面积等目标,自动调整设计参数,达到优化目标。

- 约束分析:对设计进行前仿真,预测实际运行效果,提前发现并解决潜在问题。

- 约束验证:确保设计满足预设的约束条件,避免不良设计。

2.优势Vivado XDC约束具有以下优势:- 强大的约束能力:可以描述各种复杂的时序、功耗、面积等约束条件。

- 高效率:与Vivado工具紧密结合,方便设计工程师进行约束管理和优化。

- 易用性:语法简单,易于学习和掌握。

- 可靠性:经过多年实际应用,证明了其在设计约束管理方面的稳定性和可靠性。

三、如何使用XDC约束进行设计优化1.创建XDC约束文件:使用文本编辑器或Vivado提供的XDC编辑器,创建或编辑XDC约束文件。

2.设置约束目标:在XDC约束文件中,设置时序、功耗、面积等优化目标。

3.应用约束文件:将约束文件导入Vivado工具,进行设计优化。

4.分析与验证:在Vivado中进行时序分析、功耗分析等,检查设计是否满足约束条件。

5.调整与优化:根据分析结果,调整约束文件或设计参数,重复步骤3-4,直至达到满意的设计优化结果。

XDC约束技巧之CDC篇

XDC约束技巧之CDC篇上一篇《XDC约束技巧之时钟篇》介绍了XDC的优势以及基本语法,详细说明了如何根据时钟结构和设计要求来创建合适的时钟约束。

我们知道XDC与UCF的根本区别之一就是对跨时钟域路径(CDC)的缺省认识不同,那么碰到FPGA设计中常见的CDC路径,到底应该怎么约束,在设计上又要注意些什么才能保证时序报告的准确性?CDC的定义与分类CDC是Clock Domain Crossing的简称,CDC时序路径指的是起点和终点由不同时钟驱动的路径。

在电路设计中对这些跨时钟域路径往往需要进行特别的处理来避免亚稳态的产生,例如使用简单同步器、握手电路或是FIFO来隔离。

安全的CDC路径所谓安全的CDC路径是指那些源时钟和目标时钟拥有相同的来源,在FPGA内部共享部分时钟网络的时序路径。

这里的安全指的是时钟之间的关系对Vivado来说是全透明可分析的。

不安全的CDC路径不安全的CDC路径则表示源时钟和目标时钟不同,且由不同的端口进入FPGA,在芯片内部不共享时钟网络。

这种情况下,Vivado的报告也只是基于端口处创建的主时钟在约束文件中所描述的相位和频率关系来分析,并不能代表时钟之间真实的关系。

在Vivado中分析CDC在ISE中想要快速定位那些需要关注的CDC路径并不容易,特别是要找到不安全的CDC时,因为ISE缺省认为所有来源不同的时钟都不相关且不做分析,要报告出这类路径,需要使用ISE Timing Analyzer (TRCE),并加上“-u” (表示unconstrained)这个选项。

在Vivado中则容易许多,我们可以使用report_clock_interaction命令(GUI支持)来鉴别和报告设计中所有的时钟关系。

执行命令后会生成一个矩阵图,其中对角线上的路径表示源时钟与目标时钟相同的时钟内部路径,其余都是CDC路径。

Vivado还会根据网表和已读入的约束分析出CDC路径的约束情况,并分颜色表示。

让 XDC 时序约束为您效力

让XDC 时序约束为您效力作者:Adam Taylor e2v 公司首席工程师时序和布局约束是实现设计要求的关键因素。

本文是介绍其使用方法的入门读物。

完成RTL 设计只是FPGA 设计量产准备工作中的一部分。

接下来的挑战是确保设计满足芯片内的时序和性能要求。

为此,您经常需要定义时序和布局约束。

我们了解一下在基于赛灵思FPGA 和SoC 设计系统时如何创建和使用这两种约束。

时序约束最基本的时序约束定义了系统时钟的工作频率。

然而,更高级的约束能建立时钟路径之间的关系。

工程师利用这类约束确定是否有必要对路径进行分析,或者在时钟路径之间不存在有效的时序关系时忽视路径。

默认情况下,赛灵思的Vivado® 设计套件会分析所有关系。

然而,并非设计中的所有时钟之间都有可以准确分析的时序关系。

例如当时钟是异步的,就无法准确确定它们的相位,如图1 所示。

图1–时钟域CLK1 和CLK2 相互之间异步。

您可通过在约束文件中声明时钟组来管理时钟路径之间的关系。

当声明时钟组时,Vivado 工具不会对组内定义的时钟之间的任何方向执行时序分析。

为了有助于生成时序约束,Vivado 工具将时钟定义为三种类型:同步、异步或不可扩展。

•同步时钟具有可预测的时序/相位关系。

通常主时钟及其衍生时钟符合这种特性,因为它们具有公共的根起源和周期。

•异步时钟之间不具备可预测的时序/相位关系。

通常不同的主时钟(及其衍生时钟)符合这种特性。

异步时钟有不同的起源。

•如果超过1,000个周期后,仍无法确定公共周期,那么两个时钟就是不可扩展的。

如果是这种情况,将使用1,000 个周期内的最差建立时间关系。

不过,无法保证这就是实际的最差情况。

使用Vivado 生成的时钟报告来确定您所处理的时钟是哪种类型。

该报告可帮助您识别异步和不可扩展时钟。

声明多周期路径能实现更合适而且要求放松的时序分析,从而让时序引擎集中处理其它更关键的路径。

识别出这些时钟后,您就可利用“set clock group”约束禁止它们之间的时序分析。

vivado 串口时序约束

vivado 串口时序约束Vivado是一款由Xilinx公司开发的集成电路设计和验证工具,常用于FPGA和SoC的设计与开发。

在Vivado中,串口通信是一种常见的通信方式,可以实现与外部设备的数据交互。

在这篇文章中,我们将讨论如何使用Vivado进行串口时序约束。

串口通信是一种通过串行数据传输的通信方式,常用于连接计算机与外部设备,如传感器、显示器、打印机等。

在FPGA设计中,串口通信可以实现FPGA与外部设备之间的数据交互。

为了保证数据的正确传输,需要对串口时序进行约束。

在Vivado中,可以通过约束文件(.xdc文件)来对串口时序进行约束。

约束文件是一种文本文件,用于描述设计中各个信号的时序关系。

在约束文件中,可以定义时钟信号、数据信号以及它们之间的时序关系。

我们需要定义串口通信中的时钟信号。

时钟信号是串口通信的基准信号,用于同步数据的传输。

在Vivado中,可以使用create_clock命令来定义时钟信号,并指定时钟频率和时钟源。

例如,下面的命令定义了一个时钟频率为100MHz的时钟信号:create_clock -period 10 [get_pins uart_inst/clk]接下来,我们需要定义数据信号的时序关系。

数据信号是通过串口进行传输的信息,包括起始位、数据位、校验位和停止位等。

在Vivado中,可以使用set_input_delay和set_output_delay命令来定义数据信号的输入和输出延迟。

例如,下面的命令定义了一个输入延迟为1ns的数据信号:set_input_delay -clock [get_pins uart_inst/clk] 1 [get_pins uart_inst/rx]我们还可以使用set_false_path命令来定义不需要进行时序约束的路径。

例如,下面的命令定义了一个不需要进行时序约束的路径:set_false_path -from [get_pins uart_inst/clk] -to [get_pins uart_inst/rx]在串口通信中,数据的传输速率也是一个重要的参数。

vivado差分时钟管脚约束

Vivado差分时钟管脚约束简介Vivado是Xilinx公司推出的一款集成化的设计套件,用于FPGA和SoC设计。

在设计中,时钟约束是非常重要的一步,特别是在差分时钟设计中。

本文将介绍差分时钟的概念、Vivado中的差分时钟约束方法以及一些常见的差分时钟约束实例。

差分时钟概念差分时钟是指由两个相位相反的时钟信号组成的时钟信号。

在FPGA设计中,差分时钟常用于高速接口和数据传输中,以提高抗干扰能力和信号完整性。

差分时钟信号由一个正相位时钟信号(P时钟)和一个反相位时钟信号(N时钟)组成。

这两个时钟信号的频率相同,相位相反,且幅值也相同。

差分时钟信号的传输通过差分对(Differential Pair)来实现,其中P时钟信号和N时钟信号分别传输在差分对的两个导线上。

Vivado中的差分时钟约束在Vivado中,使用XDC(Xilinx Design Constraints)文件来进行时钟约束。

对于差分时钟,我们需要指定差分对的起点和终点,以及时钟频率和时钟延迟等信息。

以下是一些常用的差分时钟约束命令:create_clockcreate_clock -period <时钟周期> -name <时钟名称> [get_pins <差分对起点>]该命令用于定义一个差分时钟。

其中,-period参数指定时钟周期,-name参数指定时钟名称,get_pins参数指定差分对的起点。

set_input_delayset_input_delay -clock <时钟名称> -min <最小延迟> [get_ports <差分对终点>]该命令用于设置差分对的输入延迟。

其中,-clock参数指定时钟名称,-min参数指定最小延迟,get_ports参数指定差分对的终点。

set_output_delayset_output_delay -clock <时钟名称> -max <最大延迟> [get_ports <差分对起点>]该命令用于设置差分对的输出延迟。

FPGA 101 手把手课堂:让 XDC 时序约束为您效力

FPGA 101 手把手课堂:让XDC 时序约束为您效力set_multicycle_path path_ multiplier [-setup|-hold][-start|-end][-from ] [-to ][-through ]当您声明多周期路径时,事实上是将建立或保持(或二者皆有)分析要求与 path_mutiplier 相乘。

例如在上面的第一个实例中,每两个时钟周期有一次输出,因此对于建立时序而言 path_multiplier 是 2。

因为多周期路径既可应用到建立时光又可应用到保持时光,那么您可以挑选其应用位置。

当您声明建立时光乘数时,最佳做法通常是用法下面的公式同时声明一个保持时光乘数。

保持周期 = 建立乘数– 1 –保持乘数这对于我们所介绍的下列容易实例意味着,保持乘数由下面这个公式确定:保持乘数 = 建立乘数– 1,当用法公共时钟时。

为了演示多周期路径的重要性,我创建了一个容易实例,您可在这里下载。

在 XDC 文件中有一个实例包含了建立和保持这两个已被同时声明的多周期路径。

物理约束最常用的物理约束是 I/O 引脚布局和与 I/O 引脚有关的参数定义,例如标准驱动强度。

不过,还有其它类型的物理约束,包括布局、布线、I/O 和配置约束等。

布局约束能够定义单元的位置,而布线约束可用来定义信号的布线。

I/O 约束可用来定义 I/O 位置及其参数。

最后,配置约束可用来定义配置办法。

同样,也有一些约束不属于这几组约束。

Vivado 设计套件包含三种这样的约束,它们主要用于网表中。

DONT_TOUCH –该约束可用来阻挡优化,这样当实现平安关键型或高牢靠性系统时该约束会十分实用。

第1页共4页。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

XDC约束技巧之时钟篇Xilinx©的新一代设计套件Vivado中引入了全新的约束文件XDC,在很多规则和技巧上都跟上一代产品ISE中支持的UCF大不相同,给使用者带来许多额外挑战。

Xilinx工具专家告诉你,其实用好XDC很容易,只需掌握几点核心技巧,并且时刻牢记:XDC的语法其实就是Tcl语言。

XDC的优势XDC是Xilinx Design Constraints的简写,但其基础语法来源于业界统一的约束规范SDC(最早由Synopsys公司提出,故名Synopsys Design Constraints)。

所以SDC、XDC跟Vivado Tcl的关系如下图所示。

XDC的主要优势包括:1.统一了前后端约束格式,便于管理;2.可以像命令一样实时录入并执行;3.允许增量设置约束,加速调试效率;4.覆盖率高,可扩展性好,效率高;5.业界统一,兼容性好,可移植性强;XDC在本质上就是Tcl语言,但其仅支持基本的Tcl语法如变量、列表和运算符等等,对其它复杂的循环以及文件I/O等语法可以通过在Vivado中source一个Tcl文件的方式来补充。

(对Tcl话题感兴趣的读者可以参考作者的另一篇文章《Tcl在Vivado中的应用》)XDC与UCF的最主要区别有两点:1.XDC可以像UCF一样作为一个整体文件被工具读入,也可以在实现过程中被当作一个个单独的命令直接执行。

这就决定了XDC也具有Tcl命令的特点,即后面输入的约束在有冲突的情况下会覆盖之前输入的约束(时序例外的优先级会在下节详述)。

另外,不同于UCF是全部读入再处理的方式,在XDC中,约束是读一条执行一条,所以先后顺序很重要,例如要设置IO约束之前,相对应的clock一定要先创建好。

2.UCF是完全以FPGA的视角看问题,所以缺省认为所有的时钟之间除非预先声明是同步的,否则就视作异步而不做跨时钟域时序分析;XDC则恰恰相反,ASIC世界的血缘背景决定了在其中,所有的时钟缺省视作全同步,在没有时序例外的情况下,工具会主动分析每一条跨时钟域的路径。

XDC的基本语法XDC的基本语法可以分为时钟约束、I/O约束以及时序例外约束三大类。

根据Xilinx的UltraFast设计方法学中Baseline部分的建议(UG949中有详细介绍),对一个设计进行约束的先后顺序也可以依照这三类约束依次进行。

本文对可以在帮助文档中查到的基本XDC语法不做详细解释,会将重点放在使用方法和技巧上。

时钟约束时钟约束必须最早创建。

对7系列FPGA来说,端口进来的时钟以及GT的输出RXCLK/TXCLK都必须由用户使用create_clock自主创建为主时钟。

如果是差分输入的时钟,可以仅仅在差分对的P侧用get_ports获取端口,并使用create_clock创建。

例如,Vivado自动推导的衍生时钟MMCM/PLL/BUFR的输出作为衍生时钟,可以由Vivado自动推导,无需用户创建。

自动推导的好处在于当MMCM/PLL/BUFR的配置改变而影响到输出时钟的频率和相位时,用户无需改写约束,Vivado仍然可以自动推导出正确的频率/相位信息。

劣势在于,用户并不清楚自动推导出的衍生钟的名字,当设计层次改变时,衍生钟的名字也有可能改变。

这样就会带来一个问题:用户需要使用这些衍生钟的名字来创建I/O约束、时钟关系或是时序例外等约束时,要么不知道时钟名字,要么时钟名字是错的。

推荐的做法是,由用户来指定这类衍生时钟的名字,其余频率等都由Vivado自动推导。

这样就只需写明create_generated_clock 的三个option,其余不写即可。

如上所示。

当然,此类情况下用户也可以选择完全由自己定义衍生时钟,只需补上其余表示频率/相位关系的option,包括-multiply_by 、-devide_by 等等。

需要注意的是,一旦Vivado在MMCM/PLL/BUFR的输出检测到用户自定义的衍生时钟,就会报告一个Warning,提醒用户这个约束会覆盖工具自动推导出的衍生时钟(例外的情况见文章下半段重叠时钟部分的描述),用户须保证自己创建的衍生钟的频率等属性正确。

用户自定义的衍生时钟工具不能自动推导出衍生钟的情况,包括使用寄存器和组合逻辑搭建的分频器等,必须由用户使用create_generated_clock来创建。

举例如下,create_clock -name clk1 -period 4 [get_ports CKP1]create_generated_clock -name clk2 [get_pins REGA/Q] \-source [get_ports CKP1] -divide_by 2I/O约束在设计的初级阶段,可以不加I/O约束,让工具专注于满足FPGA内部的时序要求。

当时序要求基本满足后,再加上I/O约束跑实现。

XDC中的I/O约束有以下几点需要注意:1.不加任何I/O约束的端口时序要求被视作无穷大。

2.XDC中的set_input_delay / set_output_delay对应于UCF中OFFSET IN / OFFSET OUT,但视角相反。

OFFSET IN / OFFSET OUT是从FPGA内部延时的角度来约束端口时序,set_input_delay / set_output_delay则是从系统角度来约束。

3.典型的I/O时序,包括系统同步、源同步、SDR和DDR等等,在Vivado图形界面的XDC templates中都有示例。

2014.1版后还有一个Timing Constraints Wizard可供使用。

时序例外约束时序例外约束包括set_max_delay/set_min_delay ,set_multicycle_path ,set_false_path 等,这类约束除了要满足XDC 的先后顺序优先级外,还受到自身优先级的限制。

一个总的原则就是针对同一条路径,对约束目标描述越具体的优先级越高。

不同的时序例外约束以及同一约束中不同条件的优先级如下所示:举例来说,依次执行如下两条XDC ,尽管第二条较晚执行,但工具仍然认定第一条约束设定的15为clk1到clk2之间路径的max delay 值。

再比如,对图示路径依次进行如下四条时序例外约束,优胜者将是第二条。

但如果再加入最后一条约束,false path 的优先级最高,会取代之前所有的时序例外约束。

set_max_delay 15 –from [get_clocks clk1] –to [get_clocks clk2]set_max_delay 12 –from [get_clocks clk1]set_false_pathset_max_delay/set_min_delayset_multicycle_path-from pin -to pin -through pin -from clock-to clock 优先级最高 优先级最低set_multicyle_path 2 –through lut/A set_multicycle_path 3 –from REGA/Qset_multicycle_path 3 –to REGB/Dset_multicycle_path 2 –from CLKA -to CLKBset_false_path –through lut/O WinnerWinner Take Precedence高级时钟约束约束最终是为了设计服务,所以要用好XDC 就需要深入理解电路结构和设计需求。

接下来我们就以常见FPGA 设计中的时钟结构来举例,详细阐述XDC 的约束技巧。

时序的零起点用create_clock 定义的主时钟的起点即时序的“零起点”,在这之前的上游路径延时都被工具自动忽略。

所以主时钟创建在哪个“点”很重要,以下图所示结构来举例,分别于FPGA 输入端口和BUFG 输出端口创建一个主时钟,在时序报告中体现出的路径延时完全不同,很明显sysclk_bad 的报告中缺少了之前一段的延时,时序报告不可信。

create_clock –name sysclk –period 10 [get_ports sys_clk]Delay type Incr(ns) Path(ns) Netlist Resource(s)-------------------------------------------- -------------------(clock sysclk rise edge) 0.000 0.000 r0.000 0.000 r sys_clknet (fo=0) 0.000 0.000 clk_infra_i/sys_clkIBUFG (Prop_ibufg_I_O) 0.766 0.766 r clk_infra_i/clkin1_buf/Onet (fo=3, unplaced) 1.109 1.875 clk_infra_i/clkin1BUFR (Prop_bufr_I_O) 0.314 2.189 r clk_infra_i/sys_clk_buf/Onet (fo=10, unplaced) 1.109 3.298 sys_clk_intr sysrst_sync_reg[2]/Ccreate_clock –name sysclk_bad –period 10 [get_pins clk_infra_i/sys_clk_buf/O] Delay type Incr(ns) Path(ns) Netlist Resource(s)-------------------------------------------- -------------------(clock sysclk_bad rise edge)0.000 0.000 rBUFR 0.000 0.000 r clk_infra_i/sys_clk_buf/Onet (fo=10, unplaced) 1.109 1.109 sys_clk_intr sysrst_sync_reg[2]/Csysclk_bad sys_clk% get_clocks -of [get_pins sysrst_sync_reg[2]/C] sysclk clkbufr% get_clocks -of [get_pins write_error_reg/C]clkbufg时钟定义的先后顺序时钟的定义也遵从XDC/Tcl 的一般优先级,即:在同一个点上,由用户定义的时钟会覆盖工具自动推导的时钟,且后定义的时钟会覆盖先定义的时钟。