第五章 MCS-51单片机中断系统

MCS-51系列单片机的中断系统

大连理工大学出版社

第5章 中断

当断不断必受其乱

第5章 中断系统

5.1 概述 MCS-51系列单片机的中断系统 5.2 MCS-51系列单片机的中断系统 5.3 中断程序设计方法

第5 章

中断系统

中断控制是单片机最重要的技术之一, 实时控制及人机交互等应用都是通过中 断实现的。 本章主要介绍中断的基本概念、MCS-51 系列单片机单片机的中断机制及其简单 应用。

5.2.2中断控制 5.2.2中断控制

1.中断允许 MCS-51系列单片机中断系统通过中断允许控制 寄存器IE实现开中断和关中断的功能。 (1)IE寄存器 IE寄存器由一个中断允许总控制位和各中断源 的中断允许控制位构成,从而进行两级中断允 许控制。IE寄存器的各位定义如下:

5.2.2中断控制 IE寄存器

5.2.2中断控制 IE寄存器

EX1(IE.2)——外中断1的中断允许控 制位。中断总允许时,EX1=0,禁止外中 断1中断;EX1=1,允许外中断1中断。 ET1(IE.3)——定时器T1的中断允许控 制位。中断总允许时,EX1=0,禁止T1中 断;ET1=1,允许T1中断。

5.2.2中断控制 5.2.2中断控制 IE寄存器

5.2.1中断源和中断标志

当MCS-51系列单片机的外中断源以脉冲方式触 发时,负脉冲有效。CPU在一个机器周期采样到 INT0(或者 INT1 )引脚上为高电平,在接下 来的一个机器周期采样到INT0(或者INT1)引 脚上是低电平,即出现了下降沿的跳变(负脉 冲)时,就认为是外中断0(或者外中断1)的 一个有效的中断请求信号。因为两次检测的间 隔时间为一个机器周期,负脉冲对应的高低电 平持续时间都应至少维持一个机器周期,从而 保证CPU能够检测到电平的跳变。

单片机原理及应用教程(C语言版)-第5章 MCS-51单片机的中断系统

5.2.5 中断允许控制

例5-1 假设允许INT0、INT1、T0、T1中断,试 设置IE的值。 (2)汇编语言程序 按字节操作: MOV IE,#8FH 按位操作: SETB EX0 ;允许外部中断0中断 SETB ET0 ;允许定时器/计数器0中断 SETB EX1 ;允许外部中断1中断 SETB ET1 ;开定时器/计数器1中断 SETB EA ;开总中断控制位

IP (B8H)

D7 —

D6 D5 D4 D3 D2 D1 D0 — PT2 PS PT1 PX1 PT0 PX0

PT2:定时器/计数器T2的中断优先级控制位 PT2设置1则T2为高优先级,PT2设置0则T2为 低优先级。 后面各位均是如此,设置1为高优先级,设置0 为低优先级,不再一一赘述。 PS:串行口的中断优先级控制位。 PT1:定时器/计数器1的中断优先级控制位。 PX1:外部中断1的中断优先级控制位。 PT0:定时器/计数器0的中断优先级控制位。 PX0:外部中断0的中断优先级控制位。

5.2.4 中断请求标志

4.定时器/计数器T2中断请求标志

T2CON D7 D6 D5 (C8H) TF2 EXF2 D4 D3 D2 D1 D0

EXF2:定时器/计数器2的外部触发中断请求标志 位。T2以自动重装或外部捕获方式定时、计数,当 T2EX(P1.1)引脚出现负跳变时,TF2由硬件置1, 向CPU请求中断,CPU响应中断后,EXF2不会被硬 件清0,需要在程序中以软件方式清0。

5.2.3 外中断触发方式

TCON格式如下:

D7 D6 D5 D4 D3 D2 D1 D0

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

IT0=1,外中断0为下降沿触发 CPU在每一个机器周期的S5P2期间对P3.2引 脚采样,若上一个机器周期检测为高电平,紧挨着 的下一个机器周期为低电平,则使IE0置1。 IT1:外中断1触发方式控制位。功能同IT0

MCS51单片机第5章

中断优先级处理原则

同时发生多个中断申请时 多个中断申请时: 对同时发生多个中断申请时: 不同优先级的中断同时申请(很难遇到) ☞不同优先级的中断同时申请(很难遇到) ——先高后低 先高后低 相同优先级的中断同时申请(很难遇到) ☞相同优先级的中断同时申请(很难遇到) ——按序执行 按序执行 ☞正处理低优先级中断又接到高级别中断 ——高打断低 高打断低 ☞正处理高优先级中断又接到低级别中断 ——高不理低 高不理低

MCS-51单片机的中断系统 MCS-51单片机的中断系统 计算机与外设之间交换信息的方式: 计算机与外设之间交换信息的方式: 无条件传送方式:外设对计算机来说总是准备好的。 (1)无条件传送方式:外设对计算机来说总是准备好的。 (2)查询传送方式:传送前计算机先查询外设的状态, 查询传送方式:传送前计算机先查询外设的状态, 若已经准备好就传送,否则就继续查询/等待。 若已经准备好就传送,否则就继续查询/等待。 中断传送方式: (3)中断传送方式:外设通过申请中断的方式与计算 机进行数据传送。 机进行数据传送。 直接存储器存取方式(DMA) (DMA): (4)直接存储器存取方式(DMA):传送数据的双方直 接通过总线传送数据, 不经CPU中转。 CPU中转 接通过总线传送数据, 不经CPU中转。

中断请求的撤除

为了避免中断请求标志没有及时撤除而造成的重复响应同一中 断请求的错误, CPU在响应中断时必须及时将其中断请求标志 断请求的错误, CPU在响应中断时必须及时将其中断请求标志 位撤除。 位撤除。

申请标志 IE0 TF0 IE1 TF1 RI/TI TF2

中断矢量 0003H 000BH 0013H 001BH 0023H 002BH

中断优先级 最高优先级

最低优先级

第05章 MCS-51单片机的中断与定时(1-4)

2

1

TH0

;P1.0输出“0” ;P1.0输出“1”

5.2 MCS-51单片机的中断系统

五、外中断应用举例

1. 中断初始化程序

设置外中断源的触发方式 设置中断允许寄存器IE 设置中断优先级寄存器IP

2. 中断服务程序

保护现场 中断处理 恢复现场

23/65

5.2 MCS-51单片机的中断系统

【例5-3】 设外部中断0为下降沿触发方 式,高优先级,试编写中断初始化程序

5.2 MCS-51单片机的中断系统

【例5-4】 将单脉冲接到外中断0(INT0)引脚,利 用P1.0作为输出,经反相器接发光二极管。编写程 序,每按动一次按钮,产生一个外中断信号,使发 光二极管的状态发生变化,由亮变暗,或反之

P1.0 单脉冲 发生器 INT0

1

+5V

8031

26/65

5.2 MCS-51单片机的中断系统

串口:0023H

20/65

5.2 MCS-51单片机的中断系统

四、中断请求的撤除

1.定时/计数器中断请求标志TF0/TF1会自动撤除 2.串行口中断请求标志TI/RI要用指令撤除

CLR TI ;清TI标志位 CLR RI ;清RI标志位

3.负脉冲触发的外中断请求标志IE0/IE1会自动撤除 4.低电平触发的外中断请求信号需要外加电路撤除

下次课前请预习5.3节

30/65

5.3 51单片机的定时器/计数器

MCS-51单片机内部有两个16位定时/计数器 T0和T1,简称定时器0和定时器1

在特殊功能寄存器TMOD和TCON的控制下, 它们既可以设定成定时器使用,也可以设定 成计数器使用

定时/计数器有4种工作方式,具有中断功能, 可以完成定时、计数、脉冲输出等任务

第5章-MCS-51单片机中断系统-PPT

5、2、2 MCS-51单片机得中断源

IT1=1,外中断1为下降沿触发 采样:CPU在每一个机器周期得S5P2期间 对P3、3引脚采样,若上一个机器周期检测为 高电平,紧挨着得下一个机器周期为低电平,则 使IE1置1。 IT0:外中断0触发方式控制位。

CPU主要就是通过标志寄存器、控制 寄存器、优先级寄存器对中断源进行管

5、2、2 MCS-51单片机得中断源

(1)与中断标志相关得SFR

主要有:定时器/计数器T0、T1控制寄 存器TCON

串行口控制寄存器SCON 定时器/计数器2控制寄存器T2CON(第 6章介绍) (2)中断控制寄存器:TCON、IE (3)中断优先级寄存器:IP

DMA释放总线:当一批数据传送后, DMA控制器再向CPU发出“结束总线请 求”,CPU响应请求,收回总线使用权。

DMA方式速度高、效率高,可以与CPU 并行工作。

5、1、2 中断得相关概念

1、中断得概念

CPU在正常运行得时候, 外部或者内部发生了请求 CPU迅速去处理得事件,CPU 暂时中断当前得程序,去处理 所发生得事件,处理完事件后, 再返回到原来被中断得程序 继续运行。此过程称为中断。

图5-3 定时器得控制寄存器

TCON可位寻址。复位后TCON=00H。 TF1(TCON、7):T1溢出标志位

当T1计满溢出时,由内部硬件置位; 中断响应后自动清 0。

5、2、2 MCS-51单片机得中断源

TF0:T0溢出标志位 功能同TF1。

IT1:外中断1触发方式设置位 IT1=0,外中断1为低电平触发

5、1、1 微机得输入/输出方式

第5章 MCS-51中断、定时计数器及串行接口

22:26

7

保护现场

课本P103

保护现场是指由于CPU执行中断处理程序时, 可能使用主程序中用过的累加器、寄存器或标志位。

为了使这些寄存器的值在中断服务程序中不被 冲掉,进入中断服务程序前,要将它们保护起来。

中断服务程序执行完,必须恢复原寄存器的内 容及原程序中断处的地址,即恢复现场和恢复断点。

22:26

课本P105

一、中断请求控制

(1) TCON中的中断请求标志位 Timer Controller

TCON为定时/计数器控制寄存器,其字节 地址为88H,可位寻址。这个寄存器除了控制定 时/计数器T0和T1的溢出中断外,还控制外部中 断的触发方式和锁存外部中断请求标志位。

图5-3 TCON中的各位定义

22:26

24

2. 中断响应过程

课本P110

CPU响应中断后,由硬件自动执行如下的功能操作:

(1)根据请求源的优先级高低,对相应的优先级状态 触发器置1,自动生成长调用指令LCALL addr16。

(2)保护断点,把程序计数器PC的内容压入堆栈。 (3)清除相应的中断请求标志位。 (4)把被响应的中断源所对应的中断服务程序入口地

…

先进后出

…

POP DPL

POP DPH

POP ACC

RETI

最后1条指令 必须是RETI

27

中断响应过程

处理文档 电话铃响 暂停文档 文档中作暂停记号 电话交谈 找出暂停记号位置 继续处理文档

执行主程序(日常事务程序) 中断申请信号有效(中断请求)

暂停执行主程序响应中断 当前PC及寄存器入栈(保护现场)

22:26

5

中断系统的基本问题

第五章 MCS-51的中断系统

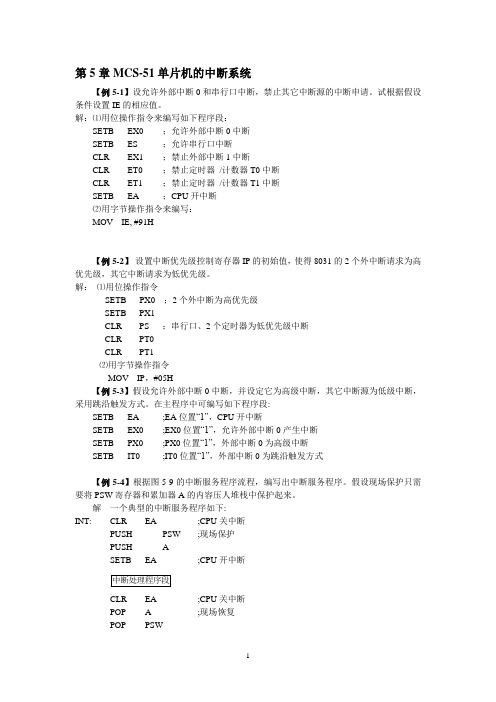

第5章MCS-51单片机的中断系统【例5-1】设允许外部中断0和串行口中断,禁止其它中断源的中断申请。

试根据假设条件设置IE的相应值。

解:⑴用位操作指令来编写如下程序段:SETB EX0 ;允许外部中断0中断SETB ES ;允许串行口中断CLR EX1 ;禁止外部中断1中断CLR ET0 ;禁止定时器/计数器T0中断CLR ET1 ;禁止定时器/计数器T1中断SETB EA ;CPU开中断⑵用字节操作指令来编写:MOV IE, #91H【例5-2】设置中断优先级控制寄存器IP的初始值,使得8031的2个外中断请求为高优先级,其它中断请求为低优先级。

解:⑴用位操作指令SETB PX0;2个外中断为高优先级SETB PX1CLR PS ;串行口、2个定时器为低优先级中断CLR PT0CLR PT1⑵用字节操作指令MOV IP,#05H【例5-3】假设允许外部中断0中断,并设定它为高级中断,其它中断源为低级中断,采用跳沿触发方式。

在主程序中可编写如下程序段:SETB E A ;EA位置“1”,CPU开中断SETB E X0 ;EX0位置“1”,允许外部中断0产生中断SETB P X0 ;PX0位置“1”,外部中断0为高级中断SETB I T0 ;IT0位置“1”,外部中断0为跳沿触发方式【例5-4】根据图5-9的中断服务程序流程,编写出中断服务程序。

假设现场保护只需要将PSW寄存器和累加器A的内容压人堆栈中保护起来。

解一个典型的中断服务程序如下:INT: CLR E A ;CPU关中断PUSH PSW ;现场保护PUSH ASETB E A ;CPU开中断中断处理程序段CLR E A ;CPU关中断POP A ;现场恢复POP PSWSETB E A ; CPU开中断RETI ;中断返回,恢复断点上述程序有几点需要说明的是:⑴本例的现场保护假设仅仅涉及到PSW和A的内容,如果还有其它的需要保护的内容,只需要在相应的位置再加几条PUSH和POP指令即可。

第5章 MCS-51单片机的中断系统

(2)实现实时处理

在实时控制中,现场的参数、信息是不断变化的。 有了中断功能,外界的这些变化量可随时向CPU 发出中断请求,CPU可以马上响应加以处理。

(3)故障处理

单片机运行过程中,出现一些故障时(如掉电、 存储出错、运算溢出等),有了中断功能,单片 机就能自行处理而不必停机。 外界的中断请求是随机的,单片机响应请求后要 转到中断服务程序,与调用子程序相类似,需要 注意对现场进行保护。

ORG 0100H

MAIN: …;

第五章 MCS-51单片机的中断系统

ORG 1000H INT1:PUSH ACC PUSH DPH PUSH DPL PUSH R0 PUSH R1 … POP R1 POP R0 POP DPL POP DPH POP ACC RETI

第五章 MCS-51单片机的中断系统

5.3 中断处理过程

中断响应

中断处理

中断返回

第五章 MCS-51单片机的中断系统

5.3.1 中断响应

1. CPU响应中断的基本条件 (1)有中断源提出中断请求; (2)中断没有被禁止; (3)没有正在响应的同级或更高优先级的中断; (4)当前的指令周期已经结束;(也就是说,中 断申请时,正在执行的这条指令完成后,才会响 应中断请求) (5)若当前指令为RETI或访问IE、IP指令, CPU在执行完当前指令后,要再执行一条指令才 会响应中断请求。

第五章 MCS-51单片机的中断系统

2.中断响应过程 (1)根据响应的中断源的中断优先级,使相应的优 先级状态触发器置1; (2)清除相应的中断请求标志位(串行口中断请求 标志RI和TI除外);

(3)把当前程序计数器PC的内容压入堆栈;

(4)把被响应的中断源所对应的中断服务程序的入 口地址送入PC,从而转入相应的中断服务程序。 CPU响应中断请求后,在中断返回(执行RETI)前, 中断请求必须被清除,即中断标志位=0,否则会再 一次引起中断响应。

郭天祥单片机教程 第5章中断

第5章 MCS - 51单片机的中断

例 2 多中断源。 MCS - 51 单片机 有两个外部中断输入 端, 当有 2 个以上中 断源时, 它的中断输 入端就不够了。此时, 可以采用中断与查询 相结合的方法来实现。 可以使每个中断源都 接在同一个外部中断 输入端上, 同时利用 输入口线作为多中断 源情况下各中断源的 识别线。

EA X X X ET2 PT2 ES PS ET1 EX1 ET0 EX0 PT1 PX1 PT0 PX0

第5章 MCS - 51单片机的中断

5.2.3 中断响应 1. 中断响应的条件

在下列情况下,中断响应会受到阻断: (1) 同级或高优先级的中断已在进行中; (2) 当前的机器周期还不是正在执行指令的最后一个机 器周期(换言之, 正在执行的指令完成前, 任何中断请求 都得不到响应); (3) 正在执行的是一条 RETI或者访问特殊功能寄存器 IE或 IP的指令(换言之, 在 RETI或读写 IE或 IP之后, 不会 马上响应中断请求, 而至少执行一条其它指令之后才会响应)。

0 0

(LSB)

PS

PT1

PX1

PT0

PX0

中 中断 IP B8H 总 允 许 断 器 时

定 串 行 口

定 时 部 器 断 1 中

外 时 器

定 部 中 断

外

2

0 1 0

第5章 MCS - 51单片机的中断 表 5.2 同级内第二优先级次序

第5章 MCS - 51单片机的中断 例如, 某软件中对寄存器IE、 IP设置如下: MOV IE, # 8FH MOV IP, # 06H 则此时该系统中: * CPU中断允许; * 允许外部中断0、外部中断1、定时器 /计数器0、定时器/计 数器1中断申请; * 中断源的优先次序为: 定时器0 > 外部中断1 > 外部中断0 > 定时器1。

单片机原理及其接口技术--第5章 MCS-51单片机中断系统

下来,这称为保护现场,由用户自己编程完成。

保护断点和现场后即可执行中断服务程序,执行完毕, CPU由中断服务程序返回主程序。 主目录 上一页 下一页 结 束

15

……

响应

单片机原理及其接口技术

主程序A

断点

返回

中断返回过程如下:

RETI 中断服务程序B

首先恢复原保留寄存器的内容和标志位的状态,这称为恢 复现场,由用户编程完成。 然后,再加返回指令RETI,RETI指令的功能是恢复PC值, 使CPU返回断点,这称为恢复断点。 恢复现场和断点后,CPU将继续执行原主程序,中断响应 过程到此为止。 主目录 上一页 下一页 结 束

主目录 上一页 下一页 结 束

单片机原理及其接口技术

5.2.2 中断标志与中断控制

1.中断标志

(1) 定时器控制寄存器TCON

SFR之一,锁存中断请求标志,字 节地址88H,可位寻址。

其结构、位名称、位地址及其功能 如表5.1所示。

主目录 上一页 下一页 结 束

单片机原理及其接口技术 表5.1 TCON的结构、位名称、位地址和功能

单片机原理及其接口技术

第5章 MCS-51单片机中断系统

教学目标 5.1 中断概述 5.2 MCS-51中断系统 5.3 中断系统的应用 本章小结 思考题与习题主目录上一页来自下一页结束

单片机原理及其接口技术

教学目标

通过本章教学,要求达到以下目标: 1.熟记MCS-51 5个中断源及其中断入口地址。 2.熟悉TCON、SCON、IE、IP的结构、控制 作用和设置方法。 3.理解MCS-51中断响应过程。 4.了解中断响应等待时间。 5.理解中断请求撤除情况和应对措施。 6.熟悉中断优先控制的方法。 7.掌握中断应用程序的编制方法。

第五章 中断系统

四、中断系统的功能 一般来说,一个中断系统具有以下功能: (一)实现中断及返回 当某中断源发出中断请求后,CPU应决定是否响应这个中断请求,如当前正 在执行更重要的工作可暂时不响应中断,若响应这个中断请求,CPU在当前指令 执行完后,就要保护断点地址和现场(即下条指令地址和相关寄存器内容),以便 执行完中断服务程序后能正确返回原处执行,然后转到需要处理的中断服务程序 的人口地址,去执行中断服务程序,当中断服务程序执行完毕再恢复现场和断点 ,去继续执行主程序。 (二)实现优先级排队 当计算机带有多个中断源时,可能会出现两个或两个以上中断源同时向CPU提 出中断请求的情况。这时CPU应能够根据事先确定的中断源的优先级别来先响应 高优先级的中断 并为它服务,然后再响应较低优先级的中断请求。 (三)实现中断嵌套 当CPU正在响应某一中断源的中断请求时,又有新的中断源发出请求,如果 新的请求的优先级别高于正在执行的中断源的优先级,则CPU暂停现行的服务程 序,转去执行更高级别的中断源的服务程序,执行完毕后再回到被中断的较低中 断源的服务程序继续执行,即实现了中断嵌套。若新的中断源的优先级别低于或 是等于正执行的中断源,则CPU不响应这个请求,直到正在处理的中断服务程序 执行完毕后,才去处理新的中断请求。

三、中断的分类 按中断产生的位置,中断可分为: (1)外部中断,或称外部硬件实时中断,它是由外部送到CPU的某一特定引脚 上产生的。 (2)内部中断,或称软件指令中断,是为了处理程序运行过程中发生的一些意 外情况或调试程序方便而提供的中断。 按接受中断的方式,中断可分为: (1)可屏蔽中断,可以通过指令使CPU根据具体情况决定是否接受中断请求。 (2)非屏蔽中断,只要中断源提出请求,CPU就必须响应,主要用于一些紧急 情况的处理,如掉电等。 以上从不同的角度对中断进行了分类,对于某一种类型的计算机可能只具备 其中的某几种方式,例如MCS—51就不具备非屏蔽中断方式。

第五章-MCS-51单中断系统习题答案.doc

第五章MCS-51单片机中断系统习题答案一、填空题1、中断允许寄存器,中断优先级寄存器。

2、电平触发,边沿触发(或答跳变触发)。

二简答题1、写出8052的中断源和相应的中断入口。

INT0 0003HT0 000BHINT1 0013HT1 001BHTI或RI 0023H2、8051单片机的中断优先级是如何排列的?硬件INT0 T0 INT1 T1 TI或RI软件通过IP定义两个优先级3、外部中断有哪几种触发方式?边沿触发和电平触发。

4、8052单片机程序存储器中的六个特殊单元是什么,各有何用途?0000H(PC),0003H(int0),000BH(c/T0),0013H(int1),001BH(c/T1),0023H(s口)。

4、三、程序设计1、8031芯片的INT0、INT1引脚分别输入压力超限及温度超限中断请求信号,定时器/计数器0作定时检测的实时时钟,用户规定的中断优先权排队次序为:压力超限温度超限定时检测要求确定IE、IP的内容,以实现上述要求。

解:(1)中断控制寄存器各位定义:D7:CPU中断允许位EA,应设为1D6:未定义,可为随意量,取为0D5:定时器/计数器2中断允许位ET2,可取0D4:串行口中断允许位ES, 可取0D3:定时器/计数器1中断允许位ET1, 应取0D2:外部中断1中断允许位EX1, 应取1D1:定时器/计数器0中断允许位ET0, 应取1D0:外部中断0中断允许位EX0, 应取1故IE=87H(2)由硬件确定的同一优先级中断源的优先权排队顺序如下:INT0-C/T0-INT1-C/T1-串行口中断-c/2MCS-51有两个中断优先级,中断优先权选择寄存器IP可对各中断源用软件进行编程,确定为高优先级中断还是低优先级中断。

因些可以用硬件与软件相结合的方法对中断源的优先级进行排序。

由题意,根据IP各位的定义:D7:未定义,可为随意量,取为0D6:未定义,可为随意量,取为0D5:定时器/计数器2优先权选择位PT2,可取0D4:串行口优先权选择位PS, 可取0D3:定时器/计数器1优先权选择位PT1, 应取0 D2:外部中断1优先权选择位PX1, 应取1,应接温度超限信号。

第5章MCS-51的中断系统

例:写出INT1为低电平触发的中断系统初始化程序

SETB EA; SETB EX1 SETB PX1 CLR IT1

二、 中断服务程序

1、编写中断程序应注意以下几点: ① 为了要跳到用户设计的中断服务程序,在相应入口 地址安排一条跳转指令; ② 在中断服务程序的末尾,安排一条返回指令RETI; ③ 由于在响应中断时,CPU只自动保护断点,所以 CPU的其他现场的保护和恢复也必须由用户在中断服 务程序中安排。

1、T0/T1中断撤除:自动清除TF0 TF1

2、TX/RX中断撤除:不能自动撤除,必须软件清“0” CLR RI CLR TI ANL SCON ,#0FCH

3、外部中断请求的撤除

对于负边沿触发的外部中断,CPU在响应中断后是 用硬件自动清除中断请求标志IE0或IE1。

电平触发时,虽然自动清除中断请求标志IE0或IE1。但 不及时撤除低电平的话会重复响应中断,必须采取措施。

中断允许寄存器IE的单元地址是A8H,各控制位也可 位寻址,故既可以用字节传送指令也可以用位操作指 令来对各个中断请求加以控制。 例:开放T/C1的溢出中断

MOV IE,#88H;

SETB EA SETB ET1

二、 对中断优先级的控制

MCS-51具有两个中断优先级,可由软件设置每个中断 源为高优先级中断或低优先级中断,可实现二级中断 嵌套。

可在中断服务程序开 头安排如下程序: INSVR:ANL P1 ,#0FEHORL Fra bibliotek1,#01H …

RETI END

§4 中断系统的初始化及应用

一、中断系统的初始化 中断初始化是指用户对TCON、SCON、IE等特殊功能 寄存器中的各控制位进行赋值。

中断系统的初始化步骤: 1、 CPU开中断或关中断 2、 某中断源中断请求的允许或禁止(屏蔽) 3、 设定所用中断的中断优先级 4、若为外部中断,则应规定低电平还是负边沿的中断 触发方式

单片机讲义(第五章MCS-51的中断系统)

5.6.2 跳沿触发方式(下降沿触发方式)

如果相继连续两次采样,一个机器周期采样到外部中断输入为高, 下一个机器周期采样为低,则置1中断申请触发器,直到CPU响应此 中断时,该标志才清0。这样不会丢失中断,输入的负脉冲宽度至少保

持12个时钟周期(若晶振频率为6 MHZ,则为2μs),才能被CPU采样到。

(2)用字节操作指令

MOV IP,#05H ;000 00101 或者用: MOV 0B8H,#05H ;B8H为IP寄存器的字节地址

5.5 外部中断的响应时间

从外部中断请求有效(外部中断请求标志置1)到转 向中断入口地址所需要的响应时间。 外部中断的最短响应时间为3个机器周期。其中中断

请求标志位查询占1个机器周期,而这个机器周期恰好是处于指令 的最后一个机器周期,在这个机器周期结束后,中断即被响应, CPU接着执行1条硬件子程序调用指令 LCALL以转到相应的中断服 务程序入口,则需要2个机器周期。

外部中断响应的最长时间为8个机器周期。执行RETI或

是访问IE或IP的指令,最长需要2个机器周期。而接着再执行的1条 指令,按最长的指令(乘法指令MUL和除法指令DIV)来算,需4 个机器周期。再加上硬件子程序调用指令LCALL的执行,需要2个 机器周期,所以,外部中断响应最长时间为8个机器周期。

5.3.3中断允许寄存器IE

IE中各位的功能如下:

(l)EA——中断允许总控制位 EA=0,CPU屏蔽所有的中断请求(CPU关中 断); EA=1,CPU开放所有中断(CPU开中断)。 (2)ES——串行口中断允许位 ES=0,禁止串行口发送/接收中断; ES=1,允许串行口发送/接收中断。 (3) ET1——定时器/计数器T1的溢出中断允许 位 ET1= 0,禁止T1计数溢出中断; ET1= 1,允许T1计数溢出中断。

第5章_MCS-51单片机中断定时器

5.1.4 P3口

P3口第二功能

第二功能状态

15:12

14

返回目录

5.1.4 P3口

P3口使用

P3口使用

P3口的每一位都可独立地定义为第一功能 I/O或第二功能使 用。P3的第二功能涉及到串行口、外部中断、定时器,与 特殊功能寄存器有关,它们的结构、功能等在后面章节中 再作进一步介绍。

P3 口 的 地 址 为 B0H , 对 应 P3.0~P3.7 的位地址为 B0H~B7H。

15:12 15

返回目录

5.1.4 小结

4个并行口使用注意事项

P0、P1、P2、P3并行端口使用注意事项

(1)4个端口的电路结构均不完全相同,并且性能和用途 也各有所侧重; (2)4个口均为“准双向口”,每个并行口都有两种读入 方法:一个是读锁存器,另一个是读取引脚状态; (3)P0口作为I/O口使用时应外接上拉电阻,其它口则可 不必; (4)P2口某几根口线作地址使用时,剩下的口线不能作为 I/O口线使用; (5)P3口的某些口线作第二功能时,剩下的口线可以单独 作为I/O口线使用。

15:12 26

返回目录

5.2.1 CPU与外设的输入/输出方式

2.异步传送方式

异步 传送又称为有条

-----异步传送方式

件传送,或查询方式,

通常 把 通过 程 序 对外 设状 态 的检 测 称 之为 “查 询”, 所 以 这种 有条 件 的传 送 方 式又 叫做 程 序查 询 方 式。 查询 的 流程 图 如 图所 示。

15:12 27

返回目录

5.2.1 CPU与外设的输入/输出方式

3.直接存储器存取(DMA)方式

---DMA方式

DMA ( Direct Memory Access ) 方 式 是

MCS51单片机中断系统

中断程序入口地址

五个中断程序的入口地址为: 五个中断程序的入口地址为: 外中断0 INT0) 外中断0(INT0) :0003H 定时器0 T0) 定时器0(T0) :000BH 外中断1 INT1) 外中断1(INT1) :0013H 定时器1 T1) 定时器1(T1) :001BH 串行口(RI/TI) 串行口(RI/TI) :0023H

可归纳为下面两条基本规则: 可归纳为下面两条基本规则: (1)低优先级可被高优先级中断,反之则不能。 低优先级可被高优先级中断,反之则不能。 (2)同级中断不会被它的同级中断源所中断。 )同级中断不会被它的同级中断源所中断。

CPU正在执行高优先级的中断 正在执行高优先级的中断, 若 CPU 正在执行高优先级的中断 , 则不能被任何中断 源所中断。 源所中断。 中断优先级寄存器IP 其字节地址为B IP, 中断优先级寄存器IP,其字节地址为B8H。

寄存器名称 D7 定时器控制 TCON(88H TF1 寄存器 ) 位地址 8FH 串行口控制 SCON(98H) 寄存器 位地址 9FH 中断允许 IE(A8H) EA 寄存器 位地址 AFH 中断优先级 IP(B8H) 寄存器 位地址 D6 D5 TF0 8DH 9DH D4 D3 IE1 8BH D2 IT1 8AH D1 IE0 89H TI 99H ET0 A9H PT0 B9H D0 IT0 88H RI 98H EX0 A8H PX0 B8H

MCS-51复位后,IE清 MCS-51复位后,IE清0,所有中断请求被禁止。 复位后 所有中断请求被禁止。 若使某一个中断源被允许中断,除了IE IE相应的位的被 若使某一个中断源被允许中断,除了IE相应的位的被 还必须使EA =1。 EA位 置“1” ,还必须使EA位=1。 改变IE的内容,可由位操作指令来实现, IE的内容 改变IE的内容,可由位操作指令来实现,即: bit; SETB bit; bit。 CLR bit。 若允许片内2个定时器/计数器中断, 例5-1 若允许片内2个定时器/计数器中断,禁止其它 中断源的中断请求。编写设置IE IE的相应程序段 中断源的中断请求。编写设置IE的相应程序段 用位操作指令来编写如下程序段: (1)用位操作指令来编写如下程序段: CLR ES ;禁止串行口中断 EX1 禁止外部中断1 CLR EX1 ;禁止外部中断1中断 EX0 禁止外部中断0 CLR EX0 ;禁止外部中断0中断

《单片机原理及基于单片机的嵌入式系统设计》第5章

89C51中断系统的五个中断源

1、INT0——外部中断0请求,低电平有效。通过 P3.2引脚输入。

2、INT1——外部中断1请求,低电平有效。通过 P3.3引脚输入。

3、T0——定时器/计数器0溢出中断请求。 4、T1——定时器/计数器1溢出中断请求。 5、TX/RX——串行口中断请求。当串行口完成一帧 数据的发送或接收时,便请求中断。

5.4 中断程序编程举例

例5.5 假设某消防队坐落在道路的一边,正常情况下,交通红 绿灯以1s的间隔轮流点亮,当有消防任务时,消防官兵只需要 按一下设置在路边的消防紧急按钮,则道路交通灯就会变成红 灯并持续1s时间,禁止其他车辆通行,使消防车可以顺利通过, 试用51单片机来模拟实现上述功能 解:电路如图5-10所示,将P1口的P1.1~P1.0分别接红和 绿色发光二极管D1~D0模拟道路交通等,P3.2(INT0) 引脚接一按键以模拟消防紧急按钮,源程序中DELAY1S为 延时1s子程序。

中断源 外部中断0(INT0) 定时器T0中断 外部中断1(INT1) 定时器T1中断 串行口中断

中断入口地址 0003H 000BH 0013H 001BH 0023H

图5-9 中断源及其对应的中断入口地址

(3)对有些中断源,CPU会自动清除中断标志位。CPU响应 中断后,自动清除中断标志,如TF1、TF0、IE1、IE0,但不 能清除RI、TI、IT1、IT0标志位。 (4)执行中断服务程序。用户设置中断的目的是执行用户中 断服务程序,当由硬件完成清除中断标志位,同时将程序跳转 到中断入口处去执行中断服务程序,但是每个中断向量地址之 间隔了8个单元,如0003-000BH,在如此少的空间中如何完成 用户中断程序呢?很简单,在中断处安排一个LJMP指令,就 可以把中断程序跳转到任何地方。当然如果用户中断程序小于 8字节,则不必安排跳转指令。建议读者即使中断服务程序小 于8字节,也采用跳转指令方式,以便养成规范的编程风格。 (5)中断服务子程序执行完返回指令RETI,中断服务程序结 束,将堆栈内容弹出到PC,返回到原来断点继续执行。

单片机原理与应用 第五章

第五章MCS-51单片机的中断系统5.1 中断系统概述中断:CPU暂时停止正在执行的程序,自动转去执行需紧迫处理的事件(程序),并在处理完毕后能够返回原来程序暂停的位置,接着继续执行。

5.2 中断源和中断控制5.2.1 中断源:能够让CPU暂停执行的信号(硬件)。

8051单片机有5个中断源:2个内部定时器/计数器T0和T1溢出中断:F0和TF1。

2个外部输入INT0(P3.2)和INT1(P3.3)中断:IE0和IE1。

1个串行口发送/接收中断:TI / RI。

1. 定时器/计数器中断控制寄存器TCON (88H)(1) IT0当IT0=0时,为负电平触发方式,即INT0(P3.2脚)为低电平时,置IE0=1。

当IT0=1时,为边沿负跳变触发方式,即INT0从高变为低电平时,置IE0=1。

(2) IE0为外部中断0的触发标志(申请中断):(当INT0的电平变化时由硬件置位)硬件置位IE0=1时,向CPU请求中断。

在CPU响应中断请求后,当IT0=1时,IE0自动清零;而当IT0=0时,IE0不能自动清零。

(3) IT1 为外部中断1的触发方式控制位:(由软件置位)同IT0。

(4) IE1 为外部中断1的触发标志(申请中断):同IE0。

(5) TF0为T0的溢出标志(申请中断):当T0的(TH0、TL0)计满溢出时,硬件置TF0为“1”,并向CPU申请中断。

CPU响应中断后,TF0自动清零。

(6) TF1为T1的溢出标志(申请中断):当T1的(TH1、TL1)计满溢出时,硬件置TF1为“1”,并向CPU申请中断。

CPU响应中断后,TF1自动清零。

2. 串行口控制寄存器SCON (98H)1) TI2) RI:串行口接收中断标志位。

接收完成后RI=1。

5.2.2 中断控制1. 中断允许控制寄存器IE (A8H)1) EA当EA=0时,所有中断都禁止;当EA=1时,所有中断都允许。

2) ES:串行口中断允许控制位当ES=0时,禁止串行口中断;当ES=1时,允许串行口中断。

单片机原理及接口技术(第二版)第五章

主程序就执行一条指令, 实现了单步执行的目的, 要注意的

是, 这个正脉冲的高电平持续时间不小于2个周期, 以确保 CPU能采集到高电平值。

第5章 MCS - 51单片机的中断

外中断的中断服务程序编程总结: 程序框架:在0000H单元放一条长跳转指令到主程 序,绕开中断服务程序入口,在中断服务程序入口放 一条长跳转指令转入中断服务程序。 初始化工作:在主程序开始部分对中断进行初始化 (1)设置中断触发方式(IT0或IT1) (2)置EA=1,开放CPU中断 (3)置EX0=1(或EX1=1),开放外中断 (4)中断优先级控制字写入IP(可选)

第5章 MCS - 51单片机的中断

当上述阻断条件存在时,中断不能被相应,且丢弃 查询结果。若阻断条件结束时,中断标志已经消失,则 这个被拖延了的中断请求可能不会再得到响应。

在单一外部中断的系统里(即不考虑上述阻断条件 中断的第一个条件),外部中断响应时间总是在3~8个 机器周期之间。

第5章 MCS - 51单片机的中断

地址(中断矢量)送入PC, 从而转入相应的中断服 务程序。

第5章 MCS - 51单片机的中断

中断响应过程,相当于执行了一条隐含的调 用指令(或称隐指令)LCALL。 例如当TF0被置1且得到中断响应时,CPU就 自动的执行一条隐指令“LCALL 000BH”。 应当注意,在中断服务子程序的调用过程中, 仅仅保存了PC的信息,其余的现场信息(如寄存 器的值等)都要由编程人员通过软件来进行保护。

第5章 MCS - 51单片机的中断 现在,若INT0保持低电平, 且允许INT0中断, 则CPU就 进入外部中断0服务程序, 由于有上述几条指令, 它就会停

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

自然优先级

中断源 外部中断0 外部中断 定时器T0溢出中断 定时器 溢出中断 外部中断1 外部中断 定时器T1溢出中断 定时器 溢出中断 串行口中断 最低级 同级自然优先级 最高级

14

外部中断触发方式

TCON (88H) D7 TF1 D6 TR1 D5 TF0 D4 TR0 D3 IE1 D2 IT1 D1 IE0 D0 IT0 INT0

10

举例

用字节操作指令或用位操作指 令对IE IE进行初始化设置的方法 令对IE进行初始化设置的方法

例:设允许T0中断和外部中断 中断,禁止其它中断 设允许 中断和外部中断0中断, 中断和外部中断 中断 用位操作指令编程如下: ★ 用位操作指令编程如下: 允许T0 T0中断 SETB ET0 ;允许T0中断 允许INT0 INT0中断 SETB EX0 ;允许INT0中断 SETB EA ;开总开关 用字节操作指令编程如下: ★ 用字节操作指令编程如下:

IT0=1时 下降沿触发,CPU响应中断 硬件自动清IE0=0 响应中断, ★ IT0=1时,下降沿触发,CPU响应中断,硬件自动清IE0=0 IT0=0时 低电平触发,CPU响应中断不会自动清除IE0标志位 响应中断不会自动清除IE0标志位, ★ IT0=0时,低电平触发,CPU响应中断不会自动清除IE0标志位, 必须撤消INT0引脚上的低电平信号,即使INT0=1 才能使IE0=0 INT0引脚上的低电平信号 INT0=1, IE0=0。 必须撤消INT0引脚上的低电平信号,即使INT0=1,才能使IE0=0。 相当于有硬件连接的: 相当于有硬件连接的: INT0 IE0 1 15

5

三、中断标志位

每个中断源都有一个对应的中断标志位, 每个中断源都有一个对应的中断标志位,中断标志 位在两个特殊功能寄存器中 TCON——定时器控制寄存器,存放有4个标志位 定时器控制寄存器,存放有 个标志位 定时器控制寄存器 SCON——串行口控制寄存器,存放有2个标志位 串行口控制寄存器,存放有2 串行口控制寄存器

中断源

3、定时器0溢出中断--T0 定时器0溢出中断--T0 -是内部中断,无外部输入。定时器T0溢出, T0溢出 是内部中断,无外部输入。定时器T0溢出,使标志 TF0置 CPU申请中断 申请中断。 位TF0置1,向CPU申请中断。 4、定时器1溢出中断—T1 定时器1溢出中断 T1 T0类似 T1溢出 TF1置 类似, 溢出, CPU申请中断 申请中断。 与T0类似,T1溢出,TF1置1,向CPU申请中断。 串行口中断—S 5、串行口中断 S 当串行口接收完一帧数据,中断标志位RI RI置 当串行口接收完一帧数据,中断标志位RI置1 当串行口发送完一帧数据,中断标志位TI TI置 当串行口发送完一帧数据,中断标志位TI置1

8

§5-2 中断控制

中断是可控的, 中断是可控的,由软件设置实现对中断功能的控制 IE——中断允许寄存器,用于中断的开放或禁止 中断允许寄存器, 中断允许寄存器 IP——中断优先级寄存器,用于中断响应优先管理 中断优先级寄存器, IP 中断优先级寄存器

1、中断允许寄存器IE 中断允许寄存器IE

Enable,为一8位寄存器,地址为A8H Interrupt Enable,为一8位寄存器,地址为A8H

IP (B8H) 管理原 则 D7 D6 D5 D4 PS S D3 PT1 T1 D2 PX1 INT1 D1 PT0 T0 D0 PX0 INT0

★ 高优先级中断源可中断正在执行的低优先级中断 ★ 同级或低优先级中断不能中断正在执行的中断

12中断Biblioteka 套主 程 序 断点 返回 返回 转移 转移 程 序

INT1 ---Interrupt Trigger, ITX---Interrupt Trigger,外部中断触发方式控制位 外部中断有两种触发方式,通过设置 实现。 外部中断有两种触发方式,通过设置IT0、IT1实现。 、 实现 设置IT0=0时——电平触发方式,低电平有效。 时 电平触发方式, 设置 电平触发方式 低电平有效。 设置IT0=1时——为边沿触发方式,下降沿有效。 时 为边沿触发方式, 设置 为边沿触发方式 下降沿有效。

返回

2、SCON中的中断标志位 中的中断标志位

Control,为 位特殊功能寄存器,地址为98H Serial Control,为8位特殊功能寄存器,地址为98H 与中断有关的为低两位

SCON (98H) D7 D6 D5 D4 D3 D2 D1 TI D0 RI

1)TI—串行口发送中断标志位 TI 串行口发送中断标志位,Transfer Interrupt 串行口发送中断标志位 CPU发送完一帧数据 硬件置位TI=1 响应中断, 发送完一帧数据, TI=1, CPU发送完一帧数据,硬件置位TI=1,响应中断,不 能硬件自动清TF1=0 必须用软件清0 TF1=0, 能硬件自动清TF1=0,必须用软件清0。 RI—串行口接收中断标志位 串行口接收中断标志位, 2)RI 串行口接收中断标志位,Receive Interrupt CPU接收完一帧数据 硬件置位RI=1 必须用软件清0 接收完一帧数据, RI=1, CPU接收完一帧数据,硬件置位RI=1,必须用软件清0

IE (A8H) D7 EA 总控位 D6 D5 D4 ES S D3 ET1 T1 D2 EX1 INT1 D1 ET0 T0 D0 EX0 INT0

9

IE (A8H)

D7 EA

D6

D5

D4 ES

D3 ET1

D2 EX1

D1 ET0

D0 EX0

EA---Enable Amount,中断总允许位 EA---Enable Amount, --EA=1,CPU开中断 EA=0,关中断, 开中断; EA=1,CPU开中断;EA=0,关中断,禁止所有中断 ES-----Enable Serial, ES---Enable Serial,串行口中断允许位 ES=1,允许串行口中断;ES=0, ES=1,允许串行口中断;ES=0,禁止串行口中断 ET1-----Enable Timer1,定时器T1 T1溢出中断允许位 ET1---Enable Timer1,定时器T1溢出中断允许位 ET1=1,允许T1中断; ET1=0,禁止T1 T1中断 T1中断 ET1=1,允许T1中断; ET1=0,禁止T1中断 EX1-----Enable eXternal,外部中断1 EX1---Enable eXternal,外部中断1中断允许位 EX1=1,允许外部中断1中断;EX1=0, EX1=1,允许外部中断1中断;EX1=0,禁止 ET0-----Enable Timer0,定时器T0中断允许位,类似ET1 T0中断允许位 ET0---Enable Timer0,定时器T0中断允许位,类似ET1 EX0-----Enable eXternal0,外部中断0允许位,类似EX1 EX0---Enable eXternal0,外部中断0允许位,类似EX1

中断及中断源 中断控制 中断响应过程 中断程序设计

1

§5-1 中断及中断源

一、中断(Interrupt)

1、CPU在执行程序时,CPU以外的设备请求停止现程序 CPU在执行程序时,CPU以外的设备请求停止现程序 在执行程序时 的执行,转去处理外设事件,处理后再回到原地执行, 的执行,转去处理外设事件,处理后再回到原地执行, 这一过程叫中断。 这一过程叫中断。 主

程 序 断 继 续 转

、中断

程

中 断 程 序 回

程序 的

2

注意

中断与子程序调用的不同点

子程序调用是固定的 专用指令,位置固定。 固定的, ● 子程序调用是固定的,专用指令,位置固定。 中断的执行是随机的,没有调用指令,任何位置。 ● 中断的执行是随机的,没有调用指令,任何位置。 随机的 3、中断工作方式的优点: 中断工作方式的优点: 优点 1)外设与CPU可并行工作 外设与CPU可并行工作 CPU CPU与多个外设同时工作, CPU与多个外设同时工作,互不干扰 与多个外设同时工作 2)实现了实时处理、实时控制 实现了实时处理、 CPU能及时处理外部信息,如数据采集,监控 CPU能及时处理外部信息,如数据采集, 能及时处理外部信息 3)能及时处理随机故障

EA 1 0 0 ES 0 ET1 0 EX1 0 ET0 1 EX0 1 = 83H

MOV IE,#83H 或 , MOV IE,#10000011B ,

11

Interrupt Preference

2、中断优先级寄存器IP 中断优先级寄存器IP

IP为一8位特殊功能寄存器,地址为B8H IP为一8位特殊功能寄存器,地址为B8H 为一 每个中断源均可设置为高优先级或低优先级: 每个中断源均可设置为高优先级或低优先级: 设置为1时 设置为 时,该中断源为高优先级 设置为0时,该中断源为低优先级 设置为 时

1、TCON中的中断标志位 中的中断标志位

Timer Control,为8位特殊功能寄存器,地址88H Control,为 位特殊功能寄存器,地址88H ● 用4位放定时器T0、T1,外部中断INT0、INT1的 位放定时器T0 T1,外部中断INT0 INT1的 T0、 INT0、 中断标志位。 中断标志位。 ● TCON用来控制定时器的启/停和外部中断管理。 TCON用来控制定时器的启 停和外部中断管理。 用来控制定时器的启/ ● TCON可读可写,可位操作。 TCON可读可写 可位操作。 可读可写,

3

二、中断源

CPU提出中断请求的设备或部件叫中断源 ● 向CPU提出中断请求的设备或部件叫中断源 来源有输入输出设备、实时时钟、硬件故障等。 ● 来源有输入输出设备、实时时钟、硬件故障等。 MCS-51有 种类型的中断源: MCS-51有5种类型的中断源: 外部中断2个——INT0、INT1 外部中断 个 、 内部中断3 定时器溢出中断, 内部中断3个——定时器溢出中断,串行口中断 定时器溢出中断 外部中断0--INT0(P3.2) INT0 1、外部中断0--INT0(P3.2) P3.2引脚输入 一旦输入有效中断信号, 引脚输入, 由P3.2引脚输入,一旦输入有效中断信号,便使标 志位IE0 IE0置 并向CPU申请中断。 CPU申请中断 志位IE0置1,并向CPU申请中断。 外部中断1 INT1 P3.3) INT1( 2、外部中断1—INT1(P3.3) 4 INT0类似 P3.3有中断信号 IE1置 类似, 有中断信号, 申请中断。 与INT0类似,P3.3有中断信号,IE1置1,申请中断。