微机接口与原理技术第5章习题及参考解答

微机原理与接口技术第五章试题及答案

第五章5-1选择题1、6264芯片是(B)(A)EEPROM (B)RAM(C)FLASH ROM (D)EPROM2、用MCS-51用串行扩展并行I/O口时,串行接口工作方式选择(A)(A)方式0 (B)方式1 (C)方式2 (D)方式33、使用8255可以扩展出的I/O口线是(B)(A)16根(B)24根(C)22根(D)32根4、当8031外出扩程序存储器8KB时,需使用EPROM 2716(C)(A)2片(B)3片(C)4片(D)5片5、某种存储器芯片是8KB*4/片,那么它的地址线根线是(C)(A)11根(B)12根(C)13根(D)14根6、MCS-51外扩ROM,RAM和I/O口时,它的数据总线是(A)(A)P0 (B)P1 (C)P2 (D)P37、当使用快速外部设备时,最好使用的输入/输出方式是(C)(A)中断(B)条件传送(C)DMA (D)无条件传送8、MCS-51的中断源全部编程为同级时,优先级最高的是(D)(A)INT1 (B)TI (C)串行接口(D)INT09、MCS-51的并行I/O口信息有两种读取方法:一种是读引脚,还有一种是(A)(A)读锁存器具(B)读数据库(C)读A累加器具(D)读CPU 10、MCS-51的并行I/O口读-改-写操作,是针对该口的(D)(A)引脚(B)片选信号(C)地址线(D)内部锁存器5-2判断题1、MCS-51外扩I/O口与外RAM是统一编址的。

(对)2、使用8751且EA=1时,仍可外扩64KB的程序存储器。

(错)60KB3、8155的复位引脚可与89C51的复位引脚直接相连。

(对)4、片内RAM与外部设备统一编址时,需要专门的输入/输出指令。

(错)统一编址的特点正是无需专门的输入输出指令。

5、8031片内有程序存储器和数据存储器。

(错)无程序存储器6、EPROM的地址线为11条时,能访问的存储空间有4K。

(错)2K.7、8255A内部有3个8位并行口,即A口,B口,C口。

《微机原理与接口技术》—习题及参考答案

3.

4. 5.

6.错误!未指定书签。集源自-4-编者:喻其山

7. 8. 9.

8086CPU 工作在最大模式时,S 2 、 S1 、 S 0 在 CPU 访问存储器与 CPU 访问外 部设备时,分别是什么状态? 在 8086 最大模式系统中,8288 总线控制器的作用是什么?它产生哪些控制 信号? FFFFF FFFFE 8086 采用什么方式管理内存?1MB 的内存空 间分为哪两个存储体?它们如何与地址总线、 数据总线相连? 答:(1)、8086 采用分段方式管理内存; (2)、 1MB 的内存空间分为偶地址和奇地址 两个存储体; A19~A1 (3)、如右图所示:

错误!未指定书签。集

-

1

-

编者:喻其山

第1章

1.

微型计算机概述

冯· 诺依曼计算机的结构特点是什么? 答:(1)、由运算器、控制器、存储器、输入设备和输出设备五大部分组成。 (2)、数据和程序以二进制代码形式不加区别地存放在存储器中,存放位 置由地址指定,地址码也为二进制。 (3)、控制器是根据存放在存储器中的指令序列及程序来工作的,并由一 个程序计数器(即指令地址计数器)控制指令的执行。控制器具有 判断能力,能以计算结果为基础,选择不同的动作流程。 微处理器内部一般由哪些部分组成?各部分的主要功能是什么? 典型微机有哪三大总线?它们传送的是什么信息? 答:(1)、有数据总线,地址总线和控制总线。 (2)、数据总线用来传输数据信息,是双向总线; 地址总线用于传送 CPU 发出的地址信息,是单向总线; 控制总线用来传送控制信号、时序信号和状态信息等。 其中有的是 CPU 向内存和外设发出的信息,有的则是内存或外设向 CPU 发出的信息。 可见,CB 中每一根线的方向是一定的、单向的,但 CB 作为一个整体是双 向的。 试用示意图说明内存单元的地址和内存单元的内容,二者有何联系和区别? 答:示意图如右所示: 联系:存储单元中存放着信息,该信 息可以是数据, 也可以是另一单元的地址 的一部分, 每个存储单元都包含着地址和 内容两个部分。都用二进制数表示,地址 为无符号整数,书写格式为 16 进制。 区别: 地址是微机用来管理内存单元 而设置的,相当于内存单元的编号;而内 容是存放在各个内存单元中的二进制信 息。

微机原理与接口技术第五章习题解答

微机原理与接口技术(楼顺天第二版)习题解答第5章总线及其形成5.1 微处理器的外部结构表现为数量有限的输入输出引脚,它们构成了微处理器级总线。

5.2 微处理器级总线经过形成电路之后形成了系统级总线。

5.3 答:总线是计算机系统中模块(或子系统)之间传输数据、地址与控制信号的公共通道,它是一组公用导线,是计算机系统的重要组成部分。

采用标准化总线的优点是:①简化软、硬件设计。

②简化系统结构。

③易于系统扩展。

④便于系统更新。

⑤便于调试与维修。

5.4 答:在微型计算机应用系统中,按功能层次可以把总线分成:片内总线、元件级总线、系统总线与通信总线。

5.5 答:RESET为系统复位信号,高电平有效,其有效信号至少要保持四个时钟周期,且复位信号上升沿要与CLK下降沿同步。

系统复位后的启动地址为0FFFF0H。

即:(CS)=0FFFFH,(IP)=0000H。

5.6 8086CPU复用的引脚有AD15~AD0、A16/S3、A17/S4、A18/S5、A19/S6、BHE/S7。

8088CPU复用的引脚有AD7~AD0、A16/S3、A17/S4、A18/S5、A19/S6、BHE/S7。

5.7 答:设置引脚复用主要是可以减少引脚数量。

CPU通过分时复用解决地址线与数据线的复用问题。

ALE为地址锁存使能信号在总线周期的T1周期有效,BHE为高8位数据线允许,在T1周期有效,需要锁存器锁存,在需要使用高8位数据线时使用。

5.8 答:高阻态可做开路理解。

可以把它看作输出(输入)电阻非常大。

5.9 答:RESET(Reset):复位信号,输入,高电平有效。

CPU 收到复位信号后,停止现行操作,并初始化段寄存器DS、SS、ES,标志寄存器PSW,指令指针IP与指令队列,而使CS=FFFFH。

RESET信号至少保持4个时钟周期以上的高电平,当它变成低电平时,CPU执行重启动过程,8086/8088将从地址FFFF0H开始执行指令。

微机原理与接口技术 第5章课后作业答案

4

D0~ D7 8088系统 BUS

D0~ D7 · · · A0 SRAM 6116

A0 A 10

MEMW

A 10

R/W OE D0~ D7 CS

MEMR

D0~ D7 A0 · · ·

A0 A 10 R/W OE CS

A 10

MEMW MEMR & A 18 A 17 A 19 A 16 A 15 A 14 A 13 A 12 A 11

5.10 74LS138译码器的接线图如教材第245页的图5-47所示,试判断其输出端Y0#、Y3#、Y5#和 Y7#所决定的内存地址范围。

解:因为是部分地址译码(A17不参加译码),故每个译码输出对应2个地址范围: Y0#:00000H ~ 01FFFH 和 20000H ~ 21FFFH Y3#:06000H ~ 07FFFH 和 26000H ~ 27FFFH

5.2 为什么动态RAM需要定时刷新?

解:DRAM的存储元以电容来存储信息,由于存在漏电现象,电容中存储的电荷会逐渐泄漏,从而使信息丢失或出 现错误。因此需要对这些电容定时进行“刷新”。 5.3 CPU寻址内存的能力最基本的因素取决于___________。 解:地址总线的宽度。 5.4 试利用全地址译码将6264芯片接到8088系统总线上,使其所占地址范围为32000H~33FFFH。 解:将地址范围展开成二进制形式如下图所示。 0011 0010 0000 0000 0000 0011 0011 1111 1111 1111

解:

(1)特点是:它结合了RAM和ROM的优点,读写速度接近于RAM,断电后信息又不会丢失。 (2)28F040的编程过程详见教材第222~223页。 5.14 什么是Cache?它能够极大地提高计算机的处理能力是基于什么原理? 解: (1)Cache 是位于CPU与主存之间的高速小容量存储器。 (2)它能够极大地提高计算机的处理能力,是基于程序和数据访问的局部性原理。 5.15 若主存DRAM的的存取周期为70ns,Cache的存取周期为5ns,有它们构成的存储器的平 均存取周期是多少? 解:平均存取周期约为 70×0.1ns + 5×0.9ns =11.5ns。

微机原理及接口技术试题第五章 习题和答案

第五章习题和答案一、单选题1.计算机的外围设备是指____A__。

A、输入/输出设备B、外存储器C、远程通信设备D、除了CPU和内存以外的其他设备2.下述I/O控制方式中,___C___主要由硬件实现。

A、程序传送方式B、中断方式C、DMA方式D、I/O处理机方式3.接口电路的最基本功能是____C__。

A、在CPU和外设间提供双向的数据传送B、反映外设当前的工作状态C、对传送数据提供缓冲功能D、对外设进行中断管理4.一个完整的DMA操作过程大致可分3个阶段,其中没有的阶段是___B___。

A、准备阶段B、总线控制阶段C、数据传送阶段D、传送结束阶段二、判断题1.把接口电路中CPU可以访问的每一个寄存器或控制电路称为一个I/O端口。

(T )2.采用统一编址方式时,CPU对I/O设备的管理是用访问内存的指令实现的。

(T )3.无条件传送是一种最简单的输入/输出传送,一般只用于简单、低速的外设的操作。

(T )4.中断方式的特点是改CPU的被动查询为主动响应。

(F )5.DMA控制器是一个特殊的接口部件,它有主、从两种工作状态。

(T )三、思考题1.外设为何必须通过接口与主机相连?存储器与系统总线相连需要接口吗?为什么?答: 外设都必须通过I/O接口电路与微机系统总线相连,因为CPU与外部设备通信在运行速度和数据格式上差异很大. 存储器与系统总线相连不需要接口.因为接口是用来连接微机和外设的一个中间部件,I/O接口电路要面对主机和外设两个方面进行协调和缓冲,存储器属于微机系统的组成部分.它们之间的数据传输是标准的、统一的没有必要通过接口.2.CPU与外设间传送的信号有哪几类?答: CPU与外设间传送的信息大致可分为以下3类: 数据信息(分为数字量,模拟量和开关量), 控制信息(CPU发出的用来控制外设工作的命令)和状态信息(用来反映输入、输出设备当前工作状态的信号).3. 常用的I/O端口编址方式有哪几种?各自的特点如何?答: 系统对I/O端口的地址分配有两种编址方式:统一编址和独立编址。

微型计算机原理与接口技术课后习题参考答案

《微型计算机原理与接口技术》习题与思考答案第1章微型计算机概论1.1 A B C 1.2 B 1.3 B 1.4 C 1.5 A B C 1.6 B D1.7 00000111B=7D=07H 11010100B=212D=D4H01101010B=106D=6AH 10110.101B=22.625D=16.AH11001.011B=25.375D=19.6H1.8 127D=11111111B=FFH 12.625D=1100.101B=C.AH225.9375D=11100001.1111B=E1.FH 18.3l25D=10010.0101B=12.5H206.125=11001110.001B=CE.2H1.9 10H=10000B=16D 0.A8H=0.10101B=0.65625D28.9H=101000.1001B=40.5625D 4B.2AH=1001011.0010101B=75.6762D20E.4H=1000001110.01B=526.25D1.10 [+37]原=00100101B [+37]反=00100101B [+37]补=00100101B [+37]过余=10100101B[+94]原=01011110B [+94]反=01011110B [+94]补=01011110B [+94]过余=11011110B [-11]原=10001011B [-11]反=11110100B [-11]补=11110101B [-11]过余=01110101B [-125]原=11111101B [-125]反=10000010B [-125]补=10000011B [-125]过余=00000011B1.11补码00010101B的真值为+21D 补码41H的真值为+65D补码9BH的真值为-101D 补码FFH的真值为-1D补码11110101B的真值为-11D1.12 A的ASCII码为41H a的ASCII码为61Hg的ASCII码为67H z的ASCII码为7AH0的ASCII码为30H 9的ASCII码为39H*的ASCII码为2AH +的ASCII码为2BHCR的ASCII码为0DH %的ASCII码为25H1.12一个16×16字形点阵占用存储空间32B一个24×24字形点阵占用存储空间72B一个32×32字形点阵占用存储空间128B1.14 (以8位补码为例)[X]补+[Y]补=[+38]补+[+100]补=0001010B,溢出[X]补+[Z]补=[+38]补+[-20]补=00010010B,未溢出[Y]补- [Z]补=[+100]补- [-20]补=01111000B,未溢出[Z]补- [X]补=[-20]补- [+38]补=11000110B,未溢出1.15 X与Y=0100B X或Z=1111B Y异或Z=1101B 非Y=1001B1.16微型计算机具有体积小、重量轻、功耗低;功能强;可靠性高;价格低廉;结构灵活、适应性强;使用方便、维护容易等特点。

《微机接口与原理技术》第5章习题及参考解答

《微机接口与原理技术》第5章习题及参考解答1.计算机的存储器采用分级存储体系的主要目的是(A.便于读写数据B.减小机箱的体积C.便于系统升级D.解决存储容量、价格和存取速度之间的矛盾解D2.在多级存储体系中,Cache─主存结构的作用是解决(问题。

A.主存容量不足B.主存与辅存速度不匹配C.辅存与CPU速度不匹配D.主存与CPU速度不匹配解D3.下列因素中,与Cache的命中率无关的是(A.主存的存取时间B.块的大小C.Cache的组织方式D.Cache的容量解A4.下列说法中不正确的是(A.每个程序的虚地址空间可以远大于实地址空间,也可以远小于实地址空间B.多级存储体系由Cache、主存和虚拟存储器构成C.Cache和虚拟存储器这两种存储器管理策略都利用了程序的局部性原理D.当Cache未命中时,CPU可以直接访问主存,而外存与CPU之间则没有直接通路解B5.下列说法中正确的是(A.虚拟存储器技术提高了计算机的速度B.Cache与主存统一编址,Cache的地址空间是主存地址空间的一部分C.主存都是由易失性的随机读写存储器构成的D.Cache的功能全部由硬件实现解D6.在Cache的地址映射中,若主存中的任意一页均可映射到Cache内的任意一页的位置上,则这种方法称为(A.全相联映射B.直接映射C.组相联映射D.混合映射解A7.在计算机系统中,下列部件都能够存储信息:①主存;②CPU内的通用寄存器;③Cachc;④磁带;⑤磁盘。

按照CPU存取速度排列,由快至慢依次为(其中,内存包括(;属于外存的是(;由半导体材料构成的是(解从快到慢依次为(②、③、①、⑤、④。

其中,内存包括(①和③;属于外存的是(④和⑤;由半导体材料构成的是(①、②、③。

8.什么是SRAM,DRAM,ROM,PROM,EPROM和FLASH解易失性半导体存储器统称为RAM,它分为静态RAM(SRAM和动态RAM(DRAM,用于在程序中保存需要动态改变的数据,或是需要动态加载的程序。

微机原理与接口技术第五章、第六章课后习题答案

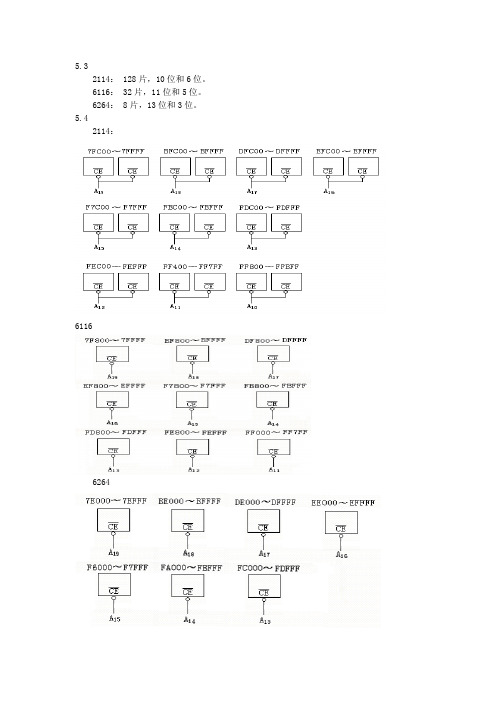

2114: 128片,10位和6位。

6116: 32片,11位和5位。

6264: 8片,13位和3位。

5.42114:611662646.4stack segment stack 'stack'dw 32 dup(0)stack endscode segmentstart proc farassume ss: stack, cs: codepush dssub ax, axpush axCALL I6116 ;调用写入6116子程序MOV AH, 2 ;回车换行MOV DL, 0DHINT 21HMOV DL, 0AHINT 21HCALL O6116 ;调用读出6116子程序ret;写入6116:将键入字符的ASCII码写入6116I6116 PROCMOV BL, 0 ;定义页地址码(16个地址为一页)MOV CX, 128 ;定义页数LOP1: PUSH CXMOV DX, 380H ;将页地址从74LS273输出MOV AL, BLOUT DX, ALMOV CX, 16 ;定义页内单元数MOV DX, 390H ;将键入数写入16个单元LOP2: MOV AH, 1INT 21HOUT DX, ALINC DXLOOP LOP2INC BL ;换页POP CXLOOP LOP1 ;页数未满换页重新写入16个单元RETI6116 ENDP;读出6116:将写入6116的数据读出送显示O6116 PROCMOV BL, 0MOV CX, 128LOP3 PUSH CXMOV DX, 390HMOV AL, BLOUT DX, ALMOV CX, 16MOV DX 380H ;将16个单元的数据送显示LOP4: IN AL, DXPUSH DXMOV DL, AL ;将6116中读出的ASCII码送DLMOV AH, 2 ;2号功能调用显示DL中的字符INT 21HPOP DXINC DXLOOP LOP4INC BLPOP CXLOOP LOP3RETO6116 ENDPend start6.5stack segment stack 'stack'dw 32 dup(0)stack endscode segmentstart proc farassume ss: stack, cs: codepush dssub ax, axpush axMOV AH, 2 ;用2号功能调用输出字符,调用号送AHMOV CX, 100 ;字符个数送计数器MOV DX, 380HWAIT0: IN AL, DX ;从244读入TEST AL, 80H ;测试状态位是否为0JNZ WAIT0 ;不为0,等待继续测试状态WAIT1: IN AL, DX ;状态为0,继续读入TEST AL, 80H ;测试状态是否为1JZ WAIT1 ;不为1,等待继续测试状态IN AL, DX ;状态为1,读入数据即ASCII码AND AL, 7FH ;去掉状态位MOV DL, AL ;ASCII码送DL,输出字符INT 21HLOOP WAIT0-3 ;跳到给DX赋值380H的MOV指令,该指令为3字节retstart endpcode endsend start。

微型计算机原理与接口技术第五课后答案

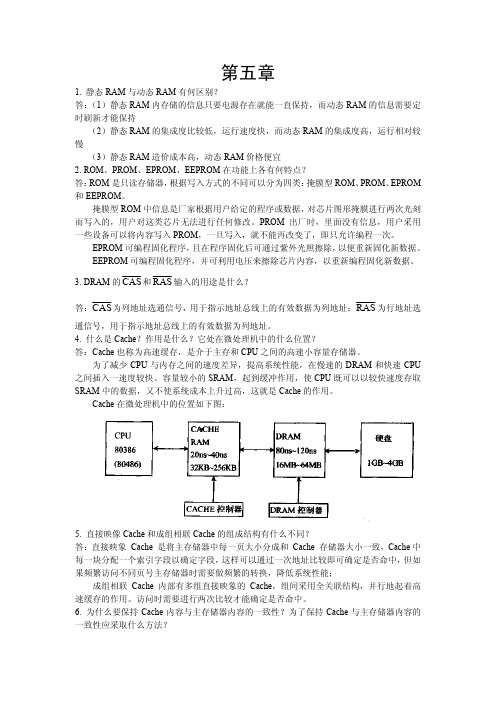

第五章1. 静态RAM 与动态RAM 有何区别?答:(1)静态RAM 内存储的信息只要电源存在就能一直保持,而动态RAM 的信息需要定时刷新才能保持(2)静态RAM 的集成度比较低,运行速度快,而动态RAM 的集成度高,运行相对较慢(3)静态RAM 造价成本高,动态RAM 价格便宜2. ROM 、PROM 、EPROM 、EEPROM 在功能上各有何特点?答:ROM 是只读存储器,根据写入方式的不同可以分为四类:掩膜型ROM 、PROM 、EPROM 和EEPROM 。

掩膜型ROM 中信息是厂家根据用户给定的程序或数据,对芯片图形掩膜进行两次光刻而写入的,用户对这类芯片无法进行任何修改。

PROM 出厂时,里面没有信息,用户采用一些设备可以将内容写入PROM ,一旦写入,就不能再改变了,即只允许编程一次。

EPROM 可编程固化程序,且在程序固化后可通过紫外光照擦除,以便重新固化新数据。

EEPROM 可编程固化程序,并可利用电压来擦除芯片内容,以重新编程固化新数据。

3. DRAM 的CAS 和RAS 输入的用途是什么? 答:CAS 为列地址选通信号,用于指示地址总线上的有效数据为列地址;RA 行地址选通信号,用于指示地址总线上的有效数据为列地址。

S 为4. 什么是Cache ?作用是什么?它处在微处理机中的什么位置?答:Cache 也称为高速缓存,是介于主存和CPU 之间的高速小容量存储器。

为了减少CPU 与内存之间的速度差异,提高系统性能,在慢速的DRAM 和快速CPU 之间插入一速度较快、容量较小的SRAM ,起到缓冲作用,使CPU 既可以以较快速度存取SRAM 中的数据,又不使系统成本上升过高,这就是Cache 的作用。

Cache 在微处理机中的位置如下图:5. 直接映像Cache 和成组相联Cache 的组成结构有什么不同?答:直接映象 Cache 是将主存储器中每一页大小分成和 Cache 存储器大小一致,Cache 中每一块分配一个索引字段以确定字段,这样可以通过一次地址比较即可确定是否命中,但如果频繁访问不同页号主存储器时需要做频繁的转换,降低系统性能;成组相联Cache 内部有多组直接映象的 Cache ,组间采用全关联结构,并行地起着高速缓存的作用。

微机原理与接口技术张颖超叶彦斐第5章习题答案

微机原理与接⼝技术张颖超叶彦斐第5章习题答案5.1 RAM 和ROM 的主要特点和区别是什么?【解答:】ROM (只读性存储器)的特点是在⼀般情况下,ROM 中的信息只能读出不能写⼊,ROM 中的内容是⾮易失性的,掉电后信息也不会丢失。

RAM (随机存储器)的特点是其内容在⼯作时既可以读出也可以随时写⼊,但是其中的内容是易失性的,掉电后信息会丢失。

5.2术语“⾮易失性存储器”是什么意思?PROM 和EPROM 分别代表什么意思?【解答:】“⾮易失性存储器”是指掉电后信息不会丢失。

PROM 是可编程ROM ,EPROM 可擦除可编程ROM 。

5.3 何谓静态RAM ?何谓动态RAM ?他们的特点各是什么?【解答:】以双稳态电路作为基本存储单元来保存信息的RAM 称为静态RAM (SRAM ),其特点是:只要不断电,信息不会丢失;访问速度快,但集成度较低,⼀般⽤于Cache 采⽤SRAM 。

以晶体管栅极电容的充放电来存储⼆进制信息的RAM 称为动态RAM ,其特点是:电容上的电荷会随时间⽽泄露,因此DRAM 需要定时刷新;DRAM 集成度较⾼,因此⾏列地址线复⽤,⼀般内存采⽤DRAM 构成。

5.4 较⼤容量的RAM 为什么总是采⽤矩阵形式?【解答:】这种形式便于采⽤双译码结构,地址线分为⾏、列两部分,分开译码,可以极⼤的减少地址译码器的输出线,简化电路。

5.5 下列RAM 芯⽚各需要多少个地址引脚?(1)16K×1b (2)1K×4b (3)2K×8b 【解答:】分别是2log 16K 14=,2log 1K 10=,2log 2K 11=根5.6 设有⼀个具有14位地址和8位字长的存储器,问:(1)该存储器能存储多少字节的信息?(2)如果存储器由1K×1b 静态RAM 芯⽚组成,需多少芯⽚?(3)需要多少位地址作芯⽚选择?(4)改⽤4K×4b 的芯⽚,试画出与总线连接框图。

微机原理与接口技术 第五章 课后答案

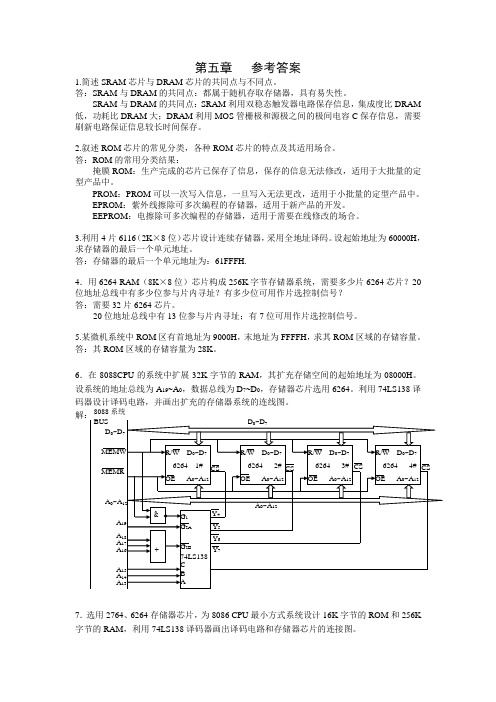

第五章参考答案1.简述SRAM芯片与DRAM芯片的共同点与不同点。

答:SRAM与DRAM的共同点:都属于随机存取存储器,具有易失性。

SRAM与DRAM的共同点:SRAM利用双稳态触发器电路保存信息,集成度比DRAM 低,功耗比DRAM大;DRAM利用MOS管栅极和源极之间的极间电容C保存信息,需要刷新电路保证信息较长时间保存。

2.叙述ROM芯片的常见分类,各种ROM芯片的特点及其适用场合。

答:ROM的常用分类结果:掩膜ROM:生产完成的芯片已保存了信息,保存的信息无法修改,适用于大批量的定型产品中。

PROM:PROM可以一次写入信息,一旦写入无法更改,适用于小批量的定型产品中。

EPROM:紫外线擦除可多次编程的存储器,适用于新产品的开发。

EEPROM:电擦除可多次编程的存储器,适用于需要在线修改的场合。

3.利用4片6116(2K×8位)芯片设计连续存储器,采用全地址译码。

设起始地址为60000H,求存储器的最后一个单元地址。

答:存储器的最后一个单元地址为:61FFFH.4.用6264 RAM(8K×8位)芯片构成256K字节存储器系统,需要多少片6264芯片?20位地址总线中有多少位参与片内寻址?有多少位可用作片选控制信号?答:需要32片6264芯片。

20位地址总线中有13位参与片内寻址;有7位可用作片选控制信号。

5.某微机系统中ROM区有首地址为9000H,末地址为FFFFH,求其ROM区域的存储容量。

答:其ROM区域的存储容量为28K。

6.在8088CPU的系统中扩展32K字节的RAM,其扩充存储空间的起始地址为08000H。

设系统的地址总线为A19~A0,数据总线为D7~D0,存储器芯片选用6264。

利用74LS138译码器设计译码电路,并画出扩充的存储器系统的连线图。

8088系统解:7.选用2764、6264存储器芯片,为8086 CPU最小方式系统设计16K字节的ROM和256K 字节的RAM,利用74LS138译码器画出译码电路和存储器芯片的连接图。

微型计算机原理与接口技术课后习题答案

数据结构与算法的关系

数据结构与算法是相辅相成的,数据结构的选择会影响算法的 效率和实现方式,而算法的选择也会影响数据结构的组织形式 和使用方式。

04 微型计算机应用与开发

Байду номын сангаас 应用软件与开发工具

计算机工作原理

总结词

计算机的工作原理基于二进制数的运算,通过存储器、运算器和控制器等部件的协同工 作,实现数据的处理和传输。

详细描述

计算机的工作原理基于二进制数的运算,通过存储器、运算器和控制器等部件的协同工 作,实现数据的处理和传输。在计算机内部,数据以二进制数的形式表示和处理,运算 器根据控制器的指令对数据进行运算,并将结果存储回存储器中。输入输出设备则负责

第2章习题答案

选择题

答案

简答题

答案

在计算机中,数据是以什么 形式存储的?

在计算机中,数据是以二进 制形式存储的。

简述计算机中存储器的分类 及其特点。

计算机中存储器可以分为随 机存取存储器(RAM)、只 读存储器(ROM)和高速缓 存存储器(Cache)等。 RAM的特点是可以随时读写, 但断电后数据会丢失;ROM 的特点是只能读取不能写入, 但数据不会因断电而丢失; Cache的特点是读写速度快, 可以暂存部分数据,提高 CPU的访问速度。

接口

接口是连接设备和总线的桥梁,负 责数据的传输和控制。

性能指标

总线的带宽和传输速率是衡量其性 能的重要指标。

04

03 微型计算机软件技术

操作系统

操作系统定义

操作系统是控制计算机硬件与软件资源、管理计算机程序的软件, 是计算机系统的核心组成部分。

微机原理及接口技术课后习题及参考答案

第一章课后习题1.1 把下列十进制数转换成二进制数、八进制数、十六进制数。

① 16.25 ② 35.75 ③ 123.875 ④ 97/1281.2 把下列二进制数转换成十进制数。

① 10101.01 ② 11001.0011 ③ 111.01 ④ 1010.11.3 把下列八进制数转换成十进制数和二进制数。

① 756.07 ② 63.73 ③ 35.6 ④ 323.451.4 把下列十六进制数转换成十进制数。

① A7.8 ② 9AD.BD ③ B7C.8D ④ 1EC1.5 求下列带符号十进制数的8位补码。

① +127 ② -1 ③ -0 ④ -1281.6 求下列带符号十进制数的16位补码。

① +355 ② -11.7 计算机分那几类?各有什么特点?1.8 简述微处理器、微计算机及微计算机系统三个术语的内涵。

1.9 80X86微处理器有几代?各代的名称是什么?1.10 你知道现在的微型机可以配备哪些外部设备?1.11 微型机的运算速度与CPU的工作频率有关吗?1.12 字长与计算机的什么性能有关?习题一参考答案1.1 ① 16.25D=10000.01B=20.2Q=10.4H② 35.75D=100011.11B=43.6Q=23.CH③ 123.875D=1111011.111B=173.7Q=7B.EH④ 97/128D=64/123+32/128+1/128=0.1100001B=0.604Q=0.C2H1.2 ① 10101.01B=21.25D ② 11001.0011B=25.1875D③ 111.01B=7.25D ④ 1010.1B=10.5D1.3 ① 756.07Q=111101110.000111B=494.109D ②63.73Q=110011.111011B=51.922D③ 35.6Q=11101.110B=29.75D ④323.45Q=11010011.100101B=211.578D1.4 ① A7.8H=167.5D ② 9AD.BDH=2477.738D③ B7C.8D=2940.551D ④ 1ECH=492D1.5 ① [+127]补=01111111 ② [-1]补= 11111111③ [-0]补=00000000 ④[-128]补=100000001.6 ① [+355]补= 0000000101100011 ② [-1]补= 1111 1111 1111 11111.7 答:传统上分为三类:大型主机、小型机、微型机。

微机原理与接口技术第五章 练习题及答案

第五章练习题及答案一、填空题1、常见的片选控制方法有____________________________________。

线选法,全译码法,部分译码法2、磁带是______存储器。

顺序存储3、为保证动态RAM中的内容的不消失,需要进行__________操作。

刷新4、全部存储系统分为四级,即寄存器组,____________,内存,外存。

高速缓冲存储器5、DRAM靠_______存储信息,所以需要定期_____。

电容刷新6、虚拟存储器由__________两级存储器组成。

主存-辅存7、存储器是计算机系统的记忆设备,它主要用来______。

存储数据和指令8、8086CPU的物理地址是指实际的20位主存单元地址,每个存储单元对应唯一的物理地址,其范围是_________________。

00000H~FFFFFH二、选择题1、RAM是随机存储器,它分为( )两种。

A、ROM和SRAMB、DRAM和SRAMC、ROM和DRAMD、ROM和CD-ROMB2、从存储器中读出或向存储器中写入一个信息所需要的时间称为( )。

A、等待时间B、存取周期C、查找时间D、寄存器B3、在计算机的专业用语中,ROM表示( )。

A、外存储器B、内存储器C、只读存储器D、随机存储器C4、在下列存储器中,若按记录密度从低到高的顺序播列,应为( )。

A、软盘、硬盘、光盘、磁带B、磁带、硬盘、软盘、光盘C、磁带、软盎、硬盘、光盘D、硬盘、软盘、磁带、光盘C5、某计算机字长32位,存储容量为4MB,若按半字编址,它的寻址范围是()。

A、0-4MBB、0-2MBC、0-2MD、0-1MBC6、下列因素中,与Cache命中率无关的是()。

A、主存的存取时间B、快的大小C、Cache的组织方式D、cache 的容量A7、计算机的存储器采用分级存储体系的主要目的是()。

A、便于读写数据B、减小机箱的体积C、便于系统升级D、解决存储容量、价格和存取速度之间的矛盾D8、磁盘存储器的数据存取速度与下列哪一组性能参数有关?( )。

国防《微机原理与接口技术》教学资料包 课后习题答案 第5章

习题51.答::存储器系统是计算机系统中必不可少的组成部分,用于存放计算机工作所必需的程序和数据。

当程序和数据输入计算机后,所有输入的信息都存放在存储器中;程序执行过程中,存储器还将保存程序执行时产生的中间数据和结果数据,以便其他部件需要时随时使用。

静态RAM进行写操作时,写入信号自I/O线和I/O线输入,如要写入1,则I/O为高电平而I/O为低电平,它们通过T7、T8管和T5、T6管分别与A端和B端相连,使A=1,B=0,即强迫T2管导通,T1管截止,相当于写入1。

当输入信号及地址选择信号消失之后,T5、T6、T7、T8都截止,由于存储单元有电源及负载管,可以不断地向栅极补充电荷,依靠两个反相器的交叉控制,只要不掉电,就能保持写入的信息1,而不用刷新。

而若要写入0,则I/O线为高电平,I/O线为低电平,T2管截止,T1管导通,即A=0,B=1;进行读操作时,只要某一单元被选中,相应的T5、T6、T7、T8均导通,A端与B端分别通过T5、T6与D、D相通,D、D 又进一步通过T7、T8与 I/O和I/O相通,即将单元的状态传送到I/O和I/O线上。

由此可见,这种存储电路的读出过程是非破坏性的,即信息在读出之后,原存储电路的状态不变。

静态RAM存取速度比动态RAM快,工作稳定,且不需要刷新电路,使用方便灵活。

但由于它所用较多,致使集成度低,功耗较大,成本也高。

DRAM存储单元实质上是依靠T1管栅极电容的充放电原理来保存信息的。

一般2 ms左右,电容上所保存的电荷就会泄漏,会造成信息的丢失;另外数据读出后,存储电容C s上的信息也被破坏。

因此,在DRAM的使用过程中,必须及时地向保存1的那些存储单元补充电荷,以维持信息的存在。

所以DRAM必须有刷新操作。

2.答:微机中的全部存储器子系统一般分为四级,即:寄存器组、高速缓存、内部存储器和外部存储器。

第一级寄存器组是为了尽可能减少微处理器直接存取微处理器外部存储器的次数而设置的。

微机原理及接口技术课后习题参考答案

如有你有帮助,请购买下载,谢谢!第1章(1.6 习题)1.简述名词的概念:微处理器、微型计算机、微型计算机系统。

答:(1)微处理器:微处理器(Microprocessor)简称µP或MP,或CPU。

CPU是采用大规模和超大规模集成电路技术将算术逻辑部件ALU(Arithmetic Logic Unit)、控制部件CU (Control Unit)和寄存器组R(Registers)等三个基本部分以及内部总线集成在一块半导体芯片上构成的电子器件。

(2)微型计算机:微型计算机(Microcomputer)是指以微处理器为核心,配上由大规模集成电路制作的存储器、输入/输出接口电路及系统总线等所组成的计算机,简称微机。

(3)微型计算机系统:微型计算机系统由硬件与软件两大部分组成,分别称为硬件(Hardware)系统与软件(Software)系统。

其中,硬件(Hardware)系统由CPU、内存储器、各类I/O接口、相应的I/O设备以及连接各部件的地址总线、数据总线、控制总线等组成。

软件(Software)系统:计算机软件(Software)是指为运行、维护、管理、应用计算机所编制的程序及程序运行所需要的数据文档资料的总和。

一般把软件划分为系统软件和应用软件。

其中系统软件为计算机使用提供最基本的功能,但是并不针对某一特定应用领域。

而应用软件则恰好相反,不同的应用软件根据用户和所服务的领域提供不同的功能。

2.简述名词的概念:指令寄存器、地址寄存器、标志寄存器。

答:(1)指令寄存器:指令寄存器(Instruction Register,IR)用来保存计算机当前正在执行或即将执行的指令。

当一条指令被执行时,首先,CPU从内存取出指令的操作码,并存入IR中,以便指令译码器进行译码分析。

(2)地址寄存器:地址寄存器(Address Register,AR)被动地接受IP传送给它的地址值(二进制地址),AR的作用是保持IP送来的地址,并且以并行方式连接输出到CPU的地址引脚上,以便CPU访问指定的内存单元。

微型计算机原理与接口技术第五版周荷琴课后答案

微型计算机原理与接口技术第五版周荷琴课后答案第一章:计算机系统概述1.1 计算机系统基本组成•核心包括 CPU、内存和 I/O 设备。

CPU 是计算机的中央处理器,负责执行指令,控制各部分设备的操作。

内存存储数据和程序指令。

I/O 设备是计算机与外部世界进行信息交换的重要途径。

1.2 计算机的基本层次结构•计算机系统的基本层次结构分为硬件体系结构和软件体系结构。

硬件体系结构定义了计算机中硬件组件的功能、特性、接口和互连方式。

软件体系结构定义了计算机的软件组件及其相互关系。

1.3 计算机的工作过程•计算机工作过程主要包括取指令、分析指令、获取操作数、执行指令、写回结果等几个阶段。

具体过程为:取指令:从内存中读取指令;分析指令:解码指令确定要执行的操作;获取操作数:从内存或寄存器中读取操作数;执行指令:进行具体的运算或操作;写回结果:将运算结果写入内存或寄存器。

1.4 计算机性能指标•计算机的性能指标包括运算速度、存储容量、传输速率、可靠性和可用性等方面。

运算速度衡量了计算机执行指令的快慢;存储容量表示计算机可以存储的数据量;传输速率表示从一个设备向另一个设备传输数据的速度;可靠性表示计算机的故障率;可用性表示计算机在给定时间内正常工作的比例。

第二章:计算机的数制与编码2.1 数制与编码的基本概念•数制是用于表示数值的方法,常见的有十进制、二进制、八进制和十六进制等。

编码是指将字符、符号等信息转换成计算机可以处理的二进制形式。

2.2 二进制与十进制的转换•将十进制数转换成二进制数时,可以采用除2取余的方法。

将二进制数转换成十进制数时,可以根据二进制位上的权值相加的原理进行计算。

2.3 BCD码与ASCII码•BCD码是Binary-Coded Decimal的缩写,用4位二进制码表示一个十进制数的一位。

ASCII码是一种字符编码,将每个字符映射成一个唯一的二进制数。

2.4 奇偶校验码•奇偶校验码是一种错误检测码,用于检测数据传输过程中出现的位错误。

微机原理及接口第五章作业答案

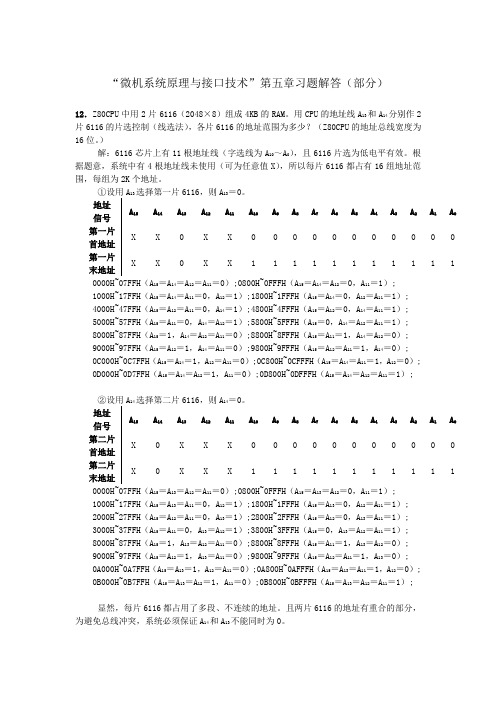

“微机系统原理与接口技术”第五章习题解答(部分)12.Z80CPU中用2片6116(2048×8)组成4KB的RAM。

用CPU的地址线A13和A14分别作2片6116的片选控制(线选法),各片6116的地址范围为多少?(Z80CPU的地址总线宽度为16位。

)解:6116芯片上有11根地址线(字选线为A10~A0),且6116片选为低电平有效。

根据题意,系统中有4根地址线未使用(可为任意值X),所以每片6116都占有16组地址范围,每组为2K个地址。

①设用A13选择第一片6116,则A13=0。

地址A15A14A13A12A11A10A9A8A7A6A5A4A3A2A1A0信号第一片X X 0 X X 0 0 0 0 0 0 0 0 0 0 0 首地址第一片X X 0 X X 1 1 1 1 1 1 1 1 1 1 1 末地址0000H~07FFH(A15=A14=A12=A11=0);0800H~0FFFH(A15=A14=A12=0,A11=1);1000H~17FFH(A15=A14=A11=0,A12=1);1800H~1FFFH(A15=A14=0,A12=A11=1);4000H~47FFH(A15=A12=A11=0,A14=1);4800H~4FFFH(A15=A12=0,A14=A11=1);5000H~57FFH(A15=A11=0,A14=A12=1);5800H~5FFFH(A15=0,A14=A12=A11=1);8000H~87FFH(A15=1,A14=A12=A11=0);8800H~8FFFH(A15=A11=1,A14=A12=0);9000H~97FFH(A15=A12=1,A14=A11=0);9800H~9FFFH(A15=A12=A11=1,A14=0);0C000H~0C7FFH(A15=A14=1,A12=A11=0);0C800H~0CFFFH(A15=A14=A11=1,A12=0);0D000H~0D7FFH(A15=A14=A12=1,A11=0);0D800H~0DFFFH(A15=A14=A12=A11=1);②设用A14选择第二片6116,则A14=0。

《微机系统原理与接口技术》答案

第1章习题解答1、冯诺依曼计算机的内涵是什么?这种计算机程序运行是由指令流驱动的还是数据流驱动的?答:冯诺依曼计算机的内涵:由运算器、控制器、存储器、输入设备、输出设备5大部分组成计算机硬件。

数据和计算机指令采用二进制数形式表示,存储在计算机内部存储器中。

计算机工作原理的核心是“存储程序”和“程序控制”。

事先编制好的由计算机指令组成的程序在执行前先装入存储器,控制器依据程序中的指令顺序周而复始地取出指令、分析指令、执行指令,根据指令的功能进行相应的运算,直到完成全部指令操作为止.程序的运行是通过指令流来驱动的。

2、微型计算机系统有哪三个层次?试简述它们的内涵及其联系和区别。

答:微型计算机系统的三个层次:微处理器、微型计算机和微型计算机系统。

三者的内涵:微处理器是利用大规模集成电路技术,将组成计算机的核心部件——运算器和控制器集成在一块硅片上的集成电路,简称MPU,习惯上称CPU。

微型计算机则是以微处理器为核心,配以内存储器、输入/输出(I/O)接口电路,通过总线结构连接而构成的裸机。

微型计算机系统是由微型计算机配以相应的外围设备(如键盘、显示器、打印机、外存储器等)、电源和其他辅助设备(如面板、机架等),以及控制微型计算机工作的软件而构成的完整的计算系统。

它们三者之间是从局部到全局的关系。

单纯的微处理器和单纯的微型计算机都不能独立工作。

只有微型计算机系统才是完整的计算系统,才可正常工作。

3、为什么把微型计算机的基本结构说成是总线结构?试简述总线结构的优点。

答:在微型计算机中,各组成部分之间是通过总线(包括地址总线、数据总线、控制总线)连接在一起而构成一个整体的,它们之间的信息交换也是通过总线进行。

CPU通过总线与存储器和I/O接口电路连接,I/O接口和外设也是通过总线连接,即使在CPU内部,它的各功能部件也是通过总线相连的。

因此微型计算机的基本结构就是总线结构。

微型计算机采用总线结构后,系统中各功能部件之间的相互关系变为各部件面向总线的单一关系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.下列因素中,与Cache的命中率无关的是(。

A.主存的存取时间

B.块的大小

C.Cache的组织方式

D.Cache的容量

解A

4.下列说法中不正确的是(。

A.每个程序的虚地址空间可以远大于实地址空间,也可以远小于实地址空间

B.多级存储体系由Cache、主存和虚拟存储器构成

C.Cache和虚拟存储器这两种存储器管理策略都利用了程序的局部性原理

SRAM的速度快、接口简单、读写操作简便,但存储容量较小、价格也比较高;而DRAM的存储密度较高、存储容量大,但接口较复杂,且需要定时刷新。

11.DRAM为什么要刷新?刷新方式有几种?

解因为DRAM存储的信息会随时间而消失,所以需要刷新。刷新方式包括:

·片外刷新(分散刷新、集中刷新和异步刷新;

·片内刷新。

16.设有一个具有24位地址和8位字长的存储器,问:

(1该存储器能够存储多少字节的信息?

(2如果该存储器由4M×1位的RAM芯片组成,需要多少片?

(3在此条件下,若数据总线为8位,需要多少位作芯片选择?

解

(116兆字节

(2需要4×8=32片

(3两位

18.某计算机系统的内存储器由Cache和主存构成,Cache的存取周期为45ns,主存的存取周期为200ns。已知在一段给定的时间内,CPU共访问内存4500次,其中340次访问主存。问:

9.存储器有哪些主要技术指标?这些指标是如何表示的?

解存储器的主要技术指标包括:

·存取速度Tacc,以ns(纳秒表示;

·存储容量,以bit表示,或用Byte表示,如62256,256kbit,或8K×8 bit;

·存储器类别,用型号来区分。

10.DRAM的存取时序和SRAM有何不同?其性能有何不同?

(1Cache的命中率是多少?

(2CPU访问内存的平均时间是多少纳秒?

(3Cache-主存系统的效率是多少?

(4CPU访存的平均时间与哪些因素有关?

解(1H=0.924

(2T=56.71ns

(3e=0.7935

(4和命中率H以及Cache和主存的存取时间T1和T2有关。

23.说明80486 CPU在进行字节/字/双字数据访问时,数据地址和BE0、BE1、BE2和BE3之间的关系。

12.8086 CPU与存储器连接时需要考虑哪几方面的因素?

解存储器接口设计需要考虑以下问题:(1存储器容量;(2存储空间的安排;(3总线上的存储器存取信号及时序;(4数据总线宽度等。

15.用2114、6116和6264分别组成容量为64K×8的存储器,各需多少芯片?地址需要多少位作为片内地址选择线,多少位作为芯片选择线?

6.在Cache的地址映射中,若主存中的任意一页均可映射到Cache内的任意一页的位置上,则这种方法称为(。

A.全相联映射

B.直接映射

C.组相联映射

D.混合映射

解A

7.在计算机系统中,下列部件都能够存储信息:

①主存;②CPU内的通用寄存器;③Cachc;④磁带;⑤磁盘。

按照CPU存取速度排列,由快至慢依次为(。其中,内存包括( ;属于外存的是( ;由半导体材料构成的是(。

解2114是1K×4的SRAM芯片。需要64X2=128个芯片,地址需要10位作为片内地址选择线,6位作为芯片ห้องสมุดไป่ตู้择线。

6116是2K×8的SRAM芯片,需要32个芯片,地址需要11位作为片内地址选择线,5位作为芯片选择线。

6264是8K×8的SRAM芯片,需要8个芯片,地址需要13位作为片内地址选择线,3位作为芯片选择线。

D.当Cache未命中时,CPU可以直接访问主存,而外存与CPU之间则没有直接通路

解B

5.下列说法中正确的是(。

A.虚拟存储器技术提高了计算机的速度

B.Cache与主存统一编址,Cache的地址空间是主存地址空间的一部分

C.主存都是由易失性的随机读写存储器构成的

D.Cache的功能全部由硬件实现

解D

第5章习题及参考解答

1.计算机的存储器采用分级存储体系的主要目的是(。

A.便于读写数据

B.减小机箱的体积

C.便于系统升级

D.解决存储容量、价格和存取速度之间的矛盾

解D

2.在多级存储体系中,Cache─主存结构的作用是解决(问题。

A.主存容量不足

B.主存与辅存速度不匹配

C.辅存与CPU速度不匹配

D.主存与CPU速度不匹配

解当只有BE0有效时,通过D7~D0传输低字节;当只有BE1有效时,通过D15~D8传输次低字节;若BE0和BE1有效而另外两个字节允许信号无效,则通过D15~D0传输低字;若四个字节允许信号都有效,则通过D32~D0传输双字。

24.对于Pentium采用全译码方式设计一个64位存储器模块,使用EPROM芯片,地址范围FFFF0000H~FFFFFFFFH,SRAM芯片,地址范围00000000H~003FFFFFH。

解SRAM的读写操作如下:首先在地址线上出现有效的地址,然后CS有效,最后根据OE或WE是否有效进行相应的读/写。而DRAM的读写操作如下:首先在地址线上出现有效的行地址,然后RAS有效;经过一定时间之后,地址线上的行地址被撤除,改送列地址,而CAS变为有效;当行、列地址都被锁存到DRAM芯片内部的锁存器之后,即可根据OE或WE信号进行读/写操作。二者的不同在于DRAM芯片采用分时复用的方式传输地址,也即将地址分为行地址和列地址两部分分时在地址线上传送,这需要两个连续的时钟周期。

解若采用EPROM芯片27C64(8K×8位,需要8片,其中SA31~SA16共16位都为1作为8片27C64的片选信号,存储器读/写信号与BE0-BE7结合产生8片存储芯片的读/写信号,SA15-SA3作为地址线连接到27C64相应的地址线A12-A0上作为各芯片内存储单元的寻址信号。

若采用SRAM芯片628128(128K×8,需要32片,用SA31-SA20共12位译码作为片选信号,其中SA31~SA22都为0,根据SA21,SA20选择地址范围00000000H~000FFFFFH ,00100000H~001FFFFFH , 00200000H~002FFFFFH ,00300000H~003FFFFFH四组存储体,存储器读/写信号与BE0-BE7结合产生低3位地址为000B-111B八个存储体芯片的读/写,SA19-SA3作为地址线连接到628128相应的地址线A16-A0上作为各芯片内存储单元的寻址信号。

解从快到慢依次为(②、③、①、⑤、④。其中,内存包括(①和③;属于外存的是(④和⑤;由半导体材料构成的是(①、②、③。

8.什么是SRAM,DRAM,ROM,PROM,EPROM和FLASH?

解易失性半导体存储器统称为RAM,它分为静态RAM(SRAM和动态RAM(DRAM,用于在程序中保存需要动态改变的数据,或是需要动态加载的程序。非易失性半导体存储器称为ROM,其中PROM是可编程ROM,EPROM是可擦除PROM(包括紫外线可擦除和电可擦除两种。FLASH是一种可以电擦除的非易失性半导体存储器。