最优秀的同步整流驱动IC-UCC24610

一种基于GaN的高效率高功率密度隔离DC

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 201710031283.X(22)申请日 2017.01.17(71)申请人 浙江大学地址 310058 浙江省杭州市西湖区余杭塘路866号(72)发明人 杨雁勇 王正仕 (74)专利代理机构 杭州求是专利事务所有限公司 33200代理人 万尾甜 韩介梅(51)Int.Cl.H02M 3/338(2006.01)H02M 3/335(2006.01)(54)发明名称一种基于GaN的高效率高功率密度隔离DC-DC变换电路(57)摘要本发明公开了一种基于GaN的高效率高功率密度隔离DC-DC变换电路,包括LLC半桥软开关、匝比N:1:1的变压器、滤波电容、Fly-back辅助电源电路、集成LLC控制UCC25600芯片电路、驱动UCC27714电路、光耦及输出反馈PI调节电路、PEM-2-S12-S5-D电压转换电路等,其中原边采用GaN器件GS66502B,副边采用GaN器件GS61004B并联同步整流;本发明将LLC谐振电路与同步整流进行结合,采用简单的控制和驱动电路以及辅助电源设计,实现了宽输入电压范围,恒定输出电压12V,200W的DC-DC变换,电路采用GaN开关器件,提高了变换器效率和功率密度。

权利要求书1页 说明书6页 附图2页CN 106712529 A 2017.05.24C N 106712529A1.基于GaN的高效率高功率密度隔离DC-DC变换电路,包括LLC半桥软开关、谐振电感、谐振电容、匝比N:1:1的变压器、及输出整流;其特征在于,所述的LLC半桥软开关采用GaN MOSFET半桥,采用GaN器件GS66502B,所述的输出整流采用GaN MOSFET并联同步整流,采用GaN器件GS61004B,该电路还包括滤波电容、Fly-back辅助电源电路、集成LLC控制UCC25600芯片电路、驱动UCC27714电路、光耦及输出反馈PI调节电路、PEM-2-S12-S5-D电压转换电路、UCC24610同步整流控制电路;滤波电容与GaNMOSFET半桥并联连接300-400V输入电压,UCC25600芯片采集谐振电流,其输出端连接UCC27714电路,UCC27714电路的两路输出各通过一个脉冲驱动变压器与GaNMOSFET半桥中的两个开关管栅极相连,Fly-back辅助电源电路从输入直流母线取电,用于将300-400V的输入电压转化为12V为原边芯片UCC25600和UCC27714供电,UCC24610芯片用于给GaNMOSFET并联同步整流电路提供驱动信号,PEM-2-S12-S5-D电压转换电路用于将原边的12V转化为5V为UCC24610芯片供电,基于431的输出反馈PI调节电路通过光耦反馈到原边控制芯片UCC25600。

IUCC2461090WLLC串联谐振电源转换器解决方案word参考模板

TI UCC24610 90W LLC串联谐振电源转换器解决方案TI 公司的UCC24610是5V系统的绿色整流控制器,当采用单独电源时LLC输出可高达15V,工作频率高达600kHz,V DS MOSFET电流检测,能从轻负载和睡眠模式中同步叫醒,主要用在AC/DC 5V适配器,5V偏压电源,低压整流电路和反激和LLC转换器。

本文介绍了UCC24610主要特性,功能方框图,反激拓扑框图和LLC串联谐振转换器框图,以及变压器配置,自同步配置和电容配置的LLC串联谐振转换器电路图和相应的材料清单。

A 90-W, High-Efficiency, LLC Series-Resonant Converter with Secondary-Side Synchronous RectificationThe UCC24610 Green Rectifier Controller is optimized for 5-V systems and can be used for LLC outputs up to 15 V when a separate 5-V supply is available. Above 15 V the UCC24610 is limited by the 50-V maximum voltage rating of the VD pin. This is because in a conventional secondary rectifier arrangement, that employs two rectifiers with a center-tapped secondary winding, each rectifier sees a peak reverse voltage equal to twice the regulated output.The scope of this reference design guide is to describe the design and performance of a functional circuit that extends the application of the UCC24610 to systems with output voltages up to 30 V. This is achieved using an alternate topology for secondary rectification and addressing the design constraints that the topology presents. Two configurations are described for synchronizing the turn-off of each SR circuit using the gate-drive signals on the primary side of the converter.An area not addressed by this guide is electromagnetic compatibility (EMC). For most applications, EMI filter components are added so that the design meets applicable environmental and system compatibility requirements.To comply with EMC standards, components such as input and output filters are required to suppress electromagnetic interference (EMI).This GREEN Rectifier™ controller is a high-performance controller and driver for standard and logic-level N-channel MOSFET power devices used for low-voltage secondary-side synchronous rectification.The combination of controller and MOSFET emulates a near-ideal diode rectifier. Thissolution not only directly reduces power dissipation of the rectifier but also indirectly reduces primary-side losses as well, due to compounding of efficiency gains.Using drain-to-source voltage sensing, the UCC24610 is ideal for Flyback and LLC-Resonant power supplies but can also be used with other power architectures. The UCC24610 is optimized for output voltages from 4.5 V to 5.5 V, and is suitable for use with lower and higher output voltages as well.UCC24610主要特性:Secondary-Side Controller Optimized for 5-V SystemsUp to 600-kHz Operating FrequencyVDS MOSFET-Sensing1.6-ohm Sink,2.0-ohm Source Gate-Drive ImpedancesMicro-Power Sleep Current for 90+ DesignsAutomatic Light-Load ManagementSynchronous Wake-Up From Sleep and Light-Load ModesProtection Features on Programming InputsSYNC Input for CCM Operation20-ns Typical Turn-Off Propagation DelayImproved Efficiency and Design Flexibility Over Traditional Diode Solution May Be Biased Directly From 5-V OutputMinimal Component CountUCC24610应用:AC/DC 5-V Adapters5-V Bias SuppliesLow Voltage Rectification CircuitsFlyback and LLC Converters图1。

top246电源

Power IntegrationsDesign Example ReportTitle21.7 W Power Supply using TOP246P Specification Input: 85 - 265 VAC Output: 48 V / 450 mA Application PoE AC AdapterAuthor Power Integrations Applications Department Document Number DER-97Date September 12, 2005 Revision1.0Summary and Features• Single Sided PC board• Reduced cost and component count • Eliminates two y-capacitors to ground• Eliminates secondary side common mode choke • Eliminates ground wire differential choke • High Efficiency (~ 80 %)• Lower Cost Transformer Construction – no sleeving termination required • Low EMI signature (both radiated and conducted emissions) •Built-in output short circuit protectionThe products and applications illustrated herein (including circuits external to the products and transformer construction) may be covered by one or more U.S. and foreign patents or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations’ patents may be found at .Table Of Contents1Introduction (3)2Power Supply Specification (4)3Schematic (5)4Circuit Operation (6)4.1General (6)4.2Description (6)5Bill of Materials (7)6Layout (9)7Transformer Design Spreadsheet (10)8Transformer Specification (13)9Performance (17)9.1Efficiency (17)9.2Regulation vs. Load (18)9.3Regulation vs. Line (19)9.4Raw Performance Data (20)10Waveforms (21)10.1Drain Current and Voltage (21)10.2Output Transient Load Response (22)10.3Output Ripple Voltage (23)10.4Switching Ripple (23)10.5Line Frequency Ripple (24)10.6Output Voltage Shutdown Profile (26)11Thermal Test (27)11.1Thermal Performance (27)12Conducted EMI (29)12.1Conducted EMI Performance (29)13Revision History (30)Important Notes:Although this board is designed to satisfy safety isolation requirements, the engineering prototype has not been agency approved. Therefore, all testing should be performed using an isolated source to provide power to the prototype board.Design Reports contain a power supply design specification, schematic, bill of materials, and transformer documentation. Performance data and typical operation characteristics are included. Typically only a single prototype has been built.1 IntroductionThis document is an engineering report describing a Power over Ethernet (PoE) power supply utilizing TOP246P. The power supply delivers 21.7 W continuous from an input of 85 to 265 VAC.This document provides complete design information including specification, schematic, bill of material and transformer design and construction information. The document also provides performance information.Figure 1 – Circuit Board - Top ViewFigure 2 – Circuit Board - Bottom View2 Power Supply SpecificationDescriptionSymbolMinTypMaxUnitsCommentInputVoltage V IN 85 265 VACOutputOutput Voltage 1V OUT1 47.52 48 48.48 V ± 1% Output Ripple Voltage 1 V RIPPLE1 480 mVp-p 20 MHz bandwidthOutput Current 1 I OUT1 0 450 mA Power Down Holdup115 VAC T H(115VAC) 18 ms 230 VACT H(230VAC)60 msTotal Output PowerAverage Output Power P OUT121.7 WFull Load Efficiency η 80 % EnvironmentalConducted EMIMeets CISPR22B / EN55022BSafety Designed to meet IEC950, UL1950Class IIAmbient Temperature T AMB 0 40 oCForced airflow3 Schematic Figure 3 – Schematic4 Circuit Operation4.1 GeneralThe power supply uses a TOP246P device (U2), with integrated MOSFET and controller, in an isolated flyback configuration. The circuit also uses the x-pin programmable current limit feature control the overload power of the power supply and also to minimize transformer size.4.2 DescriptionThe input fuse F1 protects the supply against catastrophic failure. Thermistor RT1 limits the in-rush current during power-up. Diodes D5 – D8 implement a bridge rectifier to rectify the input mains voltage. Capacitor C22 attenuates the EMI generated by the input bridge diodes D5-D8.Inductor L1 is used to attenuate both differential and common mode EMI noise from the power supply. A large value is used to also prevent any noise filtering through from networks connector to the power supply output. Capacitor C2 forms part of the EMI solution by shunting EMI signals generated across the transformer T2. Capacitor C4 decouples the rectified input voltage providing a DC-bus. Resistor R14 programs the current limit of the TOPSwitch-GX (U2). Resistors R6 and R9 modified this current limit with input voltage, to maintain a relatively flat output overload profile. Diode D2, R2, C1 and R1 implement an RCD clamp circuit to limit the leakage inductance spike on the TOPSwitch-GX Drain pin. Diode D3 and C8 implement a bias voltage supply to provide operating power to the TOPSwitch-GX with integrated PWM, controller and main switching MOSFET. Capacitors C13 and C14 provide device decoupling with C14 also programming the startup and auto-restart period of the device. Resistor R13 provides feedback compensation in conjunction with C14. The inductance of transformer T2 provides the energy storage and conversion component of the circuit. Resistor R41 feeds current to an indicator LED U6, which is illuminated during normal operation.The 48 V output is rectified and filtered by diodes D1 and D4 and capacitors C5 with C7 provided output decoupling. Resistor R18 and C21 snub high frequency ringing on these diodes. Resistors R8 and R15 sense the output voltage providing the input signal for the TL431 (U3) reference. Resistor R41 provides DC bias current (approx. 1 mA) to the U3. Components R12 and C12 provide compensation for U3, to make sure that it’s frequency response is limited only to low-frequency signals. Resistor R10 programs the high-frequency gain of the control loop and with opto-diode U5A transmits the feedback signal. Resistor R42 and C15 provide increase the high frequency gain of the feedback circuit to improve output ripple rejection. Zener diode VR1 is used due to the high 48 V output voltage and drops approximately 30 V, to bring the TL431 collector voltage comfortably within safe levels (i.e. less than 30 V). Opto-transistor U5B feeds the control signal back to the TOPSwitch-GX.5 Bill of MaterialsItem Qty. Ref. Description Mfg Part Number Mfg1 1 C1 4.7 nF, 1 kV, Thru Hole, Disc Ceramic 5GAD47 Vishay/Sprague2 1 C2 2.2 nF, Ceramic, Y1 440LD22 Vishay3 1 C4 47 uF, 400 V, Electrolytic, Low ESR, 730mOhm, (16 x 25)KMX400VB47RM16X25LL UnitedChemi-Con4 1 C5 180 uF, 63, Electrolytic, Low ESR, 145mOhm, (10 x 20) LXZ63VB181MJ20LL United Chemi-Con5 1 C7 68 uF, 63, Electrolytic, Low ESR, 340mOhm, (8 x 12) LXZ63VB68RMH15LL United Chemi-Con6 1 C8 10 uF, 50 V, Electrolytic, Gen. Purpose, (5 x11)KME50VB10RM5X11LL UnitedChemi-Con7 2 C12 C15 1.0 uF, 50 V, Ceramic, Z5U ECU-S1H105MEB Panasonic8 1 C13 100 nF, 50 V, Ceramic, X7R ECU-S1H104KBB Panasonic9 1 C14 47 uF, 16 V, Electrolytic, Low ESR, 500mOhm, (5 x 11.5) LXZ16VB47RME11LL United Chemi-Con10 1 C21 100 pF, 1 kV, Disc Ceramic NCD101K1KVY5F NIC Components Corp11 1 C22 47 nF, 275 VAC, Film, X2 ECQU2A473ML Panasonic12 2 D1 D4 100 V, 1 A, Schottky, DO-41 SB1100 Fairchild13 1 D2 1000 V, 1 A, Rectifier, Glass Passivated, 2us, DO-41 1N4007GP Vishay14 1 D3 75 V, 300 mA, Fast Switching, DO-35 1N4148 Vishay15 2 D5 D6 600 V, 1 A, Ultrafast Recovery, 75 ns, DO-41 UF4005Vishay16 2 D7 D8 600 V, 1 A, Rectifier, DO-41 1N4005 Vishay17 1 F1 1 A, 250V, Slow, TR5 3,721,100,041 Wickman18 1 J4 AC Input Receptacle and Accessory Plug,PCBM 161-R301SN13Kobiconn19 2 J5 J6 R/A, RJ45 Nonshielded, PCBM RJHS-5080 Amphenol Canada20 1 L1 19 mH, 0.5 A, Common Mode Choke ELF15N005A Panasonic21 1 L2 3.3 uH, 2.66 A 822LY-3R3M Toko22 1 R1 100 k, 5%, 1 W, Metal Oxide RSF100JB-100K Yageo23 1 R2 47 R, 5%, 1/2 W, Carbon Film CFR-50JB-47R Yageo24 1 R6 3 M, 5%, 1/8 W, Carbon Film CFR-12JB-3M0 Yageo25 1 R8 182 k, 1%, 1/4 W, Metal Film MFR-25FBF-182K Yageo26 1 R9 2.7 M, 5%, 1/8 W, Carbon Film CFR-12JB-2M7 Yageo27 1 R10 3.3 k, 5%, 1/8 W, Carbon Film CFR-12JB-3K3 Yageo28 2 R12 R40 1 k, 5%, 1/8 W, Carbon Film CFR-12JB-1K0 Yageo29 1 R13 6.8 R, 5%, 1/8 W, Carbon Film CFR-12JB-6R8 Yageo30 1 R14 9.09 k, 1%, 1/4 W, Metal Film MFR-25FBF-9K09 Yageo31 1 R15 10 k, 1%, 1/4 W, Metal Film MFR-25FBF-10K0 Yageo32 1 R18 10 R, 5%, 1/4 W, Carbon Film CFR-25JB-10R Yageo33 1 R41 2 k, 5%, 1/8 W, Carbon Film CFR-12JB-2K0 Yageo34 1 R42 330 R, 5%, 1/8 W, Carbon Film CFR-12JB-330R Yageo35 1 RT1 NTC Thermistor, 30 Ohms, 1.5 A CL210 Thermometrics36 1 T2 Bobbin, EEL25.4, Horizontal, 10 pins YW-236-03B Yih-Hwa Enterprises37 1 U2 TOPSwitch-GX, TOP246P, DIP-8B TOP246P Power Integrations38 1 U3 2.495 V Shunt Regulator IC, 2%, 0 to 70C,TO-92 TL431CLPTexasInstruments39 1 U5 Opto coupler, 35 V, CTR 300-600%, 4-DIP ISP817D, PC817X4 Isocom, Sharp40 1 U6 LED, Green, 5 mm, 565 nm, 30 mcd SSL-LX5093GD Lumex Opto41 1 VR1 30 V, 5%, 500 mW, DO-35 1N5256B Microsemi47 Total6 Layout7 Transformer Design SpreadsheetACDC_TOPSwitchGX_020 105; Rev.2.5; Copyright Power Integrations 2005 INPUT INFO OUTPUT UNIT TOP_GX_FX_020105.xls: TOPSwitch-GX/FXContinuous/Discontinuous FlybackTransformer Design SpreadsheetENTER APPLICATION VARIABLES CustomerVACMIN 85 VoltsVACMAX 265 Volts Maximum AC Input VoltagefL 50 Hertz AC Mains FrequencyVO 48 Volts Output Voltage (main)PO 21.7 Watts Output Powern 0.86 Efficiency EstimateZ 0.44 Loss Allocation FactorVB 12 Volts Bias VoltagetC 2.66 mSeconds Bridge Rectifier Conduction Time Estimate CIN 47 uFarads Input Filter CapacitorENTER TOPSWITCH-GX VARIABLESTOP-GX top246p Universal 115 Doubled/230VChosen Device TOP246P PowerOut26W 34WKI 0.78 External Ilimit reduction factor (KI=1.0 fordefault ILIMIT, KI <1.0 for lower ILIMIT) ILIMITMIN 0.948 Amps Use 1% resistor in setting external ILIMIT.Assumes 0.85 derating at 100 degrees Celsius ILIMITMAX 1.158 Amps Use 1% resistor in setting external ILIMIT Frequency (F)=132kHz,(H)=66kHzF Full (F) frequency option - 132kHzfS 132000 Hertz TOPSwitch-GX Switching Frequency: Choosebetween 132 kHz and 66 kHzfSmin 124000 Hertz TOPSwitch-GX Minimum Switching Frequency fSmax 140000 Hertz TOPSwitch-GX Maximum Switching Frequency VOR 90 Volts Reflected Output VoltageVDS 2 Volts TOPSwitch on-state Drain to Source Voltage VD 1 Volts Output Winding Diode Forward Voltage Drop VDB 0.7 Volts Bias Winding Diode Forward Voltage DropKP 0.68 Ripple to Peak Current Ratio (0.4 < KRP < 1.0: 1.0< KDP<6.0)ENTER TRANSFORMER CORE/CONSTRUCTION VARIABLESCore Type eel25Core EEL25 P/N: PC40EE25.4/32/6.4-ZBobbin EEL25_BOBBINP/N: *AE 0.404 cm^2 Core Effective Cross Sectional AreaLE 7.34 cm Core Effective Path LengthAL 1420 nH/T^2 Ungapped Core Effective InductanceBW 22.3 mm Bobbin Physical Winding WidthM 3 mm Safety Margin Width (Half the Primary toSecondary Creepage Distance)L 1 Number of Primary LayersNS 21 Number of Secondary TurnsDC INPUT VOLTAGE PARAMETERSVMIN 81 Volts Minimum DC Input VoltageVMAX 375 Volts Maximum DC Input VoltageCURRENT WAVEFORM SHAPE PARAMETERSDMAX 0.53 Maximum Duty CycleIAVG 0.31 Amps Average Primary CurrentIP 0.89 Amps Peak Primary CurrentIR 0.60 Amps Primary Ripple CurrentIRMS 0.45 Amps Primary RMS CurrentTRANSFORMER PRIMARY DESIGN PARAMETERSLP 532 uHenries Primary InductanceNP 39 Primary Winding Number of TurnsNB 5 Bias Winding Number of TurnsALG 358 nH/T^2 Gapped Core Effective InductanceBM 3027 Gauss Maximum Flux Density at PO, VMIN(BM<3000)BP 3957 Gauss Peak Flux Density (BP<4200)BAC 1029 Gauss AC Flux Density for Core Loss Curves (0.5 XPeak to Peak)ur 2053 Relative Permeability of Ungapped CoreLG 0.11 mm Gap Length (Lg > 0.1 mm)BWE 16.3 mm Effective Bobbin WidthOD 0.42 mm Maximum Primary Wire Diameter includinginsulationINS 0.06 mm Estimated Total Insulation Thickness (= 2 * filmthickness)DIA 0.36 mm Bare conductor diameterAWG 28 AWG Primary Wire Gauge (Rounded to next smallerstandard AWG value)CM 161 Cmils Bare conductor effective area in circular mils CMA 362 Cmils/Amp Primary Winding Current Capacity (200 < CMA< 500)TRANSFORMER SECONDARY DESIGN PARAMETERS (SINGLE OUTPUT EQUIVALENT)Lumped parametersISP 1.63 Amps Peak Secondary CurrentISRMS 0.77 Amps Secondary RMS CurrentIO 0.45 Amps Power Supply Output CurrentIRIPPLE 0.62 Amps Output Capacitor RMS Ripple CurrentCMS 153 Cmils Secondary Bare Conductor minimum circularmilsAWGS 28 AWG Secondary Wire Gauge (Rounded up to nextlarger standard AWG value)DIAS 0.32 mm Secondary Minimum Bare Conductor Diameter ODS 0.78 mm Secondary Maximum Outside Diameter forTriple Insulated WireINSS 0.23 mm Maximum Secondary Insulation Wall Thickness VOLTAGE STRESS PARAMETERSVDRAIN 584 Volts Maximum Drain Voltage Estimate (IncludesEffect of Leakage Inductance)PIVS 252 Volts Output Rectifier Maximum Peak InverseVoltagePIVB 65 Volts Bias Rectifier Maximum Peak Inverse Voltage TRANSFORMER SECONDARY DESIGN PARAMETERS (MULTIPLE OUTPUTS)1st outputVO1 48 Volts Output VoltageAmps Output DC CurrentIO1 0.4520833333PO1 21.70 Watts Output PowerVD1 1 Volts Output Diode Forward Voltage DropNS1 21.00 Output Winding Number of TurnsISRMS1 0.766 Amps Output Winding RMS CurrentIRIPPLE1 0.62 Amps Output Capacitor RMS Ripple CurrentPIVS1 252 Volts Output Rectifier Maximum Peak InverseVoltageCMS1 153 Cmils Output Winding Bare Conductor minimumcircular milsAWGS1 28 AWG Wire Gauge (Rounded up to next largerstandard AWG value)DIAS1 0.32 mm Minimum Bare Conductor DiameterODS1 0.78 mm Maximum Outside Diameter for Triple InsulatedWire2nd outputVO2 Volts Output VoltageIO2 Amps Output DC CurrentPO2 0.00 Watts Output PowerVD2 Volts Output Diode Forward Voltage DropNS2 0.00 Output Winding Number of TurnsISRMS2 0.000 Amps Output Winding RMS CurrentIRIPPLE2 0.00 Amps Output Capacitor RMS Ripple CurrentPIVS2 0 Volts Output Rectifier Maximum Peak InverseVoltageCMS2 0 Cmils Output Winding Bare Conductor minimumcircular milsAWGS2 N/A AWG Wire Gauge (Rounded up to next largerstandard AWG value)DIAS2 N/A mm Minimum Bare Conductor DiameterODS2 N/A mm Maximum Outside Diameter for Triple InsulatedWire3rd outputVO3 Volts Output VoltageIO3 Amps Output DC CurrentPO3 0.00 Watts Output PowerVD3 Volts Output Diode Forward Voltage DropNS3 0.00 Output Winding Number of TurnsISRMS3 0.000 Amps Output Winding RMS CurrentIRIPPLE3 0.00 Amps Output Capacitor RMS Ripple CurrentPIVS3 0 Volts Output Rectifier Maximum Peak InverseVoltageCMS3 0 Cmils Output Winding Bare Conductor minimumcircular milsAWGS3 N/A AWG Wire Gauge (Rounded up to next largerstandard AWG value)DIAS3 N/A mm Minimum Bare Conductor DiameterODS3 N/A mm Maximum Outside Diameter for Triple InsulatedWireTotal power 21.7 Watts Total Power for Multi-output sectionNegative Output N/A If negative output exists enter Output number;eg: If VO2 is negative output, enter 28 Transformer SpecificationTransformer ConstructionElectrical DiagramWinding OrderCore InformationCore Type eel25Core Material NC-2H or Equivalent Estimated Gap length, mm 0.110Gapped Effective Inductance, nH/t^2 358Primary Inductance, uH 532Bobbin Information (Manual Input)Bobbin Reference Generic, 5 pri. + 5 sec.Bobbin Orientation HorizontalNumber of Primary pins 5Number of Secondary pins 5Margin on Left, mm 3.0Margin on Right, mm 3.0Primary Winding (Manual Input)1 Parameter Section Number of Turns 39Wire Size, AWG 28Filar 1Layers 0.88Start Pin(s) 5Termination Pin(s) 3BIAS Winding (Manual Input)Parameter Value Number of Turns 6Wire Size, AWG 28Filar 1Layers 0.13Start Pin(s) 1Termination Pin(s) 2Shield InformationParameter Primary Cancellation Number of Turns 20 22Wire Size, AWG 28 28Filar 2 2Layers 0.90 0.99Start Pin(s) NC 3,4Termination Pin(s) 3,4 NCSecondary Winding (Manual Input)1 Parameter Output Spec Voltage, V 48.00Spec Current, A 0.45Actual Voltage, V 48.00Number of Turns 21Wire Size, AWG 28Filar 2Layers 0.94Start Pin(s) 6Termination Pin(s) 7Winding InstructionUse 3.0 mm margin (item [3]) on the left side. Use 3.0 mm margin (item [3]) on the rightside.Cancellation Shield WindingStart on pin(s) 3,4 and wind 22 turns (x 2 filar) of item [6]. in exactly 1 layer. Leave thisend of cancellation shield winding not connected. Bend the end 90 deg and cut the wire inthe middle of the bobbin.Add 1 layer of tape, item [4], to secure the winding in place.Primary WindingStart on pin(s) 5 and wind 39 turns of item [6] in 1.00 layer(s) from left to right. Finishwinding on pin(s) 3.Add 1 layer of tape, item [4], for insulation.Bias WindingStart on pin(s) 1 and wind 6.0 turns (x 1 filar) of item [6]. Spread the winding evenlyacross entire bobbin. Finish on pin(s) 2.Add 1 layer of tape, item [4], for insulation.Primary Balanced Shield WindingStart on any (temp) pin on the secondary side and wind 20 turns (x 2 filar) of item [6].Spread the winding evenly across entire bobbin. Finish this winding on pin(s) 3,4.Cut out wire connected to temp pin on secondary side. Leave this end of primary shieldwinding not connected. Bend the end 90 deg and cut the wire in the middle of the bobbin.Add 3 layers of tape, item [4], for insulation.Secondary WindingStart on pin(s) 6 and wind 21 turns (x 2 filar) of item [6]. Spread the winding evenlyacross entire bobbin. Finish on pin(s) 7.Add 2 layers of tape, item [4], for insulation.Core AssemblyAssemble and secure core halves. Item [1].VarnishDip varnish uniformly in item [5]. Do not vacuum impregnate.Comments1. Pins 8 through 10 on the secondary side are not connected to anyelectrical node.2. Pins 3 and 4 should be electrically connectedMaterialsItem Description [1] Core: eel25, NC-2H or Equivalent,gapped for ALG of 358 nH/t^2[2] Bobbin: Generic, 5 pri. + 5 sec.[3] Tape: Polyester web 3.0 mm wide[4] Barrier Tape: Polyester film 22.30 mmwide[5] Varnish[6] Magnet Wire: 28 AWG, SolderableDouble CoatedElectrical Test SpecificationsParameter Condition Spec Electrical Strength, VAC 60 Hz 1 minute, from pins3 - 5 to pins 6 - 10.3000Nominal Primary Inductance, uH Measured at 1 V pk-pk,typical switchingfrequency, between pin 3to pin 5, with all otherWindings open.586 +/- 10%Primary Leakage, uH Measured between Pin 3to Pin 5, with all otherWindings shorted.17.57 Goal9 Performance 9.1 EfficiencyFigure 6 – Output Regulation vs. Output Load, Room TemperatureFigure 7 – Output Regulation vs. Input Line Voltage, Room Temperature9.4 Raw Performance DataLoad was applied at the end of a 1 ft long Ethernet cable connected to the connector J6. The load was applied using an electronic load. The output voltage was measurement at the end of this cable.10 Waveforms10.1 Drain Current and VoltageFigure 8 – 85 VAC, full loadUpper Ch3: Drain Voltage 100 V, Lowr Ch4: Drain Current 0.5 A / Div, 2 µs / divFigure 9 – 115 VAC, full loadUpper Ch3: Drain Voltage 100 V, Lowr Ch4: Drain Current 0.5 A / Div, 2 µs / divFigure 10 – 230 VAC, full loadUpper Ch3: Drain Voltage 200 V, Lowr Ch4: Drain Current 0.5 A / Div, 2 µs / divFigure 11 – 265 VAC, full loadUpper Ch3: Drain Voltage 200 V, Lowr Ch4: Drain Current 0.5 A / Div, 2 µs / div10.2 Output Transient Load ResponseFigure 12 – 115 VAC, (48 V 0.23 A to 0.45 A step)48 V Output Voltage 200 mV / Div, 5 ms / divFigure 13 – 230 VAC, (48 V 0.23 A to 0.45 A step)48 V Output Voltage 200 mV / Div, 5 ms / div10.3 Output Ripple VoltageIt can be seen from the waveforms below that the power supply comfortably meets the output ripple specifications. This is possible even without the need for an output inductor.Measurements made at the end of an Ethernet cable connected to J6. The voltage measurement included a 0.1 uF ceramic capacitor in parallel with a 1 uF / 50 V electrolytic capacitor, at point of measurement (end of the cable).10.4 Switching RippleFigure 14 – 85 VAC, Full LoadCH1: 48 V Output Ripple, 200 mV, CH3: Drain Voltage, 200 V, 5 µs / divFigure 15 – 115 VAC, Full LoadCH1: 48 V Output Ripple, 200 mV, CH3: Drain Voltage, 200 V, 5 µs / divFigure 16 – 230 VAC, Full LoadCH1: 48 V Output Ripple, 200 mV,CH3: Drain Voltage, 200 V, 5µs / divFigure 17 – 265 VAC, Full LoadCH1: 48 V Output Ripple, 200 mV, CH3: Drain Voltage, 200 V, 5 µs / div10.5 Line Frequency RippleFigure 18 – 85 VAC, Full LoadCH1: 48 V Output Ripple, 200 mV, CH3: Drain Voltage, 200 V, 5 ms / divFigure 19 – 115 VAC, Full LoadCH1: 48 V Output Ripple, 200 mV, CH3: Drain Voltage, 200 V, 5 ms / divFigure 20 – 230 VAC, Full LoadCH1: 48 V Output Ripple, 200 mV,CH3: Drain Voltage, 200 V,5 ms / div Figure 21 – 265 VAC, Full LoadCH1: 48 V Output Ripple, 200 mV,CH3: Drain Voltage, 200 V,5 ms / div10.6 Output Voltage Shutdown ProfileThe results below show that the power supply comfortably meets the power-supply hold-up requirements of the specification.Figure 22 – Shutdown Profile at Full Load, 120 VACUpper Ch1: 48 V output, 10 V / div,Lower Ch3: Bus Voltage 100 V / div,20 ms / div.Figure 23 – Shutdown Profile at Full Load, 120 VACUpper Ch1: 48 V output, 10 V / div,Lower Ch3: Bus Voltage 100 V / div,20 ms / div.11 Thermal TestThe thermal measurements were made at 85 VAC (which corresponds to the worst case efficiency of the power supply). Ambient temperature of the oven was 40’C. The power supply was connected to an electronic load (external to the chamber). A cardboard box was used around the power supply to prevent significant airflow. The whole setup was saturated at 40’C for an hour before beginning measurements.11.1 Thermal PerformanceFigure 24 – Thermal Performance of Key Power Supply ComponentsDelta Ch2Ch3Ch4Ch5 Time Amb1D1TOP246P CASE 0.140404040 0.940525540 140575941 240617043 440657345 841728751 1642829960 32438310564 64438510765 128438510765Figure 25 – Raw Test Data12 Conducted EMIThe EMI was tested with and without the output connected to earth-ground. Load was connected through an Ethernet cable to a resistive load (100 ohms). 12.1Conducted EMI PerformanceFigure 26 – 115 VAC - N1 - grounded output - full-loadFigure 27 – 115 VAC - L1 - grounded output - full-loadFigure 28 – 230 VAC - N1 – grounded output - full-loadFigure 29 – 230 VAC - L1 – grounded output - full-load13 Revision HistoryDate Author Revision Description & changes Reviewed September 12, 2005 RM 1.0 First Release VC / AMDER-97 21.7 W PoE Adapter September 12, 2005Page 31 of 31Power Integrations Tel: +1 408 414 9200 Fax: +1 408 414 9201For the latest updates, visit our Web site:Power Integrations may make changes to its products at any time. Power Integrations has no liability arising from your use of any information, device or circuit described herein nor does it convey any license under its patent rights or the rights of others. POWER INTEGRATIONS MAKES NO WARRANTIES HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.PATENT INFORMATIONThe products and applications illustrated herein (including circuits external to the products and transformer construction) may be covered by one or more U.S. and foreign patents or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations’ patents may be found at .The PI Logo, TOPSwitch,TinySwitch,LinkSwitch,and EcoSmart are registered trademarks of Power Integrations. PI Expert and DPA-Switch are trademarks of Power Integrations.© Copyright 2004, Power Integrations.。

TB67S109AFNAG(CPEL 大功率驱动芯片之王

TOSHIBA BiCD Integrated Circuit Silicon MonolithicTB67S109AFNAG CLOCK-in controlled Bipolar Stepping Motor Driver・・・・・・・・・・・・Pin assignment (TB67S109AFNAG)Please mount the exposed pad of the HSSOP package to heatsink .TB67S109A Block diagramFunctional blocks/circuits/constants in the block chart etc. may be omitted or simplified for explanatory purposes.Application NotesAll the grounding wires of the TB67S109A must run on the solder mask on the PCB and be externally terminated at only one point. Also, a grounding method should be considered for efficient heat dissipation.Careful attention should be paid to the layout of the output, VDD(VM) and GND traces, to avoid short circuits across output pins or to the power supply or ground. If such a short circuit occurs, the device may be permanently damaged.Also, the utmost care should be taken for pattern designing and implementation of the device since it has power supply pins (VM, RS, OUT, GND) through which a particularly large current may run. If these pins are wired incorrectly, an operation error may occur or the device may be destroyed.The logic input pins must also be wired correctly. Otherwise, the device may be damaged owing to a current running through the IC that is larger than the specified current.Pin explanations TB67S109AFNAGINPUT/OUTPUT equivalent circuit (TB67S109A)The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.Function explanation (Stepping motor)CLK FunctionEach up-edge of the CLK signal will shift the motor’s electrical angle per step.ENABLE functionis recommended.Step resolution setting and initial angle [Full step resolution][Half step resolution (Type B)]MO output shown in the timing chart is when the MO pin is pulled up. Timing charts may be simplified for explanatory purpose.MO output shown in the timing chart is when the MO pin is pulled up. Timing charts may be simplified for explanatory purpose. CWCCWStep setting and current percentageLO(Error detect signal) output functionWhen Thermal shutdown(TSD) or Over-current shutdown(ISD) is applied, the LO voltage will be switched to Low(GND) level.Decay functionADMD(Advanced Dynamic Mixed Decay) constant current controlThe Advanced Dynamic Mixed Decay threshold, which determines the current ripple level during current feedback control, is a unique value.fchopADMDth (Advanced Dynamic Mixed Decay threshold) Timing charts may be simplified for explanatory purpose.ADMD current waveform・When the next current step is higher :・mode.・When the next current step is lower :・OSCOutput transistor function modeVM VM VMCalculation of the Predefined Output CurrentFor PWM constant-current control, this IC uses a clock generated by the OSCM oscillator.The peak output current (Setting current value) can be set via the current-sensing resistor (RS) and the referencevoltage (Vref), as follows:Iout(max) = Vref(gain) ×Vref(gain) : the Vref decay rate is 1/ 5.0 (typ.)For example : In the case of a 100% setupwhen Vref = 3.0 V, Torque=100%,RS=0.51Ω, the motor constant current (Setting current value) will becalculated as:I out = 3.0V / 5.0 / 0.51Ω= 1.18 ACalculation of the OSCM oscillation frequency (chopper reference frequency)An approximation of the OSCM oscillation frequency (fOSCM) and chopper frequency (fchop)can be calculated by the following expressions.fOSCM=1/[0.56x{Cx(R1+500)}]………C,R1: External components for OSCM (C=270pF , R1=5.1kΩ => About fOSCM= 1.12MHz(Typ.)) fchop = fOSCM / 16………fOSCM=1.12MHz => fchop =About 70kHzIf chopping frequency is raised, Rippl of current will become small and wave-like reproducibility will improve.However, the gate loss inside IC goes up and generation of heat becomes large.By lowering chopping frequency, reduction in generation of heat is expectable.However, Rippl of current may become large.It is a standard about about 70 kHz. A setup in the range of 50 to 100 kHz is recommended.byanyis (exciting mode, operating time, and so on), ambient temperature, and heat conditions (board condition and so on).isavoidAC Electrical Specification (Ta = 25°C, VM = 24 V, 6.8 mH/5.7 Ω)Timing charts may be simplified for explanatory purpose.Package DimensionsWeight TBDg (typ.) P-HSSOP36-1116-0.65-001 (unit :mm)Notes on ContentsBlock DiagramsSome of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.Equivalent CircuitsThe equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.Timing ChartsTiming charts may be simplified for explanatory purposes.Application CircuitsThe application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially at the mass-production design stage.Toshiba does not grant any license to any industrial property rights by providing these examples of application circuits.Test CircuitsComponents in the test circuits are used only to obtain and confirm the device characteristics. These components and circuits are not guaranteed to prevent malfunction or failure from occurring in the application equipment.IC Usage ConsiderationsNotes on handling of ICs(1) The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded,even for a moment. Do not exceed any of these ratings.Exceeding the rating(s) may cause devicebreakdown, damage or deterioration, and may result in injury by explosion or combustion.(2)Use an appropriate power supply fuse to ensure that a large current does not continuously flow in thecase of overcurrent and/or IC failure. The IC will fully break down when used under conditions thatexceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormalpulse noise occurs from the wiring or load, causing a large current to continuously flow and thebreakdown can lead to smoke or ignition. To minimize the effects of the flow of a large current in thecase of breakdown, appropriate settings, such as fuse capacity, fusing time and insertion circuitlocation, are required.(3) If your design includes an inductive load such as a motor coil, incorporate a protection circuit into thedesign to prevent device malfunction or breakdown caused by the current resulting from the inrushcurrent at power ON or the negative current resulting from the back electromotive force at power OFF.IC breakdown may cause injury, smoke or ignition. Use a stable power supply with ICs with built-inprotection functions. If the power supply is unstable, the protection function may not operate, causingIC breakdown. IC breakdown may cause injury, smoke or ignition.(4) Do not insert devices in the wrong orientation or incorrectly. Make sure that the positive and negativeterminals of power supplies are connected properly.Otherwise, the current or power consumption may exceed the absolute maximum rating, andexceeding the rating(s) may cause device breakdown, damage or deterioration, and may result ininjury by explosion or combustion.In addition, do not use any device inserted in the wrong orientation or incorrectly to which current isapplied even just once.(5)Carefully select external components (such as inputs and negative feedback capacitors) and loadcomponents (such as speakers), for example, power amp and regulator.If there is a large amount of leakage current such as from input or negative feedback capacitor, the ICoutput DC voltage will increase. If this output voltage is connected to a speaker with low inputwithstand voltage, overcurrent or IC failure may cause smoke or ignition. (The overcurrent may causesmoke or ignition from the IC itself.) In particular, please pay attention when using a Bridge Tied Load(BTL) connection-type IC that inputs output DC voltage to a speaker directly.Points to remember on handling of ICsOvercurrent detection CircuitOvercurrent detection circuits (referred to as current limiter circuits) do not necessarily protect ICs under all circumstances. If the overcurrent detection circuits operate against the overcurrent, clear the overcurrent status immediately.Depending on the method of use and usage conditions, exceeding absolute maximum ratings may cause the overcurrent detection circuit to operate improperly or IC breakdown may occur before operation. In addition, depending on the method of use and usage conditions, if overcurrent continues to flow for a long time after operation, the IC may generate heat resulting in breakdown.Thermal Shutdown CircuitThermal shutdown circuits do not necessarily protect ICs under all circumstances. If the thermal shutdown circuits operate against the over-temperature, clear the heat generation status immediately.Depending on the method of use and usage conditions, exceeding absolute maximum ratings may cause the thermal shutdown circuit to operate improperly or IC breakdown to occur before operation.Heat Radiation DesignWhen using an IC with large current flow such as power amp, regulator or driver, design the device so that heat is appropriately radiated, in order not to exceed the specified junction temperature (TJ) at any time or under any condition. These ICs generate heat even during normal use. An inadequate IC heat radiation design can lead to decrease in IC life, deterioration of IC characteristics or IC breakdown. In addition, when designing the device, take into consideration the effect of IC heat radiation with peripheral components.Back-EMFWhen a motor rotates in the reverse direction, stops or slows abruptly, current flows back to the motor’s power supply owing to the effect of back-EMF. If the current sink capability of the power supply is small, the device’s motor power supply and output pins might be exposed to conditions beyond the absolute maximum ratings. To avoid this problem, take the effect of back-EMF into consideration in system design.RESTRICTIONS ON PRODUCT USE∙Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.∙This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.∙Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.∙PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MA Y CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.∙Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.∙Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.∙The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.∙ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITYWHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.∙Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.∙Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSESOCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.。

电源电路设计

电源电路设计.众所皆知,电源电路设计,乃是在整体电路设计中最基础的必备功夫,因此,在接下来的文章中,将会针对实体电源电路设计的案例做基本的探讨。

电源device电路※输出电压可变的基准电源电路(特征:使用专用IC基准电源电路)图1是分流基准(shunt regulator)IC构成的基准电源电路,本电路可以利用外置电阻与的设定,使输出电压在范围内变化,输出电压可利用下式求得:----------------------(1):内部的基准电压。

图中的TL431是TI的编号,NEC的编号是μPC1093,新日本无线电的编号是NJM2380,日立的编号是HA17431,东芝的编号是TA76431。

※输出电压可变的高精度基准电源电路(特征:高精度、电压可变)类似REF-02C属于高精度、输出电压不可变的基准电源IC,因此设计上必需追加图2的OP增幅IC,利用该IC的gain使输出电压变成可变,它的电压变化范围为,输出电流为。

※利用单电源制作正负电压同时站立的电源电路(特征:正负电压同时站立)虽然电池device的电源单元,通常是由电池构成单电源电路,不过某些情况要求电源电路具备负电源电压。

图3的电源电路可输出由单电源送出的稳定化正、负电源,一般这类型的电源电路是以正电压当作基准再产生负电压,因此负电压的站立较缓慢,不过图3的电源电路正、负电压却可以同时站立,图中的TPS60403 IC可使的电压极性反转。

※40V最大输出电压的Serial Regulator(特征:可以输出三端子Regulator IC无法提供的高电压)虽然三端子Regulator IC的输出电压大约是24V,不过若超过该电压时电路设计上必需与IC 以disk lead等组件整合。

图5的Serial Regulator最大可以输出+40V 的电压,图中D2 Zener二极管的输出电压被设定成一半左右,再用R7 VR1 R8 将输出电压分压,使该电压能与VZ2 的电压一致藉此才能决定定数。

可用于低电压二次侧同步整流的最新电源管理控制器

电话 :0 1 3 5 18 2 6 3 I 9

^f :www, t r i.o 徊 / / i esl r n cn

TC 79 3 输 出 2 A MHz N步降压一 压 另一个用于降压转换。L 3 8 运用单 升

型D / C C D 转换器

个 电感器和4 关同 步整流 模式 工作 , 开

件 非 常适 用 于 工 业 控 制 、汽 车 、 太 阳 能 和 大 功 率 电池 供 电系 统 等 众 多应 用 。 LTC3 1 使 用 了 标 称 3 3 1 3 . V的 电 源 、锂 离 子 / 合物 电池 提 供 3 聚 A输 出 电 流 ,或 用 两 节碱 性 / 镉 / 氢 金 属 电池 镍 镍 方 案 总 尺 寸 和 消 除 多 路 开 关 设 计 中 的 提 供 高达 l 输 出 电 流 。 L C 1 A的 T 3 1 在 3

- ■

w ■ tH

定频 率 工作 ,也 可用 其集 成 的锁 相 环

( PLL 同步 至 相 同范 围的 外部 时钟 。4 ) ~

3 V的 宽 输 入 范 围 、0 8 8 8 . ~3 v的输 出 范

的 外部 时 钟 同 步 ,从 而 进 一 步 减 小 解 决

围以 及工作模式之 间的 无缝转换 使该 器

理 以 及 同 步 唤 醒 特 性 有 助 于 最 大 限 度

采用单 电感器 同步 降压一 压型 升 D / C 制器 C D 控

地提高效率 。

U 2461 CC

转换效率。

It r I定 采 用 漏 TC 79

输 出 电 压 的 输 入 电压 工 作 。 大 功 率 升 压 源 电 压 和 降 压 电路 一 般 依 靠 变 压 器 或 两 个 DC 传 感 技 / D C 换 器 工 作 ,一 个 用 于 升 压 转 换 , 转 术 ,支 持 反 LLC 振 转 换 器 以 及 其 他 电 源架 构 ,从 谐 而 可 为 设 计 人 员提 供更 高 的 灵活 性 。 U CC 4 1 的 主要 特 性 与优 势 :小 2 6 0

正激同步整流芯片型号

正激同步整流芯片型号正激同步整流芯片是一种广泛应用于电源电子领域的功率电子器件,它能够实现高效率的能量转换和电流整形功能。

正激同步整流芯片通常由功率MOSFET和控制电路组成,其中功率MOSFET用于开关电源的电流整形,控制电路则用于控制功率MOSFET的开关时间和频率。

正激同步整流芯片的工作原理如下:当输入电压施加在正激同步整流芯片上时,控制电路会根据输入电压的变化情况,将开关信号发送给功率MOSFET。

功率MOSFET会根据接收到的开关信号,控制开关管的导通和关断,实现输入电压的整形和输出电流的控制。

通过不断地调整开关时间和频率,正激同步整流芯片能够实现高效率的电能转换和输出电流的精确控制。

正激同步整流芯片广泛应用于各种类型的电源电子设备中,特别是在电源适配器、电动车充电器、太阳能逆变器等产品中得到了广泛的应用。

正激同步整流芯片具有高效率、低功耗、高可靠性和稳定性等优点,能够提高电源的能量转换效率,降低系统的功耗和运行温度,延长设备的使用寿命。

下面将介绍几种常见的正激同步整流芯片型号:1. LT3748LT3748是一款高性能的正激同步整流芯片,采用了恒流模式控制和频率抖动技术,能够实现高效率的能量转换和精确的输出电流控制。

该芯片工作电压范围广,可适用于多种应用场景。

此外,LT3748还具有过压保护、过流保护和短路保护等多重保护功能,能够提高系统的安全性和稳定性。

2. IR11688SIR11688S是一款高性能的同步整流控制芯片,采用了先进的电流模式控制技术和内置的PWM发生器,能够实现高效率的电源转换和快速响应的输出电流控制。

该芯片具有内置的过流保护和短路保护功能,能够保护系统免受异常工作状态的损害。

3. UCC24610UCC24610是一款集成度高、性能稳定的同步整流控制芯片,采用了先进的电流模式控制和可调频率技术,能够实现高效率的电能转换和精确的输出电流控制。

该芯片还具有过流保护、过压保护和短路保护等多重保护功能,能够提高系统的可靠性和稳定性。

bq24610原理

bq24610原理

BQ24610是一款单片锂离子电池充电管理IC,用于提供电池

充电控制和保护功能。

其工作原理如下:

1. 当充电器连接后,BQ24610会检测电源适配器的电压,并

确定电池是否已连接。

2. BQ24610会根据充电模式和电池状态,选择恰当的充电算法。

充电模式可以是预充、恒流或恒压模式。

3. 如果电池电压低于预设阈值,BQ24610将会进入预充模式。

它会以较低的电流将电池充电至某个电压,以避免过高的充电电流对电池造成损害。

4. 一旦电池电压达到预设阈值,BQ24610将会进入恒流模式,以恒定的电流将电池充电至一定的容量。

这有助于快速充电电池。

5. 当电池电压接近所需的最大充电电压时,BQ24610将会进

入恒压模式,以恒定的电压继续将电池充电至所需的最大容量。

6. 在充电过程中,BQ24610会实时监测电池的温度,以确保

充电过程的安全性。

如果电池温度异常,则会停止充电。

7. 同时,BQ24610还具有过流、过压、过温和短路保护功能,以保护充电电路和电池免受损坏。

总之,BQ24610通过灵活的充电算法和全面的保护功能,实现了高效、安全的锂离子电池充电管理。

潘启panchip 2.4ghz无线收发soc芯片pan2416av产品说明书

PAN2416AV产品说明书2.4GHz无线收发SOC芯片V1.0PAN2416AV产品说明书2.4GHz单片高速无线收发SOC芯片概述PAN2416AV芯片是工作在2.400~2.483GHz世界通用ISM频段的单片无线收发芯片。

该芯片集成射频收发机、频率发生器、晶体振荡器、调制解调器和低功耗MCU等功能模块,并且支持一对多组网和带ACK的通信模式。

用户通过MCU的I/O口向芯片发出指令,芯片自动完成收发配置进行通信,并根据应答信息自动判断数据发送/接收是否成功,从而进行重发,丢包,继续发送和等待等操作,简化了用户程序。

发射输出功率、工作频道以及通信数据率均可配置。

PAN2416AV需要少量的外围器件,支持单层/双层印制电路板的方案。

主要特性1、功耗较低发射模式(2dBm)工作电流19mA;接收模式工作电流15mA;休眠电流2uA。

2、节省外围器件支持外围5个元器件,包括1颗晶振和少量电容;支持双层或单层印制板设计,可以使用印制板微带天线或者导线天线;芯片自带部分链路层的通信协议;配置少量的参数寄存器,使用方便。

3、性能优异250K/1M/2M bps模式的接收灵敏度为-91/-87/-83dBm;发射输出功率最大可达8dBm;抗干扰性好,接收滤波器的邻道抑制度高,接收机选择性较好。

4、集成MCU功能OTP:4K×16Bit;通用RAM:176×8Bit;MCU集成高精度12位ADC,内置WDT定时器、PWM输出、低压侦测电路等模块。

其它特性四线SPI 接口通信带自动扰码和CRC校验功能支持最大数据长度为32字节(两级FIFO)或者64字节(单级FIFO)SOP16封装1M / 2Mbps模式,需要晶振精度±40ppm 250kbps模式,需要晶振精度±20ppm 工作电压支持2.2~3.3V 工作温度支持-40~+85℃GFSK通信方式支持自动应答及自动重传支持RSSI检测功能10个GPIO中断源三路定时器应用方案无线鼠标电视和机顶盒遥控器无线游戏手柄遥控玩具常用遥控器智能家居版本修订时间更新内容相关文档V0.4 2016. 12 文字勘误V1.0 2017.09 文字修改目录1. 命名规则 (8)1.1 PAN2416AV命名规则 (8)1.2 PAN2416系列产品选择 (8)2. 主要电特性 (8)3. 极限最大额定值 (10)4. 系统结构方框图 (10)5. 引脚定义 (11)6. 芯片工作状态 (13)6.1 休眠模式 (14)6.2 待机模式-I(STB1) (14)6.3 待机模式-III(STB3) (14)6.4 待机模式-II(STB2) (14)6.5 接收模式 (14)6.6 发射模式 (14)7. 数据通信模式 (15)7.1 普通模式 (15)7.2 增强模式 (15)7.3增强发送模式 (16)7.4 增强接收模式 (16)7.5 增强模式下的数据包识别 (17)7.6 增强模式下的PTX和PRX的时序图 (17)7.7 增强模式下的接收端一对多通信 (17)7.8 DATA FIFO (19)7.9 中断引脚 (19)8. SPI控制接口 (19)8.1 SPI指令格式 (20)8.2 SPI 时序 (21)9. 控制寄存器 (22)10. 数据包格式描述 (32)10.1 普通模式的数据包形式 (32)10.2 增强模式的数据包形式 (33)10.3 增强模式的ACK包形式 (33)11. MCU寄存器 (34)11.1性能特性 (33)11.2系统结构框图 (34)11.3系统配置寄存器 (35)11.4在线串行编程 (36)12. 中央处理器(CPU) (37)12.1内存 (37)12.1.1程序内存 (37)12.1.2数据存储器 (41)12.2寻址方式 (43)12.2.1直接寻址 (43)12.2.2立即寻址 (43)12.2.3间接寻址 (43)12.3堆栈 (44)12.4工作寄存器(ACC) (45)12.4.1概述 (45)12.4.2 ACC应用 (45)12.5 程序状态寄存器(STATUS) (45)12.6 预分频器(OPTION_REG) (47)12.7程序计数器(PC) (48)12.8 看门狗计数器(WDT) (48)12.8.1 WDT周期 (48)12.8.2 看门狗定时器控制寄存器WDTCON (49)13. 系统时钟 (50)13.1 概述 (50)13.2 系统振荡器 (51)13.2.1 内部RC振荡 (51)13.3起振时间 (51)13.4振荡器控制寄存器 (51)14. 复位 (52)14.1上电复位 (52)14.2 掉电复位 (53)14.2.1掉电复位概述 (53)14.2.2掉电复位的改进办法 (54)14.3 看门狗复位 (54)15. 休眠模式 (55)15.1 进入休眠模式 (55)15.2 从休眠状态唤醒 (55)15.3 使用中断唤醒 (55)15.4 休眠模式应用举例 (56)15.5 休眠模式唤醒时间 (56)16. I/O端口 (57)16.1 PORTA (58)16.1.1 PORTA数据及方向控制 (58)16.1.2 PORTA模拟选择控制 (60)16.2 PORTB (60)16.2.1 PORTB数据及方向 (60)16.2.2 PORTB上拉电阻 (61)16.2.3 PORTB电平变化中断 (61)16.3 PORTC (62)16.3.1 PORTC数据及方向 (62)16.3.2 PORTC上拉电阻 (63)16.4 PORTE (63)16.4.1 PORTE数据及方向 (63)16.5 I/O使用 (64)16.5.1 写I/O口 (64)16.5.2 读I/O口 (64)16.6 I/O口使用注意事项 (65)17. 中断 (66)17.1 中断概述 (66)17.2 中断控制寄存器 (67)17.2.1 中断控制寄存器 (67)17.2.2 外设中断允许寄存器 (68)17.2.3 外设中断请求寄存器 (69)17.3 中断现场的保护方法 (70)17.4 中断的优先级,及多中断嵌套 (70)18. 定时计数器TIMER0 (71)18.1 定时计数器TIMER0概述 (71)18.2 TIMER0的工作原理 (72)18.2.1 8 位定时器模式 (72)18.2.2 8 位计数器模式 (72)18.2.3 软件可编程预分频器 (72)18.2.4 在TIMER0和WDT模块间切换预分频器 (72)18.2.5 TIMER0中断 (73)18.3 与TIMER0相关寄存器 (73)19. 定时计数器TIMER1 (74)19.1 TIMER1概述 (74)19.2 TIMER1 的工作原理 (74)19.3 TIMER1 预分频器 (74)19.4 TIMER1 中断 (74)19.5 TIMER1相关寄存器 (75)20. 定时计数器TIMER2 (75)20.1 TIMER2概述 (75)20.2 TIMER2的工作原理 (77)20.3 TIMER2相关的寄存器 (77)21. 模数转换(ADC) (79)21.1 ADC概述 (79)21.2 ADC配置 (79)21.2.1 端口配置 (79)21.2.2 通道选择 (80)21.2.3 ADC参考电压 (80)21.2.4 转换时钟 (80)21.2.5 ADC中断 (80)21.2.6 结果格式化 (80)21.3 ADC工作原理 (81)21.3.1 启动转换 (81)21.3.2 完成转换 (81)21.3.3 终止转换 (81)21.3.4 ADC在休眠模式下的工作原理 (81)21.3.5 A/D转换步骤 (81)21.4 ADC相关RAM (83)22. PWM模块 (85)22.1 PWM1 (85)22.2 PWM2 (86)22.3 PWM模式 (87)22.3.1 PWM周期 (88)22.3.2 PWM占空比 (88)22.3.3 PWM分辨率 (89)22.3.4 休眠模式下的操作 (89)22.3.5 系统时钟频率的改变 (89)22.3.6 复位的影响 (89)22.3.7 设置PWM操作 (89)23. MCU电气参数 (90)23.1 MCU DC特性 (90)23.2 MCU AC特性 (90)23.3指令一览表 (91)23.4 指令说明 (93)24. 典型应用电路(参考) (104)25. 封装尺寸 (105)26. 联系方式 (106)1. 命名规则1.1 PAN2416AV 命名规则图1.1 PAN2416系列产品命名规则1.2 PAN2416系列产品选择表1-1 PAN2416系列产品选择产品型号芯片版本 封装形式 PAN2416AV A V :SOP16 PAN2416AF A F :SOP142. 主要电特性表2-1 PAN2416AV 的RF 部分主要电特性参数值 特 性测试条件(VCC = 3V±5%,TA=25℃)最小 典型 最大 单位 休眠模式 2 uA 待机模式1 30 uA 待机模式3 650 uA 待机模式2 780 uA 发射模式 (-35dBm) 9 mA 发射模式 (-20dBm) 9.5 mA 发射模式 (0dBm) 16 mA 发射模式 (2dBm) 19 mA 发射模式 (8dBm) 30 mA 发射模式 (13dBm) 66 mA 接收模式 (250Kbps) 15 mA 接收模式 (1Mbps) 15.5 mA ICC接收模式 (2Mbps)16.5 mA 系统指标ƒOP 工作频率24002483MHzPLL res锁相环频率步径 1 MHz ƒXTAL晶振频率16 MHz DR码率0.25 2 Mbps ∆ƒ250K调制频偏@250Kbps 125 150 KHz ∆ƒ1M调制频偏@1Mbps 160 300 KHz ∆ƒ2M调制频偏@2Mbps 320 550 KHz FCH250K频道间隔@250Kbps 1 MHz FCH1M频道间隔@1Mbps 1 MHz FCH2M频道间隔@2Mbps 2 MHz发射模式指标PRF 典型输出功率 2 8 8 dBm PRFC 输出功率范围-35 8 dBmPBW1发射带数据调制的20dB带宽(250Kbps)500 KHzPBW2发射带数据调制的20dB带宽(1Mbps)1 MHzPBW3发射带数据调制的20dB带宽(2Mbps)2 MHz接收模式指标(注1)RX max误码率<0.1%时的最大接收幅度0 dBm RXSENS1 接收灵敏度(0.1%BER)@250Kbps-91 dBmRXSENS2 接收灵敏度(0.1%BER)@1Mbps-87 dBmRXSENS3 接收灵敏度(0.1%BER)@2Mbps-83 dBm接收模式邻道选择性C/I CO同频的通道选择性@250kbps 2 dBc C/I1ST第1相邻道选择性@250kbps -8 dBc C/I2ND第2相邻道选择性@250kbps -18 dBc C/I3RD第3相邻道选择性@250kbps -24 dBc C/I4TH第4相邻道选择性@250kbps -28 dBc C/I5TH第5相邻道选择性@250kbps -32 dBc C/I6TH第6相邻道选择性@250kbps -35 dBc C/I CO同频的通道选择性@1Mbps 10 dBc C/I1ST第1相邻道选择性@1Mbps 1 dBc C/I2ND第2相邻道选择性@1Mbps -18 dBc C/I3RD第3相邻道选择性@1Mbps -23 dBc C/I4TH第4相邻道选择性@1Mbps -28 dBc C/I5TH第5相邻道选择性@1Mbps -32 dBc C/I6TH第6相邻道选择性@1Mbps -35 dBc C/I CO同频的通道选择性@2Mbps 10 dBcC/I1ST第1相邻道选择性@2Mbps -6 dBcC/I2ND第2相邻道选择性@2Mbps -10 dBcC/I3RD第3相邻道选择性@2Mbps -22 dBcC/I4TH第4相邻道选择性@2Mbps -28 dBcC/I5TH第5相邻道选择性@2Mbps -34 dBc操作条件VDD 供电电压 2.2 3 3.3 VVSS 芯片地0 VV OH高电平输出电压VDD-0.3 VDD VV OL低电平输出电压VSS VSS+0.3 VV IH高电平输入电压VDD-0.3 VDD VV IL低电平输入电压VSS VSS+0.3 V*注1:在晶振16MHz的整数倍(如2416、2432MHz等)的频道及相邻正负1MHz的频道的接收灵敏度退化2dB;发射信号调制精度(EVM)退化10%。

各种电路拓朴的同步整流技术

3

3

3

C43 0805 102/100V

3

3

3

C44 0805 102/100V

R29

R30

R31

0603

0603

0603

4.7R

4.7R

4.7R

R32

R33

R34

0603

0603

0603

4.7R

4.7R

4.7R

C35

C36

C37

C38

C39

C40

C41

C42

106/50V 106/50V 106/50V 106/50V 106/50V 106/50V 106/50V 106/50V

检测栅驱动技术等)。

控制IC方式的同步整流

IR1167

主要特色有: * 适应反激变换器的DCM,CRM及CCM三种模式工

作。适应LLC式半桥。 * 最高500KHz工作频率。 * 2A源出5A漏入的输出驱动的能力。 * 栅驱动输出电压在10.7V到14.5V。 * Vcc电压从11.3V到20V。 * 50ns关断比例延迟。 * 直接检测MOSFET的源漏电压。

0603

33R 33R 33R

105/16V

VSS 7

C32 0805 2

471/100V

Trans4

LI 6

LR 8 LO HI 5 UCC27200

1 3

2 1

3 2 1

3 2 1

3 2 1

3 2 1

3 2

1

D3 3 Q1 2

1N4148

R8

0603 PBSS4350 VCC

2K

L4 18uH Inductor Iron Dot

同步整流器能够形成的一个高效解决方案

同步整流器能够形成的一个高效解决方案

几星期前,在机场候机时,我发现登机门前的很多座位上安装了内置的USB端口,这让我既惊讶又高兴。

如图1所示,除了两个AC插座外,大多

数座位有2个USB端口。

我记得,就在几年前,机场内的USB墙式插座还很少见。

而如今,内置USB充电器变得越来越常见,即使在咖啡厅和餐饮连锁店内也能看到它们的

身影。

目前,新建房屋都有USB墙式充电器,而对现有的房屋进行装修和翻新时,也会用USB充电器取代老式的AC插座。

很明显,免适配器充电提供

了快速充电的便利性,同时也提高了整洁度。

图1:机场候机楼座椅上的内置USB端口

考虑到USB墙式充电器的采用范围越来越广泛,我想在这里给出一些与

基本设计挑战和注意事项相关的观察所得。

最不寻常的挑战就是如何满足严

格的热性能要求,以符合安全规范。

与外部或便携式AC/DC适配器设计不同,。

BD246A-S中文资料

●Designed for Complementary Use with the BD245 Series●80 W at 25°C Case Temperature ●10 A Continuous Collector Current ●15 A Peak Collector Current●Customer-Specified Selections Availableabsolute maximum ratings at 25°C case temperature (unless otherwise noted)NOTES:1.This value applies for t p ≤ 0.3 ms, duty cycle ≤ 10%.2.Derate linearly to 150°C case temperature at the rate of 0.64 W/°C.3.Derate linearly to 150°C free air temperature at the rate of 24 mW/°C.4.This rating is based on the capability of the transistor to operate safely in a circuit of: L = 20 mH, I B(on) = -0.4 A, R BE = 100 Ω,V BE(off) = 0, R S = 0.1 Ω, V CC = -20 V .RATINGSYMBOL VALUE UNITCollector-emitter voltage (R BE = 100 Ω)BD246BD246A BD246B BD246C V CER-55-70-90-115VCollector-emitter voltage (I C = -30 mA)BD246BD246A BD246B BD246CV CEO-45-60-80-100VEmitter-base voltage V EBO -5V Continuous collector current I C -10A Peak collector current (see Note 1)I CM -15A Continuous base currentI B -3A Continuous device dissipation at (or below) 25°C case temperature (see Note 2)P tot 80W Continuous device dissipation at (or below) 25°C free air temperature (see Note 3)P tot 3W Unclamped inductive load energy (see Note 4)½LI C 262.5mJ Operating junction temperature range T j -65 to +150°C Storage temperature rangeT stg -65 to +150°C Lead temperature 3.2 mm from case for 10 seconds T L250°CSOT-93 PACKAGE(TOP VIEW)Pin 2 is in electrical contact with the mounting base.MDTRAAABC E 123NOTES:5.These parameters must be measured using pulse techniques, t p = 300 µs, duty cycle ≤ 2%.6.These parameters must be measured using voltage-sensing contacts, separate from the current carrying contacts.† Voltage and current values shown are nominal; exact values vary slightly with transistor parameters.electrical characteristics at 25°C case temperatureP ARAMETER TEST CONDITIONSMIN TYPMAXUNITV (BR)CEOCollector-emitter breakdown voltageI C = -30 mA (see Note 5)I B = 0BD246BD246A BD246B BD246C -45-60-80-100VI CESCollector-emitter cut-off current V CE =-55VV CE =-70V V CE =-90V V CE =-115 VV BE =0V BE =0V BE =0V BE =0BD246BD246A BD246B BD246C -0.4-0.4-0.4-0.4mA I CEO Collector cut-off current V CE = -30 V V CE = -60 V I B =0I B =0BD246/246A BD246B/246C-0.7-0.7mA I EBO Emitter cut-off current V EB = -5 V I C =0-1mA h FE Forward current transfer ratio V CE = -4 V V CE = -4 V V CE = -4 V I C = -1A I C = -3A I C = -10A (see Notes 5 and 6)40204V CE(sat)Collector-emitter saturation voltage I B = -0.3 A I B = -2.5 A I C = -3A I C = -10A (see Notes 5 and 6)-1-4V V BE Base-emitter voltageV CE = -4 V V CE = -4 V I C = -3 A I C = -10 A (see Notes 5 and 6)-1.6-3Vh feSmall signal forward current transfer ratio V CE = -10 V I C =-0.5A f =1kHz 20|h fe |Small signal forward current transfer ratioV CE = -10 VI C =-0.5Af =1MHz3thermal characteristicsP ARAMETERMINTYPMAX UNIT R θJC Junction to case thermal resistance 1.56°C/W R θJAJunction to free air thermal resistance42°C/Wresistive-load-switching characteristics at 25°C case temperatureP ARAMETER TEST CONDITIONS †MINTYP MAXUNIT t on T urn-on time I C = -1 A V BE(off) = 3.7 VI B(on) = -0.1 A R L = 20 ΩI B(off) = 0.1 A t p = 20 µs, dc ≤ 2%0.2µs t offT urn-off time0.8µs。

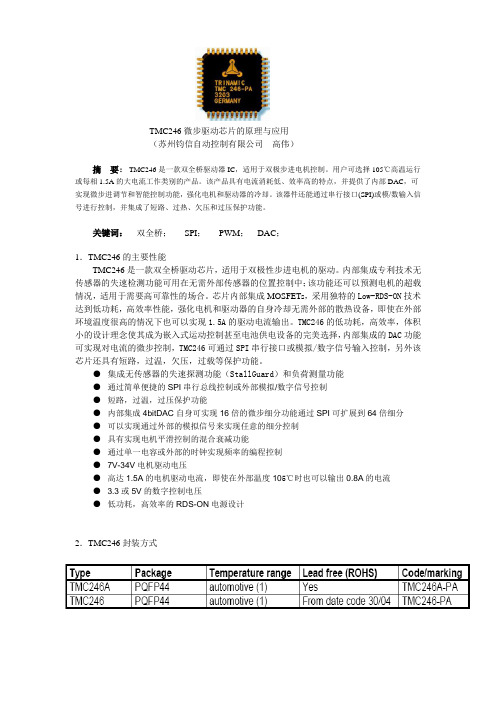

TMC246微步驱动芯片的原理与应用

TMC246微步驱动芯片的原理与应用(苏州钧信自动控制有限公司高伟)摘要:TMC246是一款双全桥驱动器IC,适用于双极步进电机控制。

用户可选择105℃高温运行或每相1.5A的大电流工作类别的产品。

该产品具有电流消耗低、效率高的特点,并提供了内部DAC,可实现微步进调节和智能控制功能,强化电机和驱动器的冷却。

该器件还能通过串行接口(SPI)或模/数输入信号进行控制,并集成了短路、过热、欠压和过压保护功能。

关键词:双全桥;SPI;PWM;DAC;1.TMC246的主要性能TMC246是一款双全桥驱动芯片,适用于双极性步进电机的驱动。

内部集成专利技术无传感器的失速检测功能可用在无需外部传感器的位置控制中;该功能还可以预测电机的超载情况,适用于需要高可靠性的场合。

芯片内部集成MOSFETs,采用独特的Low-RDS-ON技术达到低功耗,高效率性能,强化电机和驱动器的自身冷却无需外部的散热设备,即使在外部环境温度很高的情况下也可以实现1.5A的驱动电流输出。

TMC246的低功耗,高效率,体积小的设计理念使其成为嵌入式运动控制甚至电池供电设备的完美选择,内部集成的DAC功能可实现对电流的微步控制,TMC246可通过SPI串行接口或模拟/数字信号输入控制,另外该芯片还具有短路,过温,欠压,过载等保护功能。

●集成无传感器的失速探测功能(StallGuard)和负荷测量功能●通过简单便捷的SPI串行总线控制或外部模拟/数字信号控制●短路,过温,过压保护功能●内部集成4bitDAC自身可实现16倍的微步细分功能通过SPI可扩展到64倍细分●可以实现通过外部的模拟信号来实现任意的细分控制●具有实现电机平滑控制的混合衰减功能●通过单一电容或外部的时钟实现频率的编程控制●7V-34V电机驱动电压●高达1.5A的电机驱动电流,即使在外部温度105℃时也可以输出0.8A的电流● 3.3或5V的数字控制电压●低功耗,高效率的RDS-ON电源设计2.TMC246封装方式(1)IC没有按照汽车标准进行测试,但是完全可以用应在汽车行业依照其温度范围。

多输出反激式开关电源同步整流技术

多输出反激式开关电源同步整流技术

陈卓;王京梅;刘宇

【期刊名称】《电子科技》

【年(卷),期】2022(35)10

【摘要】在反激式开关电源中,传统二极管整流方式整流损耗大、效率低,多路输出交叉调节特性差。

针对该问题,文中采用同步整流技术对多输出反激式开关电源进行了研究。

对反激变换器同步整流技术及其驱动方式进行分析,选用基于漏源电压的同步整流控制芯片UCC24610设计了一款三输出反激式开关电源样机。

为使样机每路输出都得到调节,文中引入了加权电压反馈控制的方法。

将文中样机与二极管整流样机进行对比测试后发现,前者比后者的满载效率提高了7.6%。

研究结果表明,同步整流技术有效提高了样机输出电压精度,改善了多输出交叉调节特性。

【总页数】6页(P15-20)

【作者】陈卓;王京梅;刘宇

【作者单位】电子科技大学电子科学与工程学院

【正文语种】中文

【中图分类】TN86

【相关文献】

1.输出整流器占空比与反激式开关电源损耗关系的分析

2.单端反激式DC/DC变换器同步整流技术研究

3.兼容反激式和正激拓扑的同步整流控制器

4.多路输出反激式开关电源的设计

5.具同步整流的有源箝位反激双路输出DC/DC变换器设计

因版权原因,仅展示原文概要,查看原文内容请购买。

基于BQ24610的智能锂电池充电系统设计

2.B02461 0功能及特性

2.1引脚介 绍

ACN(引脚1):适配器 电流误差放大器 负输

入 。 (引脚2):适 配器 电流 误差放 大器 正

输入 。

(引脚3):AC或适 配器 电源 选择

输 出 。cE(引脚4):充 电使 能,逻辑 高 电平 输

入。高 电平 充电时能 ,低 电平停止充 电,它有

BQ24610是TI公 司生产 ,可 以实现 5V一28V

锂 电池充 电管理 。充 电控 制器与传统 的控 制器

相 比较,效率更 高 ,散热更少 ;充 电电压及 电

流 的准确度接近 百分之百 ,有助 于延长 电池 使 用寿命 ;集成型独 立解决方案 可提高设计 灵活

性 ,缩小整体解 决方案尺 寸,更有利于广泛 应

Key words:BQ24610;Intelligent charging;Oxygen generator

1.概 述

随着 移动 电话 、笔记 本电脑、平板 电脑等

众多便 携式 电子 设备的迅速普及 应用 ,与之配

套 的小型锂离子 电池、锂 聚合物 电池等二次 电

池的生产 及需求量 与 日俱增 ,特 别是锂离子 电

王庆辉

【摘要 】BQ24610是TI公司推 出的一教 比较 先进 的,面向5v至28V电压输入的锂 离子电池供电应用开关模 武独 立电池充 电器Ic。基于便携 武分子 筛制 氧机的电源管 理的设 计 需求,经过对一系列芯片原理、性能、参数设置的分析讨论 ,最后 我们选用BQ24610 ̄片作为该电源管理部分的主控制芯片 ,结合部分外 围电路 ,实现该设计的电源的 自动选择 、内部回路 补偿、内部软启动、动态 电源管理∞PM)、精确 的充电电流与电压调节、预充电、充 电终止、适配器 电流调节 以及充 电状态监控等功能。最后把该设 计制成实验板 ,经过反复调试 ,测试结果实现 了预期性 能指标 【关键词 】BQ24610;智 能充 电;制氧机

电源IC代换

发一些电源IC的代换资料DAP8A\DAP7A\LD7575\203D6\203X6\200D6可以直接代换,203d6是16v工作电压,而7575是30v ,代用要改启动电阻,可以用1200AP40直接代用OB2268,OB2269,DAP02,SG6841,SG5841DAP02\SG5841\2G684 1可以直接代换1200AP40\1200AP60\1203P60\1203AP10可以直接代换DM0465\CM0565\DM0565代换{要改电路}T O P246Y\T O P247Y可以直接代换。

大家来整理一个液晶电源的电源管理芯片集吧格式如下好了液晶品牌与型号电源管理芯片型号与封装可代换型号BENQ 71G+ 1200AP40 直插 1200AP10 1200AP60AOC 712SI EA1532A贴片三星型号忘记 DM0565R优派型号忘记 TOP245YNLG型号忘记 FAN7601飞利浦170s6 dap02alsz 贴片LG型号忘记 FAN7601 可以用LAF0001代飞利浦170s6 dap02alsz=sg6841美格WB9D7575PS清华同方XP911WD7575PS联想LXM -WL19AH LXM-WL19BH D7575PS(早期有的用:NCP1203D6) 联想LXM-17CH:1203D6方正17寸:1203D6与LD7575PS方正19寸:LD7575PSBenQ: FP94VW FP73G FP71G+S FP71G+G FP71GX等都是用:1200AP40 LG 22(南京同创):LAF001与STR W6252 。

LG 19寸:LAF001联想L193(福建-捷联代工):NCP1203D6PHILIPS 170S5FAN7601)PHILIPS 15寸(老产品):(FAN7601)LG型号忘记 FAN7601 可以用LAF0001代其他我知道的常用型号有SG6841DZ 贴片很多机器上用到SG5841SZ 贴片用SG6841DZ可以代用,DAP8A与203D6可代用还有LD7575可用203D6代用,只是1脚的对地电阻不同,LD7575是100K,203D6是24.1K,LP7552可用SG6841代用203D6 NCP1203D60R2 NCP1203D60R2G和DAP8A直接代换DAP02ALSZ与SG6841S可以互换1200AP40和1200AP60直接代换5S0765和DP104、DP704直接代换DP804和DP904直接代换2S0680和2S0880直接代换TEA1507和TEA1533直接代换LD7535兼容SG6848 (6849) / SG5701 / SG5848 /LD7535 (7550) / OB2262 (2263) / OB2278 (2279)RS2051LD7575和NCP1203、NCP1200 OB2268 SG5841 LD7552 OB2269 OB2268 RS2042CR6860兼容ACT30,CR6853兼容OB2263,CR6201兼容THX201,TFC718;CR6202兼容THX202,TFC719;CR6203兼容THX203,TFC718S。

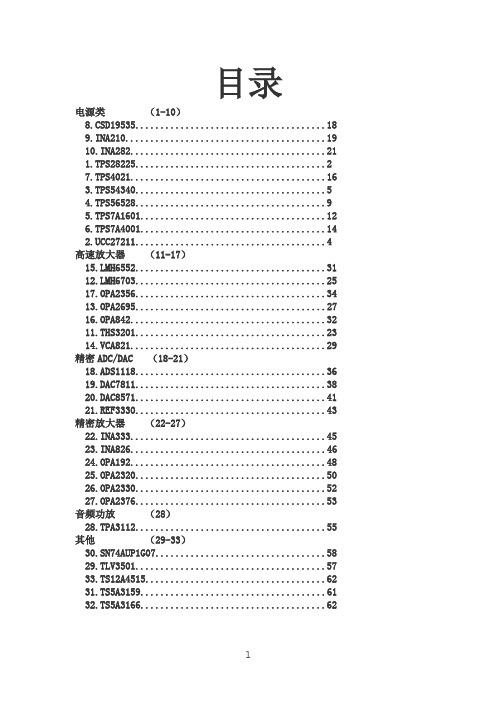

TI芯片资料

目录电源类(1-10)8.CSD19535 (18)9.INA210 (19)10.INA282 (21)1.TPS28225 (2)7.TPS4021 (16)3.TPS54340 (5)4.TPS56528 (9)5.TPS7A1601 (12)6.TPS7A4001 (14)2.UCC27211 (4)高速放大器(11-17)15.LMH6552 (31)12.LMH6703 (25)17.OPA2356 (34)13.OPA2695 (27)16.OPA842 (32)11.THS3201 (23)14.VCA821 (29)精密ADC/DAC (18-21)18.ADS1118 (36)19.DAC7811 (38)20.DAC8571 (41)21.REF3330 (43)精密放大器(22-27)22.INA333 (45)23.INA826 (46)24.OPA192 (48)25.OPA2320 (50)26.OPA2330 (52)27.OPA2376 (53)音频功放(28)28.TPA3112 (55)其他(29-33)30.SN74AUP1G07 (58)29.TLV3501 (57)33.TS12A4515 (62)31.TS5A3159 (61)32.TS5A3166 (62)零一.TPS282258引脚高频4A吸入电流同步MOSFET驱动器描述The TPS28225 and TPS28226 are high-speed drivers for N-channel complimentary driven power MOSFETs with adaptive dead-time control. These drivers are optimized for use in variety of high-current one and multi-phase dc-to-dc converters. The TPS28225/6 is a solution that provides highly efficient, small size low EMI emmissions.The performance is achieved by up to 8.8-V gate drive voltage, 14-ns adaptive dead-time control, 14-ns propagation delays and high-current 2-A source and 4-A sink drive capability. The 0.4-impedance for the lower gate driver holds the gate of power MOSFET below its threshold and ensures no shoot-through current at high dV/dt phase node transitions. The bootstrap capacitor charged by an internal diode allows use of N-channel MOSFETs in half-bridge configuration.The TPS28225/6 features a 3-state PWM input compatible with all multi-phase controllers employing 3-state output feature. As long as the input stays within 3-state window for the 250-ns hold-off time, the driver switches both outputs low. This shutdown mode prevents a load from the reversed- output-voltage.The other features include under voltage lockout, thermal shutdown and two-way enable/power good signal. Systems without 3-state featured controllers can use enable/power good input/output to hold both outputs low during shutting down.The TPS28225/6 is offered in an economical SOIC-8 and thermally enhanced low-size Dual Flat No-Lead (DFN-8) packages. The driver is specified in the extended temperature range of –40°C to 125°C with the absolute maximum junction temperature 150°C. The TPS28226 operates in the same manner as the TPS28225/6 other than the input under voltage lock out. Unless otherwise stated all references to the TPS28225 apply to the TPS28226 also.特性Drives Two N-Channel MOSFETs with 14-ns Adaptive Dead TimeWide Gate Drive Voltage: 4.5 V Up to 8.8 V With Best Efficiency at 7 V to 8 V Wide Power System Train Input Voltage: 3 V Up to 27 VWide Input PWM Signals: 2.0 V up to 13.2-V AmplitudeCapable Drive MOSFETs with ≥40-A Current per PhaseHigh Frequency Operation: 14-ns Propagation Delay and10-ns Rise/Fall Time Allow FSW - 2 MHzCapable Propagate <30-ns Input PWM PulsesLow-Side Driver Sink On-Resistance (0.4 ) Prevents dV/dT Related Shoot-Through Current 3-State PWM Input for Power Stage Shutdown Space Saving Enable (input) and Power Good (output) Signals on Same Pin Thermal Shutdown UVLO Protection Internal Bootstrap Diode Economical SOIC-8 and Thermally Enhanced 3-mm x 3-mm DFN-8 Packages High Performance Replacement for Popular 3-State Input Drivers APPLICATIONS Multi-Phase DC-to-DC Converters with Analog or Digital Control Desktop and Server VRMs and EVRDs Portable/Notebook Regulators Synchronous Rectification for Isolated Power Supplies参数零二.UCC27211120V 升压4A 峰值电流的高频高侧/低侧驱动器 描述UCC27210 和 UCC27211 驱动器基于常见的 UCC27200 和 UCC27201 MOSFET 驱动器,但是对性能进行了几项重大改进。

最优秀的同步整流驱动IC-UCC24610

绿色同步整流器控制IC—UCC24610在新一代绿色开关电源中,提高能效的关键技术是同步整流。

二次侧控制各种电路拓扑的同步整流器控制IC—UCC24610。

其为高性能控制器,即能驱动标准电平MOSFET,也可以驱动逻辑电平MOSFET,它即能大幅度减小整流的功耗,还能间接地减小初级侧的损耗。

采用漏源电压检测,最适于反激变换器和LLC谐振半桥,其最适于4.5V~5.5V的输出电压,它提供一个可调节的辅助触发滤波器调节时段自动地在轻载之下开关,而且SYNC输入还可用于CCM系统,保护特色在TON和EN/TOFF端,防止由于开路或短路造成的导通运行。

主要特色如下:◆直到600kHz工作频率;◆V DS MOSFET检测;◆ 1.6Ω漏入、2.0Ω源出的栅驱动阻抗;◆自动轻载管理;◆可调输入的保护特色;◆20ns典型的关断比例延迟;◆可以直接从5V输出电压供电;◆可以从休眠和轻载模式下同步唤醒;◆最少的外部元件;由UCC24610作反激变换器同步整流的电路如图1:图1 UCC24610 做反激电路同步整流的基本应用电路由UCC24610作LLC谐振半桥同步整流的电路如图2:图2 UCC24610 做半桥电路的同步整流驱动电路UCC24610的内部方框电路如图3:图3 UCC24610 的内部等效方框电路* UCC24610外部引脚功能如下:◆1PIN SYNC 栅关断同步端在SYNC端一个下降沿立即令栅电压为低电平,将MOSFET关断,异步端到源漏电压,而不管TON时段的状态,当功率变换器在CCM下工作时,在开关变换器的命令下必须关断控制MOSFET,将SYNC接到初级侧变换器的信号处,用一支高压电容隔离,或变压器隔离,或其他合适的元件,连续的低电平在SYNC端将会使栅电平一直为低。

◆2PIN EN/TOFF 使能功能和关断时段调节端,当V CC电平降到V CC(OFF)以下时,UCC24610处在UVLO模式,EN/TOFF端在IC内经过一支10K电阻接到GND,内部电流源也关断,当V CC超过V CC(ON)之后,10KΩ电阻被移去,电流源开启,此后,当EN/TOFF超过V EN(ON)时,UCC24610进入运行模式,而EN/TOFF降到V EN(OFF)以下时,UCC24610进入休眠模式,EN/TOFF端的电压还去调节可控制MOSFET的最小关断时间,EN/TOFF在IC内部由两个水平的电流源驱动,所以EN/TOFF端上的电压可以由从EN/TOFF端到GND 连接的电阻值决定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

绿色同步整流器控制IC—UCC24610在新一代绿色开关电源中,提高能效的关键技术是同步整流。

二次侧控制各种电路拓扑的同步整流器控制IC—UCC24610。

其为高性能控制器,即能驱动标准电平MOSFET,也可以驱动逻辑电平MOSFET,它即能大幅度减小整流的功耗,还能间接地减小初级侧的损耗。

采用漏源电压检测,最适于反激变换器和LLC谐振半桥,其最适于4.5V~5.5V的输出电压,它提供一个可调节的辅助触发滤波器调节时段自动地在轻载之下开关,而且SYNC输入还可用于CCM系统,保护特色在TON和EN/TOFF端,防止由于开路或短路造成的导通运行。

主要特色如下:◆直到600kHz工作频率;◆V DS MOSFET检测;◆ 1.6Ω漏入、2.0Ω源出的栅驱动阻抗;◆自动轻载管理;◆可调输入的保护特色;◆20ns典型的关断比例延迟;◆可以直接从5V输出电压供电;◆可以从休眠和轻载模式下同步唤醒;◆最少的外部元件;由UCC24610作反激变换器同步整流的电路如图1:图1 UCC24610 做反激电路同步整流的基本应用电路由UCC24610作LLC谐振半桥同步整流的电路如图2:图2 UCC24610 做半桥电路的同步整流驱动电路UCC24610的内部方框电路如图3:图3 UCC24610 的内部等效方框电路* UCC24610外部引脚功能如下:◆1PIN SYNC 栅关断同步端在SYNC端一个下降沿立即令栅电压为低电平,将MOSFET关断,异步端到源漏电压,而不管TON时段的状态,当功率变换器在CCM下工作时,在开关变换器的命令下必须关断控制MOSFET,将SYNC接到初级侧变换器的信号处,用一支高压电容隔离,或变压器隔离,或其他合适的元件,连续的低电平在SYNC端将会使栅电平一直为低。

◆2PIN EN/TOFF 使能功能和关断时段调节端,当V CC电平降到V CC(OFF)以下时,UCC24610处在UVLO模式,EN/TOFF端在IC内经过一支10K电阻接到GND,内部电流源也关断,当V CC超过V CC(ON)之后,10KΩ电阻被移去,电流源开启,此后,当EN/TOFF超过V EN(ON)时,UCC24610进入运行模式,而EN/TOFF降到V EN(OFF)以下时,UCC24610进入休眠模式,EN/TOFF端的电压还去调节可控制MOSFET的最小关断时间,EN/TOFF在IC内部由两个水平的电流源驱动,所以EN/TOFF端上的电压可以由从EN/TOFF端到GND 连接的电阻值决定。

EN/TOFF在内部驱动两倍电流I EN-STAR去实现使能阈值电压V EN(ON),然后进入正常的运转模式水平(I EN-ON),再调节TOFF时间,换句话说,所希望的EN/TOFF电压可以用一个外部电流源强制,调节TOFF 时间可以抑制栅GATE端的输出,达到所希望的间隔,并防止由谐振或关断噪声造成的可能的虚假触发。

TOFF时段在VD电压超过1.5V时触发,之后GATE端从高电平到低电平。

◆3PIN TON 导通时段调节端,调节最小的导通时段,可以用从TON到GND接一支电阻来完成。

当控制的MOSFET栅导通时,一些振铃噪声会产生出来,最小导通时段消隐VD-VS比较器,保持所控制的MOSFET处在导通状态,至少可以调节最小时间,这个时间还决定轻载时的关断点。

在TON时间超出前,如果VD-VS降到5mV阈值以下。

控制器传输在下一个开关周期进入轻载模式。

在TON超出后,当VD-VS降到5mV以下时,器件在下一个开关周期仍旧处在运行工作状态。

◆4PIN VCC IC供电端,接一个直流电压给VCC,用一支0.1μF电容旁路到GND,PCB轨迹要最短,VCC供电给UCC24610内全部电路,欠压锁定比以上才工作,在VCC降到VCC(OFF)以下时安全地较器可令VCC到VCC(ON)关断,当VCC降到VCC(OFF)以下出现时,GATE端立即降低,EN/TOFF也立即给10K电阻接到GND。

◆5PIN GATE 外部MOSFET的栅驱动端,通过小阻值电阻接到所控的MOSFET,引线要最短,以实现最佳的开关特性。

GATE输出可达到1A峰值,源出电流、漏入电流可达到2A,即驱动足够大的MOSFET,在休眠模式或UVLO时,GATE端立即降到GND,大约只有1.6Ω,当VCC=1.1V时,GATE端立即到GND,大约为80Ω。

◆6PIN GND IC的公共端,对GATE驱动器为参考电平,UVLO比较器EN/TOFF比较器,EN/TOFF时段,TON时段,外接一0.1μF瓷介电容旁路从VCC 到GND。

◆7PIN VS端源检测电压端,将此端接到外部所控MOSFET的源极,要以最短路径,要有最小的等效串联电感。

◆8PIN VD端漏检测电压端,将此端接到外部所控MOSFET的漏极,要以最短路径,最小的等效串联电感,VD必须大于1.5V,TOFF时段必须在器件打开保险之前能控制MOSFET在下个周期导通。

一旦保险打开控制MOSFET 在VD降到150mV低于VS时导通。

在栅驱动输出为高时,TON时段被触发,GATE仍旧为高电平,至少要超过所调解的TON时段。

除非在SYNC 输入的脉冲被检测。

在TON超出后,GATE输出在VD-VS电压减到5mV 时关断,在TON超出前,如果VD-VS减小到5mV。

控制器进入轻载模式,GATE脉冲在下一个开关周期被抑制。

当VD电压增加到1.5V时,TOFF时段被触发,防止GATE输出,从导通进入TOFF时段。

◆9PIN IC底部散热端(仅QFN封装),此端接至PCB板的GND以改善散热特性。

* UCC24610共有五种工作状态,如下:UVLO模式的阈值时,或者降到UVLO阈值以下时,器当VCC电压没有达到VCC(ON)件工作在低功耗的UVLO模式。

在此模式中,多数内部功能被禁止,ICC电流低于100μA。

在这种模式下,EN电流源关断,内部10KΩ电阻接于EN/TOFF 端到GND之间,EN/TOFF上的电压不相干。

GATE端输出为低,对VCC>1.2V,一直如此,当VCC增加超过VCC(ON)阈值时,UVLO模式非常像休眠模式,除水平。

非VCC电流达到ICC(start)Sleep模式休眠模式为低功耗模式,与UVLO模式很相似,在由外部控制强制V EN低于V EN(off)阈值进入此模式。

休眠模式可以用来减少器件工作损耗到低于1mW,VCC电流减少到I CC(stby)水平,外部控制被任何内部时间条件取代,且立即强制GATE输出为低电平,进入休眠模式,许多内部电路关闭,以减小功耗,当V EN 复原到V EN(ON)阈值以上时,器件走出休眠模式,同时在大约25μS后进入轻载模式,并允许内部电路重新加电到设置状态。

RUN模式运行模式是控制器正常工作模式,此时已不在UVLO或休眠或轻载模式。

在此模式下,VCC电流比较高,因为全部电路都在工作,GATE输出去驱动所控制的MOSFET作同步整流,VCC电流为I CC(ON)的总和加上驱动负载及GATE 输出所必须的平均电流,GATE输出占空比取决于系统线路及负载条件,可调的TON和TOFF时段,以及同步脉冲的时段。

Light-load模式轻载模式是一个低功耗工作模式,它很像休眠模式,除非这种模式自动进入基于内部时基条件,轻载模式自动减少在轻载条件下的开关损耗。

它用抑制GATE输出脉冲的方法执行。

无论何时都去检测同步导通时间,令其少于可调整的最小导通时间(TON),VCC电流减小到I CC(ON)的水平。

此时,轻载模式中,MOSFET的体二极管导通时间仍旧是连续监视的,此时,检测的时间超出TON 时,器件在下一个开关周期回到运行模式。

故障模式及其它保护功能故障模式是一种自行保护的工作模式,控制器此时在可能的端子上检测出单一故障,在此模式中,器件进入关断状态(但不是休眠)器件驱动GATE输出为低电平,特定条件下,在R TON>301KΩ或R TON<8.7KΩ时,进入故障模式。

故障模式防止进入过度条件,或不明确的导通时间,以及超出TON条件下的电流。

相似的保护也提供给EN/TOFF端,在故障没检测出来时,如果这段TOFF 变成开路,有最小0.65μs的时间,如果短路到GND,器件进入休眠模式,此外如果SYNC输入连续为低于触发电平阈值电压,GATE输出为低即进入此阶段,SYNC仍旧为此条件。

* 应用信息正常工作UCC24610为绿色电源的同步整流器控制器。

在VCC从0V增加时,开始进入UVLO模式,从EN/TOFF端的使能电流被禁止,直到VCC超过VCC(ON)的阈值,保持在激活状态,直到VCC超过VCC(OFF)阈值。

EN/TOFF端上的电压决定控制器使能与否。

控制器工作在正常运转模式下,此时使能电压(V EN)超过使能阈值V EN(ON),一直工作到V EN超出V EN(OFF)阈值。

在控制器使能后,V EN调节最小关断时间,它反比于V EN电压,两种状态的使能电流允许一个低值电阻R EN(OFF)产生足够超出V EN(ON)的电压,进入启动状态。

用一支电阻从EN/TOFF接到GND产生V EN。

V EN的值基于I EN的大小,I EN流过此电阻,见图4。

或者V EN由内部电压源驱动提供超过V EN(ON)的电压,100ns,然后开始启动,并达到设置水平。

图4 UCC24610 的EN/TOFF端电平变化曲线UCC24610作为同步整流控制器,用比较MOSFET的漏源电压来决定SR-MOSFET的导通时间,应对导通阈值和关断阈值。

GATE输出在V DS超过V TH(ON)时为高电平。

在V DS低于V TH(OFF)时为低电平,如图5。

图5 UCC24610 检测VDS电平给出栅驱动脉冲注意,因为有限的比例和上升时间,SR-MOSFET体二极管可能在V TH(ON)被超出后导通短暂时间,还有体二极管在V TH(OFF)被超出后会流过残余电流。

波形如图5中描述,在反激电路中同步整流工作期间可以监视。

当然,在电路中实际波形很难像图5中这样清晰,寄生电感和寄生电容造成在弯曲点处的谐振尖峰。

UCC24610有控制时段并调节选择,帮助防止振铃,使之合适地工作,图6示出更实际的波形及内部控制时段。

图6 UCC24610 的栅驱动波形随时序的变化最小导通时间Ton,用Ton端到地的电阻调节,消隐关断时的谐振,防止GATE由于噪声和振铃从假的穿过V TH(OFF)开始关断Ton由GATE导通被触发,参看下面Ton调节部分。

最小关断时间用从2PIN到GND的电阻来调节,去消除开启时的谐振,防止GATE由于超出的C oss谐振振铃,从假的穿过V TH(ON)开始导通,Toff由V DS 跨过V THARM在GATE关断后被触发。