VHDL语言的顺序语句.

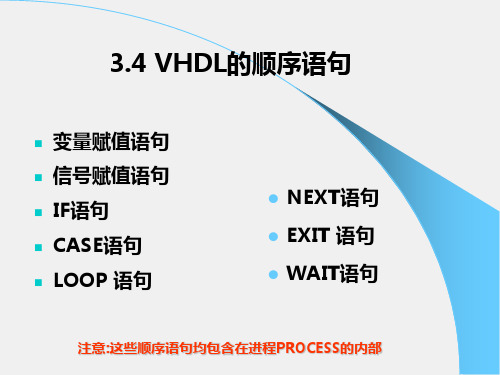

3.4 VHDL顺序语句

IS

Y<=input (0); Y<=input (1); Y<=input (2); Y<=input (3);

IF语句不仅可用于选择器设计,还可用于比较 器,译码器等进行条件控制的逻辑设计。IF语句 中至少应有一个条件句,条件句必须由布尔表达 式构成,条件表达式中能使用关系运算操作及逻 辑运算操作的组合表达式。 IF语句颠倒条件判别次序,会引起在综合时逻辑 功能的变化,即IF语句判别条件不可颠倒。 IF语句中,先处理最起始的条件;如果不满足, 再处理下一个条件。一般把条件约束最多的作为 起始条件。

例:case语句的误用 signal value :integer range 0 to 15; signal out_1:bit; case value is end case; ---缺少when条件语句

case value is ---分支条件不包含2到15 when 0 =>out_1<=‘1’; when 1 =>out_1<=‘0’; end case

ARCHITECTURE ART OF MUX41 IS

SIGNAL S :STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN S<=S1 & S2;

PROCESS(S,A,B,C,D) IS

BEGIN CASE S IS

WHEN "00"=>Z<=A;

WHEN "01"=>Z<=B; WHEN "10"=>Z<=C;

进 程 中 的 变 量 赋 值

RTL 电路

LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY DFF3 IS PORT ( CLK,D1 : IN STD_LOGIC ; Q1 : OUT STD_LOGIC ) ; END DFF3; ARCHITECTURE bhv OF DFF3 IS SIGNAL A,B : STD_LOGIC ; BEGIN PROCESS (CLK) BEGIN IF CLK'EVENT AND CLK = '1' THEN A <= D1 ; B <= A ; Q1<= B ; END IF; END PROCESS ; END bhv;

VHDL顺序语句(Sequential)

17

…… L2: loop a:=a+1; exit L2 when end …… loop L2; a >10;

18

2)for

…

loop 语句

loop

[标号]:for 循环变量 in 离散范围 顺序处理语句; end l 内部自动声明的局部量, 仅在 loop 内可见;不需要指定其变化方式。 ② 离散范围必须是可计算的整数范围: 整数表达式 to 整数表达式 整数表达式 downto 整数表达式

PROCESS BEGIN -- sequential statements WAIT ON (a,b) ; END PROCESS;

38

二、块语句

块语句将一系列并行描述语句进行组合,目 的是改善并行语句及其结构的可读性。可使结构 体层次鲜明,结构明确。 语法如下:

标记:block [( 块保护表达式 )]

when 值|值|值|…|值 => 顺序处理语句;

以上三种方式的混合;

when others => 顺序处理语句;

14

Case 语句使用注意:

1)分支条件的值必须在表达式的取值范围内。 2)两个分支条件不能重叠。 3)CASE语句执行时必须选中,且只能选中一 个分支条件。

4)如果没有others分支条件存在,则分支条

{ 块说明项 } begin { 并行语句 } end block [ 标记 ];

39

1、块语句的使用不影响逻辑功能 以下两种描述结果相同: 描述一: a1: out1<=‘1’ after 2 ns; a2: out2<=‘1’ after 2 ns; a3: out3<=‘1’ after 2 ns; 描述二: a1: out1<=‘1’ after 2 ns; blk1: block begin a2: out2<=‘1’ after 2 ns; a3: out3<=‘1’ after 2 ns; end block blk1;

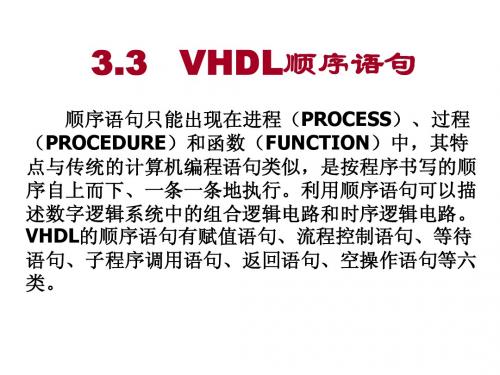

3.3 VHDL顺序语句

顺序语句只能出现在进程( )、过程 顺序语句只能出现在进程(PROCESS)、过程 )、 (PROCEDURE)和函数(FUNCTION)中,其特 )和函数( ) 点与传统的计算机编程语句类似, 点与传统的计算机编程语句类似,是按程序书写的顺 序自上而下、一条一条地执行。 序自上而下、一条一条地执行。利用顺序语句可以描 述数字逻辑系统中的组合逻辑电路和时序逻辑电路。 述数字逻辑系统中的组合逻辑电路和时序逻辑电路。 VHDL的顺序语句有赋值语句、流程控制语句、等待 的顺序语句有赋值语句、 的顺序语句有赋值语句 流程控制语句、 语句、子程序调用语句、返回语句、 语句、子程序调用语句、返回语句、空操作语句等六 类。

PROCESS(a) ( ) BEGIN IF (a(7)=‘0’) THEN y<=”111”; ( ) ) ; ELSIF (a(6)=’0’) THEN y<=”011”; ELSIF (a(5)=’0’) THEN y<=”101”; ELSIF (a(4)=’0’) THEN y<=”001”; ELSIF (a(3)=’0’) THEN y<=”110”; ELSIF (a(2)=’0’) THEN y<=”010”; ELSIF (a(1)=’0’) THEN y<=”100”; ELSE y<=”000”;

IF语句 一、IF语句 格式1 格式1:IF 条件句 Then 顺序语句; 顺序语句; IF; END IF; 格式2:IF 条件句 Then 格式2 顺序语句; 顺序语句; ELSE 顺序语句; 顺序语句; IF; END IF;

格式3:IF 条件句 Then 格式3 顺序语句; 顺序语句; ELSIF 条件句 Then 顺序语句; 顺序语句; … ELSE 顺序语句; 顺序语句; IF; END IF;

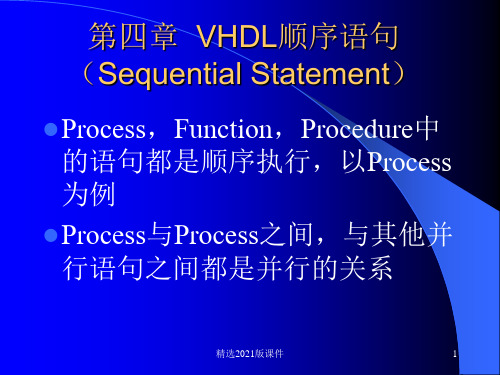

第四章 VHDL顺序语句

…

a_less_then_b <=false;

for i in 1 downto 0 loop

IF (a(i)=‘1’ AND b(i)=‘0’ THEN

a_less_then_b <=false;

EXIT ;

Elsif (a(i)=‘0’ AND b(i)=‘1’ THEN

a_less_then_b <=true;

END CASE;

END PROCESS;

END activ;

精选2021版课件

17

例:

signal C: Integer range 1 to 20;

signal Out1: ( '0', '1', '2', '3');

process ( C )

begin

case C is

when 1 => Out1 <= '0';

26

loop2: loop B := B+1; next loop2 when B<10;

.

. end loop loop2;

精选2021版课件

27

(5) exit语句

exit语句使得从循环标号所标明的循环中退出。

exit ;

exit loop标号;

exit loop标号 when 条件表达式

精选2021版课件

31

p1: process --( )

begin

…

wait on s1;

…

wait on s2;

…

wait on s1;

…

end process p1;

4、VHDL顺序语句

<法二:使用类型转换函数>

<例5.2.2>二选一数据选择器

如何描述 四选一数 据选择器?

<例5.2.3>8-3优先编码器

输入 输出 a7 a6 a5 a4 a3 a2 a1 a0 y2 y1 y0 0 x x x x x x x 1 1 1 1 0 x x x x x x 1 1 0 1 1 0 x x x x x 1 0 1 1 1 1 0 x x x x 1 0 0 1 1 1 1 0 x x x 0 1 1 1 1 1 1 1 0 x x 0 1 0 1 1 1 1 1 1 0 x 0 0 1 1 1 1 1 1 1 1 0 0 0 0

代码:

练习:3-8译码器

输入 a2 a1 a0 1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 0 0 0

y7 1 0 0 0 0 0 0 0

y6 0 1 0 0 0 0 0 0

y5 0 0 1 0 0 0 0 0

输出 y4 y3 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0

顺序语句可以包含若干条语句顺序语句可以包含若干条语句格式格式22中可以有若干个中可以有若干个elsifelsif结构结构if语句可以嵌套使用语句可以嵌套使用p111p111例例524524521法一

《VHDL顺序语句》

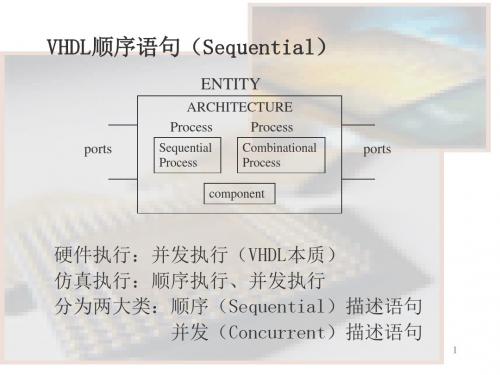

VHDL语句分为两大类:顺序语句和并行语句。 顺序语句:按照语句的前后书写顺序执行。 并行语句:执行顺序与语句的书写顺序无关。 顺序语句只能写在进程、子程序中。

作业

P126第6题(1)

“循环变量”为临时变量,不必事先声明;不 能被赋值;在loop语句中不能有与之重名的标识 符。 循环范围的写法:“初值 to 终值”或“初值 downto 终值”。

第四讲VHDL的顺序语句

architecture one of exam4_2 is begin process(clk,rst) variable q:integer range 0 to 9; begin if rst='1' then q:=0; co<='0'; elsif clk'event and clk='1' then if q=9 then q:=0; 时钟上升沿 co<='1'; else q:=q+1; co<='0'; end if; end if; y<=q; end process; end one;

library ieee; use ieee.std_logic_1164.all; entity exam4_2 is port(clk,rst:in std_logic; y:out integer range 0 to 9; co:out std_logic); end exam4_2;

演示异步清零

2、编写8位二进制加法计数器的VHDL源程序,并仿 真验证设计结果。 提示:设输入为时钟脉冲clk,复位信号rst,计数输出 为y[7..0],计数满信号为co.8位二进制计数器的计数111111”,则 计数值清0,计数满信号输出高电平1. 否则 计数值加1,计数满信号输出高电平0 结束。

语句构成,因此是按顺序执行的。

进程语句的格式为: [进程名:]process[(敏感信号表)] [is] [说明语句;] begin 顺序描述语句;

end process [进程名];

进程名用来区分不同的进程,因此,不 同的进程,进程名不能相同。但进程名 也可以缺省。 敏感信号表中列出启动该进程的敏感信 号。敏感表中任一信号发生变化,都会 触发该进程,引起进程内部的顺序语句 被执行。

4.1VHDL语言顺序描述语句

VHDL顺序语句

例:

注意变 量I初 始化和 在循环 中的加1 处理

8位奇偶校验电路 architecture abc of example is begin

PROCESS(a) variable tmp:std_logic;

begin tmp:=‘0’; i:=0; WHILE (i<8) LOOP tmp:=tmp XOR a(i); i:=i+1; END LOOP; Y<=tmp;

格式: 标号:FOR 循环变量 IN 循环次数范围 LOOP 顺序处理语句; …… END LOOP;

注意: 循环变量只是一个临时变量,由LOOP语句自动定

义,不需预先定义; LOOP语句范围内不要再使用其它与该循环变量同

名的标识符。 循环次数完成后程序自动退出循环。

VHDL顺序语句

例:

能否定 义为信

VHDL顺序语句

3、CASE语句

格式:

Case 表达式 Is WHEN 选择值 =>顺序处理语句;

…… WHEN 选择值 =>顺序处理语句; WHEN OTHERS =>顺序处理语句; End case;

注意: CASE语句至少包含一个条件句; CASE语句中条件表达式的值必须列举穷尽,但不

能重复; 无法穷举,用OTHERS表达。

注意:IF 语句隐含有优先级的关系,可用来设计具有优 先权的电路 。

VHDL顺序语句

例:

不需穷 尽所有

情况

四选一数据选择器 architecture abc of example is signal sel:std_logic_vector(1 downto 0); begin

sel<=b &a; process(sel) begin

第五节 VHDL的基本描述语句

第五节VHDL的基本描述语句----顺序语句顺序语句是相对于并行语句而言的。

执行顺序与它们的书写顺序基本一致。

只能出现在进程(Process)和子程序中。

用于实现模型的算法部分。

VHDL中的顺序语句与传统的软件编程语言中的语句的执行方式十分相似。

VHDL的顺序语句主要有六类:赋值语句流程控制语句等待语句子程序调用语句返回语句空操作语句本节介绍这六类顺序描述语句及其功能。

一、赋值语句(TOP)信号赋值语句、变量赋值语句两种。

语法格式如下:变量赋值目标:= 赋值源信号赋值目标<= 赋值源赋值目标是欲赋值的对象,是信号或变量,可以表现为文字、标志符、数组等;赋值源可以是数值、逻辑运算或者算术运算表达式。

由信号赋值语句的语法格式可见,它与并行信号赋值语句相似。

VHDL规定赋值目标与赋值源的数据类型必须严格一致。

变量赋值与信号赋值的区别在:变量具有局部特征,它的有效性只在所定义的一个进程或一个子程序中,并且其赋值行为立即发生;信号则有全局性特征,它可以在一个设计实体的各单元之间传送数据,也可以与其它的实体进行通信,并且其赋值行为不立即发生,而是发生在一个进程结束的时候。

二、流程控制语句(TOP)流程控制语句通过条件控制开关决定程序的流程。

流程控制语句有:IF语句、CASE语句、LOOP语句、NEXT语句和EXIT语句等五种。

(一)IF语句IF 语句根据语句中所设置的条件执行指定的顺序语句。

IF 语句有如下三种语法格式:1.第一种IF语句IF 条件句Then{顺序语句}END IF;2.第二种IF语句IF 条件句Then{顺序语句}ELSE{顺序语句}END IF;3.第三种IF语句IF 条件句Then{顺序语句}ELSIF 条件句Then{顺序语句}ELSE{顺序语句}]END IF;IF语句中的条件必须是BOOLEAN表达式。

IF语句的条件产生的结果是TRUE 或FALSE。

IF 语句的每个分支可以有一个或者多个顺序语句。

VHDL顺序语句

BEGIN PROCESS(a) variable tmp:std_logic;-BEGIN tmp:='0'; FOR n IN 0 TO 7 LOOP tmp := tmp XOR a(n); END LOOP ; y <= tmp; END PROCESS;

END CASE;

9

算术逻辑单元的VHDL描述,在信号opcode的控制下可分别完成加、减、相等或不相等 比较操作

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY alu IS

PORT( a, b : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

end process; end rtl;

4

5

5.2.2 CASE语句

CASE语句的结构如下:

CASE 表达式 IS When 选择值 => 顺序语句; When 选择值 => 顺序语句; ... END CASE ;

多条件选择值的一般表达式为: 选择值 [ |选择值 ]

选择值的计算结果必须是整型、枚举型或枚举型数组;选择为静 态表达式或动态范围,最终的选择是可以是"others",选择不能重 叠,若无"others"选择,那末选择必须覆盖表达式的所有可能值

opcode: IN STD_LOGIC_VECTOR (1 DOWNTO 0);

VHDL语言的顺序语句

C、LOOP 语句

(1)单个LOOP语句,其语法格式如下: [标号:] LOOP 顺序语句; END LOOP [标号 ]; 用法示例: L2 :LOOP a := a+1; EXIT L2 WHEN a >10 ; -- 当a大于10时跳出循环 END LOOP L2; ...

(2)FOR… LOOP语句,语法格式如下: [标号:] FOR 循环变量 IN 初值 TO 终值 LOOP 顺序语句; END LOOP [标号];

顺序语句是相对于并行语句而言的,其特点 是按程序书写的顺序自上而下、一条一条地执行 的。利用顺序语句可以描述数字逻辑系统中的组 合逻辑电路和时序逻辑电路。 顺序语句只能出现在进程(PROCESS)、 过程(PROCEDURE)、 函数(FUNCTION) 中。在同一设计实体中,所有的进程是并行执行 的,每个进程内部是顺序执行的。

3、等待语句

WAIT; WAIT ON 信号表; WAIT UNTIL 条件表达式; WAIT FOR 时间表达式;

WAIT语句

EXIT有四种用法,其语法格式如下:

-- 第一种语句格式,表示永远挂起 -- 第二种语句格式 -- 第三种语句格式 -- 第四种语句格式, 超时等待语句

用法示例1: SIGNAL s1,s2 : STD_LOGIC; ... PROCESS BEGIN ... WAIT ON s1,s2 ; END PROCESS ;

顺序语句1;

顺序语句2;

ELSIF 条件2 … 第三种 ELSIF 条件n ELSE END IF;

THEN

顺序语句n;

顺序语句n+1;

例

用IF语句描述一个四选一电路

LIBRARY IEEE; USE IEEE. STE_LOGIC_1164.ALL;

VHDL语言的顺序语句

目 录

• 顺序语句概述 • 顺序语句概述 • 赋值语句 • 条件语句 • 循环语句 • 控制流语句

01

CATALOGUE

顺序语句概述

过程块(process block)

过程块是顺序语句的一种形式,它包含一系列的顺序语句,按照一定的顺序执行。

过程块通常在仿真过程中按照时间顺序逐行执行。

loop-statement循环语句

语法示例

```vhdl

loop_statement: process(some_signal)

loop-statement循环语句

01

02

begin

• 循环体

03

if some_condition then

loop-statement循环语句

• 条件满足时执行的代码

并行过程块(concurrent process block)

并行过程块是另一种形式的顺序语句,它包含一系列的顺序语句,这些语句在仿真过程中同时执行。

并行过程块通常用于描述数字系统的并发行为。

02

CATALOGUE

赋值语句

连续赋值语句

总结词

在连续赋值语句中,信号或变量的值 在每个仿真时间步都会更新。

case语句

end case;

```

conditional语句

描述:类似于其他编程语言中的三元操作符。

01

02

语法

```vhdl

03

04

signal_name <= "0" when condition else "1";

```

05

06

上述语句表示,如果条件为真,则将 `signal_name`设置为"0",否则设置为 "1"。

vhdl顺序语句

vhdl顺序语句VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统的结构和行为。

在VHDL中,顺序语句用于按照特定的顺序执行操作。

下面将列举10个VHDL顺序语句的示例。

1. 赋值语句(Signal Assignment Statement):使用“:=”操作符将一个信号或变量赋给另一个信号或变量。

例如:```vhdlsignal a, b : std_logic;signal c : std_logic;c := a and b;```2. 过程调用语句(Procedure Call Statement):用于调用已定义的过程。

例如:```vhdlprocess(clk)beginif rising_edge(clk) thenmy_procedure(param1, param2);end if;end process;```3. 条件语句(If-then-else Statement):根据条件执行不同的语句块。

例如:```vhdlif a = '1' thenb <= '0';elseb <= '1';end if;```4. 选择语句(Case Statement):根据选择的值执行相应的语句块。

例如:```vhdlcase sel iswhen "00" =>out <= a;when "01" =>out <= b;when "10" =>out <= c;when others =>out <= '0';end case;```5. 循环语句(Loop Statement):用于重复执行一组语句。

例如:```vhdlprocessbeginloopif a = '1' thenb <= '0';elseb <= '1';end if;wait for 10 ns;end loop;end process;```6. 退出语句(Exit Statement):用于提前退出循环语句。

VHDL顺序语句获奖课件

WHEN 0|6 TO 10 => out <= 4 ; 能取旳值

WHEN OTHERS => out <= 5 ;

END CASE;

……

使用CASE语句需注意下列几点:

(1) 条件句中旳选择值必在体现式旳取值范围内。

(2) CASE语句中每一条语句旳选择值只能出现一 次,即不能有相同选择值旳条件语句出现。

2.CASE语句--举例

SIGNAL sel : INTEGER range 0 to 20;

……

CASE sel IS 数值

取值范围

WHEN 1

=> out <= 1 ; 并列数值

WHEN 3 TO 5 => out <= 2 ; 混合方式

WHEN 2|15 => out <= 3 ; 表达其他可

-- value2~15旳值未涉及进去

CASE value IS

WHEN 0 TO 10 => out1<= '1';

WHEN 5 TO 15 => out1<= '0';

END CASE;

……

-- 选择值中5~10旳值有重叠

例题: 用CASE语句设计四选一数据选择器

s1 s2

a

b

MUX41

z

c

d

architecture rt1 of mux4 is begin process(creset)

begin if(creset=‘1’) then if(sel=“00”) then q<=cdata(0); elsif(sel=“01”) then q<=cdata(1); elsif(sel=“10”) then q<=cdata(2); else q<=cdata(3); end if; else q<=‘0’; end if;

VHDL顺序语句

F、返回语句

RETURN语句是一段子程序结束后,返回主程序的 控制语句。它有两种格式: RETURN; RETURN 表达式; --第一种语句格式 -- 第二种语句格式

第一种格式只能用于过程,它后面一定不能有表达式; 第二种格式只能用于函数,它后面必须有条件表达式, 它是函数结束的必要条件,函数结束必须用RETURN语 句。

NEXT [LOOP 标号] [WHEN 条件表达式];

当LOOP 标号缺省时,则执行NEXT 语句时,即 刻无条件终止当前的循环,跳回到本次循环LOOP语 句开始处,开始下一次循环,否则跳转到指定标号的 LOOP语句开始处,重新开始执行循环操作。若 WHEN子句出现并且条件表达式的值为TRUE,则执 行NEXT语句,进入跳转操作,否则继续向下执行。

THEN

顺序语句n;

顺序语句n+1;

例 :IF (SET=’1’) THEN

c<=b END IF; 例 : IF (sel=’1’) THEN

c<=a;

ELSE

c<=b;

END IF;

IF语句 实例1 : 4选1数据选择器

LIBRARY IEEE;

USE

IEEE. STE_LOGIC_1164.ALL;

B、CASE 语句

CASE 表达式 IS When 选择值 => 顺序语句; When 选择值 => 顺序语句; ... [When OTHERS =>顺序语句;] END CASE ;

选择值可以有四种不同的表达方式: 单个普通数值,如6。 数值选择范围,如(2 TO 4),表示取值为2、3或4。 并列数值,如35,表示取值为3或者5。 混合方式,以上三种方式的混合。

VHDL顺序语句

第2章 VHDL硬件描述语言

EDA技术

【例2.15】求4个数值的平均值程序 】 个数值的平均值程序 PROCESS BEGIN WAIT UNTIL CLK= '1'; ; AVE<=A; ; WAIT UNTIL CLK= '1'; ; AVE<=AVE+A; ; WAIT UNTIL CLK= '1'; ; AVE<=AVE+A; ; WAIT UNTIL CLK= '1'; ; AVE<=(AVE+A)/4; ; END PROCESS; ; 例2.15中的进程 中的进程 将完成一个硬件 求平均的功能, 求平均的功能, 每一个时钟脉冲 由A输入一个数 输入一个数 值,4个时钟脉冲 个时钟脉冲 后将获得此4个数 后将获得此 个数 值的平均值。 值的平均值。

第2章 VHDL硬件描述语言

EDA技术

例 PROCESS BEGIN y<=a AND b; ; WAIT ON a,b; , ; END PROCESS; ;

第2章 VHDL硬件描述语言

EDA技术

(3)条件等待语句:WAIT UNTIL 布尔表达式 条件等待语句: 条件等待语句 当进程执行到该语句时,被挂起;若布尔表达式为真时, 当进程执行到该语句时,被挂起;若布尔表达式为真时, 进程将被启动。 进程将被启动。 例: WAIT UNTIL ((x*10)<100) (4) WAIT FOR 时间表达式 当进程执行到该语句时,被挂起;等待一定的时间后, 当进程执行到该语句时,被挂起;等待一定的时间后,进 程将被启动。 程将被启动。 例:WAIT FOR 20 ns

第2章 VHDL硬件描述语言

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例

用CASE语句描述4选1多路选择器。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX41 IS PORT(S1,S2: IN STD_LOGIC; A,B,C,D:IN STD_LOGIC; Z: OUT STD_LOGIC);

END ENTITY MUX41;

END mux4;

ARCHITECTURE rt1 OF mux4 BEGIN PROCESS (input, sel) BEGIN IF (sel=”00”) THEN ELSIF (Sel=”01”) THEN ELSIF (Sel=”10”) THEN ELSE END IF; END PROCESS; END rt1;

B、CASE 语句

CASE 表达式 IS When 选择值 => 顺序语句; When 选择值 => 顺序语句; ... [When OTHERS =>顺序语句;] END CASE ;

选择值可以有四种不同的表达方式: 单个普通数值,如6。 数值选择范围,如(2 TO 4),表示取值为2、3或4。 并列数值,如35,表示取值为3或者5。 混合方式,以上三种方式的混合。

(4) CASE语句执行中必须选中,且只能选中所列条件语

句中的一条。这表明CASE语句中至少要包含一个条件语句。

CASE语句常用来描写总线行为、编码器和译码器的结构。CASE语句 与IF语句功能相似但CASE语句的可读性好,非常简洁。

C、LOOP 语句

(1)单个LOOP语句,其语法格式如下: [标号:] LOOP 顺序语句; END LOOP [标号 ]; 用法示例: L2 :LOOP a := a+1; EXIT L2 WHEN a >10 ; -- 当a大于10时跳出循环 END LOOP L2; ... (2)FOR… LOOP语句,语法格式如下: [标号:] FOR 循环变量 IN 循环次数范围 LOOP 顺序语句; END LOOP [标号];

IS

Y<=input (0); Y<=input (1); Y<=input (2); Y<=input (3);

IF语句不仅可用于选择器设计,还可用于比较 器,译码器等进行条件控制的逻辑设计。IF语句 中至少应有一个条件句,条件句必须由布尔表达 式构成,条件表达式中能使用关系运算操作及逻 辑运算操作的组合表达式。 IF语句颠倒条件判别次序,会引起在综合时逻辑 功能的变化,即IF语句判别条件不可颠倒。 IF语句中,先处理最起始的条件;如果不满足, 再处理下一个条件。一般把条件约束最多的作为 起始条件。

VHDL有如下六类基本顺序语句: 1、赋值语句 2、流程控制语句

信号赋值语句 变量赋值语句 IF语句 CASE语句 LOOP语句 NEXT语句 EXIT语句

3、等待语句

4、子程序调用语句

WAIT语句

过程调用 函数调用 RETURN语句 NULL语句

5、返回语句

6、空操作语句

1、赋值语句

A、变量赋值语句

ARCHITECTURE ART OF MUX41 IS

SIGNA S :STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN S<=S1 & S2;

PROCESS(S,A,B,C,D) IS

BEGIN CASE S IS

WHEN "00"=>Z<=A;

WHEN "01"=>Z<=B; WHEN "10"=>Z<=C;

条件句

THEN

顺序语句;

END IF; IF 条件句 THEN 顺序语句;

第二种

ELSE

顺序语句;

END IF;

IF

条件句1

THEN

THEN

顺序语句1;

顺序语句2;

ELSIF 条件2 … 第三种 ELSIF 条件n ELSE END IF;

THEN

顺序语句n;

顺序语句n+1;

例 :IF (SET=’1’) THEN

WHEN "11"=>Z<=D;

WHEN OTHERS =>Z<='X'; END CASE;

END PROCESS;

END ARCHITECTURE ART;

使用CASE语句需注意以下几点: (1) 条件句中的选择值必须在表达式的取值范围内。 (2) 除非所有条件句中的选择值能完整覆盖 CASE语句中 表达式的取值,否则最末一个条件句中的选择必须用 “OTHERS”表示。 (3) CASE语句中每一条语句的选择只能出现一次,不能 有相同选择值的条件语句出现。

c<=b END IF; 例 : IF (sel=’1’) THEN

c<=a;

ELSE

c<=b;

END IF;

例

用IF语句描述一个四选一电路

LIBRARY IEEE;

USE

IEEE. STE_LOGIC_1164.ALL;

ENTITY mux4 IS PORT (input: IN STD_LOGIC_VECTOR (3 DOWNTO 0); sel: IN STD_LOGIC_VECTOR (1 DOWNTO 0); Y: OUT STD_LOGIC);

[理解]

顺序语句是相对于并行语句而言的,其特点 是每一条顺序语句的执行(指仿真执行)顺序是与 它们的书写顺序基本一致的, 顺序语句只能出现在 进程(PROCESS) 过程(PROCEDURE) 函数(FUNCTION) 中,其它都是并行语句。 一个进程是由一系列顺序语句构成的,而进 程本身属并行语句。也就是说,在同一设计实体 中,所有的进程是并行执行的,每个进程内部是 顺序执行的。

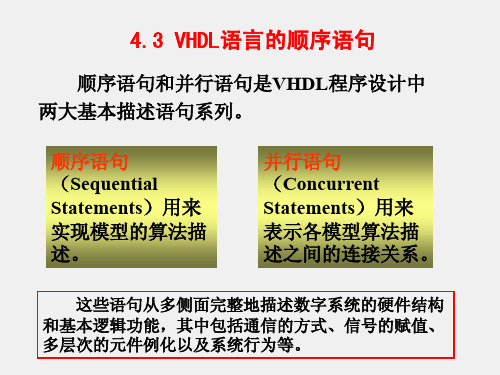

五、VHDL语言的顺序语句

顺序语句和并行语句是VHDL程序设计中 两大基本描述语句系列。 顺序语句 (Sequential Statements)用来 实现模型的算法描 述。 并行语句 (Concurrent Statements)用来 表示各模统的硬件结构 和基本逻辑功能,其中包括通信的方式、信号的赋值、 多层次的元件例化以及系统行为等。

目的变量 := 表达式;

例:x:=15; 变量的说明和赋值限定在顺序区域内,即只能在 进程或子程序中使用,它无法传递到进程之外。

B、信号赋值语句

目的信号 <= 表达式;

例:y<=‘1’;

信号赋值可以在顺序区域内作顺序语句,也可以 在结构体中当作并行语句使用。

2、流程控制语句

A、IF 语句

第一种

IF