如何将altium designer的原理图和PCB转入cadence里

Altium Designer原理图元件和PCB元件互相定位

Altium Designer原理图元件和PCB元件互相定位使用快捷键:“T”+“C”然后点击要定位的元件即可。

此方法元件被中,其他元件会被过滤掉。

DXP里原理图里的元件怎么快速从PCB中找到呢

首先确认你的原理图与PCB在同一工程之下,并且原理图与PCB均已打开

然后选择原理图中你想要找的原件

然后快捷键T S ,好了,你已经找到你选择的元件在PCB中的位置,并且是处于被选中状态

(此方法只选中,其他元件不变)

在PCB文件中,查看-->工作区面板-->PCB-->PCB,窗口弹出,选择components,元件列表中点击你要查找的元件,就会高亮显示了。

如何将altiumdesigner的原理图和PCB转入cadence里

如何将altiumdesigner的原理图和PCB转入cadence里说明:1)本教程适用于将altiumdesigner的原理图和PCB转入cadence(分别对应captureCIS和allegro)里。

对于protel99se,可以将其先导入较新版本的AD里,再转入cadence中。

2)整个过程中使用的软件包括altiumdesignerSummer08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。

其中,后面两个软件较小,便于下载。

3)原理图的转化路线是,从altiumdesigner导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。

因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。

如果你不是这些版本的软件,也可以参考本人的方法进行尝试。

4)pcb转化的顺序是,altiumdesigner导出的文件,导入PADS9.3打开,然后导出.asc文件。

随后利用allegro对pads的接口,将pads文件导入。

1.原理图的导入1.1选中原理图的项目文件,即.PRJPCB文件,右键-》saveprojecas,选择.dsn文件,输入要保存的文件名,保存。

注意输入新的文件名的时候要把文件名的后缀手动改掉。

1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。

具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。

而对于cadence16.6来说,环境变量必须是5280@localhost。

因此要使用orCAD10.3的话,必须将CDS_LIC_FILE的值改掉,否则无法打开。

Altium向Cadence数据转换-17

Altium向Cadence数据转换-17.2 Altium数据向Cadence数据转换向导选择合适的PCB设计解决方案从来都不是一件简单的事情。

无论是初创企业还是已经完善的企业,都需要考虑多方面的因素,如工具设计功能、成本、技术服务、技术性与前瞻性、市场占有率等。

当完成了产品75%研发的时候,突然发现现有的PCB设计工具无法满足设计要求,这是任何企业或研发工程师都不想面对的事实。

Cadence设计解决方案是一个可以信赖的研发方案,可以满足您现在以及未来的技术需求。

以下是五个原因供您参考:原因1:扩展性能够满足企业未来的研发技术要求Cadence解决方案提供一整套完善、可扩展的PCB设计方案。

随着企业研发要求的提升,Cadence设计方案可以无缝扩展、升级,随时满足您的技术要求。

这样能够满足现状与未来的设计解决方案,能够让您的企业研发投入更有价值。

原因2:高性价比与灵活的销售模式Cadence PCB设计方案并不是一个标准套件模式。

Cadence灵活的销售模式,研发团队可以根据技术需求与研发预算,合理选择最适合的模块配置。

原因3:功能先进Cadence为工程师提供先进的PCB设计技术。

约束规则驱动PCB设计,结合高速信号布线、自动/交互式布线、DFM分析、动态覆铜等先进技术,帮助工程师高效完成PCB设计,加速产品上市时间,并确保设计的一次成功率。

原因4:完全可定制的企业研发系统Cadence为用户提供很多API应用接口,用户可以以此为基础,定制开发完全符合企业内部研发需求的完整设计环境。

Cadence可以与PDM/ERP等外部数据管理系统互联,可以自动创建企业标准化报告文档,甚至可以定制全新的界面。

原因5:最好的客户技术支持Cadence提供及时的在线技术支持,能够快速解答技术问题。

这样能够让企业在使用过程中更加放心,提高研发团队的能力与产品的可靠性。

XXX产品得到了Cadence技术团队以及国内代理商(CCP)的全方位技术支持。

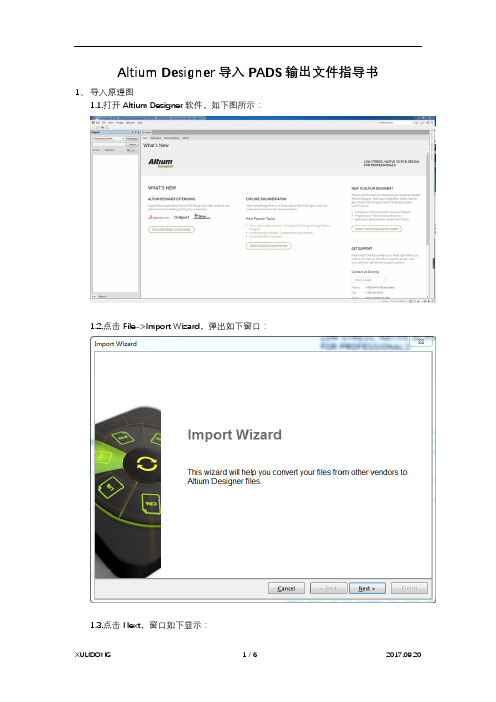

Altium Designer导入PADS输出文件指导书

Altium Designer导入PADS输出文件指导书

1、导入原理图

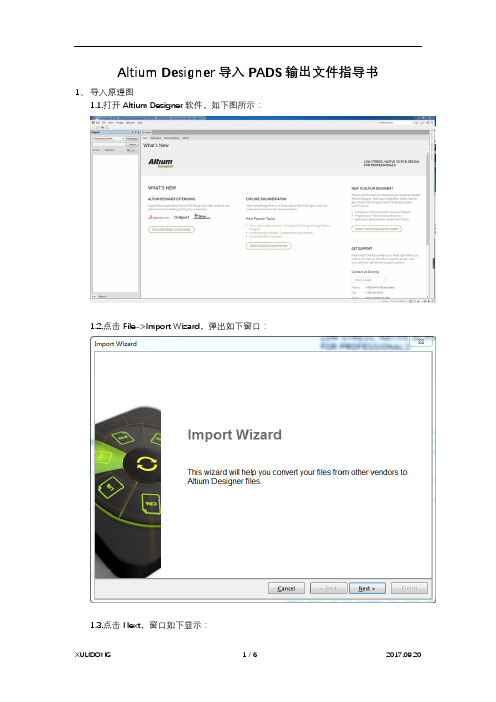

1.1.打开Altium Designer软件,如下图所示:

1.2.点击File->Import Wizard,弹出如下窗口:

1.3.点击Next,窗口如下显示:

1.4.选择PADS ASCII Design And Library Files,并点击Next,显示如下窗口:

1.5.点击Add,弹出窗口如下图所示:

1.6.选择对应文件夹\00.SCHEMATIC DIAGRAM下的TXT文档,点击打开,如下所示:

1.7.保持默认选项设置,点击Next,直至Finish。

2、导入PCB图

2.1.打开Altium Designer软件,如下图所示:

2.2. 点击File->Import Wizard,弹出如下窗口:

2.3. 点击Next,窗口如下显示:

2.4. 选择PADS ASCII Design And Library Files,并点击Next,显示如下窗口:

2.5. 点击Add,弹出窗口如下图所示:

2.6. 选择对应文件夹\04.PCB下的ASC文档,点击打开,如下所示:

2.7.保持默认选项设置,点击Next,直至Finish。

pads格式的PCB 导入到allegro之后再与orcad格式的原理图同步的全过程经验总结

源库替换掉原来有非法路径信息的库元件1 U: E" `: z( J0 G; m

元件的引脚也要严格区分,如某个引脚定义为output 则该引脚不能连到地。这也会造成同步失败

元件的引脚名和引脚号不能分别不能与另一个引脚有重复的部分)

转换后没有REF的问题,发现在不开ALLEGRO的情况下,直接运行PADS_IN.EXE是可以的,INI文件用安装目录下的。

E:\Cadence\SPB_15.5.1\tools\pcb\bin\pads_in.exe,E:\Cadence\SPB_15.5.1\tools\pcb\bin\pads_in.ini

2,pads输出powerpcb3.5格式的asc文件,

3,在allegro里面导入asc文件

4,在allegro导出库文件.

5,在用户设置里面,设置焊盘和flash的两个库文件的路径,都指向刚从allegro导出的库

6,打开orcad,输出网表,选择要同步的allegro PCB,并指定要生成的allegro PCB

导入pads格式的PCB 导入到allegro之后再与orcad格式的原理图同步的全过程经验总结)

步骤

1,先将orcad原理图与pads PCB严格同步,同时保证pads的每一种元件的库都有元件序号和值的label(两个label),不然会出现同步allegro传送网络表时会出现没有标示的问题

7,执行同步。(此过程会产生很多问题,大部分的问题原因是,

原理图的焊盘个数与PCB库焊盘个数不一致, 修改原理图,保证与PCB库一致

如何将altiumdesigner的原理图和PCB转入cence里

如何将a l t i u m d e s i g n e r的原理图和P C B转入c e n c e里This model paper was revised by the Standardization Office on December 10, 2020说明:1)本教程适用于将altiumdesigner的原理图和PCB转入cadence(分别对应captureCIS和allegro)里。

对于protel99se,可以将其先导入较新版本的AD 里,再转入cadence中。

2)整个过程中使用的软件包括altiumdesignerSummer08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。

其中,后面两个软件较小,便于下载。

3)原理图的转化路线是,从altiumdesigner导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。

因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。

如果你不是这些版本的软件,也可以参考本人的方法进行尝试。

4)pcb转化的顺序是,altiumdesigner导出的文件,导入PADS9.3打开,然后导出.asc文件。

随后利用allegro对pads的接口,将pads文件导入。

1.原理图的导入1.1选中原理图的项目文件,即.PRJPCB文件,右键-》saveprojecas,选择.dsn文件,输入要保存的文件名,保存。

注意输入新的文件名的时候要把文件名的后缀手动改掉。

1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。

具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。

AltiumDesigner的同一个工程中有多原理图多PCB工程处置惩罚

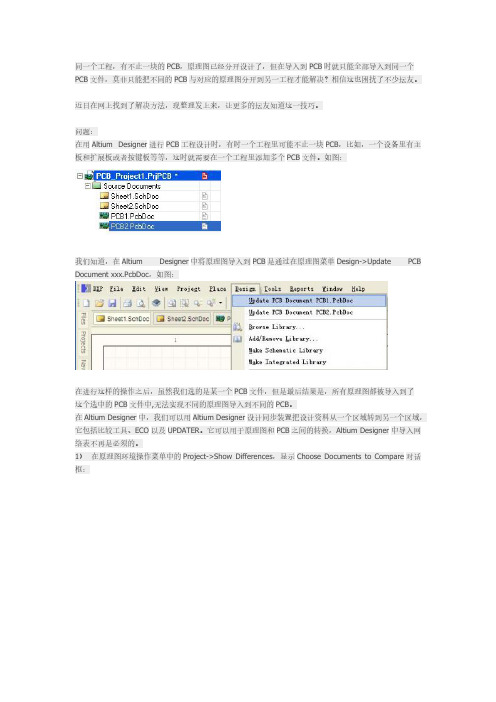

我们知道,在 Altium Designer 中将原理图导入到 PCB 是通过在原理图菜单 Design->Update PCB Document xxx.PcbDoc,如图:

在进行这样的操作之后,虽然我们选的是某一个 PCB 文件,但是最后结果是,所有原理图都被导入到了 这个选中的 PCB 文件中,无法实现不同的原理图导入到不同的 PCB。 在 Altium Designer 中,我们可以用 Altium Designer 设计同步装置把设计资料从一个区域转到另一个区域, 它包括比较工具、ECO 以及 UPDATER。它可以用于原理图和 PCB 之间的转换,Altium Designer 中导入网 络表不再是必须的。 1) 在原理图环境操作菜单中的 Project->Show Differences,显示 Choose Documents to Compare 对话 框:

对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行高中资料试卷调整试验;通电检查所有设备高中资料电试力卷保相护互装作置用调与试相技互术关,通系电1,力过根保管据护线生高0不产中仅工资2艺料22高试2可中卷以资配解料置决试技吊卷术顶要是层求指配,机置对组不电在规气进范设行高备继中进电资行保料空护试载高卷与中问带资题负料2荷试2,下卷而高总且中体可资配保料置障试时2卷,32调需3各控要类试在管验最路;大习对限题设度到备内位进来。行确在调保管整机路使组敷其高设在中过正资程常料1工试中况卷,下安要与全加过,强度并看工且25作尽52下可22都能护可地1关以缩于正小管常故路工障高作高中;中资对资料于料试继试卷电卷连保破接护坏管进范口行围处整,理核或高对者中定对资值某料,些试审异卷核常弯与高扁校中度对资固图料定纸试盒,卷位编工置写况.复进保杂行护设自层备动防与处腐装理跨置,接高尤地中其线资要弯料避曲试免半卷错径调误标试高方中等案资,,料要编试求5写、卷技重电保术要气护交设设装底备备置。4高调、动管中试电作线资高气,敷料中课并设3试资件且、技卷术槽及避、系免管统不架启必等动要多方高项案中方;资式对料,整试为套卷解启突决动然高过停中程机语中。文高因电中此气资,课料电件试力中卷高管电中壁气资薄设料、备试接进卷口行保不调护严试装等工置问作调题并试,且技合进术理行,利过要用关求管运电线行力敷高保设中护技资装术料置。试做线卷到缆技准敷术确设指灵原导活则。。:对对在于于分调差线试动盒过保处程护,中装当高置不中高同资中电料资压试料回卷试路技卷交术调叉问试时题技,,术应作是采为指用调发金试电属人机隔员一板,变进需压行要器隔在组开事在处前发理掌生;握内同图部一纸故线资障槽料时内、,设需强备要电制进回造行路厂外须家部同出电时具源切高高断中中习资资题料料电试试源卷卷,试切线验除缆报从敷告而设与采完相用毕关高,技中要术资进资料行料试检,卷查并主和且要检了保测解护处现装理场置。设。备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况,然后根据规范与规程规定,制定设备调试高中资料试卷方案。

Altium中导入ALLEGRO的brd文件

Altium 中导入ALLEGRO的brd文件一步一步教你如何在Altium Designer中导入ALLEGRO的brd文件[本文由 Hiber 发表在 /post.1766615.html]课题组其他人都用ALLEGRO,我一个人死撑着用AD。

共享设计时原理图还方便导入,PCB文件麻烦了,于是一直在找如何从AD中导入ALLEGRO的brd文件的方法,一直未果(曾经找了个CAMCAD Pro,号称可以,但不会用--呵呵,也可能是不可以)。

AD不支持导入ALLEGRO的brd文件,orcad的layout的max文件倒是支持,可是同为cadence的产品,居然layout不能导入brd。

我算是一个准超级AD fans,经过自己的摸索,找到一些实现的曲线实现方法。

我用Altium Designer 6.6,下面以6.6为例讲讲如何将ALLEGRO的brd板子导入Protel (DXP)中。

基本思想是用CAM文件,具体步骤:1、从ALLEGRO PCB Editor中导出Gerber文件和IPC网表文件(不要IPC网表也可以,不过那样导入的PCB网络名是AD随机命名的)。

也可以导出ODB++文件(可能还是需要IPC网表),我觉得这个比Gerber 方便。

ALLEGRO需要安装第三方软件才能输出ODB++,这个在导出时会提示下载的(软件是free的)。

2、在AD中新建一个CAM文件。

3、通过AD的File/Import导入ALLEGRO输出的Gerber/ODB++,(可选)通过File/Import/Net List导入IPC网表。

4、使用Tool/Netlist/Extract提取导入的Gerber/ODB++的网络(将相连的Track视为同一网络,网络名随机生成)。

5、(可选)通过File Import/NetList导入IPC网表。

如果3中已导入,忽略本步。

6、通过Tool/NetList/Campare将Extrat的网表和IPC网表进行比较,从而将网络(大部分)命名为ALLEGRO 中原来的网络名。

Protel原理图PCB到Cadence的数据转换

Protel原理图PCB到Cadence的数据转换Date: 2008/ 04 / 25Author:周曙光Version: v16.xKeywords:数据转换AD6(Altium Designer 6)Note: 任何两个EDA工具之间的数据转换都不是百分百的正确,都需要做一定修改。

随着PCB设计的复杂程度和高速PCB设计需求的不断增加,越来越多的PCB设计者、设计团队选择Cadence的设计平台和工具。

但是,由于没有AD6数据到Cadence数据直接转换工具,长期以来如何将现有的基于AD6平台的设计数据转化到Cadence平台上来一直是处于平台转化期的设计者所面临的难题。

下面结合Cadence和Altium的PCB设计工具,提供一条比较合理的转换途径。

1、环境:转换中使用到的工具a) Altium Designer 6b) Cadence Capture CISc) Cadence Orcad Layoutd) Cadence PCB Editore) Cadence PCB Router(CCT)2、Altium - AD6原理图到Cadence - Capture CIS在Altium Designer 6原理图的转化上我们可以利用Altium Designer 6的Save Preject As来实现。

通过这一功能我们可以直接将AD6的原理图转化到Capture CIS中。

然后直接保存为*.dsn文件。

注意事项:这里,我们仅提出几点通过实践总结出来的注意事项。

a)封装信息AD6在输出Capture DSN文件的时候,没有输出封装信息,在Capture中我们会看到所以元件的PCB Footprint属性都是空的。

这就需要我们手工为元件添加封装信息,这也是整个转化过程中最耗时的工作。

在添加封装信息时要注意保持与AD6 PCB设计中的封装一致性,以及Cadence在封装命名上的限制。

例如一个电阻,在AD6中的封装为AXIAL0.4,在后面介绍的封装库的转化中,将被修改为AXIAL04,这是由于Cadence不允许封装名中出现“.”;再比如DB9接插件的封装在AD6中为DB9RA/F,将会被改为DB9RAF。

Cadence常用技巧、网表导入PADS、CAD板框导入

在进行中等以上规模电路设计的时候,一般都是专人负责原理图原理图,专人负责layout,orCAD因为他的输出网表种类相当丰富,操作方便深受原理设计人员青睐,orCAD可以输出目前市面上大部分PCB设计软件的网表,包括protel、AltiumDesigner、PADS、Alegrro等等,下面介绍一下两者交互设计时候网表导入和更新问题。

1、生成网表。

首先在rocad中选中要生成网表的原理图文件夹,之后执行Tool/Creat Netlist命令,之后弹出下面的对话框:在other页面中Formatter中选择,之后点击确定,便会生成PDAS所使用.asc格式的网表,如下图所示:2、导入网表。

新建一个PADS PCB文件,在此假设名字为.如下图所示:新建文件之后,首先要有自己的PCB封装库,并且设置好自己的PCB封装库路径,设置PCB封装库路径发方法如下:工具/选项之后弹出来如下界面:点击右侧的库列表文件夹,如下图所示,之后选择自己的PCB封装库所在位置:这样自己的封装库路径设置完成了。

之后可以在PADS layout软件中导入网表了。

打开刚才创建的文件,执行"文件/导入"命令,打开刚才用orcad生成的.asc文件。

之后会弹出一个检验文本,提示所有的错误和警告,如下图所示:之后还会弹出一个警告对话框,可以忽略之。

之后所有的原件就导入进来了,如下图所示,此时元件是堆放在一起的:执行命令:“工具/分散元器件”,之后元器件被分散开来,如下图所示:这样,就完成了PCB的导入,之后可以进行布线工作。

3、更新原理图中修改的网表。

在PCB布线的时候可能会修改原理图中的部分器件或者连线,这时候就要进行网表更新。

步骤如下:a、更改好原理图之后,重新生成网表,然后新建一个空的PCB文件,给这个pcb文件起一个名字(名字随便起),这里就叫做.b、打开文件,执行"文件/导入"命令,导入新生成的.asc网表,之后关闭。

Altium Designer导入PADS输出文件指导书

Altium Designer导入PADS输出文件指导书

1、导入原理图

1.1.打开Altium Designer软件,如下图所示:

1.2.点击File->Import Wizard,弹出如下窗口:

1.3.点击Next,窗口如下显示:

1.4.选择PADS ASCII Design And Library Files,并点击Next,显示如下窗口:

1.5.点击Add,弹出窗口如下图所示:

1.6.选择对应文件夹\00.SCHEMATIC DIAGRAM下的TXT文档,点击打开,如下所示:

1.7.保持默认选项设置,点击Next,直至Finish。

2、导入PCB图

2.1.打开Altium Designer软件,如下图所示:

2.2. 点击File->Import Wizard,弹出如下窗口:

2.3. 点击Next,窗口如下显示:

2.4. 选择PADS ASCII Design And Library Files,并点击Next,显示如下窗口:

2.5. 点击Add,弹出窗口如下图所示:

2.6. 选择对应文件夹\04.PCB下的ASC文档,点击打开,如下所示:

2.7.保持默认选项设置,点击Next,直至Finish。

从Cadence到Altium Designer的转换,为何设计中面临越来越多挑战

从Cadence到Altium Designer的转换,为何设计中面临越来越多挑战本篇文章主要介绍了PCB项目在不同开发平台之间进行转换的相关信息。

Altium Designer 对基于不同开发平台开发的PCB项目都可以进行无缝转换,整个转换的过程操作简单,各种平台的支持范围广泛。

开发人员可以利用Altium Designer 对不同平台的PCB项目进行二次编辑提供了极大的便利。

本篇文章内容包括作为PCB设计人员在设计过程中对于开发平台本身应当关注的问题有哪些。

Altium Designer 对比Cadence开发平台优势在哪里,将PCB项目从Cadence平台转换到Altium Designer平台主要步骤有哪些。

从Cadence到Altium Designer的转换今天的电子工程师在产品的设计中面临越来越多的挑战,并且未来还会持续这一趋势;作为使用Cadence的工程师或PCB设计人员,您应当对这些问题了如指掌,并且还应清楚您当前工具的优势功能;您目前可能正面临哪些设计挑战:您是否确定您的PCB Layout 完全体现了原理图的设计意图,而无需在修正上花费大量的时间?您是否确保最终产品跟机械外壳能够完美的匹配?您是否能够在较短的时间内就能熟练的应用设计软件,而无需花费大量的时间和精力去学习和适应设计工具?Altium在为工程师和设计团队提供统一的一体化产品设计平台方面具有明显的优势,该平台可针对元器件选择、原理图设计、PCB Layout、产品外观尺寸及对机械件的匹配进行优化,并生成制作、装配文档。

Altium的历史:Altium一直专注于提供最新的、易于使用的、性能增强的的PCB设计工具:1985年,Nick Martin 创建Altium Designer的首个版本- Protel PCB,开创Altium公司;1988年,Altium 发布AutoTrax (提供自动布线、自动移位和照片绘图功能);1994年,Altium 提出客户端/服务器端架构,以整合各种EDA设计工具;。

如何实现PCB元件封装与原理图元件封装的同步

在使用AlTIum Designer的过程中我们收到许多用户的提问Q&A系列将针对用户关注度较高的问题请AlTIum技术专家为大家答疑解惑从PCB文档更新原理图元件的关联封装对于那些PCB中的元件封装与原理图元件ProperTIes属性面板Parameters中显示的封装不匹配的设计,下面将向您介绍如何使它们同步。

有几种方法可以更新原理图元件的关联封装。

最佳做法是在原理图库中进行更改,然后再更新到原理图。

注意:如果您使用的是托管内容服务器中的元件,这些元件将被锁定,并且它的封装无法直接更改。

从库更新:原理图元件可以直接从关联的库中更新,如下所示。

从打开的原理图文档中,选择工具►从库中更新(Tools ►Update from Libraries)。

注意:原理图库中有一个选项工具►更新原理图(Tools ►Update SchemaTIcs),但这会将库中所选元件完全替换到所有打开的原理图文档中。

使用原理图中的Update from Libraries选项,可以更好控制哪些元件需要更新。

属性面板(Properties):可以使用属性面板将封装添加到原理图元件中。

选择原理图元件,在Properties面板Parameters参数部分下,单击添加Add按钮,然后选择封装。

从PCB更新:如果PCB文档中的封装发生了变化,则可以通过运行PCB文档中的命令来更新相关原理图元件的封装,设计►更新原理图(Design ►Update Schematics)。

这将更新现有原理图元件中关联的封装。

这个命令不会添加新的原理图元件。

使用封装管理器(Footprint Manager):如果原理图库没有关联封装,或者您需要动态设置某些内容,则可以使用封装管理器(Footprint Manager)进行封装管理。

您可以从打开的原理图中访问封装管理器,然后选择工具►封装管理器(Tools ►Footprint Manager)。

Cadence从原理图到PCB

Cadence从原理图到PCB的流程图:一.原理图1.建立工程2.绘制原理图3. 生成网络表(Net List):在画板的时候需要导入网络表,在这之前可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate;再进行DRC检测。

DRC之后可以尝试去生成网络表了,在工程管理界面下,选Tools--Create Netlist,二.PCB1. 打开PCB Editor,在弹出的对话框中选择Allegro PCB Design GXL(legacy),然后点击Ok进入PCB编辑器。

接下来就是利用向导建立电路板了,包括确定板子的大小、层数、形状等等参数。

File-new 在弹出的对话框中的Drawing Type选择Board(wizard),然后确定文件名,Browse存盘路径等,最后点Ok进入向导。

注意:板子的路径应该和前面生成网表的路径保持一致。

2.导入网络表接上一个步骤,将网络表导入到刚建好的PCB中。

在此之前还有一个很重要的工作要做,就是指定PCB封装的路径。

点击Setup--User Preferences,在弹出对话框中的Categories中选中Design_paths,分别为padpath和psmpath指定路径,即将PCB元件封装路径添加到padpath和psmpath中,以告知Allegro从指定的路径寻找封装。

元件的PCB封装需要自己做或是直接用别人做好的,封装准备好后往PCB 中导入网络表,点击File--Import--Logic,在Import directory中指定在原理图部分生成的网络表文件路径,其他设置使用默认值即可,点击Import Cadence即可导入网络表。

3.叠层设计,规则设定,布局布线暂时简单描述下元件的放置,布局,布线,具体的叠层设计,设计规则等后面再详细补充3.1 元件放置成功导入网络表之后,放置元件。

点击菜单Place--Quickplace,在弹出的对话框中使用默认设置,点击Place按钮即可完成元件的放置。

CADENCE从原理图到PCB步骤

CADENCE从原理图到PCB步骤一(原理图1(建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第一项OrCAD_Capture_CIS_option withcapture,点击Ok进入Capture CIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2(绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Project manager(文件夹树图标)进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1) 修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等;2) 添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;3) 添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

4) 生成网络表(Net List):在画板的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。

Cadence从原理图到PCB

Cadence从原理图到PCB的流程图:一.原理图1.建立工程2.绘制原理图3. 生成网络表(Net List):在画板的时候需要导入网络表,在这之前可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate;再进行DRC检测。

DRC之后可以尝试去生成网络表了,在工程管理界面下,选Tools--Create Netlist,二.PCB1. 打开PCB Editor,在弹出的对话框中选择Allegro PCB Design GXL(legacy),然后点击Ok进入PCB编辑器。

接下来就是利用向导建立电路板了,包括确定板子的大小、层数、形状等等参数。

File-new 在弹出的对话框中的Drawing Type选择Board(wizard),然后确定文件名,Browse存盘路径等,最后点Ok进入向导。

注意:板子的路径应该和前面生成网表的路径保持一致。

2.导入网络表接上一个步骤,将网络表导入到刚建好的PCB中。

在此之前还有一个很重要的工作要做,就是指定PCB封装的路径。

点击Setup--User Preferences,在弹出对话框中的Categories中选中Design_paths,分别为padpath和psmpath指定路径,即将PCB元件封装路径添加到padpath和psmpath中,以告知Allegro从指定的路径寻找封装。

元件的PCB封装需要自己做或是直接用别人做好的,封装准备好后往PCB 中导入网络表,点击File--Import--Logic,在Import directory中指定在原理图部分生成的网络表文件路径,其他设置使用默认值即可,点击Import Cadence即可导入网络表。

3.叠层设计,规则设定,布局布线暂时简单描述下元件的放置,布局,布线,具体的叠层设计,设计规则等后面再详细补充3.1 元件放置成功导入网络表之后,放置元件。

点击菜单Place--Quickplace,在弹出的对话框中使用默认设置,点击Place按钮即可完成元件的放置。

Expedition数据转换至Cadence

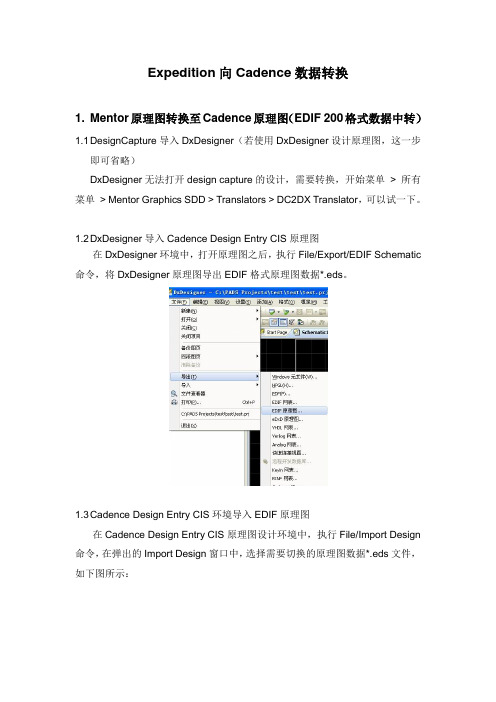

Expedition向Cadence数据转换1. Mentor原理图转换至Cadence原理图(EDIF 200格式数据中转)1.1 DesignCapture导入DxDesigner(若使用DxDesigner设计原理图,这一步即可省略)DxDesigner无法打开design capture的设计,需要转换,开始菜单> 所有菜单> Mentor Graphics SDD > Translators > DC2DX Translator,可以试一下。

1.2 DxDesigner导入Cadence Design Entry CIS原理图在DxDesigner环境中,打开原理图之后,执行File/Export/EDIF Schematic 命令,将DxDesigner原理图导出EDIF格式原理图数据*.eds。

1.3 Cadence Design Entry CIS环境导入EDIF原理图在Cadence Design Entry CIS原理图设计环境中,执行File/Import Design 命令,在弹出的Import Design窗口中,选择需要切换的原理图数据*.eds文件,如下图所示:至此,DesignCapture原理图即可切换至Design Entry CIS原理图环境中。

当然,毫无疑问,完成数据切换之后,必须检查完成数据转换的原理图——任何两种格式数据的切换,都必须认真检查,验证其正确性。

2. Mentor Expedition PCB转换至Cadence Allegro PCB数据(ASCII格式数据中转)2.1 PADS导入WG 2005-Expedition PCB设计数据在PADS环境中执行File/import命令,导入Expedition PCB设计数据。

2.2 在PADS环境中保存该PCB数据,然后执行File/Export命令,输出标准ASCII格式的PCB设计文件。

Layout原理图机构图PCB图档之间的转换

Layout原理图机构图PCB图档之间的转换

图档的导⼊和导出

1.电路图导⼊PCB:

(1)DSN⽂件导成asc⽂件:

打开DSN⽂件→点击“Create Netlist”→点击“Other”→从Formatters列表中选择PADSPCB.DLL

→保存为asc类型⽂件

(2)导成PCB:File→Imput

2.⽤CAM导⼊DXF⽂件设置原点:

(1)打开CAM350

(2)导⼊原DXF⽂件,对话框中的单位选“MM”

(3)设置单位:Settings→Unit→对话框Unit选“MM”

(4)设置原点:Edit→Change→Origin→space Origin

(5)导出新的DXF⽂件

3. 从Power PCB导⼊DXF⽂件:

(1)将单位设置为“MM”:Option→Globle→Design units→Metric(先设置不容易出错)

(2)导⼊DXF⽂件:File→Import→选择DXF⽂件→出现DXF Import对话框,选择Layer 25→点击Remove,mode为New→OK,DXF-File选metric

(3)保存机构外框图到Layer 25:

①去掉⽂字(关闭⽂字显⽰颜⾊)→框选机构外框→点击右键→Option→

选择Layer 25→OK

②去掉line(关闭line显⽰颜⾊)→框选⽂字→点击右键→Option→选择Layer 25

→OK

4.从Power PCB导出机构图DXF⽂件:

(1)打开PCB⽂件

(2)导出DXF⽂件:File→Export→选择DXF⽂件→出现DXF Export对话框

(3)勾选该选项,→OK.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

说明:

1)本教程适用于将altium designer的原理图和PCB转入cadence(分别对应capture CIS和allegro)里。

对于protel 99se,可以将其先导入较新版本的AD里,再转入cadence中。

2)整个过程中使用的软件包括altium designer Summer 08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。

其中,后面两个软件较小,便于下载。

3)原理图的转化路线是,从altium designer导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。

因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。

如果你不是这些版本的软件,也可以参考本人的方法进行尝试。

4)pcb转化的顺序是,altium designer导出的文件,导入PADS9.3打开,然后导出.asc文件。

随后利用allegro对pads的接口,将pads文件导入。

1. 原理图的导入

1.1选中原理图的项目文件,即.PRJPCB文件,右键-》save projec as,选择.dsn文件,输入要保存的文件名,保存。

注意输入新的文件名的时候要把文件名的后缀手动改掉。

1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。

具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。

而对于cadence16.6来说,环境变量必须是5280@localhost。

因此要使用orCAD10.3的话,必须将CDS_LIC_FILE的值改掉,否则无法打开。

等下使用cadence16.6,就必须将值改回来)。

1.3使用orCAD10.3将刚才保存的.dsn文件打开,并保存成project。

1.4 随后就可以使用新版本的cadence的capture CIS打开保存的文件(注意改环境变量中的用户变量CDS_LIC_FILE)。

2. PCB的导入

由于allegro可以根据已有的brd文件生成元器件的封装,因此将PCB导入allegro后使用者免于重新使用allegro绘制一遍封装。

1.1打开pads9.3,file-》new,按照默认配置建立一个文件,保存。

1.2file-》import,选中要转换的.pcb文件,打开,保存在C盘的PADS Projects文件夹下面。

(安装PADS9.3三合一完美精简版时会自动在C盘产生这个文件夹。

)

1.3file-》export,将文件保存为.asc文件。

接下来回弹出下图所示的对话框。

注意要将.pcb

文件和.asc文件保存在同一个目录下,即C盘的PADS Projects文件夹下面,否则allegro

转换时会出现pads_in.log找不到的现象。

(关于AD的pcb文件导入pads,网上还有一种方法是AD保存为PCB二进制文件,即.PcbDoc文件,再由pads导入.PcbDoc文件。

用户可以自行尝试。

总之,ad转换成pads似乎较为顺畅)

1.4格式选择PowerPCB V5.0,勾选认为比较的项目。

点击“OK”。

1.5随后使用allegro的import-》translator,选择pads,弹出如下的对话框。

其中第一行是指定.asc文件,第三行是指定要转换成的.brd文件。

一般而言都是C盘的PADS Projects文件夹内部。

第二行只要指定目录,然后在对话框里点保存即可。

点击translate,即可完成转换。

随后file-》open,打开刚才建立的.brd文件。