嵌入式双网冗余通信设计与实现

双网冗余系统的设计和实现的开题报告

双网冗余系统的设计和实现的开题报告1. 研究背景在现代的信息技术和通信技术中,双网冗余系统是一种常见的设计方案。

它的主要目的是提高整个系统的可靠性和稳定性,确保系统在任何情况下都能够正常运行。

双网冗余系统可以分为主备式和并行式两种设计。

其中,主备式双网冗余系统是将主网和备网分别连接在两个不同的进出口上,当主网发生故障时自动切换至备网,保证整个系统的正常运行。

而并行式双网冗余系统则是将主网和备网同时运行,并使用智能算法进行数据的负载均衡和故障切换。

2. 研究内容本文将重点研究双网冗余系统的设计和实现。

具体内容包括:(1)双网冗余系统的原理和工作模式。

介绍双网冗余系统的基本原理和运行方式,包括主备式和并行式两种设计。

(2)双网冗余系统的设计方案。

对于双网冗余系统的设计方案进行详细的分析和比较,并从系统的可靠性、稳定性和可扩展性等多个方面进行评价。

(3)双网冗余系统的实现技术。

选择适合的技术方案,详细讲解双网冗余系统的实现方式和实现过程,包括硬件和软件两方面。

(4)双网冗余系统的测试。

设计实验,利用具体的实验数据对双网冗余系统的性能进行评估,检测双网冗余系统的可靠性和稳定性等关键参数。

3. 研究意义研究双网冗余系统的设计和实现,对于提高信息和通信系统的可靠性和稳定性具有重要的实用价值。

另外,通过对双网冗余系统的研究,可以提高我们的设计能力和技术水平,内容的研究有助于对系统设计的完整性和一致性有更好的理解。

4. 研究方法本文主要采用文献综述和实验方法进行研究。

文献综述主要是针对国内外相关领域的文献资料进行搜集和总结,系统地分析和比较了不同的双网冗余系统设计方案和实现技术。

实验方法则是运用具体实验数据进行分析和验证,对所设计的双网冗余系统进行性能测试和压力测试等。

5. 预期成果本文预期将设计和实现一个基于双网冗余系统的实验平台,通过对实验平台的性能测试,可以验证所设计的双网冗余系统的可靠性和稳定性,并得出实验数据。

(完整)一个典型的嵌入式系统设计和实现

关键字:嵌入式系统设计ARM FPGA多功能车辆总线Multifunction Vehicle Bus 在计算机、互联网和通信技术高速发展的同时,嵌入式系统开发技术也取得迅速发展,嵌入式技术应用范围的急剧扩大.本文介绍了一种基于ARM和FPGA,从软件到硬件完全自主开发多功能车辆总线(Multifunction Vehicle Bus)MVB??B嵌入式系统的设计和实现。

系统设计和实现通常来说,一个嵌入式系统的开发过程如下:1.确定嵌入式系统的需求;2.设计系统的体系结构:选择处理器和相关外部设备,操作系统,开发平台以及软硬件的分割和总体系统集成;3.详细的软硬件设计和RTL代码、软件代码开发;4.软硬件的联调和集成;5.系统的测试。

一、步骤1:确定系统的需求:嵌入式系统的典型特征是面向用户、面向产品、面向应用的,市场应用是嵌入式系统开发的导向和前提。

一个嵌入式系统的设计取决于系统的需求。

1、MVB总线简介列车通信网(Train Communication Network,简称TCN)是一个集整列列车内部测控任务和信息处理任务于一体的列车数据通讯的IEC国际标准(IEC-61375-1), 它包括两种总线类型绞线式列车总线(WTB)和多功能车厢总线(MVB)。

TCN在列车控制系统中的地位相当与CAN总线在汽车电子中的地位。

多功能车辆总线MVB是用于在列车上设备之间传送和交换数据的标准通信介质。

附加在总线上的设备可能在功能、大小、性能上互不相同,但是它们都和 MVB总线相连,通过MVB总线来交换信息,形成一个完整的通信网络.在MVB系统中,根据IEC-61375-1列车通信网标准, MVB总线有如下的一些特点:拓扑结构:MVB总线的结构遵循OSI模式,吸取了ISO的标准。

支持最多4095个设备,由一个中心总线管理器控制。

简单的传感器和智能站共存于同一总线上。

数据类型:MVB总线支持三种数据类型:a.过程数据:过程变量表示列车的状态,如速度、电机电流、操作员的命令。

嵌入式系统的冗余设计研究

嵌入式系统的冗余设计研究嵌入式系统是指嵌入到封闭系统中的小型计算机系统,包括硬件和软件部分,为特定应用而设计和优化。

随着嵌入式系统在电子、通信、交通等领域的广泛应用,嵌入式系统的可靠性和稳定性变得越来越重要。

而冗余设计作为提高嵌入式系统可靠性的一种重要手段,一直备受关注。

冗余设计的目的是通过增加系统硬件或软件的冗余度,使嵌入式系统在面临单个或多个故障时能够继续运行或快速恢复,同时也提高了系统对故障的自诊断能力。

冗余设计主要通过以下几种方式实现:1.硬件冗余:通过硬件电路的备份或冗余,提高系统的可靠性。

例如,采用双路热备插槽服务器、RAID磁盘阵列等。

2.软件冗余:通过软件程序的备份或冗余,提高系统的可靠性。

例如,采用备份系统镜像、主备切换等。

3.信号冗余:通过对信号进行冗余传输和校验,提高系统的可靠性。

例如,采用冗余传输通道、冗余校验机制等。

在实际的嵌入式系统中,冗余设计更多地采用硬件冗余的方式。

因为硬件冗余设计具有可靠性高、实现简单、成本低等优点。

例如,在飞行器、高铁、核电站等高可靠性要求的领域,通常采用双路热备插槽服务器、多点采样等硬件冗余手段。

而在一些低可靠性要求的领域,如家电、智能穿戴等,软件冗余和信号冗余等手段相对更常用。

除了基本的硬件和软件冗余设计外,还可以通过其他方式提高嵌入式系统的冗余性。

例如,采用错误检测与纠正技术、自适应容错控制策略等。

错误检测与纠正技术是指通过检测和纠正错误位,提高系统可靠性的技术。

自适应容错控制是指根据系统状态,自适应调整容错控制策略,以适应系统的不同工作环境。

然而,冗余设计并不是一种完美的解决方案。

冗余设计虽然可以提高嵌入式系统的可靠性,但是同时也带来了一些不可避免的问题,如增加成本、增大系统复杂度、可能会导致单点故障等。

因此,在进行冗余设计时,需要权衡系统要求和成本等方面因素。

总之,对于嵌入式系统的冗余设计问题,需要根据系统要求选择合适的冗余设计方式。

船用嵌入式冗余智能网关的设计

De i n o h mb d e e u d n y s a tg t wa n b a d sg ft ee e d d r d n a c m r a e y o o r

Y N Y n W A n yn Ct N L i A G a g N Ma ・ i g IE e Isi t O o e l t dA tmai S a g a Ja tn i ri S r n t u e f w r a uo t n h n h i i o gUnv s y h 培 t P P n a n o o e t a 2 o 3 Oo0

现场设备一级 ; 同时为了提高通信系统的可靠性 ,

冗余的设计也是不可缺少的。

片, 它是A m l 司推 出的一款用 于工业 控制 的 te 公 A M9 理 器 , 基 于 A M9 0 R 处 它 R 2 T内 核, 作 在 工

10MHz 8 频率 下 , 运算 速 度高达 20MtS 独 立 0 P , 的l 指令 和 l 6K 6K数据 c h , 缓存 , a e写 c 全功 能的 MMU虚拟内存管理单元 , 内部 的1 B S A 6K R M和 1 8K O 外 部总线接 口( B )最重 要的是 2 BR M, E I, 其内含E C 以太 网控制器 ) 这就提高了集成 MA ( , 度, 减少 了系统所需要的芯片数量 。

A  ̄ r c Th ein 0 h eu d c matg twa nb adb t e h N u dEt en t r t t ta t ed sg f erd n a ys r ae yo o r ewe nt eCA b sa h r e ei m— t n n a n d cd u e 、A e lainpa fh r waeitra eb t e I RM 9 0 n h rai t l o d r efc ewen A' z o n a n gl 2 0a dt eCAN o tol C 2 1 ie . c nr lrM P 5 0i gy n e s Th ot r sgv nas esf waei ie l o.

基于BF537构建双冗余以太网的设计方案

基于BF537构建双冗余以太网的设计方案随着信息技术的高速发展,网络通信显得越发重要,以太网成为了各种控制系统接口互联的主要媒介。

在金融机构、军事应用等特殊应用场合对网络系统的稳定性要求非常高,为了提高系统的可靠性和抗毁性,采用双冗余的设计方式。

双冗余网络实现是以故障检测为基础,通过软件检查、交换机及网络节点的网卡协同处理。

冗余网络的构建方式通常是在每个网络节点采用双网卡,中间用2个HUB或交换机相连。

这样当某个节点的一块网卡、网线或者HUB出现故障时,系统会启用另一块冗余网卡使得系统仍能够正常运行。

本文提出了两种基于BF537的冗余网络构建方案。

1 BF537的结构特点BF537是Blackfin家族的升级产品,其在标准Blackfin内核的基础上拥有丰富接口,并在内部集成有以太网MAC控制器。

Blackfin内核包含2个乘/累加器(MAC),2个40位的ALU,4个视频专用8位ALU和1个40位移位器。

运算单元处理来自寄存器组的8、16或32位数据。

每个MAC每周期可完成一个16位×16位的乘法运算,并把结果累加到40位的累加器中,提供8位的精度扩展。

ALU单元执行标准的算术和逻辑运算,由于2个ALU具备对16或32位数据操作的能力,因此运算单元具备的灵活性可以满足各种应用中信号处理的要求。

每个32位的输入寄存器可以作为2个16位的寄存器,因此每个ALU可以完成非常灵活的单16位算术运算。

通过把寄存器当作2个16位的操作数使用,双16位或单32位操作可以在一个周期中完成。

更好地利用第2个ALU,4个16位操作可以简单地完成,加速了每个周期的吞吐量。

强大的40位移位器功能丰富,可以对数据进行移位、循环移位、归一化、提取和存储等操作。

运算单元所使用的数据来自具有16个16位操作数或8个32位操作数的寄存器组。

同时BF537把存储器视为统一的4 GB的地址空间,使用32位地址并采用分级的存储器结构。

基于PowerPC的嵌入式系统的双冗余网口切换技术

2018年第5期 信息通信2018 (总第 185 期)INFORMATION&COMMUNICATIONS(Sum.No 185)基于PowerPC的嵌入式系统的双冗余网口切换技术张曼(中航工业计算所,陕西西安710068)摘要:Pow erPC处理器以其多样化功能和优异性能得到各领域广泛应用。

文章以powerpc8270为例,对嵌入式实 时操作系统V xW orks下配置多网卡通讯进行了研究和实现,并且着重阐述了双网卡保持同一 IP和M A C地址冗 余切换的方法。

同时,文中分析了 8270F C C在VxW orks操作系统下设备驱动程序在系统中的层次结构和网络设 备驱动程序的运行机制,并在此基础上针对DP83848Y B网络芯片给出了实现代码,此方法已经成功运用在某项 目中。

关键词:VxWorks;DP83848Y B;双网卡通信;冗余切换中图分类号:TP393 文献标识码:A文章编号:1673-1131(2018 )05-0116-020引言MPC8270是Freescale公司的一款多功能通信处理器,集 成了 PowerPC内核和通信处理内核,有较髙的集成度和较低 的功耗,能够简化电路板的设计,被广泛应用于使用PC I接口 的网络基础结构、电讯和其他嵌入式应用等方面。

双网卡冗余备份及智能切换技术,主要是为了解决系统 中,当一路以太网卡出现故障时,系统通讯会突然中断的问题,为了使系统通讯不中断,使用双冗佘网卡智能切换技术自动 切换到另一路冗余网卡上,不仅可以保证通讯能够不中断,还 可以提髙系统的可靠性和稳定性。

1硬件组成及工作原理双冗余网卡设计在MPC8270的CPU板上,MPC8270提 供了两路以太网接口 FCC1和FCC2,MPC8270内部的FCCW 配置成ethemet模式后,实现以太网物理层数据处理和控制功 能即M AC层功能,来与外部物理层PH Y芯片DP83848连接,连接关系如图1所示。

一种新型双机冗余系统的设计与实现

一种新型双机冗余系统的设计与实现

长 沙 铁 道 学 院 现 代 教 育 技 术 中 心 !"#$$%&’

摘 要: 分析了带专用检测转换电路的双机冗余系统存在的可靠性问题, 提出了利用双机的

串行口代替专用检测转换电路, 通过串行通信相互检测主备机工作状态, 由软件完成备机切换成 主机的新型设计思想, 给出了此类系统的软件模板。 关键词: 双机 冗余 切换

冗余技术是计算机系统可靠性设计中常用的一种技 术, 是提高计算机系统可靠性的最有效方法, 同时也是鉴 别各类计算机控制系统好坏的标志之一。 故世界各地厂商 推 出 的 新 产 品 都 或 多 或 少 带 有 冗 余 技 术 。 如 美 国 的 ’(") 德国的西门子和日本的三武等, 它们都有一个共 *+,*-- 、 同的特点, 就是自己设计了专用检测转换电路来实现主备 切换。 本文提出一种新的构思, 取消专用检测转换电路, 采 用一种高效、 实用的软件冗余技术来完成双机切换。

通信由定时器 < D(%7@AYXXB ; O R 等待与对方建立通信连接, 的中断例程完成 R O

*."%(A<B

O R 备机单元的前台例行监控循环 R O

G"HA96&:070&,WW:CSUDV\B *."%(A96&:070&,WW:CSUDV\B O R 在 备 机 状 态 中 循 环 R O G和 应 用 系 统 实 现 相 关 的 备 机 例 程 ; "HAAI87"%&2(B[[A56’70(B[[2($("?(FH274(ABB 56’70(WH7%,( ; Q (%,( G56’70(W02&( ; O R 以便在未来的备机联机后再次发送备

一种嵌入式系统高可用冗余方案

嵌入式系统处理器、存储器存在受电磁干扰影响正常启动,系统可用性低问题。

本文从软件方面着手设计一套冗余方案,在不添加硬件成本的提前下提高系统可用性。

方案涉及看门狗保护启动阶段技术、U-Boot防串口干扰技术、U-Boot校验内核完整性和匹配技术、冗余双内核倒换技术、文件系统分区管理技术。

最后从多方面测试本方案的有效性,具有不错的应用前景。

1.引言嵌入式产品由于处理器、存储抗干扰能力不强,在高、低温下工作不稳定也可导致处理器跑飞。

业界嵌入式系统抗干扰和可靠性设计包括看门狗、指令冗余、数据校验、数模信号过滤(赵坤鹏,不依赖人重启。

看门狗定时器(Watchdog Timer )是一个电子定时器,用于监测计算机故障并从中恢复,在正常运行期间,计算机重置看门狗定时器以防止它超时,俗称“喂狗”,如果由于硬件故障、程序错误,计算机无法重置看门狗,定时器产生超时信号,信号通常使计算机重启(罗丹,王会燃,基于9263的嵌入式测控系统看门狗技术研究:软件导刊,2015;王彬,李文新,李得天,刘礼,通过看门狗软件设计提高抗干扰能力的方法:计算机技术与发展,2012)。

本设计中也采用看门狗监测系统故障:U-Boot 启动后立即打开看门狗,设置2s 看门狗超时,要求U-Boot 在这2s 内完成将内核从存储设备载入内存;若处于U-Boot 命令模式则设置60s 看门狗超时,一种嵌入式系统高可用冗余方案桂林聚联科技有限公司 蔡爱华 吴梦龙 阳 韬图1 存储器分区吴龙胜,马徐瀚,等.一种基于矩阵的并行CRC 校验算法:电子设计工程,2017;伍伟杰,嵌入式系统软件可靠性和抗干扰技术:电子产品可靠性与环境试验,2006)。

本文提供一种系统组织方案保障系统可靠性、可恢复性,可绕过有缺陷的内核,应用程序丢失可升级。

本系统由看门狗和5个存储分区组成,5分区分别存储U-Boot 、第一内核、第二内核、只读文件系统第一分区、可读写文件系统第二分区,如图1所示。

VxWorks环境下底层双冗余以太网卡关键技术实现

ZHoU J n i

( h n h i hp a d S i pn s a c n t u e h n h i 0 ,Ch n ) S a g a i n hp i g Re e rh I si t ,S a g a 0 5 S t 2 1 3 ia

络层和链路层 4 , 层 网卡冗余切换技术可以在其中各个层面中实现 , 但总 的来说 , 实现的层面越高, 实现的难 度越小 , 网卡 自动 切换所 需 要 的时 间越长 。

1 Vx r s网络 协议 栈 简介 Wo k

嵌入式实 时操作系统 V wok x rs的网络协议栈 与网络设备驱动 的接 口有 2 : 种是 标准 的 B D . 种 1 S4

冗余设计来作为提高设备和系统可靠性的一种方法。在双冗余网络中, 每个节点都采用网卡进行双冗余热 备份 , 中间用 2 H 个 UB或交换机互连。当正常通信的网卡或线路出现故障时, 该节点能 自动地切换到备份 网卡进行通信 。图 1 为双冗余网络一种典型连接形式 。

根据 双冗 余备 份 的要求 , 每个 节 点 只能有 1 I 址 , 个 P地 这对 于应 用层 的用 户程 序来 说 , 不用关 心 哪块 网 卡在 工作 , 就好 像 只有 1 网卡 一样 。根 据 TC /P参考 模 型 ,T P I 块 PI C /P协议 族可 以分 为应 用层 、 输层 、 传 网

收 稿 日期 :0 10 —5 2 1-70

作者 简介 : 周

进 ( 9 7) 男 , 1 7一 , 湖北 省黄冈县人 , 副研究员 , 主要从事船舶监控技术研究 。

第3 4卷

第 2期

组播及双冗余网络通信的设计与实现

组播及双冗余网络通信的设计与实现作者:李元哲朱永超来源:《现代信息科技》2017年第01期摘要:本文针对双冗余网络接口功能的实现问题,根据船用网络环境,确定了双冗余网络的主备工作模式。

根据网卡芯片架构及组播通信协议,对双网口的初始化、数据收发及网卡切换进行了分析和设计,并进行功能性能试验。

该方案满足了船用条件使用需求,具备良好的切换性能和稳定性,具备很好的实用价值。

关键词:双网卡;组播;双网冗余中图分类号:TN913.21 文献标识码:A 文章编号:2096-4706(2017)01-0063-03Abstract:This paper aiming at the realization of double redundancy network interface function,the main standby mode of dual redundancy network is determined according to the ship network environment.According to the network card chip architecture and multicast communication protocol,initialization,data transceiver and network switching of dual network is analyzed and designed,and the function of performance test.The scheme meets the requirements of ship conditions,has good switching performance and stability,and has good practical value.Keywords:dual network interface card;multicast;dual network redundancy目前的双网卡冗余网络的方案一般包括双机热备和一主一备两种方案,双机热备方案只能用于相互独立的双网,当连接在同一网段下会导致IP冲突问题,无法适应船上网络环境。

嵌入式双冗余CAN—Ethernet网关的设计与实现

Hu a Ji n , Gu o J i a n gu o

( 1 . Re s e a r c h a nd De v e l o p me n t De p a r t me n t ,Ch i na S h i p p i n g T e c h n o l o g y Co .,LTD, S h a n g h a i 2 0 01 35, Ch i n a ;

性。

1 硬 件设 计

1 . 1 C P U 单 元

中央处理 器 ( C e n t r a l P r o c e s s i n g Un i t , C P U) 芯 片选 用 NX P公 司的 L P C 2 3 7 8微 控制 器 , 其功 能 强 大 、 成

本低 、 效 率高 , 支持 1 0 / 1 0 0 M E t h e r n e t , 提供 2 路 C AN 2 . 0 B接 口、 多个 串行 接 口, 具 有 系统 编程 ( I n — S y s t e m

a n d TCP / I P p r o t o c o l s u c c e s s f u l l y .Th i s p a p e r g i v e s t h e d e s i g n o f h a r d wa r e a n d s o f t wa r e i n d e t a i l .

2 .中海船 研 科技 股份 有 限公 司 民船 产 品事业 部 , 上海 2 0 0 1 3 5 )

摘

要: 随 着 互 联 网技 术 与船 舶 自动 化 技 术 的 深 入 结 合 , 为 了 使 船 舶 控 制 系 统 实 现 现 场 控 制 网 与 信 息 管 理 网 的 无

嵌入式系统中一对多通信技术设计与实现

嵌入式系统中一对多通信技术设计与实现摘要:针对当前高校实验室信息管理自动化布线困难、建设及维护费用高、信息反馈不及时的问题,提出一种使用物联网rfid射频识别技术来实现实验室智能开放管理的方案。

系统使用msp430单片机作为实验室主控系统,负责接收并处理无线模块传送的设备使用信息,并通过tcp连接服务器获取并操作数据。

该方案可以使实验室管理更加科学化、信息化、自动化,提高实验管理水平与设备使用效率。

关键词:物联网;无线通信;一对多;实验室管理;自动化;实验过程控制中图分类号:tp393 文献标识码:a 文章编号:1009-3044(2013)12-2792-03在电子商务和物联网应用中,射频卡技术和无线数据通讯技术是不可或缺的重要组成部分,因此,在智能实验室管理中,实验台51单片机与实验室主控系统msp430单片机之间的分布式通信尤为重要,两者之间采用一对多无线通信,可以降低布线及维护难度。

通信是本系统中的关键环节,msp430单片机通过tcp网络连接与控制室通信,获取相关数据。

而后,msp430单片机与多个实验台51单片机进行通信,将设备分配情况分别存储于实验台51单片机。

1 nrf24l01无线通信原理无线通信模块采用工作在2.4ghz,ism频段的nrf24l01芯片,具有低功耗的特点,其工作电压为1.9~3.6v,通过spi总线与mcu相连。

具有126个频道,能够满足多点通信和跳频通信的需要,支持crc校验,能够提供高达2mbps的传输速率,可以工作在有较强干扰、低功耗的场合。

实验测试证明,当有门、窗、墙等障碍物阻挡时,无线射频通信范围在10~20m,适用于单个实验室内部通信。

如需更大通信范围,可适当增加功率放大装置。

多个实验室可以分别使用不同的频道。

以下为nrf24l01无线模块操作的基本函数:设置通讯频段:nrf_set_channel(0);设置数据通道:nrf_set_pipe(0);设置为接收模式:set_nrf_rx_mode();读取rf-setup寄存器值:nrf_spi_read_reg(rf_setup);设置发射速率:nrf_spi_rw_reg(nrf_write_reg+rf_setup,0x__);接收数据:nrf_rxpacket(rx_payload);发送数据:nrf_txpacket(string);2 硬件配置结构分析2.1 实验台51单片机简介实验台51单片机采用最新的stc11f60xe高速1t型单片机,单时钟周期指令执行,60kb片内flash,1280b片内ram,运行速度高达32mhz,完全满足复杂系统开发。

基于FPGA的嵌入式千兆网冗余设计(全文)

基于FPG的嵌入式千兆XX冗余设计千兆XX相比其它通信方式具有传输速度快、组XX方式灵活等特点,因此在嵌入式系统当中得到越来越多的应用。

随着系统间数据交互量的增大,对XX络带宽和数据安全需求的提高。

本文利用FPG的优点设计了一种嵌入式千兆XX冗余设计方案,可以很好的满足复杂环境下对数据带宽和数据安全的要求。

嵌入式系统以其架构多样、硬件成本低、小型化、执行效率高等优点,在军事、航天、航空、自动操纵等领域得到越来越多的应用。

随着时代的进展,嵌入式系统处理的数据量越来越大,系统之间的数据交互量也变得越来越大。

因此对系统间的数据接口要求也变得越来越高。

千兆以太XX以其连接芯线数量少、传输速度高、组XX方式灵活、可进行多发多收等优点,在嵌入式系统当中得到越来越多的应用。

工程实际主要应用于舰船复杂环境下接收无压缩的高分辨率数字图像,并通过板间总线传输给其它芯片处理。

由于高分辨率数字图像不能进行压缩,因此数据量非常大,对XX络带宽占用在700Mb/s以上,因此对XX络数据吞吐能力要求较高。

舰船在复杂环境下对数据安全要求很高,实际设计上要求提供主备IP地址,且每路IP地址都要有两路物理连接,且能自动在毫秒级进行切换。

针对以上客观实际要求,我们需要采取特别的设计方案。

1 设计思路优选常见的嵌入式千兆XX设计方案主要有以下几种:1.主控芯片+NON-PCI芯片;2.TI公司自带千兆XX接口RM芯片;3.TI 公司基于NDK开发库的带千兆XX接口的DSP;4.自带千兆XX 接口的Power pc芯片;5.基于FPG的千兆XX设计。

以上方案各自具有不同的优缺点。

方案一开发最简便,开发成本最低,但NON-PCI芯片受限于接口形式,无法满足大带宽需求,且NON-PCI芯片只有民用级芯片,无法满足复杂自然环境下的应用;方案二开发难度中等,开发成本中等,但TI已经不再推出RM芯片,后续产品的研制维护存在困难,切相对其它RM芯片厂商,价格偏贵;方案三由于NDK库为基于底层硬件设计,因此开发难度相对较大,且芯片成本、开发工具成本比较高;方案四软件由于芯片支持操作系统,因此开发难度相对较容易,但芯片昂贵,且很少有自带多个XX络接口冗余设计不方便;方案五由于FPG自带有Power pc内核,因此软件开发难度与方案四大体相当,且FPG内部自带多个三态以太XX硬核,因此比较适合进行冗余设计。

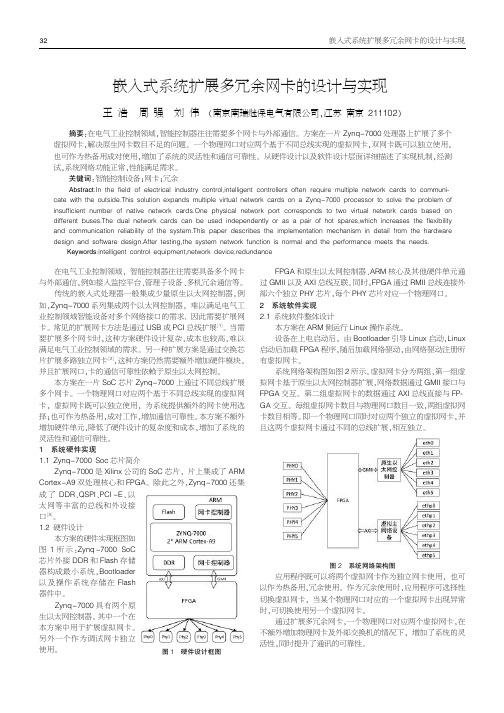

嵌入式系统扩展多冗余网卡的设计与实现

在电气工业控制领域,智能控制器往往需要具备多个网卡与外部通信,例如接入监控平台、管理子设备、多机冗余通信等。

传统的嵌入式处理器一般集成少量原生以太网控制器,例如,Zynq-7000系列集成两个以太网控制器,难以满足电气工业控制领域智能设备对多个网络接口的需求熏因此需要扩展网卡。

常见的扩展网卡方法是通过USB或PCI总线扩展[1]。

当需要扩展多个网卡时,这种方案硬件设计复杂,成本也较高,难以满足电气工业控制领域的需求。

另一种扩展方案是通过交换芯片扩展多路独立网卡[2],这种方案仍然需要额外增加硬件模块,并且扩展网口,卡的通信可靠性依赖于原生以太网控制。

本方案在一片SoC芯片Zynq-7000上通过不同总线扩展多个网卡。

一个物理网口对应两个基于不同总线实现的虚拟网卡,虚拟网卡既可以独立使用,为系统提供额外的网卡使用选择;也可作为热备用,成对工作,增加通信可靠性。

本方案不额外增加硬件单元,降低了硬件设计的复杂度和成本,增加了系统的灵活性和通信可靠性。

1系统硬件实现1.1Zynq-7000Soc芯片简介Zynq-7000是Xilinx公司的SoC芯片,片上集成了ARM Cortex-A9双处理核心和FPGA。

除此之外,Zynq-7000还集成了DDR、QSPI、PCI-E、以太网等丰富的总线和外设接口[3]。

1.2硬件设计本方案的硬件实现框图如图1所示:Zynq-7000SoC芯片外接DDR和Flash存储器构成最小系统,Bootloader以及操作系统存储在Flash器件中。

Zynq-7000具有两个原生以太网控制器。

其中一个在本方案中用于扩展虚拟网卡。

另外一个作为调试网卡独立使用。

FPGA和原生以太网控制器、ARM核心及其他硬件单元通过GMII以及AXI总线互联。

同时,FPGA通过RMII总线连接外部六个独立PHY芯片,每个PHY芯片对应一个物理网口。

2系统软件实现2.1系统软件整体设计本方案在ARM侧运行Linux操作系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第41卷第5期2018年10月电子器件ChineseJournalofElectronDevicesVol 41㊀No 5Oct.2018收稿日期:2017-11-08㊀㊀修改日期:2018-01-02DesignandImplementationofEmbeddedDualRedundantNetworkCommunicationZHOUYunshui1∗ꎬJIANGBo2ꎬLIJian2(1.ZhejiangCollegeofZhejiangUniversityofTechnologyꎬShaoxingZhejiang312030ꎬChinaꎻ2.HangzhouNavigationInstrumentCo.ꎬLtdꎬHangzhou310024ꎬChina)Abstract:InordertoimprovethereliabilityofUDPcommunicationꎬanembeddeddualredundantnetworkUDPcommunicationmodulebasedonSTM32F429andW5500wasdesignedandimplemented.Themutualhotbackupdualredundantcircuitwasdesignedbyhardwareꎬandtimeslicepollingmethodwasappliedinsoftware.MCUfoundthenetworkfaultbyreadingtheregistersofW5500.Afastandreliablehandoverstrategywasdesignedtoachievethehandoverbetweentwonetworksꎬandthehandofftimewaslessthan10ms.Itwasstableandreliablewhenworkinginrealenvironment.Keywords:embeddedꎻdualredundantnetworkꎻUDPꎻtimeslicepollingEEACC:6210C㊀㊀㊀㊀doi:10.3969/j.issn.1005-9490.2018.05.042嵌入式双网冗余通信设计与实现周云水1∗ꎬ江㊀波2ꎬ李㊀健2(1.浙江工业大学之江学院ꎬ浙江绍兴312030ꎻ2.杭州航海仪器有限公司ꎬ杭州310024)摘㊀要:为提高UDP网络通信的可靠性ꎬ设计了一个基于STM32F429和W5500的嵌入式双网冗余UDP通信模块ꎬ硬件上设计了相互热备份双网冗余电路ꎬ软件上采用了时间片轮询方法ꎬ通过读取W5500状态数据发现网络故障ꎬ并设计了快速可靠的切换策略ꎬ实现了两路网络的切换ꎬ切换时间小于10msꎮ该设备在实际应用过程中ꎬ工作稳定可靠ꎮ关键词:嵌入式ꎻ双网冗余ꎻUDPꎻ时间片轮询中图分类号:TP336㊀㊀㊀㊀文献标识码:A㊀㊀㊀㊀文章编号:1005-9490(2018)05-1296-04㊀㊀在一些工业现场ꎬ广泛采用嵌入式UDP网络进行数据传输ꎬ但大部分是传统的单链路网络ꎬ由于工业现场环境复杂ꎬ无法避免的网络故障(网线松动㊁交换机等故障)可能会导致传输中断ꎮ另外ꎬUDP通信没有反馈机制和数据丢失重传机制ꎬ也无法保证数据的可靠传输[1-2]ꎮ为提高UDP通信的可靠性ꎬ常在工业网络中采用相互热备份双网冗余切换的保障策略ꎬ其网络拓扑结构如图1所示ꎬ该拓扑结构采用双网级联的形式ꎬ对于单个设备来说ꎬ某个时刻ꎬ只有一个网络在工作ꎮ若网络A在工作中一旦发生故障ꎬ立即切换到网络Bꎬ反之ꎬ也一样ꎮ网络A和B配置成相同的IP地址和端口ꎮ图1㊀双冗余网络拓扑结构针对拓扑结构中的设备ꎬ本文设计并实现了在ARM ̄cortex ̄M4系列器件STM32F429VE上完成双第5期周云水ꎬ江㊀波等:嵌入式双网冗余通信设计与实现㊀㊀网冗余切换热备份UDP通信ꎮ硬件采用了STM32F429VE自带的两路SPI接口分别与两路网络控制芯片W5500连接ꎬ软件采用了时间片轮询方法ꎬ通过读取W5500状态数据发现网络故障ꎬ并设计了快速可靠的切换策略ꎬ实现了两路网络的切换ꎬ切换时间小于10msꎬ提高了UDP网络数据传输的可靠性[3-5]ꎮ1㊀硬件设计1.1㊀主要器件1.1.1㊀STM32F429微控制器本设计采用意法半导体(ST)公司的STM32F429VEꎬ该芯片是以32位Cortex ̄M4为内核ꎬ具有180MHz的工作频率ꎬ内置高速存储器(512kbyteFLASHꎬ256kbyteRAM)和6路SPI及其他丰富的外设接口ꎮ图3㊀其中一路网络电路图1.1.2㊀W5500以太网接口芯片本设计采用WIZnet公司的高性能以太网接口芯片W5500ꎬ其内部集成了全硬件TCP/IP协议栈㊁以太网数据链路层(MAC)和10BaseT/100BaseTX以太网物理层(PHY)ꎮW5500支持TCP㊁UDP㊁ICMP㊁IPv4㊁ARP㊁IGMP㊁PPPoE80MHz时钟的SPI接口ꎮ与传统软件协议栈不同ꎬW5500内嵌的8个独立硬件Socket可以进行8路独立通信ꎬ该8路Socket的通信效率互不影响ꎬ可以通过W5500片上32kbyte的收/发缓存灵活定义各个Socket的大小[7-8]ꎮ1.2㊀硬件电路设计STM32F429通过两路自带的高速SPI接口与两个W5500相连ꎬ其原理框图如图2所示ꎮ图2㊀双网冗余硬件原理框图图2中ꎬ一路网络的实际电路图如图3所示ꎬ该路W5500通过SPI接口与控制器STM32F429的SPI1相连ꎬ其RX差分对㊁TX差分对与带RJ45的网络变压器HR911105A相连[9]ꎮ7921电㊀子㊀器㊀件第41卷2㊀软件设计2.1㊀软件流程图本软件设计采用时间片轮询方法ꎬ将整个处理过程分成4个任务ꎬ分别是 网络切换任务处理 ㊁ 网络接收任务处理 ㊁ 网络发送任务处理 ㊁ 超时及调度任务处理 ꎬ每个任务占用1ms时间ꎬ也就是每4ms判断了一次两个网络的状态ꎬ若发生网络切换ꎬ切换时间不会超过4msꎮ其主循环流程如图4所示ꎮ图4㊀主循环流程图图4中ꎬ 初始化 主要包括 系统时钟配置㊁端口设置㊁定时器设置㊁看门狗设置㊁W5500UDP网络参数配置 等ꎬ两路W5500配置成相同的IP地址㊁相同的源端口㊁相同的目的端口ꎮ另外ꎬ控制器读取两个W5500的PHYCFGR寄存器状态ꎬ判断两个网络其是否处于LINK状态ꎬ若两个都处于LINK状态ꎬ则选择其中一个作为网络发送任务的网络ꎻ若有一个或两个网络未处于LINK状态ꎬ则报故障ꎬ查明原因㊁修复后才进入后续主循环任务ꎮ2.2㊀各个任务处理流程2.2.1㊀网络切换任务处理网络切换的策略设计如下:判断两个网络是否处与LINK状态ꎬ共有3种情况ꎬ第1种情况是两个网络都处于LINK状态ꎬ则根据当前是哪个网络接收到数据就激活哪个网络的原则ꎬ确定网络发送任务的网络ꎻ第2种情况是两个网络只有一个处于LINK状态ꎬ则只能激活这个网络ꎬ确定它为网络发送任务的网络ꎬ并报故障信息ꎻ第3种情况是两个网络都未处于LINK状态ꎬ报两个网络均故障信息ꎮ激活网络的方法是对该W5500复位ꎬ重新配置网络参数ꎮ其处理流程图如图5所示ꎮ2.2.2㊀网络接收任务处理本设计采用查询的方式进行网络数据接收ꎬ并对接收到的数据进行相应的处理ꎬ其处理流程图如图6所示ꎮ图5㊀网络切换任务处理流程图图6㊀网络接收任务处理流程图2.2.3㊀网络发送任务处理根据网络切换任务处理的结果选择相应的网络ꎬ将待发送的数据存入发送缓存器中ꎬ启动网络发送任务ꎮ处理流程图略ꎮ2.2.4㊀超时及调度任务处理本设计中ꎬ由于采用UDP通信方式㊁还可能在收发报文时发生网络故障ꎬ因此设计了超时处理流程ꎮ若在向某设备发送了某些网络报文后未能在规定的时间内未收到其网络应答报文ꎬ则启动超时处理ꎬ比如再次发送报文等措施ꎬ尽量避免报文遗漏ꎮ处理流程图略[10-12]ꎮ3㊀系统测试设备实物如图7所示ꎬ配置其网络参数如下:网关参数192.168.1.1ꎬ子网掩码255.255.255.0ꎬ本机IP地址192.168.1.10ꎬ源端口号5000ꎬ目的端口号6000ꎬ工作模式为UDPꎮ通过双网连接到两个交换机ꎬPC1和PC2也分别连接到两个交换机ꎬ其验证测试硬件连接如图8所示ꎮ8921第5期周云水ꎬ江㊀波等:嵌入式双网冗余通信设计与实现㊀㊀图7㊀设备实物图8㊀验证测试连接图测试过程如下ꎬ首先设置网络A处于激活状态ꎬ通过PC机以500次/s的频率向网络A发数据ꎬ在 超时任务处理 中增加串口发送 网络切换时间 功能ꎮ经多次插拔网络A的网线ꎬ人为模拟网络A故障ꎬ检测网络切换时间ꎮ检测方法如下ꎬ当检测到处于激活状态的网络A发生故障时ꎬSTM32F429读取此时的SYSTEMTICK值ꎬ当网络B正常接收数据时ꎬ再次读取SYSTEMTICK值ꎬ两者的差值就是的网络切换时间间隔ꎬ经过多次试验ꎬ网络切换时间均小于10msꎬ该嵌入式UDP双网冗余通信系统工作正常ꎮ4㊀结束语本设计硬件采用了高性能的STM32F429与相互备份的两路W5500ꎬ软件应用了时间片轮询方法ꎬ设计了可靠的网络切换策略ꎬ实现了嵌入式双网冗余UDP网络通信ꎬ该设备工作稳定可靠ꎮ参考文献:[1]㊀屈景怡ꎬ杨俊ꎬ高泽应ꎬ等.空管系统中高可靠性双网冗余方法研究[J].计算机应用研究ꎬ2014ꎬ31(8):2430-2433.[2]李乐义ꎬ史洪源ꎬ杜军钊.基于CPLD的Profibus ̄DP冗余双网切换逻辑的设计[J].测控技术ꎬ2011ꎬ30(2):83-85.[3]易宇航ꎬ张开法ꎬ田广平.基于ARMCortex ̄M4双网口扩展的设计与实现[J].自动化与仪表ꎬ2016(10):74-76.[4]吕跃刚ꎬ刘浩ꎬ李子民.W5500在风电机组状态监测远程通信的应用[J].仪器仪表用户ꎬ2015ꎬ22(3):62-64.[5]汤巧戈ꎬ高强ꎬ刘超.基于STM32的嵌入式以太网定位系统[J].兵工自动化ꎬ2017ꎬ36(5):17-20.[6]杨俊ꎬ屈景怡ꎬ吴仁彪.基于双网的高可靠UDP通信方法[J].计算机工程与设计ꎬ2016ꎬ37(3):567-570.[7]强景ꎬ赵多ꎬ王红兵.PwerPC下双网冗余热备份高速切换技术的实现[J].单片机与嵌入式应用系统ꎬ2016ꎬ3:24-26.[8]徐业荣ꎬ包明磊ꎬ李明.一种基于lwIP协议栈的双网口通信方案设计[J].计算机应用与软件ꎬ2016ꎬ33(9)127-129.[9]曾红ꎬ党盼盼.基于W5500的嵌入式系统以太网网关设计[J].网络安全技术与应用ꎬ2015(2):36-37.[10]翟明玉ꎬ高原ꎬ杨志宏.调度自动化系统双网卡热备冗余机制的设计与实现[J]电力系统自动化ꎬ2012ꎬ36(8):87-91.[11]张丽蓉.双网冗余模块的设计[J].计算机工程ꎬ2002ꎬ28(12):160-162ꎬ220.[12]陈昕ꎬ杨杰ꎬ周拥军.航空全双工交换以太网冗余管理机制研究[J].计算机工程与应用ꎬ2009ꎬ45(2):102-105.周云水(1975-)ꎬ江西临川人ꎬ男ꎬ讲师ꎬ主要从事嵌入式㊁无线通信等方面的研究ꎬzhouys@zjut.edu.cnꎮ9921。