手机频率合成器电路分析

MTK手机原理图分析

手机原理图分析一、手机基本电路框图:二、基带CPU(MT6226)内部框图:1、组成部分:z DSP:主要完成对语音信号的编解码、信道编码、加密、交织处理等;z ARM7:主要是对外部Memory接口、用户接口(LCD、键盘、触摸等)、语音接口、射频接口、电源管理等的命令控制,使各部分协调工作。

2、基带部分语音编码过程(DSP):GSM标准规定时隙宽为0.577ms,8个时隙为一帧,帧周期为0.577×8=4.615ms。

因此,用示波器观测GSM移动电话机收发信息,会看到周期为4.615ms、宽0.577ms的突发脉冲。

基带部分电路包括信道编/译码、加密/解密、TDMA帧形成/信道分离及基准时钟电路,它还包括话音/译码、码速适配器等电路。

来自送话器的话音信号经过8kHz抽样及A/D转换,变成13bit均匀量化的104kbit/s数据流,再由话音编码器进行RPE-LTP编码。

编码输入为每20ms一段,经话音编码压缩后变为260bit,其中LPC-LTP为72bit,RPE为188bit。

话音编码后的信号速率为13kbit/s。

同时话音编码器还提供话音活性检测(vAD)功能,即当有话音时,其SP信号为1;当无话音传输时,将SP示为0(即SID帧)。

13kbit/s 话音信号进入信道编码器进行编码。

对于话音信号的每20ms 段,信道编码器首先对话音信号中最重要的Ia 类50bit 进行分组编码(CRC 校验),产生3bit 校验位,再与132bit 的Ib 类比特组成185bit ,再加上4个尾比特“0”,组合为189bit ,这189bit 再进入1/2速率卷积码编码器,该编码限制长度为5,最后产生出378bit 。

这378bit 再与话音信号中对无线信道最不敏感的II 类78bit 组成最终的456bit 组。

同样,对于信令信号,由控制器产生并送给信道编码器,首先按FIRE(法尔)码进行分组编码(称为块编码),然后再进入1/2卷积编码,最后形成456bit 组。

通信终端设备原理与维修实训 样章 五章 手机电路分析

手机电源电路中还有一些基本的电路。 1. 电池供电电路 电池供电电路是指外接电源或者电池供电到手机的转换电路和保护电路。手机电池电压 和外接电源电压经过电池供电电路以后,一般称为 B+电压或者 BATT、VBATT 等。 2. 开机信号电路 手机开机以后,手机各个功能电路才会得到工作电压,关机以后就没有工作电压。所以 稳压电源 IC 要受到手机开关机信号的控制。手机开机第一步是通过按下开关机键,产生开 机信号,去触发启动稳压电源。开机信号常用 ON/OFF、POWERON、POWERKY 等表示。 手机的开机方式有两种:一种是高电平开机方式,当开关键被按下时候,开关键触发端 接到电池电压,用高电平去触发启动电源 IC。二种是低电平开机方式,当开关机键被按下 时候,开关键触发端接地,用低电平去触发启动电源 IC。这两种方式没有好坏之分,在电 路图中观察,如果开机键一端接电池正极,则是高电平开机方式,如果开机键一端接电池地, 则是低电平开机方式。 3. 升压电路 由于电池电压较低,而有些电路需要较高工作电压,或者电池电压随着用电时间增长而 降低,所以手机中常采用升压电路。当然并不是所有的手机都有升压电感,要看手机厂家和 手机电路设计而定。 升压电路本质是开关稳压电源,由电感、电源模块(一般是稳压电源 IC,提供电子开 关)、放电电容、续流二极管等配合组成,完成对手机电池电压小幅度提升,如图 5-4 所示。 升压电路中的电感经常被称为升压电感,或者是储能电感。

5.2 手机充电电路

市场所谓的充电器,实际上是适配器,我们有必要区分这两种功能。适配器主要是把交 流市电转换成直流电,根据电池的规格提供相应的电压电流,一般采用恒压恒流方式,能够 隔离主电压和危险电压,对市电波动有一定耐受力,需要时可安全关断。

而充电器的主要功能是把充电电流限制在一个安全水平上,主要采用恒流方式,能检测 充电的完成,根据某种算法终止充电以延长电池寿命,若发现电池异常可终止充电。GSM 手机通常包含充电功能,与手机配套的只需适配器。

(完整版)锁相环工作原理

基本组成和锁相环电路1、频率合成器电路频率合成器组成:频率合成器电路为本机收发电路的频率源,产生接收第一本机信号源和发射电路的发射信号源,发射信号源主要由锁相环和VCO电路直接产生。

如图3-4所示。

在现在的移动通信终端中,用于射频前端上下变频的本振源(LO),在射频电路中起着非常重要的作用。

本振源通常是由锁相环电路(Phase-Locked Loop)来实现。

2.锁相环:它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域3.锁相环基本原理:锁相环包含三个主要的部分:⑴鉴相器(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。

⑶压控振荡器(VCO):振荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。

在PLL中,压控振荡器实际上是把控制电压转换为相位。

1、压控振荡器的输出经过采集并分频;2、和基准信号同时输入鉴相器;3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4、控制VCO,使它的频率改变;5、这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环电路是一种相位负反馈系统。

一个完整的锁相环电路是由晶振、鉴相器、R分频器、N分频器、压控振荡器(VCO)、低通滤波器(LFP)构成,并留有数据控制接口。

锁相环电路的工作原理是:在控制接口对R分频器和N分频器完成参数配置后。

晶振产生的参考频率(Fref)经R分频后输入到鉴相器,同时VCO的输出频率(Fout)也经N分频后输入到鉴相器,鉴相器对这两个信号进行相位比较,将比较的相位差以电压或电流的方式输出,并通过LFP滤波,加到VCO的调制端,从而控制VCO的输出频率,使鉴相器两输入端的输入频率相等。

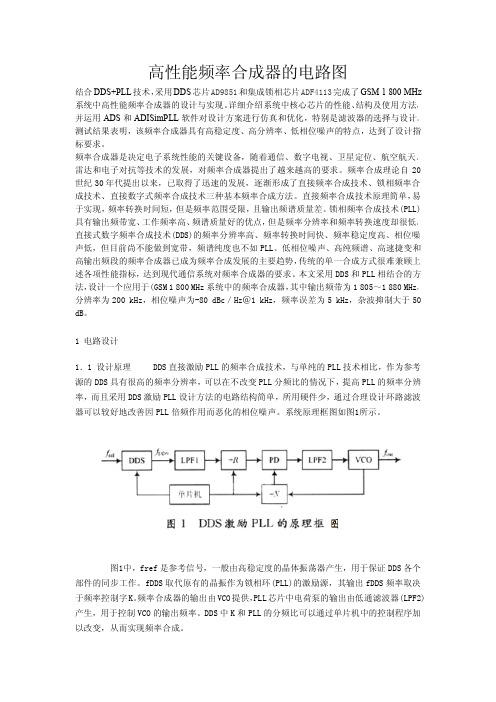

高性能频率合成器的电路图

高性能频率合成器的电路图结合DDS+PLL技术,采用DDS芯片AD9851和集成锁相芯片ADF4113完成了GSM1800MHz 系统中高性能频率合成器的设计与实现。

详细介绍系统中核心芯片的性能、结构及使用方法,并运用ADS和ADISimPLL软件对设计方案进行仿真和优化,特别是滤波器的选择与设计。

测试结果表明,该频率合成器具有高稳定度、高分辨率、低相位噪声的特点,达到了设计指标要求。

频率合成器是决定电子系统性能的关键设备,随着通信、数字电视、卫星定位、航空航天、雷达和电子对抗等技术的发展,对频率合成器提出了越来越高的要求。

频率合成理论自20世纪30年代提出以来,已取得了迅速的发展,逐渐形成了直接频率合成技术、锁相频率合成技术、直接数字式频率合成技术三种基本频率合成方法。

直接频率合成技术原理简单,易于实现,频率转换时间短,但是频率范围受限,且输出频谱质量差。

锁相频率合成技术(PLL)具有输出频带宽、工作频率高、频谱质量好的优点,但是频率分辨率和频率转换速度却很低。

直接式数字频率合成技术(DDS)的频率分辨率高、频率转换时间快、频率稳定度高、相位噪声低,但目前尚不能做到宽带,频谱纯度也不如PLL。

低相位噪声、高纯频谱、高速捷变和高输出频段的频率合成器已成为频率合成发展的主要趋势,传统的单一合成方式很难兼顾上述各项性能指标,达到现代通信系统对频率合成器的要求。

本文采用DDS和PLL相结合的方法,设计一个应用于(GSM1800MHz系统中的频率合成器,其中输出频带为1805~1880MHz,分辨率为200kHz,相位噪声为-80dBc/Hz@1kHz,频率误差为5kHz,杂波抑制大于50 dB。

1电路设计1.1设计原理DDS直接激励PLL的频率合成技术,与单纯的PLL技术相比,作为参考源的DDS具有很高的频率分辨率,可以在不改变PLL分频比的情况下,提高PLL的频率分辨率,而且采用DDS激励PLL设计方法的电路结构简单,所用硬件少,通过合理设计环路滤波器可以较好地改善因PLL倍频作用而恶化的相位噪声。

频率合成技术

1、直接模拟频率合成

直接模拟频率合成技术是一种早期旳频率合成技术,它用一种或几 种参照频率源经谐波发生器变成一系列谐波,再经混频、分频、倍频和 滤波等处理产生大量旳离散频率,这种措施旳优点是频率转换时间短、 相位噪声低,但因为采用大量旳混频、分频、倍频和滤波等途径,使频 率合成器旳体积大、成本高、构造复杂、轻易产生杂散分量且难于克制。 不能实现单片集成,逐渐被锁相频率合成,直接数字频率合成技术替代。

K

累加寄存器输出旳累加相位数据相加,把相加后旳成果送至累加寄存器旳数据输入端。累 加寄存器将加法器在上一种时钟脉冲作用后所产生旳新相位数据反馈到加法器旳输入端, 以使加法器在下一种时钟脉冲旳作用下继续与频率控制字相加。这么,相位累加器在时钟 作用下,不断对频率控制字进行线性相位累加。由此能够看出,相位累加器在每一种时钟 脉冲输入时,把频率控制字累加一次,相位累加器输出旳数据就是合成信号旳相位,相位 累加器旳溢出频率就是DDS输出旳信号频率。

DDS问世之初,构成DDS元器件旳速度旳限制和数字化引起旳噪声这两个主要缺 陷阻碍了DDS旳发展与实际应用。近几年超高速数字电路旳发展以及对DDS旳进一步 研究,DDS旳最高工作频率以及噪声性能已接近并到达锁相频率合成器相当旳水平。

2、锁相频率合成技术 (1)锁相环路工作原理

PD ————产生误差电压 ,LF ————产生控制电压, VCO ————产生瞬时输 出频率

PLL环路在某一原因作用下,利用输入与输出信号旳相位差产生误差电压,并滤除其 中非线性成份与噪声后旳纯净控制信号控制压控振荡器,使相位差朝着缩小固有角频 差方向变化,一旦相位差趋向很小常数(称为剩余相位差)时,则锁相环路被锁定了,

波形存储器设计主要考虑旳问题是其容量旳大小,利用波形幅值旳奇、偶对称特征,能够节省3/4 旳资源,这是非常可观旳。为了进一步优化速度旳设计,能够选择菜单Assign|Global Project Logic Synthesis旳选项Optimize10(速度),并设定Global Project logic Synthesis Style为FAST,经寄存器性 能分析最高频率到达100MHz以上。用FPGA实现旳DDS能工作在如此之高旳频率主要依赖于FPGA先 进旳构造特点。

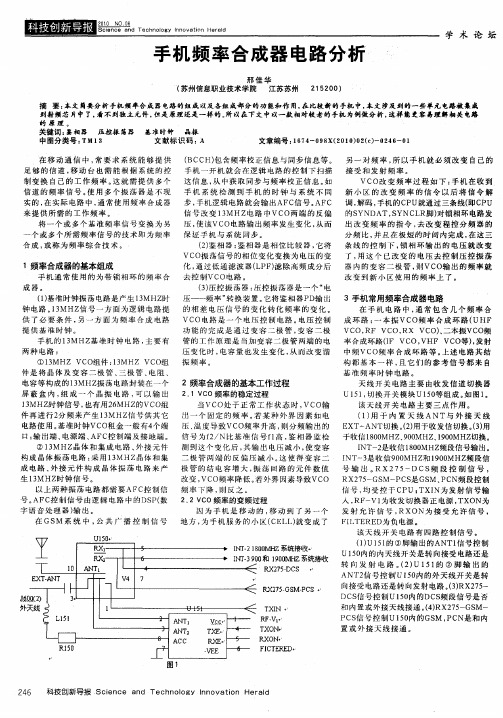

手机频率合成器电路分析

Sci enc e an Tech I d n0 Ogy nn I ovaton i He al r d

学 术 论 坛

手 机 频 率合 成器 电路 分 析

邢 佳 华 ( 州信 息职业技 术学院 江苏苏州 21 2 0 苏 0) 5 摘 要: 本文 简要 分析 手机频率合成器 电路 的组成 以及各 组成部分的功 能和作 用, 比较 新的手机 中, 在 本文涉及到 的一些单 元电路被 集成 到射频芯 片中了, 看不到独立元件 , 但是 原理还是一样的 。 以在下文 中以一款 相对较 老的手机 为例做 分析 , 所 这样能更容 易理解 相关电路

成 器。 () 控 振 荡 器 : 控振 荡 器 是一 个 “ 3压 压 电 () 准时 钟振 荡 电路 是产 生 1 MHZ 1基 3 时 压——频 率 ” 换 装 置 。 将 鉴相 器 P 转 它 D输 出 3手机常用频率合成器电路 钟 电路 。 MHZ l 3 信号 一 方 面 为 逻 辑 电 路提 的 相 差 电压 信 号 的 变化 转 化 频 率 的 变 化 。 在 手 机 电 路 中 , 常 包 含 几 个 频 率 合 通 供 了必 要 条 件 , 另一 方 面 为 频 率 合 成 电路 VC O电路 是 一 个 电压 控 制 电路 。 电压 控 制 成 环 路 : 本 振 VC 一 O频 率 合 成 环 路 ( UHF 提供基准时钟 。 功 能 的 完 成 是 通 过 变 容 二 极 管 , 容 二 极 Vc RF VC Rx VC )二 本振VC 频 变 0, O, O 、 O 手 机 的 1 MHZ 准 时 钟 电 路 , 要 有 管 的 工 作 原理 是 当加 变 容 二 极 管 两端 的 电 3 基 主 率 合成 环路 ( O, I VC VHF F VC O等)发 射 , 两种 电路 : 压 变 化时 , 电容 量 也发 生 变 化 , 而 改 变 谐 中频 VC 从 O频 率 合 成 环 路 等 。 述 电 路 其 结 上 ① l MHZ 3 VCO组件 : MHZ 1 3 VCO组 振 频 率 。 构都基本 一样 , 它们的参考信号都来 自 且

7.2__DDS(直接数字式频率合成器)电路

7.2.1 基于AD9834的50MHz DDS电路

AD9834是一个将相位累加器、正弦只读存储器(SIN ROM) 和一个10位D/A转换器集成在一个CMOS芯片上的、一个完 全集成的DDS(Direct Digital Synthesis)芯片,频率精确性 能被控制在0.25billion(十亿分之一),时钟频率为50MHz, 具有低抖动的时钟输出和正弦波输出/三角波输出,窄带 SFDR>72dB。控制字采用串行装载方式,通过串行接口装 载控制字到寄存器,可以实现相位和频率调制。 AD9834为用户提供了多种输出波形。利用SIN ROM将产生 一个正弦曲线输出。SIN ROM可以被旁路,可以直接从DAC 输出线性向上斜坡电压或者向下斜坡电压。另外,如果需要 时钟输出,可以将DAC 数据的MSB位作为时钟输出,或者利 用芯片上的比较器。

数字部分电源电压由在芯片上的一个稳压器提供,当 DVDD输入电压超过2.7V时,稳压器使芯片内部数字部 分电源电压下降到2.5V。 模拟和数字部分电源是独立的,并且可以由不同的电 源驱动,例如,在AVDD输入电压等于5V时,DVDD输 入电压可以等于3V。AD9834电源电压为2.3~5.5V, 在3V电源电压时仅消耗功率20mW。AD9834有一个低 功耗模式控制引脚端(SLEEP),可以利用外部控制器 控制芯片的低功耗模式。AD9834采用TSSOP20封装。

⑤ 稳压器(Regulator) 对于芯片内部的模拟电路和数字电路,AD9834提供独立的 电源。AVDD提供了模拟电路部分所需要的电源,而DVDD则 提供了数字电路部分所需要的电源。这两个电源的取值范围 均为2.3~5.5V,而且每个都是独立的,例如,模拟电路部 分能够工作在5V电压下,而同时数字电路部分工作在3V,或 者是其他值。 AD9834内部的数字电路部分通常工作在2.5V。在芯片上的 稳压器将在DVDD输入的电源电压降至2.5V。AD9834的数字 接口(串行端口)工作电压也来自DVDD。这些数字信号在 AD9834内进行调整,使它们与2.5V一致。 当AD9834的DVDD引脚的电源电压等于或小于2.7V时,引脚 端CAP/2.5V和DVDD将同时被约束,从而将芯片上的稳压器 旁路。

锁相式数字频率合成器实验报告.

*******************实践教学*******************兰州理工大学计算机与通信学院2012年春季学期《通信系统基础实验》设计项目实验报告设计题目:锁相式数字频率合成器实验报告专业班级:设计小组名单:指导教师:陈昊目录一、设计实验目的 (3)二、频率合成基本原理 (4)2.1频率合成的概念 (4)2.2频率合成器的主要技术指标 (4)2.3锁相频率合成器 (5)三、锁相环技术 (6)3.1 锁相环工作原理 (6)3.2 锁相环CD4046芯片介绍 (6)四、基于锁相环技术的倍频器 (10)4.1 HS191芯片介绍 (10)4.2 基于锁相环技术的倍频器的设计 (12)4.2.1 工作原理 (12)3.2.2 Proteus软件仿真 (13)4.2.3 硬件实现 (14)4.2.4 锁相环参数设计 (15)五、总结与心得 (17)六、参考文献 (18)七、元器件清单 (19)一、设计实验目的1. 掌握VCO压控振荡器的基本工作原理。

2. 加深对基本锁相环工作原理的理解。

3. 熟悉锁相式数字频率合成器的电路组成与工作原理.。

二、频率合成基本原理2.1频率合成的概念频率合成是指由一个或多个频率稳定度和精确度很高的参考信号源通过频率域的线性运算,产生具有同样稳定度和精确度的大量离散频率的过程。

实现频率合成的电路叫频率合成器,频率合成器是现代电子系统的重要组成部分。

在通信、雷达和导航等设备中,频率合成器既是发射机频率的激励信号源,又是接收机的本地振荡器;在电子对抗设备中,它可以作为干扰信号放生器;在测试设备中,可作为标准信号源,因此频率合成器被人们称为许多电子系统的“心脏”。

早期的频率合成是用多晶体直接合成,以后发展成用一个高稳定参考源来合成多个频率。

20世纪50年代出现了间接频率合成技术。

但在使用频段上,直到50年代中期仍局限于短波范围。

60年代中期,带有可变分频的数字锁相式频率合成器问世。

频率合成技术原理

1.1 频率合成技术频率源作为通信系统中的重要组成部分,在通信系统中起到关键的作用,随着现代通信技术向着高速率、高频率的方向发展,要求频率综合器向着高频率、超宽带、小步进、快速跳频、低杂散、低相位噪声的方向发展错误!未找到引用源。

得益于电子器件和微电子技术的发展,频率合成技术也得到了突破性的发展。

尤其是数字频率合成技术的出现,大大促进了小步进、捷变频频率合成器的发展错误!未找到引用源。

错误!未找到引用源。

1.1.1 数字直接频率合成技术数字频率合成器(DDS )的组成主要有波形存储器 、相位累加器、低通滤波器、D/A 转换器等错误!未找到引用源。

图 错误!文档中没有指定样式的文字。

.1为其原理框图。

图 错误!文档中没有指定样式的文字。

.1 DDS 原理框图DDS 的工作为相位累加器在外部时钟的控制下对频率控制字进行线性累加,累加后得到相位码,作为正弦查找表的地址,通过查找表方式得到对应的正弦波的幅度码,在经过D/A 转换得到相应的阶梯波,最后经过低通滤波器得到平滑的正弦波错误!未找到引用源。

下面将分析DDS 输出频率与频率控制字的关系。

为了简化分析过程,假设输出信号为初始相位为0,幅度为1,那么输出正弦波可以表示为:(t)cos t cos2s ft ωπ== (2.11)其中f 为信号频率,从式中可知DDS 输出信号的瞬时相位是时间的函数,其就是利用这种联系实现所需要频率。

将f 表示为:22f t ωϕππ∆==∆ (2.12)其中ϕ为采样间隔t 时间内的相位增量, 22n K πϕ⋅∆=(2.13) n 为采样位数,采样周期1/c t f ∆=,可得:22c c n f K f f ϕπ∆⋅== (2.14)所以通过频率控制字K 即可实现对输出频率的控制,频率分辨率由采样位数n 决定错误!未找到引用源。

从上面的分析可知,DDS 作为频率合成器具有频率分辨率高、频率切换时间短等显著特点,但是也存很多不可避免的缺陷,如输出频率低、输出杂散较多等。

锁相环及频率合成器的原理及电路设计方案介绍

锁相环及频率合成器的原理及电路设计方案介绍引言锁相环简称PLL,是实现相位自动控制的一门技术,早期是为了解决接收机的同步接收问题而开发的,后来应用在电视机的扫描电路中。

由于锁相技术的发展,该技术已逐渐应用到通信、导航、雷达、计算机到家用电器的各个领域。

自从20世纪70年代起,随着集成电路的发展,开始出现集成的锁相环器件、通用和专用集成单片锁相环,使锁相环逐渐变成一个低成本、使用简便的多功能器件。

如今,PLL技术主要应用在调制解调、频率合成、彩电色幅载波提取、雷达、FM立体声解码等各个领域。

随着数字技术的发展,还出现了各种数字PLL器件,它们在数字通信中的载波同步、位同步、相干解调等方面起着重要的作用。

随着现代电子技术的飞快发展,具有高稳定性和准确度的频率源已经成为科研生产的重要组成部分。

高性能的频率源可通过频率合成技术获得。

随着大规模集成电路的发展,锁相式频率合成技术占有越来越重要的地位。

由一个或几个高稳定度、高准确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环及频率合成器的原理1.1 锁相环原理PLL是一种反馈控制电路,其特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因PLL可以实现输出信号频率对输入信号频率的自动跟踪,所以PLL通常用于闭环跟踪电路。

PLL在工作的过程中,当输出信号的频率与输入信号的频率相同时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是PLL名称的由来。

PLL通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,PLL组成的原理框图如图1所示。

PLL中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控。

各种手机电路分析bkdo

当手机加电时, 电池电压通过输入电路送至电源 模块(N100)的F1、 G1、 G3、 G5、 A4、 H6、 D2等脚 , 经其内部电路转换后, 从N100的E4脚输出3 V左右 的触发电压, 使触发端保持高电平。 当按下电源开关 键(ON/OFF), 给电源模块(N100)的触发端输入一低 电平触发信号时, 电源模块(N100)开始工作, 并分别 从下列各脚输出相应的电压给手机各电路供电:

(8) 从N100的D4脚输出VREF(1.5 V)电压, 给射频 处理模块(N505)、 多模转换器(N250)等供电。

(9) 从N100的B4脚输出VCORE(2.0 V)电压, 给中 央处理器(D200)等供电。

(10) 从N100的H7脚输出VCP(5.0 V)电压, 给稳压 模块(N600)等供电。

图3-15 摩托罗拉V60型手机接收一本振电路原理图

发射TXVCO U350的第3脚VT为内部压控振荡器的 控制脚, 该脚电压越高, 第6脚产生的TX_OUT的频 率也相应越高, 反之越低。 当由于温度或其它原因导 致TX_OUT变化时, V60通过R353把该改变反应给 U201内部。 首先经过分频, 然后与已经经过基校准的 基准频率26 MHz进行鉴相, 把鉴相后误差的结果由 U201的B1脚输出来(即CP_TX), 再对TXVC第3脚进行 调整, 进而调整了TXVCO U350的输出射频信号, 使 之符合基站的要求。 其电路原理如图3-16所示。

3.1 诺基亚8210/8850型手机电路分析

诺基亚8210/8850型手机是由芬兰诺基亚公司推出 的两款双频手机, 这两款双频手机电路结构基本一样 , 而外观变化较大, 其外形如图3-1、 3-2所示。 这两 款双频手机的特点是采用了内置天线和电池, 逻辑部 分多处采用软封装IC。

模拟电子技术基础 7.4频率合成器PPT课件

7.4 频率合成器

为实现高质量的无线通信,抗干扰,近代通信系统往往要求通信机具有大量的、可供用户选择的、能迅速更换的频率稳定度和精度很高的载波信号频率。

晶体振荡器虽然频率稳定度和精度很高,但其频率值只能在很小范围内微调。

频率合成器作用:利用一个或多个基准频率,产生一系列等间隔的离散频率。这些频率的频率稳定度和精度均和基准频率的相同,且频率转换的时间很短。

三、改进思路

2. 由于固定分频器速度远比程序分频器的高,故采用由固 定分频器与程序分频器组成的吞脉冲可变分频器,可既 获得小的频率间隔,又显著提高输出频率。

采用多环式锁相频率合成器

构成吞脉冲锁相频率合成器

四、多环式锁相频率合成器

单环

单环

混 频 环 C

由设备内部各种不规则的电扰动所产生

7.4.2 锁相频率合成器

一、简单锁相频率合成器

晶体振荡器

参考分频器 ÷R

PD

LF

VCO

分频器 ÷N

fs

fs/R

fr

fo

fo/N

环路锁定时

fr = fs / R = fo / N

故得

fo = N fs/ R = N fr

改变N可得不同输出频率。

频率分辨率为fr 。

五、吞脉冲锁相频率合成器

1. 吞脉冲可变分频器

在一个计数周期内,总脉冲计数量为

N=(P+1)A + P (N-A) = PN+A

吞脉冲可变分频器的分频比为 f0’/ f0 =1/(PN+A) N、A均为整数0、1、2……

2. 吞脉冲锁相频率合成器的组成与工作原理

吞脉冲可变分频器

fA = (NA/100)fr

锁相式数字频率合成器的设计实验报告解析甄选范文

锁相式数字频率合成器的设计实验报告解析实验四锁相式数字频率合成器的设计一. 实验目的1. 掌握锁相环及频率合成器原理。

2. 利用数字锁相环CD4046设计制作频率合成器。

3. 利用有源滤波器将CD4046输出方波。

二. 实验仪器1. DSO-2902示波器/逻辑分析仪一台 2. 模拟信号源一台 3. 锁相环电路板一个 4. 微机一台5. 微机专用直流电源一台 三. 实验原理1.锁相频率合成器原理锁相频率合成器是基于锁相环路的同步原理,由一个高准度、高稳定度的参考晶体振荡器,合成出许多离散频率。

即将某一基准频率经过锁相环(PLL )的作用,产生需要的频率。

原理框图如图4-1所示。

图4-1 锁相环原理框图由图4-1可知,晶体振荡器的频率i f 经M 固定分频后得到步进参考频率REF f ,将REF f 信号作为鉴相器的基准与N 分频器的输出进行比较,鉴相器的输出d U 正比与两路输入信号是相位差,d U 经环路滤波器得到一个平均电压c U ,c U 控制压控振荡器(VCO )频率0f 的变化,使鉴相器的两路输入信号相位差不断减小,直到鉴相器的输出为零或为某一直流电平,这时称为锁定。

锁定后的频率为0//i REF f M f N f ==即()0/i REF f N M f N f ==⋅。

当预置分频数N 变化时,输出信号频率0f 随着发生变化。

锁相环中的滤波器时间常数决定了跟随输入信号的速度,同时也限制了锁相环的捕捉范围,详细原理见参考书。

2.CD4046锁相环工作原理数字锁相环CD4046由两个鉴相器、一个压控振荡器、一个源极跟随器和一个齐纳二极管组成。

鉴相器有两个共用输入端INPCA和INPCB,输入端INPCA既可以与大信号直接匹配,又可直接与小信号相接。

自偏置电路可在放大器的线性区调整小信号电压增益。

鉴相器Ⅰ为异或门,鉴相器Ⅱ为四组边沿触发器。

由于CD4046的两个鉴相器输入信号均为数字信号,所以称CD4046位数字锁相环。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

手机频率合成器电路分析手机通常使用的为带锁相环的频率合成器。

每个频率合成环路都包括5个基本的功能电路:基准时钟振荡器、鉴相器、低通滤波器、压控振荡器和分频器。

如图4-22所示。

设基准振荡信号为f1,设VCO输出信号为f2。

分频器输出的信号为f2/N。

整个环路的控制目的就是要使f1=f2/N1.图4-24是诺基 3310手机的26MHzVCO电路。

另一种是由一个13MHz(26MHz、19.5MHz)石英晶体、集成电路和外接元件构成晶振振荡电路。

图4-25是爱立信T28手机的13MHz晶振振荡电路。

由N234和13MHz晶体B320、变容二极管V322、V321等构成,该电路产生13MHz的信号,经N234模块处理后输出两路:一路经电容C300、C302到D300模块的15脚,给频率合成电路提供参考信号;另一路从N234的52脚输出,给逻辑电路提供逻辑时钟信号;13MHz电路的控制信号VCXOCONT来自N800模块。

图4-26是摩托罗拉V998手机的26MHz振荡电路。

由26MHz石英晶体Y230、变容二极管CR230及中频模块U913内部的振荡电路所组成。

电路中,Y230是4脚晶体,其中三只脚是连在一起作为接地端,而另外一脚则作为输出,自动频率控制电压AFC从U913的J7端输出,U913的J8脚为供电端,U913振荡器产生13MHz基准频率一路作为基准频率信号源去合成各种载频,另外一路则从U913的J6端输出送到中央处理器,作为手机的逻辑时钟。

图4-27是三星A188手机19.5MHz振荡电路。

由U101和石英晶体Y101等元件组成,石英晶体Y101的谐振频率(基准频率)为19.5MHz,在U101模块内进行1.5倍分频处理,得到频率合成的参考信号和逻辑电路的13MHz时钟信号。

频率合成的参考信号从U101的C10脚输出;逻辑时钟信号从U101的H7脚输出。

U101的D10脚为供电端。

不管是VCO组件还是晶振组成的振荡电路,都需要AFC控制信号,AFC信号由逻辑电路中的DSP(数字语音处理器)输出。

由于GSM手机采用时分多址(TDMA)技术,以不同的时间段(时隙)采区分用户,手机与系统保持时间同步就显得非常重要。

如手机时钟与系统时钟不同步,则会导致手机不能与系统进行正常的通信。

在GSM系统中,公共广播控制信道(BCCH)包含频率校正信息与同步信息等。

手机一开机,就会在逻辑电路的控制下扫描这个信道,从中获取同步与频率校正信息。

如手机系统检测到手机的时钟与系统不同步,手机逻辑电路就会输出AFC信号。

AFC信号改变13MHz电路中VCO 两端的反偏压,使该VCO电路输出频率发生变化。

从而保证手机与系统同步。

常见手机所采用的基准时钟电路对比见下表。

2.鉴相器3.低通滤波器简称LPF(LowPassFilter)。

低通滤波器在频率合成环路中又被称为环路滤波器。

它是一个RC电路。

位于鉴相器与VCO电路之间,低通滤波器电路基本形式如图4-28所示。

低通滤波器通过对电阻电容进行适当的参数设置,使高频成分被滤除。

由于鉴相器PD输出的不但包含直流控制信号,还有一些高频谐波成分。

这些谐波会影响VCO电路的工作。

低通滤波器就是要把这些高频成分滤除,以防止对VCO电路造成干扰。

4.5.1.VCO当VCO处于正常工作状态时,VCO输出一个固定的频率。

若某种外界因素如电压、温度导致VCO频率升高,则分频输出的信号为f2/N比基准信号n高,鉴相器检测到这个变化后,其输出电压减小,使变容二极管两端的反偏压减小。

这使得变容二极管的结电容增大,振荡回路改变,VCO输出频率降低。

若外界因素导致VCO频率下降,整个控制环路则执行相反的过程。

2.VCO三、手机常用频率合成器电路1.对于带发射VCO电路的手机,一本振VCO频率合成器产生一本振信号,一方面送到接收一混频电路,和接收信号进行混频,从混频器输出一中频信号。

另一方面,产生一本振信号与发射VCO(TXVCO)输出的信号进行混频,输出发射中频参考信号,发射中频参考信号和发射己调中频信号在发射变换模块鉴相器中进行比较,输出包含发送数据的脉动直流信号,再去控制发射VCO电路。

对于带发射上变频电路的手机(较少,如诺基亚6110手机),一本振VCO频率合成器产生一本振信号,一方面送到接收一混频电路,和接收信号进行混频,从混频器输出一中频信号。

另一方面,产生的一本振信号直接与发射已调中频信号进行混频(因为没有发射VCO电路),得到最终的发射信号。

下面以松下GD90手机的一本振VCO频率合成电路为例进行说明,有关电路图见图4-29所示。

松下GD90手机的接收第一混频和发射的变换电路都要使用到RXVCO信号,而RXVCO电路由U302模块提供。

U302模块可工作在GSM模式或DCS模式下,频段切换控制信号DCS-GSM通过Q301电路使U302工作在相应的模式下。

U302的1脚是信号输出端;3脚是频段切换控制端;5脚是控制端;7脚是电源端。

当U302工作于GSM频段时,从1脚产生1160~1185MHz 的一本振信号。

当U302工作于DCS频段时,从重脚产生1580--1665MHz的一本振信号。

U302的输出分为两路:一路到U101的39脚作为输出信号;另一路到锁相环U301的13脚作取样信号。

该信号在U301内被分频,并与基准时钟信号进行比较,得到电压控制信号从U301的9脚输出,信号经电阻R302、R303和R304及电容C311等构成的低通滤波器电路到U302的5脚,通过改变U302内变容二极管两端的反偏压,从而控制U302的输出频率。

当逻辑电路通过SYNEN、SYNDATA、SYNCLK三条线改变U301中分频器的分频比时,U301的9脚的电压随之改变,U302的输出频率也随之改变,达到信道转换的目的。

2.对于超外差二次变频电路的接收电路:二本振VCO频率合成器的主要作用是产生二本振信号,送到接收二混频电路,与接收二混频电路输入的一中频信号进行混频,产生二中频信号。

对于超外差一次变频电路的接收电路:二本振VCO频率合成器的主要作用是产生二本振信号,送到接收解调电路,以解调出RXI/Q信号。

下面以松下GD90手机的二本振电路为例进行说明,有关电路图见图4-30所示。

二本振VCO电路(1FVCO)由VCO组件U303模块提供,U303的1脚是信号输出端,5脚是控制端,脚是电源端。

U303电路将产生540MHz的二本振信号。

U303输出的信号分为两路:一路到U101的36脚作为输出信号;另一路到U301的4脚作取样信号。

U101的8脚输出中频VCO的控制信号。

3.发射中频VCO频率合成器主要是产生发射中频载波信号。

手机在设计时,为了简化电路,发射中频频率合成器常和二本振VCO频率合成器合在一起,这样,二本振VCO频率合成器和发射中频VCO频率合成器就合成了一个电路。

另外,需要说明的是:发射VCO(TXVCO)电路从原理上分析也是一个频率合成器,前面已有分析,这里不再多述。

发射中频VCO频率合成器二本振VCO频率合成器一本振VCO 频率合成器在手机电路中,通常包含几个频率合成环路:一本振VCO频率合成环路(UHFVCO、RFVCO、RXVCO)、二本振VCO频率合成环路(1FVCO、VHFVCO等)、发射中频VCO频率合成环路等。

不管是哪一个频率合成环路,其电路结构都基本一样,且它们的参考信号都来自基准频率时钟电路。

上面是说明的是怎样使VCO输出的频率稳定。

那怎样使VCO的频率能改变呢?在说明这个问题前,先解释一下为什么VCO的频率要改变这个问题。

因为手机是移动的,移动到了另一个地方,为手机服务的小区(CELL)就变成了另一对频率,所以手机就必须改变自己的接收和发射频率。

VCO改变频率过程如下:手机在收到新小区的改变频率的信令以后,将信令解调、解码,手机的CPU就通过三条线(即CPU的SYNDA T、SYNCLK、SYNSTR脚)对锁相环电路发出改变频率的指令,去改变程控分频器的分频比,并且在极短的时间内完成。

在这三条线的控制下,锁相环输出的电压就改变了,用这个己变大或变小了的电压去控制压控振荡器内的变容二极管,则VCO输出的频率就改变到新小区使用的频率上了。

频率的变频过程频率的稳定过程二、频率合成器的基本工作过程鉴相器是将VCO输出信号与基准信号进行比较。

在频率合成中,为了提高控制精度,鉴相器在低频下工作。

而VCO输出频率是比较高的,为了提高整个环路的控制精度,就离不开分频技术。

手机中的频率合成环路多,不同的频率合成环路使用的分频器不同:接收机的第一本机振荡(RXVCO、UHFVCO、RFVCO)信号是随信道的变化而变化的,该频率合成环路中的分频器是一个程控分频器,其分频比受控于频率合成数据信号(SYNDA T\SYNCLK、SYNSTR)。

二本振VCO,也称中频VCO(1FVCO、VHFVCO),信号是固定的,中频VCO频率合成环路中的分频器的分频比也是固定的。

分频器输出的信号送到鉴相器,和基准时钟信号进行相位比较。

分频器压控振荡器简称VCO(V oltageControlOscillator)。

压控振荡器是一个“电压—频率”转换装置。

它将鉴相器PD输出的相差电压信号的变化转化成频率的变化。

顾名思义,VCO电路是一个电压控制电路。

电压控制功能的完成是通过一个特殊的器件来完成的,这个器件就是变容二极管。

鉴相器输出的相差电压实际上是加在变容二极管两端的。

当鉴相器输出发生变化时,变容二极管两端的反偏发生变化,导致变容二极管的结电容改变,VCO振荡回路改变,VCO输出频率也随之改变。

在实际应用中,变容二极管为反向偏置使用,其线性好,可控范围大。

在手机电路中,VCO从电路形式上来说,有分离元件电路与VCO组件。

但VCO组件采用的电路也基本与分立元件的VCO电路相似。

相比较采说,摩托罗拉手机常使用分立元件的VCO电路,而其它手机则较多地采用了VCO组件。

无论是分立元件还是VCO组件,一般都是一个电容三点式振荡电路。

VCO在锁相环中比较重要,是频率合成及锁相环路的核心电路。

它应满足这样一些特性:输出幅度稳定性要好,在整个VCO工作频带内均应满足此要求,否则会影响鉴相灵敏度;频率覆盖范围要满足要求且有余量;电压一频率变换特性的线性范围要宽。

压控振荡器低通滤波器鉴相器简称PD、PH或PHD(PhaseDetector)。

是一个相位比较器,它将VCO振荡信号的相位变化变换为电压的变化,鉴相器输出的是一个脉动直流信号,这个脉动直流信号经低通滤波器(LPF)滤除高频成分后去控制VCO电路。

鉴相器是相位比较器,它对基准信号输入与VCO产生的信号输入进行相位比较,输出反映两信号相位误差的误差电压。