最新dsp原理与应用-第四章时钟,中断,看门狗

第四章 F2833x系统时钟及中断控制-TMS320F28335 DSP原理、开发及应用-符晓

看门狗计数器独立于CPU而运行 看门狗计数器溢出时,产生复位或者中断

CPU正常运行时看门狗计数器被定时复位,即“喂狗” 150MHz的时钟频率相当于6.67ns,看门狗计数器是16

位的,从0开始计数到计满溢出是65536个数,即 6.67ns*65536=4.396ms

第四章 系统时钟及中断控制

4.1 F2833x OSC与PLL (对应: SysCtrl.c)

3.3V时钟脉冲输入

外部晶振

片上振 荡器

PLL工作模式 XRS

表4-1 PLL工作模式

工作模式介绍

PLLSTS[DIVSEL]

PLL关闭

通过将PLLSTS寄存器中的PLLOFF位置1可将PLL模块关闭,从而减少

2-0

HSPCLK

ADC

2-0

LSPCLK

SCI / SPI / I2C / McBSP

4.2 外设时钟信号的寄存器

SysCtrlRegs.PCLKCR0

15

14

13

ECANB ECANA MA ENCLK ENCLK ENCLK

7

6

5

reserved reserved

SCIC ENCLK

12

MB ENCLK

0,1

系统噪声并减少功率损耗。在进入此模式前应首先将PLLCR寄存器设为

0x0000。

2

3

PLL旁路

上电复位或 复位后,PLL进入该模式。在该模式下时钟信号直接绕过

0,1

PLL模块,但PLL模块却未关闭。

2

3

PLL使能

向PLLCR寄存器中写入非零的数可使能PLL模块,一旦写入数据后,PLL

DSP完整课件第4章

4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 系统配置寄存器 中断优先级和中断向量表 外设中断扩展控制器 中断响应的过程 中断响应的等待时间 CPU的中断寄存器 复位和无效地址检测 外部中断控制寄存器

作业:11) 240x中断系统结构特点 12)中断响应过程 13)主中断服务程序与外设中断服务子程序的任务

2010退出Βιβλιοθήκη 4.2 中断优先级和中断向量表

CPU级中断向量表及优先级

K值 0 1 2 3 4 5 6 7 8 9 16 17 18 19 ... 31

2010

CPU中断向量 0000h 0002h 0004h 0006h 0008h 000Ah 000Ch 000Eh 0010h ... 0020h 0022h 0024h 0026h ... 003Eh

2010

退出

中断系统

240x的2级(层次)中断结构。

(1) CPU内核级(顶层)中断(INT1~INT6)

(2) 外设级(底层)中断 利用6个内核级中断扩展38个外设级中断。

(2) 外设级(底层)中断 每级可屏蔽的CPU级中断(INT1~6)又对应多个外设级中 断源,每个外设级中断源具有唯一的中断入口地址向量,它 们构成了外设级中断向量表。 • 外设中断向量表 用来获取响应外设中断服务子程序。一般存放跳转到外 设中断服务子程序的跳转指令。 • 外设中断服务子程序 完成具体中断要实现的功能。

优先级 1 4 5 6 7 8 9

中断名称 RS INT1 INT2 INT3 INT4 INT5 INT6

INT8

INT16 TRAP NMI ... INT31

3 2

说明 硬件上电复位中断(不可屏蔽) 1号可屏蔽中断 2号可屏蔽中断 3号可屏蔽中断 4号可屏蔽中断 5号可屏蔽中断 6号可屏蔽中断 保留 用户自定义软件中断 .... 用户自定义软件中断 陷阱软件中断 NMI软件中断 保留 ... 用户自定义软件中断

DSP 原理及应用精品课件第4章第2节

4.8 CPU定时器中断应用举例

▪ 配置CPU定时器,启动定时器。 ▪ 开中断,程序进入死循环中等待中断。 ▪ 每次进入中断子程序中使

CpuTimer2.InterruptCount加1。

例4.7

▪ #include "DSP28_Device.h"

▪ void main(void)

▪{

▪

InitSysCtrl();

10

4.7 CPU定时器寄存器

CPU定时器预定标寄存器TIMERxTPR CPU定时器预定标寄存器高位TIMERxTPRH

11

位 15~8

7~0

名称 PSC

TDDR

描述

CPU定时器预定标计数器。

这些位保持了定时器的当前预定标计数值。当PSCH:PSC的值大于0时, 对每一次定时器时钟源周期PSCH:PSC减1。PSCH:PSC减到0以后的 下一个定时器时钟(定时器预定标器的输出)周期,TDDRH:TDDR的 值装入PSCH:PSC中,且定时器计数器寄存器 (TIMH:TIM)减1。 当定时器重新装载位TRB用软件置1时,可以重新装载PSCH:PSC值。 通 过 读 寄 存 器 可 以 检 查 PSCH : PSC 中 的 值 , 但 不 能 直 接 设 置 PSCH : PSC中的值,PSCH:PSC中的值只能从定时器分频寄存器(TDDRH: TDDR)中得到。复位时,PSCH:PSC被设置为0。

//初始化系统控制寄存器、PLL、看门狗、时钟位默认配置

▪

DINT;

//禁止全局中断

▪

IER = 0x0000; //禁止CPU中断

▪

IFR = 0X0000; //清除所有中断标志

▪

InitPieCtrl(); //初始化PIE控制寄存器为默认状态(PIE中断被禁止并且标志被清除)

DSP原理及应用第四章

9

常用的汇编命令:

汇编命令 .title .end 作 用 .title "example.asm" 放在汇编语言源程序的最后 .text段是源程序正文。经汇编后,紧随.text后的是可执 行程序代码 有两种数据形式:.int和.word Table: .word 1,2,3,4 .word 8,6,4,2 表示在程序存储器标号为table开始的8个单元中存放初 始化数据1、2、3、4、8、6、4和2 .bss x,4表示在数据存储器中空出4个存储单元存放变 量x1,x2,x3和x4 .sect " vectors "定义向量表,紧随其后的是复位向量 和中断向量,名为vectors STACK .usect "STACK",10H在数据存储器中留出16 个单元作为堆栈区,名为STACK .def 举 例 紧跟其后的是用双引号括起的源程序名 结束汇编命令,汇编程序将忽略此后的任何源 语句,所以它应是程序的最后语句 紧跟其后的是汇编语言程序正文

分段的优点:在目标文件中将放置程 序、数据、变量的代码分开,便于在链 接时作为一个单独的部分分配存储器。 由于大多数系统都有好几种形式的存储 器,通过对各个段重新定位,可以使目 目标文件中的段与目标存 标存储器得到更为有效的利用。 储器之间的关系

17

2.外部符号的概念

外部符号 在一个模块中定义,可在另 一个模块中引用的符号。

25

段命令应用举例

汇编语言源程序: .data coeff .word 044h,055h,066h .bss buffer,8 prt .word 0456h .text add: LD 0Dh,A aloop:SUB #1,A BC aloop,AGEQ .data ivals .word 0CCh,0DDh,0EEh

dsp看门狗定时器的作用解析

dsp 看门狗定时器的作用解析

一、DSP 看门狗定时器介绍

看门狗在外围监控DSP 中软件的运行以及硬件的操作,当CPU 出现故障时,看门狗将执行系统复位。

如果软件进入了一个不正确的循环或者CPU 出现暂时的混乱,看门狗定时器将出现溢出来使系统复位。

在大多数情况下,DSP 短暂的混乱以及CPU 不正确的操作都可以被看门狗所清除并重新进行设置。

由于看门狗稳定的性能,其增加了CPU 的可靠性,以确保系统的完整。

在看门狗中这个外围设备中,所有的寄存器都是8 位的,连接到16 位CPU 的低8 位外围数据总线上。

240XA 看门狗定时器和C240 看门狗定时器唯一的区别就是其缺乏实时的中断能力。

看门狗定时器将通过对从CPU 出来的CLKOUT 进行分频而得到自己所需的时钟

二、看门狗定时器工作原理

使用时,WDT 将递增,直到溢出,或称超时。

除非处于休眠或空闲模式,WDT 超时会强制器件复位。

为避免WDT 超时复位,用户必须定期用。

DSP原理与应第四章.ppt

1.HPI与主机的连接

HCNTL0、

主机控制信号,与主机地址线

HCN或TL控1:制线连接,用来选择主机所要寻址的寄

存器。

HCNTL0 HCNTL1

功能说明

0

0

主机可以读/写HPIC寄存器。

主机可以读/写HPID寄存器。

0

1

每读1次,HPIA事后增1;

每写1次,HPIA事先增1。

1

0

主机可以读/写HPIA寄存器。 这个寄存器指向HPI存储器。

可以访问HPI RAM,而’C54x则配置为最小功耗

。 2021年2月25日

DSP原理及应用

4

第4章 TMS320C54x的片内外设、接口及应用

4.1 ’C54x的主机接口

HPI口可以支持主设备与’C54x之间的高速 数据传送。

在SAM工作方式时,若HPI每5个CLKOUT周 期传送一个字节,则主机的运行频率可达(fd×n)/5 。 f在d—H—OM’方C5式4x时的,C主LK机O可UT以频获率得;更高的速度。 即每5n—0n—s寻主址机一每个进字行节一(次即外16部0寻M址bp的s)周,期且数与,通 常 ’nC是543x(的或时4)钟。速度无关。

1.HPI与主机的连接

HPI与主机连接的信号名称和功能:

HD0~HD 双向并行三态数据总线,与主机数据总

7:

线相连。

当不传送数据(HDSx或HCS=1)或EMU1/OFF=0(切 断所有输出)时,HD7~HD0均处于高阻状态。

HCS: 片选信号,与主机地址线或控制线相连。

作为HPI的使能输入端,在每次寻址期间必须 为低电平,而两次寻址之间也可以停留在低电平。

第4章 TMS320C54x片内外设、接口及应用

第4章TMS320x28xx系列DSP综述

电气工程学院

DSP应用技术

帧同步和数据时钟的极性都是可编程的;可编程的内部

时钟和同步帧; 能同CODEC、AIC(Analog Interface Chips)等标准 串行A/D和D/A器件接口; 两个16× 16深度的发送通道FIFO; 两个16× 16深度的接收通道FIFO。

20

盐城工学院

电气工程学院

DSP应用技术

4.3.1 事件管理器(281x处理器)

在281x DSP上有EVA和EVB两个事件管理器,它们 是数字电机控制应用所使用的非常重要的外设,能够实 现机电设备控制的多种必要功能。 每个事件管理器模块包括定时器、比较器、捕捉单 元、PWM逻辑电路、正交编码脉冲电路以及中断逻辑电 路等。

4. 专门的分支跳转(Branch-look-)硬件减少了条件指令执行的 反应时间,条件存储操作更进一步提高了28xx的性能。 5. 28xx控制器具有许多独特的功能,如可在任何内存位置进 行单周期读一修改一写操作供了高性能和代码高效编程,还提

供了许多其他原始指令。

6. F28xx系列控制器在1个闪存上可以提供150 MIPS的性能。 7. F2808、F2806和F2801可以提供经济高效的基于闪存的数 字信号控制器,并且运行速度达100 MIPS。

27

盐城工学院

电气工程学院

DSP应用技术

4.3.6 CAN总线通信模块

CAN总线是一种串行通信协议,具有较强的抗干扰能力,

可以应用在电磁噪声比较大的场合。 F281x的CAN总线接口模块是增强型的CAN接口,完全支 持CAN2.0B总线规范。它有32个可配置的接收/发送邮箱, 支持消息的定时邮递功能。最高通信速率可以达到1Mbps, 可以使用该接口构建高可靠的CAN总线控制或检测网络。

DSP课件、、、看门狗

表4 看门狗复位寄存器位功能介绍

位 15~8 名 Reserved 称 保留 首先写0x55,然后再写0xAA到WDKEY会使WDCNTR (看门狗计数器)清零。写其他的任何值都会使看门狗 产生复位信号;读操作将返回WDCR寄存器的值 功能介绍

需要特别说明的是,看门狗模块可以产生复位信号和中断信号,但是 两者不能同时产生。当产生复位信号时,出现故障时,信号直接使器件复位; 当产生中断信号时,出现故障时,模块只能产生中断信号,如果中断使能, 则执行中断服务子程序。看门狗模块的中断信号和复位信号是通过寄存器 SCSR的第二位WDENIN位决定的,具体的位信息在前面已经介绍了,在本程序 中,设置该位信息为1,即屏蔽看门狗复位信号,使能看门狗中断信号,所 以在产生故障时,不会复位芯片,而是执行中断服务子程序。

组员:余洋勇、张佳杰、张萌

1.看门狗模块介绍 1.看门狗模块介绍

看门狗,又叫 watchdog timer,是一个定时器电路, 一般有一个 输入,叫喂狗,一个输出到MCU的RST端,MCU正常工作的时候,每隔一端 时间输出一个信号到喂狗端,给 WDT 清零,如果超过规定的时间不喂 狗,(一般在程序跑飞时),WDT 定时超过,就回给出一个复位信号到MCU, 是MCU复位. 防止MCU死机. 看门狗的作用就是防止程序发生死循环, 或者说程序跑飞 在实际的DSP应用系统当中,运行时极有可能发生干扰和被干扰的 现象。特别是产品化的DSP系统,可靠性是一个不容忽视的问题,严重 时系统会出现程序“跑飞”现象。为了克服这种情况,在可能的情况 下软硬件都应作相应的处理。目前,看门狗技术就是这种处理的有效 措施之一。 F2812中的看门狗模块与240x器件上的看门狗模块基本相同。当8 位看门狗递增计数器计数达到最大值时,看门狗模块输出一个脉冲信 号(512个振荡器时钟宽度)。为了阻止这种情况发生,用户可以屏 蔽计数器或者利用软件定时向看门狗复位控制寄存器写“0x55+0xAA” 序列(可以复位看门狗计数器)。

第4章 DSP片内外设(1)

D7 D7 RW_0

D6 D6 RW_0

D5 D5 RW_0

D4 D4 RW_0

D3 D3 RW_0

D2 D2 RW_0

D1 D1 RW_0

D0 D0 RW_0

_”后为复位后的值 后为复位后的值。 注:R=可读; “_”后为复位后的值。 可读; D7~D0:数据值。这些只读数据位包含8 WD复位关键字值 复位关键字值, D7~D0:数据值。这些只读数据位包含8位WD复位关键字值, 若读该寄存器, WDKEY不返回上次关键字值 而返回WDCR 不返回上次关键字值, 若读该寄存器,则WDKEY不返回上次关键字值,而返回WDCR 寄存器的内容。 寄存器的内容。 WD定时器控制寄存器 WDCR)——地址 定时器控制寄存器( 地址7029h ⑶ WD定时器控制寄存器(WDCR)——地址7029h WDCR用来存放看门狗配置的控制位 用来存放看门狗配置的控制位。 8位WDCR用来存放看门狗配置的控制位。

D7 WDFLAG RC_x D6 WDDIS RWC_0 D5 D4 D3 WDSHK2 WDCHK1 WDCHK0 RW_0 RW_0 RW_0 D2 WDPS2 RW_0 D1 WDPS1 RW_0 D0 WDPS0 RW_0

注:R=读;W=写;C=写1则清零;WC=当系统控制寄存器SCSR2 :R=读 W=写 C=写 则清零;WC=当系统控制寄存器SCSR2 当系统控制寄存器 OVERRIDE位为 时可写;“_”后为复位后的值,“x” 位为1 ;“_”后为复位后的值,“x”不 的WD OVERRIDE位为1时可写;“_”后为复位后的值,“x”不 确定值。 确定值。

D7:WDFLAG,看门狗标志位。该位指出WD定时器是否要求了 D7:WDFLAG,看门狗标志位。该位指出WD定时器是否要求了 WD 一个系统复位。该位由WD产生的复位来置1 WD产生的复位来置 一个系统复位。该位由WD产生的复位来置1,其它任何系统 复位对该位无效。 复位对该位无效。 WD定时器没有要求一个复位 0:WD定时器没有要求一个复位 WD定时器要求一个复位 1:WD定时器要求一个复位 D6:WDDIS,禁止看门狗。只有当SCSR2中的WD OVERRIDE位 SCSR2中的 D6:WDDIS,禁止看门狗。只有当SCSR2中的WD OVERRIDE位 向该位写有效。 为1时,向该位写有效。 0:使能看门狗 1:禁止看门狗 D5~D3:WDCHK2~WDCHK0,看门狗检查位。必须向这3 D5~D3:WDCHK2~WDCHK0,看门狗检查位。必须向这3位写 101,系统才能继续正常工作。否则将要求一个系统复位。 入101,系统才能继续正常工作。否则将要求一个系统复位。 读这3位总是000 000。 读这3位总是000。 D2~D0:WDPS2~WDPS0,看门狗预定标因子选择位。 D2~D0:WDPS2~WDPS0,看门狗预定标因子选择位。这3位 旋转产生用于WD计数器CLK的计数器溢出抽头( 4.1列出了 WD计数器CLK的计数器溢出抽头 旋转产生用于WD计数器CLK的计数器溢出抽头(表4.1列出了 WD溢出时间的选择)。由于WD计数器在溢出前计数257个时 溢出时间的选择)。由于WD计数器在溢出前计数257 WD溢出时间的选择)。由于WD计数器在溢出前计数257个时 所以给出的时间是溢出的最小值。 钟,所以给出的时间是溢出的最小值。因为预定标因子未被 清除而产生了附加的不精确性, 清除而产生了附加的不精确性,所以最大溢出的时间比表 列出的时间长1/256 1/256。 列出的时间长1/256。

第4讲:281x时钟和系统控制

PLL禁止,系统时钟等于XCLKIN; PLL旁路(上电时默认配置, PLLCR寄存器为零), 系统 时钟等于XCLKIN/2 PLL使能(PLLCR寄存器中有一个非零值n),系统时钟 等于XCLKIN的(n/2)倍

锁相环控制寄存器PLLCR

• ‘28x DSP片上晶振电路模块允许采用内部振荡 器或外部时钟源为CPU内核提供时钟; • 在使用片上晶振模块的内部振荡器时,应当在 X1/XCLKIN和X2两个引脚之间连上一个石英晶振 ,片上晶振模块输出与石英晶振频率相同的时钟 信号,典型的晶振频率是30MHz。 • 采用外部时钟应把时钟信号直接接到X1/XCLKIN 引脚,X2引脚则必须悬空,这时内部振荡器不工 作,片上晶振模块输出该外部时钟信号。

• ’28XDSP芯片有独立的看门狗模块,看门狗计 数器WDCNTR为8位,计数器达到最大值2^81=255 时,看门狗模块输出一个DSP系统复位 脉冲 。 • 喂狗操作:在看门狗计数器达到最大值之前向看 门狗复位密钥寄存器WDKEY先后写入0x55和 0xAA,则看门狗计数器清零,并自动开始下一 轮的递增计数; • 写入其他任何数据都会引起DSP系统复位。

高速外设时钟预定标寄存器HISPCP

控制高速外设的时钟 ,复位时默认为001; HSPCLK配置高速外设时钟相对于系统时钟SYSCLKOUT的 分频系数;

如果HSPCLK等于零,则高速外设时钟等同于SYSCLKOUT;如果 HSPCLK不等于零,则高速外设时钟为SYSCLKOUT/(HSPCLK×2):

4.3 看门狗单元

• 看门狗单元,又称为看门狗定时器WatchDog Timer( WDT),其本质是一个定时器电路; • 若使能看门狗单元,则在系统运行时,看门狗定时器自 动计数;如果不能定时清除看门狗计数器(俗称“喂狗 ”,或“踢狗”Kick Dog),那么看门狗定时器就会溢 出从而引起看门狗中断,强行系统复位。 • 看门狗单元可以防止系统程序发生死循环(俗称“程序 跑飞”),监测软件和硬件的运行状态,从而提高系统 的可靠性。

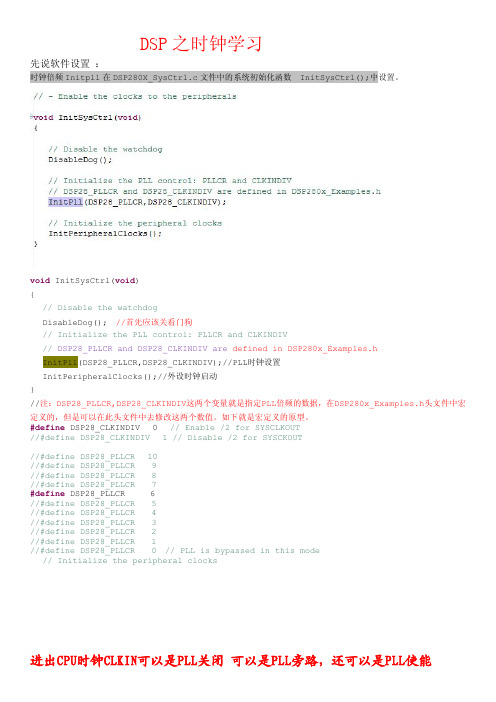

DSP时钟

DSP之时钟学习先说软件设置:时钟倍频Initpll在DSP280X_SysCtrl.c文件中的系统初始化函数InitSysCtrl();中设置。

void InitSysCtrl(void){//Disable the watchdogDisableDog();//首先应该关看门狗//Initialize the PLL control:PLLCR and CLKINDIV//DSP28_PLLCR and DSP28_CLKINDIV are defined in DSP280x_Examples.hInitPll(DSP28_PLLCR,DSP28_CLKINDIV);//PLL时钟设置InitPeripheralClocks();//外设时钟启动}//注:DSP28_PLLCR,DSP28_CLKINDIV这两个变量就是指定PLL倍频的数据,在DSP280x_Examples.h头文件中宏定义的,但是可以在此头文件中去修改这两个数值。

如下就是宏定义的原型。

#define DSP28_CLKINDIV0//Enable/2for SYSCLKOUT//#define DSP28_CLKINDIV1//Disable/2for SYSCKOUT//#define DSP28_PLLCR10//#define DSP28_PLLCR9//#define DSP28_PLLCR8//#define DSP28_PLLCR7#define DSP28_PLLCR6//#define DSP28_PLLCR5//#define DSP28_PLLCR4//#define DSP28_PLLCR3//#define DSP28_PLLCR2//#define DSP28_PLLCR1//#define DSP28_PLLCR0//PLL is bypassed in this mode//Initialize the peripheral clocks进出CPU时钟CLKIN可以是PLL关闭可以是PLL旁路,还可以是PLL使能注:·晶振操作:此模式允许使用外部为器件提供时基。

DSP第06章时钟及看门狗页码_图文(精)

// Step 5、用户特定函数,重新分配向量(可选择),使能中断: // 重新为WAKEINT 分配 PIE 向量,并指向相应的中断服务程序 EALLOW; PieVectTable.WAKEINT = &wakeint_isr; EDIS; // 使能WAKEINT 的中断INT1 IER |= M_INT1; // 使能 PieCtrlRegs.PIEIER1.bit.INTx8 = 1; // 对程序状态寄存器进行操作,避免清除WDOVERRIDE 标识位 EALLOW; SysCtrlRegs.SCSR.all = BIT1; EDIS; // 计数器清零 WakeCount = 0; // 中断计数 LoopCount = 0; // 循环计数 BP106 36// 使能全局中断,并配置为real-time debug 模式 EINT; // 使能全局中断INTM ERTM; // 使能全局 realtime 中断DBGM // Step 6、主循环 for(;; { LoopCount++; //用KickDog 操作看门狗Key 寄存器,避免产生WAKEINT 中断 // 通常情况下,需要在主循环或定时中断中对Key 进行操作 KickDog(; } } WAKEINT:位于PIE 的组1 的第8 中断 BP106 37// Step 7、中断服务程序 interrupt void wakeint_isr(void { WakeCount++; // 响应中断 PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; } //--------------------------------------------------------------------------// KickDog: 此函数复位看门狗定时器 voidKickDog(void { EALLOW; SysCtrlRegs.WDKEY = 0x0055; SysCtrlRegs.WDKEY = 0x00AA; EDIS; } BP107 38void InitSysCtrl(void // 系统初始化 { Uint16 i; EALLOW; // 禁止看门狗模块 // SysCtrlRegs.WDCR= 0x0068; // 本例中不使用 //初始化锁相环 SysCtrlRegs.PLLCR = 0xA; // 等待锁相环稳定 for(i= 0; i< 5000; i++{} // HISPCP/LOSPCP 预定标寄存器设置 SysCtrlRegs.HISPCP.all = 0x0001; SysCtrlRegs.LOSPCP.all = 0x0002; // 使能选择的外设时钟 // 对于不用的时钟,一般情况下需要禁止相应的中断SysCtrlRegs.PCLKCR.bit.EVAENCLK=1; SysCtrlRegs.PCLKCR.bit.EVBENCLK=1; SysCtrlRegs.PCLKCR.bit.SCIENCLKA=1; //SysCtrlRegs.PCLKCR.bit.SCIENCLKB=1; EDIS; BP107 } 39。

DSP28335 看门狗中断程序如何变为看门狗重启程序

//i2c

void InitI2C(void);

Uint16 I2C_xrdy();

Uint16 I2C_rrdy();

Uint16 Readbyte(Uint16 *RamAddr, Uint16 RomAddress);

Uint16 Writebyte(Uint16 Ramdata, Uint16 RomAddress);

/*

DSP28335 看门狗中断程序如何变为看门狗重启程序

编28335C程序时没有现成的看门狗重启程序, 但有许多看门狗中断程序, 中断程序运行正常, 取消主循环程序的喂狗 ServiceDog(), 可进入中断. 想改为看门狗重启程序 , 按IT 28335的说明修改, 将中断设置语句SysCtrlRegs.SCSR = BIT1;改为重启设置语句SysCtrlRegs.SCSR =0; 取消喂狗, 程序并不能重启, 将SysCtrlRegs.SCSR =0放到:

//ScicRegs.SCIHBAUD =0x0001;

/// ScicRegs.SCILBAUD =0x0086;

ScicRegs.SCICTL1.bit.SWRESET=1;

EDIS;

}

///

//xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

"

PieCtrlRegs.PIECTRL.bit.ENPIE = 1; //su3 Enable the PIE block

PieCtrlRegs.PIEIER1.bit.INTx8 = 1; //su4 Enable PIE Gropu 1 INT8

DSP原理及应用技术第4.1-4.3节 系统控制与中断

4.1 系统时钟和PLL

PLL模块的三种配置模式如表4-1所述。

PLL模式 PLL关闭 PLL旁路 PLL使能

表4-1 PLL的3种配置模式

描述

PLLSTS[DI VSEL]

通过设置PLLSTS寄存器中PLLOFF可使PLL工作在

该模式且在该模式下PLL模块被禁止。该模式可 0,1

用于减少系统噪声和低功耗操作。在进入该模

➢ 片内外设所使用的低速外设时钟LSPCLK。这个时钟信号通过对CPU时钟SYSCLKOUT 分频得到。

4.1 系统时钟和PLL

4.1.2 晶体振荡器和PLL模块

F2833x系列DSP可以 通过外置振荡器或外部时 钟信号提供时钟,并通过 内部PLL锁相环电路倍频 后提供给系统。用户可以 根据实际运行频率计算所 需的倍频系数,并通过软 件设置PLL的倍频系数。 图4-1为片上外设时钟的 产生。

➢ OSCCLK通过锁相环(PLL)模块后或直接送至CPU,这个时钟信号为CPU时钟输入, 记为CLKIN。

➢ CLKIN输入CPU后,CPU将其输出,称为CPU时钟输出或系统输出时钟,记为 SYSCLKOUT。SYSCLKOUT与CLKIN频率相同。

➢ 片内外设所使用的高速外设时钟HSPCLK。这个时钟信号通过对CPU时钟SYSCLKOUT 分频得到。

2 OSSCLK×k/2

至PLL锁定住新的频率。

4.1 系统时钟和PLL

1. XCLKOUT信号的产生 XCLKOUT信号是直接由系统时钟SYSCLKOUT产生的,如图4-3所示。XCLKOUT频率

可以配置为SYSCLKOUT/1、SYSCLKOUT/2或SYSCLKOUT/4,默认状态下,XCLKOUT = SYSCLKOUT/4 或XCLKOUT = OSCCLK/16。

最新dsp原理与应用-第四章时钟,中断,看门狗

DSP原理与应用

2020年10月15日

45

习题

1.使用TMS320LF28335中断在主程序中需进行哪 些工作,在中断处理子程序中需进行哪些工作? 请具体编写一段程序进行说明。

2.通常情况下复位和NMI中断处理程序应该进行哪 些工作?

DSP原理与应用

2020年10月15日

46

参考文献

TMS320F28335, TMS320F28334, TMS320F28332 Digital Signal Controllers (DSCs) Data Manual(SPRS439B)

3

第4.1节TMS320F2833X 时钟

内部时钟模式

外部时钟模式

DSP原理与应用

2020年10月15日

4

第4.1节TMS320F2833X 时钟

时钟模块功能图

DSP原理与应用

2020年10月15日

5

第4.1节TMS320F2833X 时钟

PLL倍率选择:PLLCR

DSP原理与应用

2020年10月15日

14个可屏蔽中断:INT1~INT14

中断向量0D02h~0D1Ch,有多组中断源,每个中断源可以在 相应地址再设定中断向量:INT1.1 SEQ1INT 0D40h

另有用户定义的软件陷阱中断(和高级软件配合)

DSP原理与应用

2020年10月15日

24

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT1

26

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT4

ECAP1~ECAP6中断

中断优先级和中断向量: INT5

EQEP1,EQEP2中断

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EPWM1~EPWM6中断

DSP原理与应用

2021年2月13日

27

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT4

ECAP1~ECAP6中断

中断优先级和中断向量: INT5

EQEP1,EQEP2中断

DSP原理与应用

2021年2月13日

28

上电(复位)后其值为:1 1 0 对应: 从Boot ROM Block 0x3FFFC0~0x3FFFFF读取中断向量表 reset中断总是从0X3FFFC0读取中断向量 复位完成后,需要由用户程序自行指定PIE中断向量表映射关

系。

DSP原理与应用

2021年2月13日

32

第4.2节TMS320F2833X 中断

第4.1节 TMS320F2833X 时钟

第4.2节TMS320F2833X 中断

第4.3节TMS320F2833X 看门狗 习题

DSP原理与应用

2021年2月13日

14

第4.2节TMS320F2833X 中断

中断: 中断产生及处理流程 中断优先级和中断向量(Interrupt Priority and

DSP原理与应用

2021年2月13日

19

第4.2节TMS320F2833X 中断

DSP原理与应用

2021年2月13日

20

第4.2节TMS320F2833X 中断

DSP原理与应用

2021年2月13日

21

第4.2节TMS320F2833X 中断

DSP原理与应用

2021年2月13日

22

DSP原理与应用

DSP原理与应用

2021年2月13日

10

第4.1节TMS320F2833X 时钟

DSP原理与应用

2021年2月13日

11

第4.1节TMS320F2833X 时钟

DSP原理与应用

2021年2月13日

12

第4.1节TMS320F2833X 时钟

DSP原理与应用

2021年2月13日

13

第四章:TMS320F2833X 系统功能和其他功能

中断优先级和中断向量: INT9

SCI中断 CAN中断

中断优先级和中断向量: INT10保留 中断优先级和中断向量: INT11保留

DSP原理与应用

2021年2月13日

30

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT12

外部引脚中断(XINT3~XINT7) 浮点运算中断(LVF,LUF)

DSP原理与应用2009-第四 章时钟,中断,看门狗

第四章:TMS320F2833X 系统功能和其他功能

第4.1节 TMS320F2833X 时钟

第4.2节TMS320F2833X 中断 第4.3节TMS320F2833X 看门狗 习题

DSP原理与应用

2021年2月13日

2

DSP原理与应用

2021年2月13日

Vectors) 外部中断扩展控制器(Peripheral Interrupt

Expansion Controller PIE) CPU中断寄存器(CPU Interrupt Registers IFR

IMR) 外设中断寄存器 外部中断

DSP原理与应用

2021年2月13日

15

第4.2节TMS320F2833X 中断

复位:

DSP原理与应用

2021年2月13日

33

第4.2节TMS320F2833X 中断

复位:从内部BOOT ROM的0X3FFFC0开始读取

Sin/cos表:1282个字,IQMath格式 倒数表:528字, IQMath格式 平方根表:274字, IQMath格式 Arctan表:452字, IQMath格式 …

2021年2月13日

23

第4.2节TMS320F2833X 中断

中断优先级和中断向量:

DSP原理与应用

2021年2月13日

24

第4.2节TMS320F2833X 中断

中断优先级和中断向量:

3个不可屏蔽中断:

中断优先级 中断名 中断向量 说明

1

Reset 0D00h 复位和WD溢出

2

EMUINT 0D22h 仿真器中断

3

NMI

0D24h 外部不可屏蔽中断

4

RTOSINT 0D1Eh 实时操作系统中断

14个可屏蔽中断:INT1~INT14

中断向量0D02h~0D1Ch,有多组中断源,每个中断源可以在 相应地址再设定中断向量:INT1.1 SEQ1INT 0D40h

另有用户定义的软件陷阱中断(和高级软件配合)

DSP原理与应用

3

DSP原理与应用

2021年2月13日

4

DSP原理与应用

2021年2月13日

5

DSP原理与应用

2021年2月13日

6

DSP原理与应用

2021年2月13日

7

DSP原理与应用

2021年2月13日

8

第4.1节TMS320F2833X 时钟 外设时钟信号

DSP原理与应用

2021年2月13日

9

第4.1节TMS320F2833X 时钟

中断优先级和中断向量: INT13

外部引脚中断(XINT13) CPU定时器1(TI RTOS)

中断优先级和中断向量: INT14

CPU定时器2(TI RTOS)

DSP原理与应用

2021年2月13日

31

第4.2节TMS320F2833X 中断

中断向量表由3个标志位决定其映射关系: VMAP-1(ST1.3),M0M1MAP-1(ST1.11),ENPIE-0(PIECTRL.0)

2021年2月13日

25

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT1

ADC有关中断 外部中断 Timer0中断 唤醒中断

DSP原理与应用

2021年2月13日

26

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT2

EPWM1~EPWM6中断

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT6

SPI中断 McBSP中断

中断优先级和中断向量: INT7

DMA中断(DINTCH1~DINTCH6)

DSP原理与应用

2021年2月13日

29

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT8

I2C中断 SCI中断

DSP原理与应用

2021年2月13日

16

第4.2节TMS320F2833X 中断

DSP原理与应用

2021年2月13日

17

第4.2节TMS320F2833X 中断

PIEIER,PIEIFR,PIECTRL,PIEACK

DSP原理与应用

33X 中断