电子科技大学功率器件和功率集成电路-(功率集成技术)

关于西安电子科技大学微电子考研方向

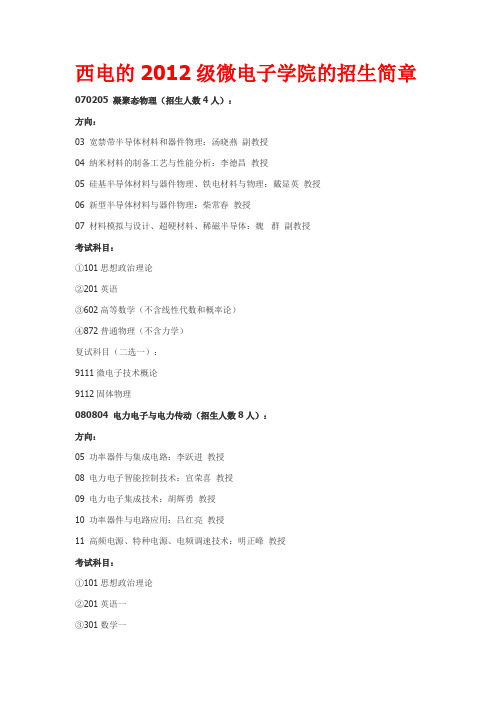

西电的2012级微电子学院的招生简章070205 凝聚态物理(招生人数4人):方向:03 宽禁带半导体材料和器件物理:汤晓燕副教授04 纳米材料的制备工艺与性能分析:李德昌教授05 硅基半导体材料与器件物理、铁电材料与物理:戴显英教授06 新型半导体材料与器件物理:柴常春教授07 材料模拟与设计、超硬材料、稀磁半导体:魏群副教授考试科目:①101思想政治理论②201英语③602高等数学(不含线性代数和概率论)④872普通物理(不含力学)复试科目(二选一):9111微电子技术概论9112固体物理080804 电力电子与电力传动(招生人数8人):方向:05 功率器件与集成电路:李跃进教授08 电力电子智能控制技术:宣荣喜教授09 电力电子集成技术:胡辉勇教授10 功率器件与电路应用:吕红亮教授11 高频电源、特种电源、电频调速技术:明正峰教授考试科目:①101思想政治理论②201英语一③301数学一④843自动控制原理(古典控制)复试科目(二选一):9111 微电子技术概论9113模拟电子技术基础080903 微电子学与固体电子学(招生人数105人):方向:01 新型半导体器件和VLSI可靠性:郝跃教授03 微电路系统芯片设计与可靠性:庄奕琪教授04 集成电路设计与VLSI技术:杨银堂教授08 半导体器件与电路计算机模拟:张玉明教授09 VLSI技术与可靠性、新型材料与器件:柴常春教授10 VLSI与高密度集成技术:李跃进教授12 新型半导体器件与集成电路技术:戴显英教授14 新型半导体器件和VLSI可靠性:刘红侠教授17 VLSI设计方法学:马佩军副教授18 VLSI系统设计和半导体集成电路工艺技术:刘毅副教授19 SOC设计方法学:王俊平教授20 VLSI设计与可制造性研究:赵天绪教授21 微波功率半导体器件:刘英坤教授22 宽禁带半导体材料和器件:张进成教授23 VLSI器件模型及仿真:吕红亮教授24 混合信号集成电路设计:朱樟明教授25 新型半导体材料、器件与集成:贾护军副教授26 宽禁带半导体物理与器件:杨林安教授28 高速半导体器件与集成电路技术:胡辉勇教授29 宽禁带新型电子器件和光电器件:冯倩副教授32 微电路可靠性:包军林副教授33 集成电路设计与新型半导体器件:高海霞副教授34 宽禁带半导体材料和器件的研究:汤晓燕副教授35 系统集成技术及集成电路设计方法学:董刚副教授36 MEMS技术:娄利飞副教授37 VLSI技术与VLSI可靠性:吴振宇副教授38 宽禁带半导体材料与器件:张金风副教授39 宽禁带半导体材料与器件:郭辉副教授40 大规模混合信号集成电路设计及高层次模型:刘帘曦副教授41 高速半导体器件与集成电路技术:舒斌副教授42 集成电路可靠性与制造过程控制、评价技术:游海龙副教授43 新型半导体材料与器件:张军琴副教授44 混合信号集成电路、可重构系统、SoC设计:赖睿副教授45 超低功耗射频混合信号集成电路设计方法学:李小明副教授46 宽禁带半导体工艺与新型器件结构:王冲副教授考试科目:①101思想政治理论②201英语一③301数学一④801 半导体物理、器件物理与集成电路(半导体物理60%,MOS器件物理20%,数字集成电路20%)复试科目(三选一):9113模拟电子技术基础9114半导体器件物理9115半导体集成电路080920 集成电路系统设计(招生人数19人):方向:01 SOC设计与设计方法学:郝跃教授02 通信与功率系统集成:庄奕琪教授03 混合信号电路与系统芯片设计:杨银堂教授04 射频集成电路设计:张玉明教授06 模拟集成电路设计:柴常春教授07 高速半导体器件与集成电路设计技术:刘红侠教授08 VLSI系统及设计研究:马佩军副教授09 VLSI设计及高速集成电路设计方法学:刘毅副教授10 集成电路设计方法与物理实现技术:史江义副教授考试科目:①101思想政治理论②201英语一②201英语一④801 半导体物理、器件物理与集成电路(半导体物理60%,MOS器件物理20%,数字集成电路20%)复试科目(三选一):9113模拟电子技术基础9114半导体器件物理9115半导体集成电路085209 集成电路工程(招生人数45人):方向:02 SOC与混合信号集成电路设计:杨银堂教授03 通信与射频集成电路设计:庄奕琪教授04 高速集成电路设计:张玉明教授05 模拟与混合集成电路设计:刘红侠教授06 模拟与混合集成电路设计:柴常春教授07 高密度系统集成技术:李跃进教授08 新型半导体器件与集成电路技术:戴显英教授09 模拟集成电路及SOC设计方法学:朱樟明教授10 电路设计与系统集成:宣荣喜教授11 毫米波与太赫兹功能电路设计:杨林安教授12 VLSI系统设计:马佩军副教授13 超大规模数字集成电路设计:刘毅副教授14 宽禁带半导体功率器件与电路设计:张进成教授15 模拟与混合集成电路设计:吕红亮教授16 VLSI设计与制造:贾护军副教授17 系统集成技术及集成电路设计方法学:董刚副教授18 高速半导体集成电路设计与制造:胡辉勇教授19 新型微波功率与光电集成电路设计:冯倩副教授21 集成电路封装设计:包军林副教授22 超大规模集成电路与功率器件设计:高海霞副教授23 VLSI设计方法学:汤晓燕副教授24 MEMS设计与制造技术:娄利飞副教授25 VLSI技术与可靠性:吴振宇副教授26 SOC设计与物理实现技术:史江义副教授28 新型半导体器件与集成电路设计:郭辉副教授29 大规模混合信号集成电路设计:刘帘曦副教授30 高速半导体集成电路设计与制造:舒斌副教授31 集成电路设计与质量可靠性保证技术:游海龙副教授32 新型半导体器件与电路设计:张军琴副教授33 大规模集成电路设计:蔡觉平教授34 混合信号IC、可重构系统、SoC设计:赖睿副教授35 功率与射频集成电路设计:李小明副教授考试科目:①101思想政治理论②201英语一③301数学一④802 集成电路与器件物理、半导体物理(数字集成电路40%,MOS器件物理40%,半导体物理20%复试科目(三选一):9111微电子技术理论9113模拟电子技术基础9115半导体集成电路085212 软件工程(招生人数80人):本领域所有考试科目均为全国统考方向:01 嵌入式系统设计:IC导师组一02 数字集成电路设计:IC导师组二03 射频与通信芯片设计:IC导师组三04 混合信号集成技术:IC导师组四考试科目:①101思想政治理论②201英语一③301数学一④408计算机学科专业基础综合(数据结构、计算机组成原理、操作系统、计算机网络) 复试科目(三选一):9111 微电子技术概论9113模拟电子技术基础9115 半导体集成电路参考书目:801 半导体物理、器件物理与集成电路:《半导体物理学》刘恩科国防工业出版社2005《半导体物理与器件》(三版)赵毅强等译电子工业出版社2005《数字集成电路—电路、系统与设计》(二版)周润德等译电子工业出版社2004 802 集成电路与器件物理、半导体物理:《半导体物理学》刘恩科国防工业出版社2005《半导体物理与器件》(三版)赵毅强等译电子工业出版社2005《数字集成电路—电路、系统与设计》(二版)周润德等译电子工业出版社2004 843 自动控制原理:《自动控制原理》吴麒等编清华大学出版社9111微电子技术概论:《微电子概论》郝跃高等教育出版社 20039112固体物理:《固体物理学》黄昆著韩汝琪编高等教育出版社 20059113模拟电子技术基础《模拟电子技术基础》孙肖子西电科大出版社20089114半导体器件物理《半导体物理与器件》赵毅强等译电子工业出版社20059115半导体集成电路《半导体集成电路》朱正涌清华大学出版社2000。

电子薄膜与集成器件国家重点实验室

电子薄膜与集成器件国家重点实验室

闫裔超

【期刊名称】《中国材料进展》

【年(卷),期】2012(031)007

【摘要】电子薄膜与集成器件国家重点实验室(UESTC)是以电子科技大学教育部新型传感器重点实验室、信息产业部电子信息材料及应用重点实验室和功率半导体技术重点实验室为基础,于2006年7月经科技部批准组建,2008年10月通过科技部验收并正式开放运行,现任实验室学术委员会主任为雷清泉院士,

【总页数】1页(P64-64)

【作者】闫裔超

【作者单位】电子科技大学

【正文语种】中文

【中图分类】TN248.4

【相关文献】

1.2012年IEEE国际功率半导体器件(电力电子器件)及功率集成电路会议综述[J], 胡冬青

2.薄膜制冷器与光电子器件的单片集成 [J], 高国龙

3.电子薄膜与集成器件国家重点实验室中山分室 [J],

4.电子薄膜与集成器件国家重点实验室中山分室 [J],

5.电子薄膜与集成器件国家重点实验室在红外隐身结构研究方面取得重要进展 [J], 周佩珩

因版权原因,仅展示原文概要,查看原文内容请购买。

功率集成电路及其应用——特邀主编评述

2 0 1 3年 l 2 月

电 力 电子 技 术

P o we r E l e c t r o n i c s

Vo 1 . 4 7,No . 1 2

De c e mb e r 2 01 3

功率集成 电路及其应用——特邀主编评述

张 波

( 电子科 技大 学 ,四川 Байду номын сангаас 都

存 储 电路 工 艺 兼 容 的领 域 。根 据 系 统 应 用 电压 的 不 同, 也可将基于 B C D 工 艺 的功 率 集 成 电路 分 为 1 0 0 V以下、 1 0 0 ~ 3 0 0 V及 3 0 0 V 以上 3类 。 1 0 0 V

电路、 半桥或全 桥逆变 器 、 两相 步进 电机 驱动器 、

半导 体公 司( F a i r c h i l d ) 、 国 际整 流 器 公 司 ( I R) 、 安

森 美半导 体公 司( O n — S e mi ) 、 美国 P I公 司 等 世 界 著 名 的半 导 体 公 司 , 已经 将 功 率 集 成 电路 产 品系 列化 、 标准化。 随着 智 能 手机 、 笔 记 本 电脑 等 便 携 式 电子 产 品需 求 的强 劲 增 长 . 以 电压 调 整 器 为代 表 的 电源 管 理 集 成 电路 得 到 迅 速 发 展 。有 人 认 为 功 率 集 成 电路 重 在 高低 压 兼 容 的 功 率 集 成 ,而 电源 管 理 集 成 电路 重 在 功 率 管 理 。故 应 独 立 于 功 率集 成 电路 的 范 围之 外 。 而 笔 者 认 为 功 率 集 成 电路 即 是 进 行 功 率 处 理 的 集 成 电路 , 电源 管 理 集 成 电路 应 置 于 功 率 集 成 电路 的 范 围之 内。

电力电子技术课后题答案

0-1. 什么是电力电子技术 ?电力电子技术是应用于电力技术领域中的电子技术;它是以利用大功率电子器件对能量进行变换和控制为主要内容的技术。

国际电气和电子工程师协会( IEEE)的电力电子学会对电力电子技术的定义为:“有效地使用电力半导体器件、应用电路和设计理论以及分析开发工具,实现对电能的高效能变换和控制的一门技术,它包括电压、电流、频率和波形等方面的变换。

”0-2. 电力电子技术的基础与核心分别是什么?电力电子器件是基础。

电能变换技术是核心.0-3. 请列举电力电子技术的 3 个主要应用领域。

电源装置 ; 电源电网净化设备 ; 电机调速系统 ; 电能传输和电力控制 ; 清洁能源开发和新蓄能系统 ; 照明及其它。

0-4. 电能变换电路有哪几种形式?其常用基本控制方式有哪三种类型AD-DC整流电 ;DC-AC逆变电路 ;AC-AC 交流变换电路 ;DC-DC直流变换电路。

常用基本控制方式主要有三类:相控方式、频控方式、斩控方式。

0-5. 从发展过程看,电力电子器件可分为哪几个阶段? 简述各阶段的主要标志。

可分为:集成电晶闸管及其应用;自关断器件及其应用;功率集成电路和智能功率器件及其应用三个发展阶段。

集成电晶闸管及其应用:大功率整流器。

自关断器件及其应用:各类节能的全控型器件问世。

功率集成电路和智能功率器件及其应用:功率集成电路( PIC),智能功率模块( IPM)器件发展。

0-6. 传统电力电子技术与现代电力电子技术各自特征是什么?传统电力电子技术的特征:电力电子器件以半控型晶闸管为主,变流电路一般为相控型,控制技术多采用模拟控制方式。

现代电力电子技术特征:电力电子器件以全控型器件为主,变流电路采用脉宽调制型,控制技术采用 PWM 数字控制技术。

0-7. 电力电子技术的发展方向是什么?新器件:器件性能优化,新型半导体材料。

高频化与高效率。

集成化与模块化。

数字化。

绿色化。

1-1. 按可控性分类,电力电子器件分哪几类?按可控性分类,电力电子器件分为不可控器件、半控器件和全控器件。

微电子研究所

北京大学微电子学系国家大力支持的重点学科点北京大学微电子学系,又称微电子学研究所(院),有着源远流长的学术传统。

1956年,由著名物理学家黄昆院士在北大物理系领导创建了我国第一个半导体专业机构,之后在我国著名微电子专家王阳元院士的带领下,北京大学微电子学系发展成为我国培养高水平微电子人才的一个重要基地,是国家的重点学科点。

【硬件环境】三大重点实验室国内领先北大微电子学系有着国内一流的科研硬件设施,有微米/纳米加工技术国家级重点实验室、北方微电子研究开发基地新工艺新器件新结构电路国家计委专项实验室、北京市软硬件协同设计高科技实验室三大重点实验室,还有MPW(多项目晶圆)中心平台。

【师资科研】科研小组特色明显北大微电子所下设SOI、SOC、ASIC、MPW中心、MEMS、新器件、可测性、宽禁带、纳太器件等多个研究小组。

所长王阳元院士是中国微电子产业的奠基人之一,目前出任中芯国际的董事长。

SOI研究组的研究领域有SOI技术、纳米量级新结构器件及制备工艺技术,以及射频电路技术。

黄如教授是北京市优秀教师,目前为IEEE EDS(Electron Device Society)和ADCOM (Administrative Committee)的成员,主要科研方向是SOI,但同时也指导学生进行射频方面的研究。

廖怀林教授专门从事RF电路方面的研究,功底深厚。

该研究组掌握了国内科研界最先进的加工技术(流片基本上采用0.13微米工艺),研究生博士生已有多篇文章发表在国际高水平刊物上。

SOC研究组在敦山教授领导下,拥有北京大学-安捷伦科技SOC测试教育中心和北京大学-安捷伦科技SOC测试工程中心两大平台。

于老师虽然是研究微处理器,但在系统方面也有很深的造诣。

重视工艺是北大微电子所的传统,所里不少老师是学物理出身的,对于器件工艺十分重视,再加上最先进的微米/纳米加工条件,因此该所的微电子器件加工工艺一直保持着国内领先水平。

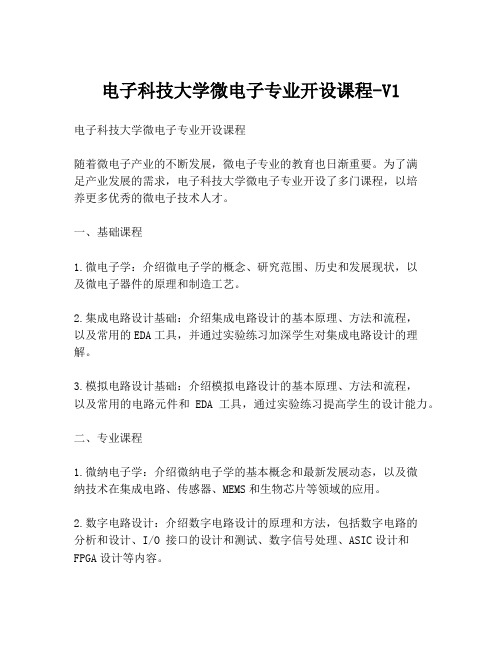

电子科技大学微电子专业开设课程-V1

电子科技大学微电子专业开设课程-V1

电子科技大学微电子专业开设课程

随着微电子产业的不断发展,微电子专业的教育也日渐重要。

为了满

足产业发展的需求,电子科技大学微电子专业开设了多门课程,以培

养更多优秀的微电子技术人才。

一、基础课程

1.微电子学:介绍微电子学的概念、研究范围、历史和发展现状,以

及微电子器件的原理和制造工艺。

2.集成电路设计基础:介绍集成电路设计的基本原理、方法和流程,

以及常用的EDA工具,并通过实验练习加深学生对集成电路设计的理解。

3.模拟电路设计基础:介绍模拟电路设计的基本原理、方法和流程,

以及常用的电路元件和EDA工具,通过实验练习提高学生的设计能力。

二、专业课程

1.微纳电子学:介绍微纳电子学的基本概念和最新发展动态,以及微

纳技术在集成电路、传感器、MEMS和生物芯片等领域的应用。

2.数字电路设计:介绍数字电路设计的原理和方法,包括数字电路的

分析和设计、I/O 接口的设计和测试、数字信号处理、ASIC设计和FPGA设计等内容。

3.模拟集成电路设计:介绍模拟集成电路设计的原理和方法,包括运放电路、数据转换电路、功率放大器、PLL和时钟等元件的设计。

4.射频集成电路设计:介绍射频集成电路设计的原理和方法,包括射频电路理论、射频芯片、高频传输线、滤波器和功率放大器等元件的设计。

以上课程涵盖了微电子专业的基础知识和专业技术,学生在学期间不仅可以加深对微电子学科的理解,还可以提高实践能力。

通过这些课程的学习,毕业生将具备较强的微电子技术应用能力和解决问题的能力,为微电子产业的发展做出重要贡献。

18、电子科技大学(罗萍)张波课题组

(一)课题组成员及导师名单(二)课题组主要研究方向与特点¾Power Devices¾(Bipolar) CMOS DMOS Process¾Power ICs功率集成技术实验室SOI High Voltage ICs:Novel integrated SOI power devices PDP Driver ICs High Voltage Gate Driver ICs High Voltage Control ICs High Voltage IC with Radiation-Hard2010-4-2911功率集成技术实验室功率集成理论-PSoC Power System on Chip2010-4-29Novel Integrated Power Devices Control Mode suited for SPIC Power Integrated Process Digital Assistant Power Design12功率集成技术实验室Power Device Control Theory BCD Process Power IC & PSoC2010-4-29 13功率集成技术实验室(三)课题组部分研究成果展示2010-4-2914Power management IC Series功率集成技术实验室Motor Driver ICs Motor Driver ICs2010-4-2915White LED Driver ICs White LED Driver ICs功率集成技术实验室2010-4-2916Power management IC Series功率集成技术实验室2010-4-2917电路理论功率集成技术实验室Pulse Skip Modulation (PSM)100Efficiency(%)90 80 70 60 50 20 40 60 Vin=2.0V Vin=1.8V Vin=1.5V Vin=1.2V 80 100I-out(mA)2010-4-2918Digitally Assisted Power Integration (DAPI) 功率集成技术实验室复杂负载SoC的低功耗设计问题数模混合SoC SIP2010-4-2919集成电路发展趋势ITRS功率集成技术实验室国 际 半 导 体 技 术 蓝 图2010-4-2920¾Realization of high voltage (> 700 V) in Device Letters¾New high-voltage (> 1200 V) MOSFET with the¾30(3):305-307, 2009 ¾¾ADI ¾NIKO(四)课题组在研的主要项目(五)课题组培养研究生的优势和竞争力(六)课题组对学生的要求。

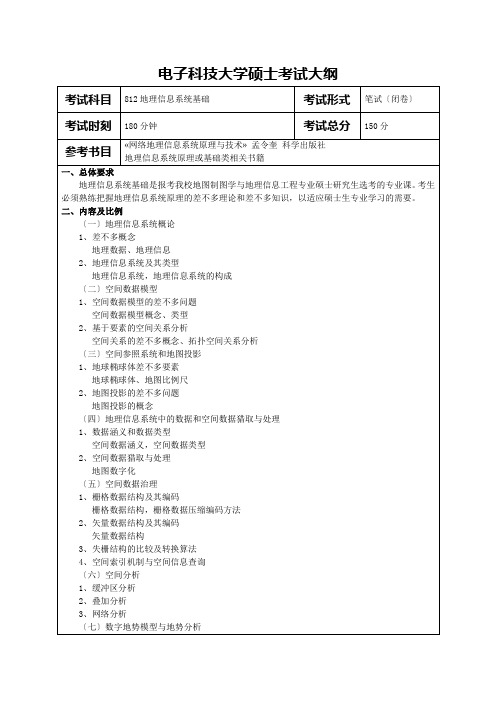

电子科技大学硕士考试大纲

电子科技大学硕士考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲

电子科技大学硕士研究生入学考试初试考试大纲。

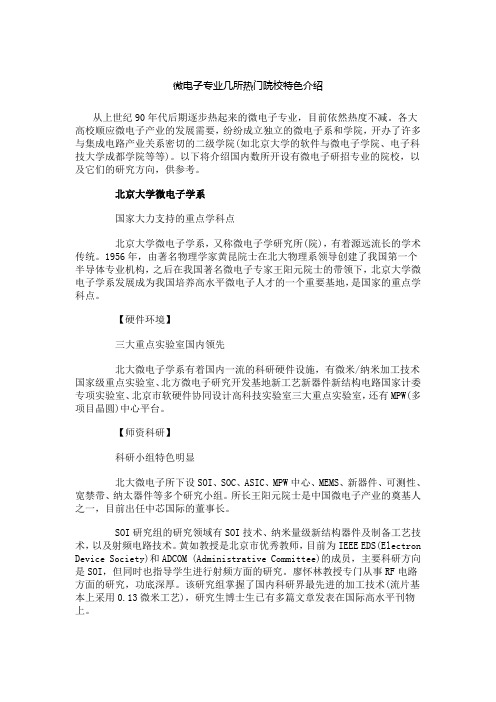

微电子专业各高校概况

微电子专业几所热门院校特色介绍从上世纪90年代后期逐步热起来的微电子专业,目前依然热度不减。

各大高校顺应微电子产业的发展需要,纷纷成立独立的微电子系和学院,开办了许多与集成电路产业关系密切的二级学院(如北京大学的软件与微电子学院、电子科技大学成都学院等等)。

以下将介绍国内数所开设有微电子研招专业的院校,以及它们的研究方向,供参考。

北京大学微电子学系国家大力支持的重点学科点北京大学微电子学系,又称微电子学研究所(院),有着源远流长的学术传统。

1956年,由著名物理学家黄昆院士在北大物理系领导创建了我国第一个半导体专业机构,之后在我国著名微电子专家王阳元院士的带领下,北京大学微电子学系发展成为我国培养高水平微电子人才的一个重要基地,是国家的重点学科点。

【硬件环境】三大重点实验室国内领先北大微电子学系有着国内一流的科研硬件设施,有微米/纳米加工技术国家级重点实验室、北方微电子研究开发基地新工艺新器件新结构电路国家计委专项实验室、北京市软硬件协同设计高科技实验室三大重点实验室,还有MPW(多项目晶圆)中心平台。

【师资科研】科研小组特色明显北大微电子所下设SOI、SOC、ASIC、MPW中心、MEMS、新器件、可测性、宽禁带、纳太器件等多个研究小组。

所长王阳元院士是中国微电子产业的奠基人之一,目前出任中芯国际的董事长。

SOI研究组的研究领域有SOI技术、纳米量级新结构器件及制备工艺技术,以及射频电路技术。

黄如教授是北京市优秀教师,目前为IEEE EDS(Electron Device Society)和ADCOM (Administrative Committee)的成员,主要科研方向是SOI,但同时也指导学生进行射频方面的研究。

廖怀林教授专门从事RF电路方面的研究,功底深厚。

该研究组掌握了国内科研界最先进的加工技术(流片基本上采用0.13微米工艺),研究生博士生已有多篇文章发表在国际高水平刊物上。

SOC研究组在敦山教授领导下,拥有北京大学-安捷伦科技SOC测试教育中心和北京大学-安捷伦科技SOC测试工程中心两大平台。

(整理)电子科技大学硕士考试大纲

熟练掌握常用数字逻辑功能单元电路(如译码器、编码器、数据选择器、比较器、加法器、计数器、移位寄存器等)的综合应用。能够根据给定的数字电路功能模块准确地设计出能完成指定任务要求的电路,同样也能够正确地分析出给定电路所能实现的数字逻辑功能。

三、题型及分值

填空题(20分)

选择题(20分)

180分钟

考试总分

150分

一、总体要求

主要考察学生掌握《电力电子技术》的基本知识,基本理论和基本技能的情况及其用分析的理论与方法分析问题和解决问题的能力。

二、内容

1.电力电子技术的基本概念

熟悉和掌握晶闸管、电力MOSFET、IGBT等电力电子器件的结构、原理、特性和使用方法。不可控器件:各种二极管;半控型器件:晶闸管;典型全控型器件:GTO、电力MOSFET、IGBT、BJT等其他电力电子器件;功率集成电路和智能功率模块;电力电子器件的串并联;电力电子器件的保护;电力电子器件的驱动电路。理解波形系数的概念,理解电力电子器件的动态特性。

6.软开关技术与组合变流

掌握软开关技术的分类与基本概念。理解基本电力电子装置的实验和调试方法。了解间接交流变流电路;交—直—交变频电路(VVVF);恒压恒频变流电路(CVCF),开关电源的基本电路。

三、题型及分值比例

选择题(30分)

填空题(50分)

简答题(25分)

推论题(15分)

计算题(30分)

考试科目

15)高频晶体管最大功率增益与最高振荡频率的定义与计算,影响功率增益的主要因素

4.绝缘栅场效应晶体管(MOSFET)

1)MOSFET的类型与基本结构

2)MOSFET的工作原理

3)MOSFET阈电压的定义、计算与测量、影响阈电压的各种因素、阈电压的衬底偏置效应

功率集成电路PIC

数字电路

隔离技术

集成兼容

CMOS-DMOS兼容工艺 Bipolar-CMOS-DMOS兼容工艺

16/22

解决兼容性问题的若干技术

解 决 兼 容 性 问 题 BCD工艺 RESURF技术 场板技术

SOI隔离技术

17/22

模拟 版图

工艺和器件定形

版图整合及验证

18/22

基于标准模型库PIC设计

为了缩短研发周期,一般将工艺和电路设计分 开。在稳定的BCD工艺基础上建立一系列各种器 件(包括功率器件)模型库、以及低压数字、控制 电路、高压功率器件等IP核,电路设计人员以此为

基础进行系统的PIC设计。

19/22

基于标准模型库PIC设计流程

6/22

功率集成电路(PIC)仅在电路性能、电路稳定性和 功耗方面有很大的优势,而且在降低成本、减小体积和减 轻重量等方面也有着巨大的潜能。 发展趋势: 近几年来,出于电子系统对体积、可靠性、性能和成 本等方面的不断要求,PIC也需要向更快速度、更多功能、 更低成本、更大功率处理和更低功耗等方面发展,特别在 兼容技术、电热效应和功率器件库模型等方面仍面临着很 多挑战。

21/22

PIC发展存在的几点困难

由于需要集成不同结构的功率器件,很多情况下 兼容性的考虑会导致不能充分发挥出功率器件的 性能; 由于采用兼容多种器件的技术,会导致工艺复杂 度或占用芯片面积的增加,从而增加产品的成本 ; 工艺复杂度和芯片面积的增加必然导致产品成品 率的降低,从而间接影响PIC的成本。

3/22

第一章 绪论

功率集成电路概念 功率集成电路发展历程 功率集成电路技术特点 功率集成电路开发流程 功率集成电路存在的挑战和机遇

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

自隔离D/CMOS集成技术

采用该集成技术可以集成高压LDMOS,低压增强和耗尽型NMOS及 PMOS, 由于采用了自隔离,输出级必须是漏极开路结构, CMOS的 工作电压为15V,输出LDMOS的击穿电压为400V,采用4um硅栅工艺, 逻辑的时钟频率为5MHz。

结隔离D/CMOS IC集成技术

功率集成电路的主要技术

高压功率器件技术 隔离技术 材料技术 工艺兼容技术

材料技术

高阻外延技术 SOI SiC GaN

高阻外延技术

N P

SOI

Si SiO2

Si

Si Si Si Si Si Si

Si

SiO2

Si

隔离岛

键合

SiO2 Si

SiO2 Si

Si SiO2

厚外延BiMOS集成技术

薄外延BiMOS集成技术

功率集成电路的主要技术

高压功率器件技术 隔离技术 材料技术 工艺技术

功率集成中的其他重要问题

高压互连线问题

Metal SiO2

Si

Metal SiO2

Si

Metal SiO2

Si

HV

Metal

SiO2 (Metal) poly silicon

隔离技术

1. SI (自隔离) 2. JI (PN结隔离) 3. DI (介质隔离)

SI (自隔离)

自隔离的HV-LDMOS与CMOS逻辑元件的集成

优点: •工艺较为简单 •集成度高 •高压M05击穿电压高 •在工艺上高压管与低压 管可以兼容。

限制: 1) 高压管必须设计成环形结构,漏区在当中,漏区完全被栅区

采用掺杂的方法使其掺杂浓度稍有提高,更有 利于提高低压器件的性能。 P+隔离和N+埋层联接扩散。

DI (介质隔离)

介质隔离结构

介质隔离的主要工艺过程

介质隔离的主要工艺过程

衬底采用N型,(100)面,其电阻率由高压器件所要求的击穿电 压决定。

在生长氧化层后,用光刻技术刻蚀出窗孔,其宽度由以下关系决 定:窗孔宽度=0.7槽深。要注意,隔离槽图形边缘应平行于 <110>晶向.

和源区所包围,这种坏形结构可以避免寄生的场反型问题, 2) 自隔离可用于集成多个输出MOS,但必须采用共源联接: 3) VDMOS不是自隔离的,故不能采用自隔离

用于自隔离的RESURF LDMOS示意图

JI (PN结隔离)

对通隔离结构

对通结隔离示意

对通结隔离中的纵向LV—PNP晶体管 加有场板的隔离

SiO2 Si

Si SiO2

Si

Si SiO2

Si

SIMOX

Si

Si

SiO2 Si

SiC

功率集成电路的主要技术

高压功率器件技术 隔离技术 材料技术 工艺兼容技术

高压CMOS技术-双深阱高压CMOS技术

双深阱高压CMOS的剖面图

这一高压CMOS技术是与低压CMOS/双极技术相兼容的. 高压PMOS的击穿电压将大于160V。; 低压CMOS的工作电压为15V。

高压CMOS技术-浅阱高压CMOS技术

•高压NMOS的击穿电压为400V •高压PMOS的击穿电压为225V •阱与衬底之间的击穿电400V。

浅阱高压CMOS剖面图 (o)高压PMOS; (b)高压NMOS

CD工艺(D/CMOS集成技术)

自隔离D/CMOS集成技术 结隔离D/CMOS IC集成技术 结隔离互补D/CMOS集成技术

半阱隔离结构

采用薄外延层, 这样隔离的厚 外延区很容易 得到,而不需 要深隔离扩散。

半阱隔离结构

半阱隔离(SWI)的主要工艺

氧化 用硅腐蚀技术形成制作高压器件的阱 N+埋层扩散 常规外延生长,外延层的掺杂浓度由高压器件

对击穿电压的要求决定。 平整表面并按需要调整外延层厚度 ‘ 制作低压器件的N阱的形成。如果需要还可以

功率器件和功率集成电路

功率集成技术

1.概述

功率集成电路 高压集成电路

线性稳压器 汽车

AC马达驱动

日光灯镇流器

开关稳压器

双极电路

数字电路

HVIC

HVIC实例

高压全桥驱动电路的版图

高

大

压

电

功

流率输来自器出件

电

路

接 口 电 路

控 制 电 路

保护电路

PIC实例

功率集成电路的主要技术

高压功率器件技术 隔离技术 材料技术 工艺兼容技术

功率集成电路的主要技术

高压功率器件技术 隔离技术 材料技术 工艺兼容技术

功率集成电路的主要技术

高压功率器件技术 隔离技术 材料技术 工艺兼容技术

隔离技术

为什么要隔离?

低压器件和电路

高压器件

低压器件和电路

高压器件

功率/高压集成电路

说明HV NPN管与LVPMOS必须隔离的示意

SiO2

Si

GND

Cross-talk与latch-up

P+

N+

N+

p

P+

N+ N

p

P+

N+

N+

p

P+

p

N+ N

热分布问题

在采用结隔离后,由于两个高压LDMOS的漏极可以处于不同的电位,因此 可以联接成图腾柱输出,并且除高压 LDMOS能与CMOS集成外,还可以 与NPN和PNP晶体管集成这给电路设计带来方便,使设计的灵活性大为 增加

结隔离互补D/CMOS集成技术

结隔离和高压LDMOS能承受120-150V电压, 低压逻辑的工作电压为5—15V

采用各向异性腐蚀液腐蚀出隔离槽。 采用外延技术或扩散技术使表面形成5~7um厚作为·埋层及埋层

联接用的N+层。 对表面进行隔离氧化,应特别注意氧化层的致密, 以降低隔离

岛之间的漏泄电流。 采用外延技术生长作为支撑的多晶硅衬底,其厚度为400um,

外延生长的工艺条件将影响到硅片的弯曲,故必须加以严格控制。 最后将背面研磨抛光形成隔离岛。

BCD(Bipolar-CMOS-DMOS)工艺

对于结隔离的情况,B工MOS集成技术可分为两大类: 制作在厚外延层上的称为厚外延B工MOS集成技术,高压

输出管一般为LDMOS或VDMOS,击穿电压不太高。 制作在薄外延层上的称为薄外延BIMOS集成技术,高压

输出管为RESURF器件,击穿电压很高。