接口与通信设备培训课程

通信技术培训教程

通信技术培训教程在当今高度信息化的社会中,通信技术的重要性不言而喻。

它不仅改变了我们的生活方式,还推动了各行各业的发展。

从简单的语音通话到高清视频会议,从短信交流到实时社交媒体互动,通信技术的不断进步为我们带来了前所未有的便捷和效率。

为了让大家更好地理解和掌握通信技术,下面为您带来一份详细的通信技术培训教程。

一、通信技术的基本概念通信,简单来说,就是信息的传递。

通信技术则是实现这种信息传递的手段和方法。

它包括了信息的采集、编码、传输、接收和解码等多个环节。

信息可以是多种多样的,比如声音、图像、文字、数据等。

而通信的目的就是要将这些信息准确、快速地从一个地方传送到另一个地方。

在通信过程中,有几个关键的概念需要了解。

首先是信号,它是信息的载体,可以是电信号、光信号等。

然后是信道,也就是信号传输的通道,比如电缆、光纤、无线电波等。

二、通信技术的发展历程通信技术的发展经历了漫长的过程。

从古代的烽火台、驿站传信,到近代的电报、电话,再到现代的移动通信、互联网通信,每一次的进步都带来了巨大的变革。

早期的通信方式速度慢、效率低,而且受到距离和环境的限制很大。

随着科技的不断发展,通信技术逐渐实现了数字化、网络化和智能化。

例如,移动通信从最初的大哥大只能进行简单的语音通话,发展到现在的智能手机能够实现高速上网、视频通话、移动支付等多种功能。

三、常见的通信技术类型1、有线通信电缆通信:通过铜质电缆传输电信号,常用于固定电话和早期的网络连接。

光纤通信:利用光在光纤中的全反射原理进行信号传输,具有高速、大容量、低损耗等优点,是现代通信骨干网络的主要传输方式。

2、无线通信无线电通信:包括短波、中波、长波等频段,广泛应用于广播、电视、航海通信等领域。

移动通信:如 2G、3G、4G、5G 等,让人们可以随时随地进行通信和获取信息。

卫星通信:通过卫星作为中继站实现远距离通信,常用于广播电视传输、导航定位、军事通信等。

3、数据通信以太网:用于计算机局域网的连接,实现数据的高速传输。

华为SDH传输设备培训课件(ppt 67张)

a. 阻抗特性:提供75o和120o阻抗; b. 保护:通道保护:保护1—32路2M

华为机密,未经许可不得扩散

文档密级:内部公开

PD1板

PD1板的功能及使用:

1、拉手条宽度为24mm 2、提供32个2M上下线路(映射和解映射) 3、2M口Bit误码检测 4、邮箱电路和485接口实现告警性能上报和板间通讯 5、接口板:D75B、D75S、D12S板 6、中继电缆:SFYV-75-2-1,插接口为HM-4*6PIN:

文档密级:内部公开

2500+各IU板位

OptiX 2500+各IU板位支持的接入容量

I U 板 位1 2 3 4 5 6 7 8 9 1 01 11 2 接 入 V C 4 的 最 大 容 量 4 4 4 1 61 61 61 61 61 6 4 4 4 ( 个 )

华为机密,未经许可不得扩散

文档密级:内部公开

IU接口单元

IU接口单元

定时单元

辅助接口单元

主控单元

外同步接口

华为机密,未经许可不得扩散

辅助接口

文档密级:内部公开

管理接口

系统信号流

交叉连接矩阵 (高阶、低阶)

STM-1

STM-4

STM-16

S D H 接 口

P D H 接 口

E1(2M) E3(34M) E4(140M) PDH子速率

同步定时

系统控制与通信

文档密级:内部公开

PQ1

?

PQ1板 的 内 容 等 同 于 PD1板 , 只 是 ......

1、提供63个2M上下线路(映射和解映射); 2、接口板:E75B、E75S、E12S板

运营商网络部新员工培训课程

语音编码

块编码器

01

激励 编码器

02

50bit

03

+3

04

2+4

05

132bit

06

78bit

07

456bit

08

信道编码

09

语音信号处理过程

语音信号处理过程

{B0,A4} {B1,A5} {B2,A6} {B3,A7} {C0,B4} {C1,B5} {C2,B6} {C3,B7}

在检测位置更新时,要使用位置区识别LAI,寻呼移动台是以LAI为单位进行

Location Area Identification

MCC

MNC

LAC

CGI

CGI是所有GSM PLMN中小区的唯一标识,是在位置区识别LAI的基础上再加上小区识别CI构成的。 编码格式为LAI+CI CI:Cell Identity, 是2个字节长的十 六进制BCD码,可由运营部门自定 例:4600017A728FD

TDMA是以不同的时隙实现通信

CDMA是以不同的代码序列来实现通信

频率复用

C

1

C

1

f

1

P

0

f

1

P

0

R

R

C/I=γ

C/I=γ

D

(D/R)2=3×k D—频率复用距离 R—小区半径 K—频率复用模式

频率复用指处在不同位置(不同小区)上的用户可以同时使用相同频率的信道。可以极大地提高频谱效率。 但如果系统设计得不好,将产生严重的干扰。(同频干扰、邻频干扰)

1

2

网络应用层信令-层3信令

Abis接口

Abis 接口定义为基站控制器(BSC)和基站收发信台(BTS)之间的通信接口.

通信线路施工培训课程(2024)

电缆选择与铺设

根据传输需求和管道条件,选择 合适的电缆类型和铺设方式,保

证电缆的传输性能和安全性。

回填与夯实

对管道和电缆进行回填和夯实, 确保管道的稳定性和电缆的安全

性。

2024/1/26

17

水下线路施工方法

2024/1/26

水下地形勘测

01

对施工区域进行水下地形勘测,了解水深、水流、河床等情况

,为施工提供准确的数据支持。

了解工程概况

准备施工材料和设备

熟悉工程规模、建设目标、施工周期 等基本信息。

根据设计文件要求,准备相应的线缆 、接头、辅助材料等,以及所需的施 工工具和设备。

组建施工队伍

根据工程需求,组建具备相应技能和 经验的施工队伍,并进行必要的培训 。

2024/1/26

12

现场勘察与选址

01

02

03

现场环境勘察

不合格品标识

对检测出的不合格品进行标识和记录,防止 误用。

原因分析

对不合格品进行原因分析,找出问题根源。

整改措施

根据原因分析,制定相应的整改措施,如更 换破损线路、重新施工等。

2024/1/26

重新验收

整改完成后,进行重新验收,确保问题得到 解决。

27

07

总结回顾与展望未来发展

2024/1/26

28

量。

2024/1/26

衰减

信号在传输过程中的能量损失 ,影响信号的传输距离和质量 。

抗干扰能力

通信线路对外部干扰的抵抗能 力,决定了信号的稳定性和可 靠性。

误码率

衡量通信线路传输质量的指标 ,表示在一定时间内传输错误

的比特数与总比特数之比。

3、接口介绍

传输接口

3)E1接口。 物理特性:采用G.703标准,该接口在中国及欧洲使 用。与接口对应的概念有: 时隙(TS):以8个bit为1个时隙的基本传输单位, 每秒传输8K次,所以每个时隙的传输速率为64Kb/S。 帧(Frame):一个帧由32个时隙(TS0-TS31)组 成,每秒传输8K次,帧可分为奇帧、偶帧,其中偶帧的 TS0用于帧同步,奇帧的TS0用于对告信息传输,每个帧 的TS0的第一个比特用于CRC校验。 复帧(MFrame):由16个帧组成一个复帧,每个帧 的TS16时隙传输控制信息及复帧同步信息,所以每秒传 输512个复帧。 非帧(No Frame):非帧结构没有帧和复帧概念。

课程提纲

一、接口的分类 二、音频接口 三、视频接口 四、控制接口 五、传输接口

控制接口

1)RS-232接口。 RS-232接口:它是一种异步串口,支持点对点全 双工方式,主要出线为RXD,TXD,GND。波特率: 300-115000b/s,一般1位起始位,8位数据位,1位停止 位。 最简单的连接方式:RXD接对方TXD,TXD接对方 RXD,GND接对方GND。 公司产品的RS-232接口通常采用RJ45头方式,引脚 定义如下:

RJ45头

传输接口

2)以太网接口(续)。 双绞网线头(RJ45)常见做法: 1 2 3 4 5 6 7 8 白橙 橙 白绿 蓝 白蓝 绿 白棕 棕 实际只采用1、2与3、6两对双绞线传输数据,直连的双 绞线网线头,两头是同样的做法,交叉的双绞线网线头, 一头同上,另一头1、3交换位置,2、6交换位置,如下 图所示: 1 2 3 4 5 6 7 8 白绿 绿 白橙 蓝 白蓝 橙 白棕 棕 对于1000M交叉的双绞线网线头,4、7及5、8也要交换 位置,如下图所示: 1 2 3 4 5 6 7 8 白绿 绿 白橙 白棕 棕 橙 蓝 白蓝

VoLTE基础技术培训

网元接口1网元接口IMS 网络拓扑MMTel-AS 补充业务:-OIP, OIR, TIP, TIR -CDIV(CFU, CFNL, CFB, CFNRc, CFNR)-呼叫禁止(ICB, OCB, ICB-R, OCB-IC)-呼叫保持,呼叫等待-MWI-多跳会议•VOLTE 网络分为终端、接入网、承载网、核心网、业务平台,其中较为复杂的是核心网,主要分为分组域(接入核心网)、策略控制单元、信令网、IMS 域、CS 域、用户域。

DNS 域名解析和ENUM (SIP URI /TEL URI / IP 的号码转换)功能三合一HSS (EPC-HSS / IMS-HSS /HLR)IBGFI-BGF 提供与其它IMS 网络互通的媒体通道资源S103S101S102Mw/I2CUPS 后增加Sx网元接口三组“网元三角关系”SBC 和PGW 之间无信令接口VoLTE 流程中PCRF 负责“传话”建专载/更新专载都在SBC触发SBC–Rx PCRF –Gx PGW PCRF 需要对Gx/Rx 做会话绑定Gx/Rx的Diameter信令走DRA 路由两台DRA 之间需要数据同步SBC 是IMS 的安全边界门卫I-CSCF 是个没记性的包打听注册找哪个代理?问I-CSCF 谁是为主叫提供服务的代理?该I-CSCF 是主叫侧网元呼叫找哪个代理?问I-CSCF 谁是为被叫提供服务的代理?该I-CSCF 是被叫侧网元P-CSCF 与SBC 合设,是IMS 入口注意顺序!删除专载-Delete Bearer Command sgw-Delete Bearer Request sgw-Delete Bearer Response sgwUE 上下文释放:EPCCommander CSCF代理的代理代理包打听PCC 门卫策略执行策略控制传话网元接口PCC网元PCC 门卫策略执行策略控制传话PCC =Policy and Charging Control 策略与计费控制主要功能:策略控制、计费控制功能、业务数据流的事件报告-PCRF (Policy and Charging Rule Function 策略和计费规则功能):负责策略控制和基于流计费控制决策的功能。

2024版华为培训学新版Datacom

华为培训学新版Datacom REPORTING2023 WORK SUMMARY目录•Datacom技术概述•网络基础知识梳理•路由交换技术深入剖析•网络安全策略部署与优化•故障排查与性能调优技巧分享•华为Datacom产品配置实践•总结回顾与未来展望PART01 Datacom技术概述Datacom定义与发展趋势Datacom定义Datacom(数据通信)是指通过计算机网络进行数据传输和通信的技术,是实现各种信息系统互联互通的基础。

发展趋势随着云计算、大数据、物联网等技术的快速发展,Datacom技术正朝着更高速度、更大容量、更低时延、更安全可靠的方向发展。

华为Datacom产品家族介绍路由器产品包括AR系列路由器、NE系列路由器等,提供丰富的接口类型和高性能转发能力,满足不同场景的组网需求。

无线产品包括Wi-Fi 6/6E无线接入点、5G CPE 等,提供高速无线接入和移动性支持,满足各种无线应用场景的需求。

交换机产品包括CloudEngine系列交换机、S系列交换机等,提供大容量、高密度的端口接入和高速转发能力,支持多种网络协议和特性。

安全产品包括防火墙、VPN网关、入侵检测/防御系统等,提供全面的网络安全防护和管理功能。

应用场景及市场需求分析应用场景Datacom技术广泛应用于政府、金融、教育、医疗、企业等各个领域,支持各种信息系统的建设和运行。

市场需求随着数字化转型的加速推进,市场对Datacom技术的需求不断增长,特别是在云计算、大数据、物联网等新兴领域的应用需求更加旺盛。

培训目标与课程设置培训目标通过华为培训学新版Datacom课程的学习,使学员全面掌握Datacom技术的基础知识和实践技能,能够独立完成网络规划、设计、实施和运维等工作。

课程设置包括Datacom基础、路由交换技术、无线技术、网络安全技术等多个模块,涵盖理论讲解、实验操作、案例分析等多种教学方式。

PART02网络基础知识梳理OSI七层模型及TCP/IP协议栈OSI七层模型01物理层、数据链路层、网络层、传输层、会话层、表示层、应用层TCP/IP协议栈02网络接口层、网络层、传输层、应用层各层功能及协议03如物理层负责传输比特流,数据链路层负责将比特流组合成帧等;TCP/IP协议栈中,IP协议位于网络层,TCP和UDP协议位于传输层等路由器交换机防火墙负载均衡器常见网络设备功能介绍01020304连接不同网络,实现路由选择和数据转发用于局域网内设备之间的数据交换保护网络安全,过滤非法访问和数据包分发网络负载,提高网络性能和可靠性局域网、广域网技术原理及应用以太网、令牌环网、FDDI等PPP、HDLC、ATM、帧中继等星型、树型、环型、网状型等企业内部网络、园区网络、城域网等局域网技术广域网技术网络拓扑结构应用场景IP地址分类子网划分与CIDRIP地址分配策略IP地址管理工具IP地址规划与管理方法A类、B类、C类、D类、E类静态分配、动态分配(DHCP)提高IP地址利用率,减少网络广播风暴IPAM(IP Address Management)系统,实现IP地址的集中管理和监控PART03路由交换技术深入剖析路由原理及静态路由配置实践路由表与路由查找流程了解路由表结构,掌握路由查找过程,理解路由优先级和度量值概念。

et200接口模块和通讯模块教程

et200接口模块和通讯模块教程ET200接口模块和通讯模块教程概述:ET200接口模块是西门子公司推出的一种用于工业自动化控制系统的接口模块,可用于与其他设备进行通信。

通讯模块是实现不同设备之间数据传输的关键设备。

本教程将重点介绍ET200接口模块的基本知识和通讯模块的使用方法。

一、ET200接口模块1.ET200接口模块的基本概念ET200接口模块是一种用于连接不同设备的接口设备,它能够根据不同的通信协议进行数据传输。

ET200接口模块通常由硬件和软件两个部分组成,硬件部分包括接口电路和物理接口,软件部分包括通信协议和通信接口。

2.ET200接口模块的功能ET200接口模块可以实现不同设备之间的数据交换和通信。

它可以将不同设备的信号转换为统一的信号格式,以便于设备之间的互联和数据传输。

ET200接口模块还可以实现设备的参数配置、状态监测和故障诊断等功能。

3.ET200接口模块的应用领域ET200接口模块广泛应用于工业自动化领域,包括工业控制系统、机器人控制系统、仪器仪表等。

它可以实现不同设备之间的数据交换和通信,提高生产效率和产品质量。

二、通讯模块的使用方法1.通讯模块的选择在选择通讯模块时,需要考虑通讯距离、通讯速率、通讯协议等因素。

通讯距离决定了通讯模块的传输能力,通讯速率决定了数据传输的效率,通讯协议决定了设备之间的通信方式。

根据实际需求选择合适的通讯模块。

2.通讯模块的配置在使用通讯模块之前,需要进行一些配置操作。

首先,需要设置通讯模块的参数,包括通讯速率、通讯协议等。

其次,需要配置通讯模块的接口,包括设置物理接口和逻辑接口等。

3.通讯模块的连接通讯模块通常需要与其他设备进行连接,以实现数据传输。

连接方式可以是串口连接、网口连接、无线连接等。

根据实际需求选择合适的连接方式,并正确连接通讯模块和其他设备。

4.通讯模块的数据传输通讯模块的主要功能是实现设备之间的数据传输。

在进行数据传输之前,需要编写相应的程序或配置文件,以实现数据的读取和写入。

接口培训资料

接口培训资料在当今数字化的时代,接口的应用越来越广泛。

无论是软件开发、系统集成,还是不同平台之间的数据交互,接口都扮演着至关重要的角色。

对于想要深入了解和掌握接口相关知识的人员来说,一份全面且易懂的培训资料是必不可少的。

一、接口的基本概念接口,简单来说,就是两个系统或者模块之间的连接部分,它规定了双方交互的数据格式、通信协议和调用方式等。

就好像两个拼图的拼接处,只有形状和尺寸匹配,才能完美地拼合在一起。

接口可以分为多种类型,比如硬件接口和软件接口。

硬件接口常见的有 USB 接口、HDMI 接口等,用于连接不同的硬件设备。

软件接口则更多地出现在程序开发中,比如 API(应用程序编程接口),它允许不同的软件组件相互通信和协作。

二、接口的重要性接口的存在有着诸多重要意义。

首先,它实现了系统的解耦。

想象一下,如果一个大系统中的各个模块之间紧密耦合,一处修改可能会引发连锁反应,导致整个系统的不稳定。

而通过接口,各个模块可以独立开发和维护,只要接口不变,内部的修改就不会影响到其他模块的正常运行。

其次,接口提高了开发效率。

开发人员不需要了解其他模块的内部实现细节,只需要按照接口的规范进行调用,就能够快速实现功能。

这就好比我们使用电器,不需要知道它内部的电路原理,只要会操作开关和按钮就行。

此外,接口还促进了系统的集成和复用。

不同的系统可以通过统一的接口进行集成,实现数据的共享和业务的协同。

同时,已经开发好的接口可以在多个项目中复用,节省开发成本和时间。

三、接口的设计原则在设计接口时,需要遵循一些重要的原则,以确保接口的可用性、稳定性和可扩展性。

1、简洁性接口应该尽量简单明了,避免复杂的参数和返回值。

过多的参数会增加调用者的负担,容易出错。

2、一致性接口的风格和规范应该保持一致,包括命名规则、参数顺序、错误处理方式等。

这样可以提高开发人员的使用体验,减少理解和使用成本。

3、稳定性接口一旦发布,就应该尽量保持稳定。

《接口与通讯》课件

HTTP协议

Web接口基于HTTP协议, 通过GET、POST等请求方 法实现数据交互。

RESTful风格

采用资源的表现层状态 转化,使接口更加简洁、 可读性强。

接口安全性

通过身份验证和授权等 方式确保接口的安全性 和数据的机密性。

RPC通讯

1

RPC原理

远程过程调用,允许在不同的系统

传输协议

2

中进行函数调用和数据传输。

《接口与通讯》PPT课件

这是关于《接口与通讯》的PPT课件,让我们一起探索接口与通讯的世界吧! 通过本课件,你将了解接口的定义、分类和作用,接口的实现方式,Web接 口和RPC通讯,消息队列,数据交换格式,以及接口与通讯在实际应用中的例 子。

什么是接口?

定义

接口是指在不同模块之 间进行通讯的连接点, 用于定义一组操作。

2

云盘应用

使用接口和通讯实现文件上传、下载和共享功能。

3

网上书店应用

接口和通讯用于处理订单、库存管理和支付功能。

总结

1 接口和通讯的重要性

它们是系统和模块之间进行信息交换和功能调用的关键。

2 接口和通讯的未来发展方向

随着技术的发展,接口和通讯将不断演进和创新。

3 接口和通讯的挑战和解决方法

安全性、可靠性和性能是接口和通讯面临的挑战,可以通过加密、冗余和负载均衡等方 式解决。

使用TCP、HTTP等协议在网络中传

输数据。

3

应用场景

分布式系统、微服务架构等需要不 同模块之间进行远程调用的场景。

消息队列

消息型

包括点对点、发布/订阅、消 息中间件等不同类型的消息 队列。

消息队列的优劣

提高系统的可靠性、可扩展 性,但需要考虑消息丢失、 延迟等问题。

2024年移动通信基础知识培训(全)

移动通信基础知识培训(全)一、引言移动通信作为现代通信技术的重要组成部分,已经深入到我们生活的方方面面。

随着移动通信技术的不断发展,对于移动通信基础知识的了解和掌握显得尤为重要。

本培训旨在帮助大家全面了解移动通信的基本原理、关键技术和发展趋势,为今后的工作提供有力支持。

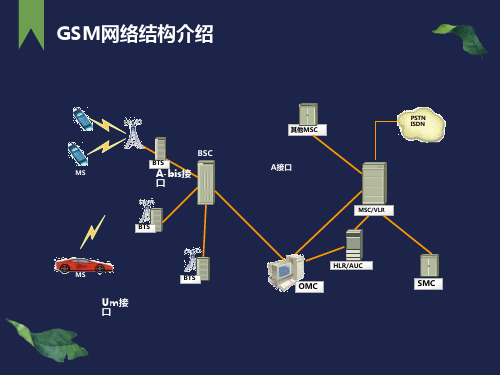

二、移动通信基本原理1.移动通信系统组成移动通信系统主要由移动台、基站、交换中心和传输系统等组成。

移动台包括方式、平板等移动设备,基站负责与移动台进行无线信号传输,交换中心负责处理呼叫控制和用户鉴权等功能,传输系统则负责将信号从一个基站传输到另一个基站或交换中心。

2.无线信号传输(1)发射:移动台将语音或数据信号转换为无线信号并发射出去。

(2)传播:无线信号在空间中传播,可能会受到多种因素的影响,如衰减、多径效应等。

(3)接收:基站接收到无线信号后,将其转换为电信号并进行处理。

(4)解调:基站将处理后的电信号还原为原始的语音或数据信号。

3.无线信号调制与解调无线信号调制是将原始信号转换为适合在无线信道中传输的信号的过程。

解调则是将接收到的信号还原为原始信号。

常见的调制方式有调幅(AM)、调频(FM)和调相(PM)等。

三、移动通信关键技术1.多址技术多址技术是移动通信系统中实现多个用户共享同一信道的关键技术。

常见多址技术有频分多址(FDMA)、时分多址(TDMA)和码分多址(CDMA)等。

2.扩频技术扩频技术是通过扩展信号带宽来降低信号功率谱密度,从而提高信号的抗干扰能力和隐蔽性。

常见的扩频技术有直接序列扩频(DSSS)和跳频扩频(FHSS)等。

3.信道编码与解码信道编码是为了提高信号在传输过程中的抗干扰能力而进行的编码处理。

解码则是将接收到的信号进行解码,恢复出原始信号。

常见的信道编码技术有卷积编码、Turbo编码等。

4.数字信号处理数字信号处理技术包括滤波、调制、解调、信道估计等,是移动通信系统中实现信号处理的关键技术。

四、移动通信发展趋势1.5G技术5G技术是当前移动通信领域的研究热点,其主要特点包括高速率、低时延、大连接等。

有线通信设备安装工程知识培训

有线通信设备安装工程知识培训1. 导言有线通信设备的安装是现代通信基础设施建设中不可或缺的一环。

为了确保通信网络的稳定运行和提高通信设备的使用效果,进行有线通信设备安装工程知识培训是非常必要的。

本文将介绍有关有线通信设备安装工程知识的相关内容,包括设备选型、安装策略、设备调试等方面的内容。

2. 设备选型在进行有线通信设备安装工程之前,首先需要进行设备选型工作。

设备选型的关键是根据实际需求和项目要求,选择合适的设备型号和规格。

选择设备时需要考虑以下因素:•带宽需求:根据网络使用情况和预测未来增长趋势,选择能够满足带宽需求的设备。

•设备可靠性:选择具有高可靠性的设备,以确保通信网络的稳定运行。

•设备兼容性:考虑设备与已有设备的兼容性,避免因设备之间的不兼容而导致安装工程的失败。

•设备价格:在满足性能需求的前提下,选择价格合理的设备,使项目的成本控制在合理范围内。

3. 安装策略安装策略是指根据具体项目的特点,制定适合的有线通信设备安装计划和流程。

安装策略的制定需要考虑以下几个因素:•安装位置:根据设备的功能和使用需求,确定最佳的安装位置,以保证设备的正常运行和维护。

•线缆布线:根据设备的连接需求,合理布置线缆,避免线缆交叉和过度拉伸,提高通信信号的传输质量。

•电源供应:确保有充足的电源供应,以满足设备的运行需求,并采取必要的保护措施来防止意外停电对设备造成的损害。

•措施与方法:根据具体项目的情况,选择合适的安装措施和方法,如使用支架、固定设备等,确保设备的安全和稳定性。

4. 设备调试设备安装完成后,需要进行设备调试工作,以确保设备的正常运行和通信效果的良好。

设备调试需要遵循以下步骤:•连接检查:检查设备的接线是否正确,确保线缆连接牢固。

•功能测试:对设备的各项功能进行测试,确保设备能够正常运行,并能够满足项目要求。

•信号质量检测:使用专业的测试仪器,检测通信信号的质量,包括信号强度、信噪比等指标,以确保通信质量达到要求。

通信培训内容

通信培训内容

通信培训的内容广泛而深入,主要包括以下几个方面:

1.通信原理:介绍通信系统的基本概念和工作原理,包括信号的传输、调制解调、信噪比等。

2.通信协议:深入了解各种通信协议,如TCP/IP协议栈、HTTP 协议等,以及如何在不同协议之间进行转换。

3.通信网络:介绍各种类型的通信网络,如固定电话网络、移动电话网络、互联网等,以及各种网络设备的连接和配置。

4.通信设备:了解各种通信设备的原理和操作,如交换机、路由器、基站等,以及如何对设备进行维护和故障排除。

5.无线通信:深入了解无线通信的原理和技术,包括无线电波的传播、无线网络的组建等。

6.卫星通信:了解卫星通信的基本原理和技术,包括卫星轨道、信号传输等。

7.网络安全:介绍如何保障通信网络的安全,包括防火墙的设置、加密技术的使用等。

8.通信系统集成:了解如何将多个通信系统进行集成,以提高通信效率和质量。

以上是通信培训的主要内容,通过培训,学员可以全面了解通信行业的基本知识和技术,提高自己在通信领域的专业水平和实践能力。

1。

通信技术培训教程

通信技术培训教程第一部分:通信技术概述通信技术是现代社会的基石,它让信息能够在全球范围内快速、准确地传递。

从电话、互联网到移动设备,通信技术不断地改变着我们的生活方式和工作方式。

因此,了解和掌握通信技术对于个人职业发展和企业运营至关重要。

通信技术包括有线通信和无线通信两大类。

有线通信主要通过电缆、光纤等物理媒介进行信号传输,如传统的电话通信和有线电视。

无线通信则利用无线电波进行信号传输,如移动通信、无线网络等。

随着科技的发展,通信技术也在不断进步。

例如,5G技术的推出,使得数据传输速度更快、延迟更低,为物联网、虚拟现实等新兴技术提供了强大的支持。

第二部分:通信技术的基本原理通信技术的基本原理涉及信息的发送、传输和接收过程。

这个过程可以分为三个主要步骤:编码、调制和解调。

编码是将信息转换成适合传输的信号形式的过程。

例如,在数字通信中,信息通常被编码为一系列的0和1,这些二进制数字可以被转换成不同的电信号或光信号。

调制是将编码后的信号转换成适合在特定媒介输的信号的过程。

例如,在无线通信中,信息被调制到高频的载波上,以便通过无线电波传输。

解调是接收端将调制后的信号转换回原始信息的过程。

这个过程通常涉及到对信号的滤波、放大和数字化。

理解这些基本原理对于掌握通信技术至关重要。

它们不仅帮助我们理解通信设备的工作原理,也为我们设计和优化通信系统提供了基础。

在下一部分,我们将探讨通信技术的关键技术,包括信号处理、编码解码、网络协议等。

这些技术是通信系统高效运行的关键,也是通信技术不断进步的动力。

第三部分:通信技术的关键设备通信技术的关键设备是确保信息能够准确、高效地传输的重要工具。

这些设备包括发射器、接收器、交换机、路由器等。

发射器是将信息转换成适合传输的信号形式并发射出去的设备。

例如,在无线通信中,发射器将信息调制到高频的载波上,并通过天线发射出去。

接收器是接收传输信号并将其转换回原始信息的设备。

接收器通常包括天线、滤波器、放大器等组件,以确保信号能够被准确地接收和转换。

5G通信技术培训资料大全

其他创新融合应用场景展望

5G+医疗健康

将5G技术应用于远程医 疗、移动医疗、健康监 测等领域,提升医疗服 务水平和健康管理能力 。

5G+教育培训

利用5G网络实现高清在 线教育、虚拟现实/增强 现实(VR/AR)教学等 功能,创新教育培训模 式并提高教育质量。

5G+文化旅游

结合5G网络提供沉浸式 文化体验、智能导览讲 解等功能,丰富文化旅 游内涵并提升游客体验 满意度。

01

独立组网(SA)

全新建设的5G网络,包括新基站、回程链路以及核心网,实现端到端

的5G服务。

02

非独立组网(NSA)

利用4G基础设施,通过升级或扩展现有网络功能来提供5G服务,实现

4G和5G的协同工作。

03

对比分析

独立组网具备更高的灵活性和可扩展性,但建设成本较高;非独立组网

则可利用现有资源快速部署5G服务,但长期来看可能面临技术升级和

关键技术:网络切片与虚拟化

网络切片技术将物理网络划分为多个逻辑网络,满足不 同业务需求

通过网络切片和虚拟化的结合,实现网络资源的灵活调 度和按需分配

虚拟化技术实现网络功能的软件化和硬件资源的池化, 提高资源利用率

降低网络建设和运营成本,促进5G网络的快速部署和 商业化应用

5G无线传输技术详

03

解

推动新能源汽车产业发展。

智慧城市领域应用案例剖析

城市管理与公共服务

利用5G网络实现城市各部门间信息共享与协同管理,提高城市治理 效率和公共服务水平。

智慧安防与应急响应

借助5G网络实现高清视频监控、智能分析预警、快速应急响应等功 能,提升城市安全防范和应急处理能力。

智慧交通与物流配送

通讯培训(S3700)-精品课件.ppt

防火墙

终

端

主干路由器

汇聚层交换机

网线

楼层接入层交换机

典型网络拓扑图结构

无汇聚层

10M接入

核心层交换机

防火墙

终

端

主干路由器

网线

楼层接入层交换机

典型网络拓扑图结构

无路由器

10M接入

核心层交换机

防火墙

终

端

网线

楼层接入层交换机

内容介绍

第一节 S27&37&57产品简要概述 第二节 S27&37&57产品命名规则 第三节 S2700交换机产品介绍 第四节 S3700交换机产品介绍 第五节 S5700交换机产品介绍

S2700-52PEI-AC

S2700-9TPSI-AC

S270018TP-SI-AC

S270026TP-SI-AC

S2700-9TPPWR-EI

S270026TP-PWREI

02352333 48个10/100BASE-T,2个百兆/千兆SFP上行口(100/1000 BASE-X),2个千兆SFP上行口(SFP Req.),交流供电

注: S3700TP 有2个千兆光电复用口,2个千兆 百兆自适应的光口(可做堆叠用) *见备注

S3700设备外观图片

S3700-28TP-SI/EI S3700-28TP-EI-24S S3700-52P-SI/EI S3700-52P-EI-24S

S3700非POE产品外观及主要特点

• S3700为L3层百兆交换机 。

业务端口高防雷规格(非POE机型):可 达6KV共模防护

电源内臵,便于设备的安装

S2700 POE产品主要特点

S2700为L2层交换机。 O 上行端口为combo端口,可以灵活选择光或电口接入。 O 下行端口可提供远供电源, 每端口最大输出功率30W(支持802.3AT 标准) O 每个业务端口指示灯均有Link/Act、POE status、Speed几种指示 模式,可 通过右侧的mode按钮 进行模式切换。 O 可热插拔风扇,方面现场维护更换。 O 风扇转速自动智能调速,节能减排。 O 双槽位电源,可形成电源备份 O 电源可插拔,方便维护 O POE电源有12V和53V两种电压输出, 12V供本设备供电,53V为 POE电源, 供远端PD使用。 O POE电源有250W(120W@12V+130W@53V)、500W ( 120W@12V+380W@53V)两种功率型号, 250W满足8端口满供功率 , 500W满足24端口满供功率

计算机接口与通信第9章 USB 通用串行总线

9.2

USB总线的体系结构 USB总线的体系结构

9.2.1 USB总线的物理接口 USB总线的物理接口 USB总线的物理传输介质由一根4线的电 USB总线的物理传输介质由一根4线的电 缆组成,如图9 所示。其中两条(VBus、 缆组成,如图9-1所示。其中两条(VBus、 GND)用于提供设备工作所需电源。VBus GND)用于提供设备工作所需电源。VBus 在源端的标称电压值为+5V,GND为其对 在源端的标称电压值为+5V,GND为其对 应地线。另两条(V+、V-)为绞线形式 应地线。另两条(V+、V 的信号传输线,90 的信号传输线,90 的阻抗。

9.2.3

USB的信号和编码 USB的信号和编码

USB数据收发器包含了发送数据所需的差 USB数据收发器包含了发送数据所需的差 模输出驱动器和接收数据用的差模输入接 收器。 USB输出信号时,差模输出驱动器向USB USB输出信号时,差模输出驱动器向USB 电缆传送USB信号。 电缆传送USB信号。 在信号的低输出状态,驱动器稳态输出值 必须小于0.3V,且要承担1.5K 必须小于0.3V,且要承担1.5K 的负载加到 3.6V电源的灌电流。 3.6V电源的灌电流。 在信号的高输出状态,驱动器稳态输出值 必须大于2.8V,且要承担15K 必须大于2.8V,且要承担15K 的负载到地 的拉电流。

带USB接口的PC(百万) USB接口的PC(百万)

800 700 600 500 400 300 200 100 0 1999 2000 2001 2002 2003 2004

带USB接口的外设(百万) USB接口的外设(百万)

600 500 400 300 200 100 0 1999 2000 2001 2002 2003 2004

通信设备人员培训计划

通信设备人员培训计划一、培训目标本次培训旨在提高通信设备人员的专业技能和知识水平,使其能够熟练掌握通信设备的安装、维护、调试等工作,并具备解决通信设备故障的能力,从而提高工作效率、降低设备故障率,保障通信系统的正常运行。

二、培训内容1. 通信设备基础知识学习:对通信设备的基本原理、结构、功能进行系统的学习,包括传输设备、通信终端设备、接入网设备等相关知识。

2. 通信设备安装调试:学习通信设备的安装方法、调试步骤,包括设备的布线、接地、安装位置选择、开机自检等技能。

3. 通信设备维护保养:学习通信设备的日常维护保养知识,包括定期检查、清洁、防潮防尘等措施。

4. 通信设备故障排除:学习通信设备故障排除的方法和技巧,包括针对常见故障的排查、分析及修复方法。

5. 相关法律法规及安全操作规程:学习通信设备维护和操作中的相关法律法规,以及安全操作规程。

三、培训安排1. 培训时间:本次培训将持续3个月,每周进行3天培训,每天培训8个小时,共计360个培训课时。

2. 培训地点:培训地点将在公司内部的培训中心进行。

3. 培训方式:采取理论教学与实践结合的方式进行培训,通过理论课程学习和实际操作演练相结合,强化学员的操作技能和实际应用能力。

4. 培训教材:选择通信设备相关的教材和资料,由专业的讲师进行讲解,确保培训内容权威、准确。

四、培训师资力量1. 培训师资:将邀请公司内部通信设备专家和工程师担任培训讲师,确保培训内容的相关性和实用性。

2. 培训师团队:为保证培训师团队的专业性和全面性,将邀请公司多个部门的专业人员组成培训讲师团队,共同参与培训指导工作。

五、培训评估1. 考试评估:对培训结束进行阶段考试和结业考试,对学员的学习情况进行全面评估。

2. 实际操作考核:对学员进行实际操作能力的考核,包括通信设备安装、调试和故障排除等能力的检测。

3. 培训效果评估:对培训结束后的一段时间内学员在工作中的实际表现进行评估,确保培训提高了学员的工作能力和实际效果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬 实现外部设备间的并行工作, 提高了计算机系统的工作效率。但中断

件 系统的保存与恢复现场需一定的时间, 且主机与外设之间的数据交换

技

要由CPU直接控制。这对一些工作频率高、要成批交换数据且单位 数据之间的时间间隔较短的外设,如磁盘、磁带等来说, 将引起CPU

术 频繁干预, 同时还可能引起数据丢失。

件 技

信号变换:完成计算机数字信号与I/O设备信号(如模拟信 号、开关信号、计数脉冲等)的相互转换。

术 中断:接口电路一般有中断功能,以提高接口程序的效率。 基 础接口的高级功能

差错控制:实现检错或纠错。

高层通信协议:实现呼叫、数据加密、流量控制等。

即插即用、电源管理、动态配置等。

它是指当CPU需要与外设备交换数据时,首先查询设备的 状态,只有在设备准备就绪时才进行数据传输。查询式输

机 入和输出程序控制流程如图所示。

硬

件

技

术

基

础

7.1.3 接口软件

计 算

中断控制方式:程序查询法是CPU等待工作,而中断控

制方式是外部设备等待方式。只有当外部设备数据已经准 备好以后,才向CPU发出请求中断信号,在CPU允许中断

机 硬

1) 向CPU发出HOLD信号。 2) 当CPU发出HLDA信号后,接管对总线的控制,进入

件

DMA方式。

技

3) 发出地址信息,能对存储器寻址,能修改地址指针。

术

4) 能发出读或写等控制信号。

基

5) 能决定传送的字节数,判断DMA传送是否结束。

础

6) 发出DMA结束信号,使CPU恢复正常工作状态。

基

中断服务子程序

础

启动打印机 数据传送 数据传送

打印机工作状况

准备

打印

打印

空闲

交换数据 交换数据

7.1.3 接口软件

计 DMA传送方式的提出

算 中断的缺点:采用程序中断控制, 能使多台外设依次启动后同时进行数

机

据交换的准备工作; 若在某时刻有几台外设发中断请求信号,CPU可 根据预先规定好的优先顺序, 按轻重缓急处理几台外设的数据传送,

• 使用方便性和高层协议功能。

7.1 计算机接口原理——接口的功能

计接口的基本功能

算 数据传送:CPU执行输入/输出指令与外部设备交换数据。

机 数据缓冲:用于实现输入输出过程中的暂存。接口电路中存

硬

储机制可以是寄存器(1~2个字节)、FIFO存储器(数十到 数百字节)、或是普通数据存储器。

3FB

实现数据位数、校验等设 置

线路状态寄存器 状态

3FD

指示接收、发送和错误状 态

…

…

……

线路状态寄存器位定义

位

含义

0

接收到数据

1

接收超时错误

2

接收奇偶错误

3

接收帧错误

4

接收间隔错误

5 发送寄存器缓存空

6

发送缓存空

7

发送FIFO错误

缓冲存储机制

计 接口电路的构成——数据缓冲存储接口电路在发送

算 机

和接收过程中,都有缓冲存储机制。多数缓存机制 为FIFO方式。

硬

件 例如:某接口电路具有16字节的发送和接收FIFO

技:

术

基

接口软件写入

础

16字节发送FIFO

已写入未发出数据 16字节接收FIFO

接口电路发送

接口软件读取 已收到未读取数据

接口电路接收

数据变换

计 数据变换可以是电平变换(如RS-232串行接口)、脉冲变

基 DMA(直接存储器存取——direct memory access)控制:是在内存与

础

设备之间开辟一条直接数据传送通路, 并把传送过程交DMA控制器 进行管理, 形成以存储器为中心的体系结构。DMA可看作是和CPU

共享存储器的处理器。CPU与DMA各自能独立地工作, 挖掘了系统

部件级的并行性。

7.1.3 接口软件

技 逐渐减少。

术

基

础

RS-232C 串行接口

插座

7.2 串行接口——RS-232C信号

计 算

异步串行传输:异步串行传输中以字节为传输单位, 传输一个字节包括起始位、数据位和终止位。

机

11010110

+12V

硬

-12V

件

技

空闲 起

数据位:5~8位

停

术

始 位

止 位

算 机

由地址译码器确定控制和状态寄存器地址,不同的接口电路 占用不同的I/O端口地址。

硬 在Windows 件 下,通过设

技 备管理器可

术 以看到一些

基 接口的I/O地

础

址。如串行 接口COM1

的I/O地址:

控制和状态寄存器

计 接口电路的构成——控制和状态寄存器(续) 算 例如:串行接口COM1的I/O地址范围3F8~3FF共8个地址。 机 部分定义如下:

接口与通信设备培训课程

第7章 接口与通信设备

计 7.1 计算机接口原理 算 7.2 串行接口 机 7.3 并行接口 硬 7.4 USB接口 件 7.5 IEEE 1394接口 技 7.6 红外线接口 术 7.7 蓝牙接口 基 7.8 远程通信设备 础 7.9 网络通信设备

7.1 计算机接口原理

计 算 机

硬 ⑶ 将辅存数据缓冲区首地址送入DMA控制器的设备地址寄

件 存器中;

技 术 基

⑷ 将要传送的数据字节数或字数送入数据计数器中。

❖ DMA请求

DMA控制器收到上述控制命令后,向外设接口提出传送 数据请求。外设接口准备好了接收或发送数据时,就会给出

础 DMA请求信号,DAM控制器向CPU提出总线请求信号。

技

术

基

础

串行数据传送方式

计 全双工方式

算

当数据的发送和接收分流,分别由两根不同的传输线传

机 硬

送时,通信双方都能在同一时刻进行发送和接收操作,这样 的传送方式就是全双工(Full Duplex)制。

件

A站

B站

技

术

发送器

接收器

基

础

接收器

发送器

全双工方式示意图

串行数据传送方式

计半双工

算 若使用同一根传输线既作接收又作发送,虽然数据可以 机在两个方向上传送,但通信双方不能同时收发数据,这样的 硬传送方式就是半双工(Half Duplex)制。

7.1.3 接口软件

计 算

DMA方式数据传输的步骤:

机

硬

1) DMA启动

件

2) DMA请求

技

3) DMA响应

术

4) DMA操作

基

5) DMA撤消

础

7.1.3 接口软件

计 ❖ DMA启动 算 ⑴ 向DMA控制器的地址寄存器中送入设备号并启动设备;

机 ⑵ 将主存中数据区首地址送入DMA控制器的地址寄存器中;

机 打印机的数据缓冲寄存器;然后, CPU可继续执行原来的程序,打印机

硬 件

开始打印这批数据。这批数据打印完成后,打印机向CPU发出中断请求 , CPU接到中断请求后对打印机进行中断服务,如再送出一批打印数据 等, 然后又继续执行原来的程序。

技 术

CPU工作状况

主程序执行

中断返回 响应中断 中断返回 响应中断

机 出现的各种事件。

硬

接口软件的程序控制方式主要有三种,即查询控制方式、中断控制 方式和DMA(Direct Memory Access,直接存储器访问)控制方式。

件

技

接口电路

术 基 础

总 线 控 制 接 口

发送FIFO 接收FIFO

发送电路

连

计数器

接

器

接收电路

计数器

7.1.3 接口软件

计 算

查询控制方式:查询式传送控制方式也称为异步传送,

总线

术定完的成地CP址U的对I特/O 基读写的识别。

础

地址总线

地

址

读写控制 译

状态 寄存器

接口 控制 电路

接口的控制。 记录接口的状态、错误。外设 的情况等。CPU通过读状态

寄存器了解接口的情况。

实现对接口的内部时序控

码 中断

制,实现中断,管理缓存 ,写状态寄存器等。

控制和状态寄存器

计 接口电路的构成——控制和状态寄存器

算 机

换(如红外接口)、差分变换(如USB),也可以是数模变 换(如音频)等。

硬 例如:三种基本输出变换: 件 技

5V

-5V

电平变换

术

基

01

础

脉冲变换

5V

0V 5V

差分变换 0V

7.1.3 接口软件

计

接口软件是实现接口功能的软件部分,接口软件连接应用程序与接 口电路。

算

接口软件需要及时掌握接口电路的状态,以便及时处理接口电路中

接口——用于完成计算机主机系统与外部设备之间的信息 交换。接口由接口硬件(接口电路、连接器、连接电缆等) 和接口软件(程序)组成。

硬 件 技接:主口运机软行系件在统

术

主机 系统

(CPU 系统)

总

接口

线

电路

连接电缆

外部 设备

基

础

接口的指标

• 传输速度、传输距离、传输媒介类型; • 可靠性(差错控制) 、安全性(保密); • 资源占用(包括CPU时间、中断、DMA等);

串行接口即通过逐位传送的方式实现字节的传输的一类 接口。串行接口中通常只有一条(可实现双向传输)或两条 (双方向各一条)数据线。由于习惯上的称谓,串行接口有