第7章 中断系统

51单片机学习教程第7章 中断PPT课件

2020/8/20

单片机C语言程序设计

19

中断的优先原则

8051单片机中断优先级遵循以下原则:

中断 Interrupt

1

标题添加

点击此处输入相 关文本内容

标题添加

点击此处输入相 关文本内容

总体概述

点击此处输入 相关文本内容

Байду номын сангаас

点击此处输入 相关文本内容

2

中断的事例

日常生活中有很多计划任务要完成 或突发事件要处理,常用的是查询法, 但更好的处理办法是中断。

如烧开水时,水烧开后应及时切断 加热源。

RI/TI=1

10

单片机中断系统的结构

中断服务程序入口地址和中断号:

中断源

中断标志

中断服务程序入 口地址

优先级顺序

外部中断(INT0) IE0

0003H

高

定时/计数器0(T0) TF0

000BH

↓

外部中断(INT1) IE1

0013H

↓

定时/计数器1(T1) TF1

001BH

↓

串行口

RI和TI

0023H

1. 查询法:不断地检查水是否烧开 2. 中断法:在烧水的壶上装哨子,利用水

烧开后的蒸汽吹响哨子

2020/8/20

单片机C语言程序设计

3

中断的概念

计算机处理的任务按实时性要求分 为两类:

1. 非实时性任务:显示刷新、声音鸣响 2. 实时性任务:系统错误处理、实时监控

对于实时性要求高的任务,出现后 要求立即处理,采用轮询的方式容易实 现,但实时性不高,浪费CPU时间,采 用中断的方式较为适宜。

9

单片机中断系统的结构

微计算机原理(第2版)课后习题答案潘名莲马争丁庆生编著

第七章微计算机的中断系统7-1 什么是中断类型码、中断向量、中断向量表?在基于8086/8088的微机系统中,中断类型码和中断向量之间有什么关系?解:处理机可处理的每种中断的编号为中断类型。

中断向量是指中断处理程序的入口地址,由处理机自动寻址。

中断向量表是存放所有类型中断处理程序入口地址的一个默认的内存区域。

在8086系统中,中断类型码乘4可得到向量表的入口,从此处读出4字节内容即为中断向量。

7-2 什么是硬件中断和软件中断?在PC机中两者的处理过程有什么不同?解:硬件中断通过中断请求线输入电信号来请求处理机进行中断服务;软件中断是处理机内部识别并进行处理的中断过程。

硬件中断一般由中断控制器提供中断类型码,处理机自动转向中断处理程序;软件中断完全由处理机内部形成中断处理程序的入口地址并转向中断处理程序,不需外部提供信息。

7-3 试叙述基于8086/8088的微机处理硬件中断的过程。

解:以INTR中断请求为例。

当8086收到INTR的高电平信号时,在当前指令执行完毕且IF=1的条件下,8086在两个总线周期中分别发出INTA#有效信号;在第二个INTA#期间,8086收到中断源发来的一字节中断类型码;8086完成保护现场的操作,CS、IP内容进入堆栈,清除IF、TF;8086将类型码乘4后得到中断向量入口地址,从此地址开始读取4字节的中断处理程序的入口地址,8086从此地址开始执行,完成INTR中断请求的响应过程。

7-4 在PC机中如何使用“用户中断”入口请求中断和进行编程?解:PC机中分配用户使用的中断是IRQ9,经扩展槽B40h亿引出,故把用户的中断请求线连接到B40h上。

在应用程序中,利用25H号系统调用将中断服务程序的入口地址写入对于0AH 类型中断对应的中断向量表中去。

在应用程序中把主片8259A D2屏蔽位清零,把从主片8259A D1屏蔽位清0,使主片的IR2、从片的IR1可以输入中断请求。

微机原理第7章 8086中断系统和中断控制器

3)高级中断源能中断低级的中断处理

中断嵌套 当CPU正在响应某一中断源的请求,执行为其服务的中断服务程序时, 如果有优先级更高的中断源发出请求,CPU将中止正在执行的中断服务程 序而转入为新的中断源服务,等新的中断服务程序执行完后,再返回到被 1 中止的中断服务程序,这一过程称为中断嵌套。 • 中断嵌套可以有多级,具体级数原则上不限,只取决于堆栈深度。

外部中断 非屏蔽中断 可屏蔽中断

可屏蔽中断源

CPU 中断逻辑

INTR

8259A 中断 INTA 控制器

INT N 指令

INTO 指令

除法 错误

单步 中断

IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

外 设 中 断 源

内部中断: 除法错中断 指令中断 溢出中断 单步中断

硬件(外部)中断 非屏蔽中断请求 INT 2 NMI(17号引脚) 中 断 逻 辑 可屏蔽中断请求 中断类型号32~255 INTR(18号引脚)

中断指令 INT n N=32~255

溢出中断 INTO INT 4

断点 中断 INT 3

单步中断 (TF=1) INT 1

除法 错误 INT 0

软件(内部)中断

8086/8088中断源

1.软件中断(内部中断) 8086/8088的软件中断主要有三类共五种。 (1) 处理运算过程中某些错误的中断 执行程序时,为及时处理运算中的某些错误 ,CPU以中断方式中止正在运行的程序,提醒程 序员改错。 ① 除法错中断(中断类型号为0)。在8086 /8088 CPU执行除法指令(DIV/IDIV)时,若发现 除数为0,或所得的商超过了CPU中有关寄存器所 能表示的最大值,则立即产生一个类型号为0的 内部中断,CPU转去执行除法错中断处理程序。

7章中断系统

① 0型中断——除法出错中断。 ② 1型中断——单步中断。 ③ 3型中断——断点中断(INT)。 ④ 4型中断——溢出中断(INTO指令)

(2)指令中断——INT n指令,其类型号就是 给定的n。

7.2.2 中断向量和中断向量表

IP 000 类型0中断入口(除法出错) CS

专 004 类型1中断入口(单步中断) IP

(2)CPU的标志寄存器入栈,以保护各个标志位, 此操作类似于PUSHF指令。

(3)清除IF和TF标志,屏蔽新的INTR中断和单步 中断

(4)保存断点,即把断点处的IP和CS值压入堆栈, 先压入CS值,再压入IP值。

(5)根据第一步计算出来的地址从中断向量表中 取出中断服务程序的入口地址(段和偏移),分 别送至CS和IP中。

3.若CPU处于开中断状态,则在当前指令 执行结束后,启动中断响应总线操作,发出 两个负脉冲作为响应信号。

4.8259A接收到第一个负脉冲,完成如下工作:

(1)使ISR相应位置1,表示CPU已为该中断请求服务。

(2)使IRR的相应位清0。

5.8259A接收到第二个负脉冲,将中断类型号送 上数据总线。中断类型号由用户编程和中断请求 引脚IRi的序号i共同决定(CPU读取中断类型号, 经响应过程后,进入中断服务程序,直到服务结 束返回)。

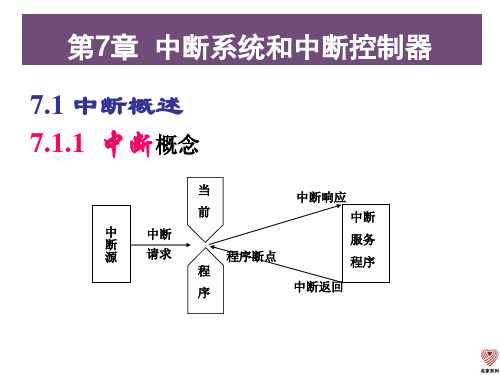

图5-1 中断处理过程

1.中断请求

中断请求是中断过程的第一步。中断源产生中断请求 的条件,因中断源而异

2.中断判优

由于中断产生的随机性,可能出现两个或两个以上的 中断源同时提出中断请求的情况。这时就必须要求 设计者事先根据中断源的轻重缓急,给每个中断源 确定一个中断级别——优先权。

3.中断响应

中断优先权确定后,发出中断申请的中断源中优先权 最高的中断请求就被送到CPU的中断请求引脚上。

第7章 中断

例如: PUSH DS MOV AX, MOV DS, MOV DX, MOV AL, MOV AH, INT 21H POP DS

SEG NEWINT AX OFFSET NEWINT N 25H

7.5 可编程中断控制器8259A

7.5.1 8259A的功能 1.具有8级优先级控制,通过级联可扩充到64级; 2.每一级中断可由程序单独屏蔽或允许;

非屏蔽中断请求 NMI

8259A

2 INTR

CPU

中断逻辑

INT

可编程 IR 4 中断 IR 5 控制器 (PIC) IR 6

IR 7

8086/8088中断源的优先级 优先级 高

低

内部中断 ( 除法出错,INT 指令,断点,INTO指令 ) 非屏蔽中断 可屏蔽中断

低

内部中断( 单步 )

当有多个中断源同时产生中断申请时,CPU先响应 优先权最高的中断源,再响应优先级较低的中断源。

6.4.3 硬件中断响应过程

4)中断处理 保护现场; 开中断,以允许嵌套,也可不开中断; 中断服务; 关中断,保证无干扰恢复现场; 恢复现场。 5)中断返回 开中断; 中断返回。

6.4.3 软件中断响应过程

通过中断指令来调用中断处理子程序,CPU 从指令流中读得终端类型码。 与硬件中断的区别: 1、用一条指令进入中断处理子程序,并且中断 类型码由指令提供。 2、进行中断时,不需执行中断响应总线周期, 也不从DB中读取中断类型码。 3、不受IF的影响。

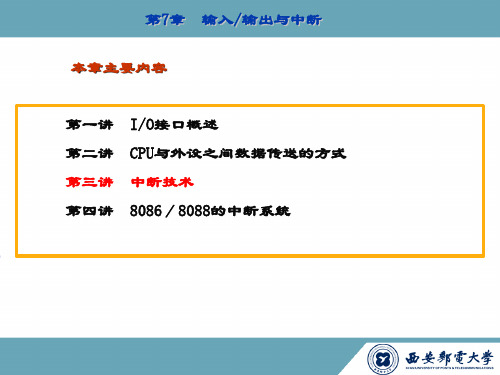

第6章 输入/输出与中断

6.1 6.2 6.3 6.4 6.5

I/O接口概述 CPU与外设之间的数据传送的方式 中断技术 8086/8088中断系统 可编程中断控制器8259A

第7章 中断系统

可 屏 蔽 中 断 请 求

软件中断

硬件中断

小结: 中断分类及中ຫໍສະໝຸດ 类型码8086/8088系统最多可处理256级不同类型的中断。

可屏蔽中断(INTR) 外部中断(硬件中断) 非屏蔽中断(NMI,中断类型码2) 中断分类 单步中断(中断类型码1) 内部中断(软件中断) 断点中断(中断类型码3) 溢出中断(中断类型码4) Int n 中断

器退出暂停状态,响应中断,进入中断处理程序。

若现行指令为WAIT指令,且 TEST 引脚加入低电平信号, 则中断请求信号INTR产生后,便使处理器脱离等待状态,响 应中断,进入中断处理程序。

HLT: 暂停指令

(4) 8259A连续两次接收(2个总线周期) INTA = 0的中断 响应信号后,便通过总线将中断矢量号送CPU。 (5) 保护断点。将标志寄存器内容、当前CS内容及当前IP 内容压入堆栈: (SP)←(SP)-2

((SP)+1:(SP))←(PSW)

(SP)←(SP)-2 ((SP+l:(SP))←(CS) (SP)←(SP)-2 ((SP)+1:(SP))←(IP)

(6) 清除IF及TF(IF←0,TF←0),以便禁止其它可屏蔽中 断或单步中断发生。 (7) 求中断程序的入口地址 :根据8259A向CPU送的中断 矢量号n求得矢量地址,再查中断矢量表,得相应中断处理程 序首地址(段内偏移地址和段地址),并将 位首地址置入CS及

7.1 概述

中断和异常是处理器处理突发事件时所采取的两种不同 的处理方法,具体来说,中断指的是处理器暂停当前的程序, 转而去处理中断事件;而异常虽然也会对异常事件作出反应, 但不一定会暂停当前的程序。 在8086/8088处理器时代,中断主要包括外部中断 和 内 部中断两种。 在386/486等32位处理器时代,内部中断的数量和功能被 扩充,习惯上,称内部中断为异常,而中断则主要指外部中 断。

单片机讲义第七章

一、中断的起因

什么可以引起中断? 生活中很多事件可以引起中断:有人 按了门铃了,电话铃响了,你的闹钟闹响 了,你烧的水开了….等等诸如此类的事件, 我们把可以引起中断的称之为中断源,单 片机中也有一些可以引起中断的事件, 8051中一共有5个:两个外部中断,两个 计数/定时器中断,一个串行口中断。

三、中断的响应过程

当有事件产生,进入中断之前我们必须先记住现 在看书的第几页了,或拿一个书签放在当前页的位置, 然后去处理不同的事情(因为处理完了,我们还要回 来继续看书):电话铃响我们要到放电话的地方去, 门铃响我们要到门那边去,也说是不同的中断,我们 要在不同的地点处理,而这个地点通常还是固定的。 89C51中也是采用的这种方法,五个中断源,每个 中断产生后都到一个固定的地方去找处理这个中断的 程序,当然在去之前首先要保存下面将执行的指令的 地址,以便处理完中断后回到原来的地方继续往下执 行程序。

二、中断的嵌套与优先级处理

设想一下,我们正在看书,电话铃响了,同时又 有人按了门铃,你该先做那样呢?如果你正是在等一 个很重要的电话,你一般不会去理会门铃的,而反之, 你正在等一个重要的客人,则可能就不会去理会电话 了。如果不是这两者(即不等电话,也不是等人上 门),你可能会按你通常的习惯去处理。总之这里存 在一个优先级的问题, 单片机中也是如此,也有优先级的问题。优先级 的问题不仅仅发生在两个中断同时产生的情况,也发 生在一个中断已产生,又有一个中断产生的情况,比 如你正接电话,有人按门铃的情况,或你正开门与人 交谈,又有电话响了情况。考虑一下我们会怎么办吧。

电平触发的外部中断的清除

对于电平触发的外部中断,CPU响应中断后, 虽然也是由硬件清除了相应的标志位,但是不 能对外部引脚上的电平进行处理,也就是说, 这时如果外部引脚上的低电平依然存在,会造 成重复中断,因此我们应该在电路上增加对外 部引起中断的信号进行处理。P148图7-5是一 个可行的方案之一。通过I/O口输出一个信号, 使得外部引脚上的中断请求信号变为高电平。

STC15F2K60S2单片机中断系统 例题

ORG 0100H MAIN:

MOV SP,#60H SETB IT0 SETB EX0 SETB EA LOOP: MOV A, P1 ANL A,#15H JNZ Trouble CLR P1.7 SJMP LOOP Trouble: SETB P1.7

;设定堆栈区域 ;设定外部中断 0 为下降沿触发方式 ;开放外部中断 0 ;开放总中断

void int0_isr( ) interrupt 0

{

Pl = i;

i <<= 1 ; if(i==0) i = 0xfe;

//移位 8 次后,i 将变为 0,需要重新赋值

} /*------------------------ 主函数------------------------*/

139

void main(void) {

汇编语言参考程序如下:

ORG 0000H

LJMP MAIN

ORG 0003H

LJMP INT0_ISR

ORG 0l00H

MAIN:

MOV A,#0FEH ;设置 LED 灯起始驱动信号

SETB IT0

;设置外部中断 0 为下降沿触发方式

SETB EX0

;开放外部中断 0

SETB EA

;开放总中断

SJMP $

;读取 P1 口中断输入信号 ;截取中断输入信号 ;有中断请求,转 Trouble,熄灭正常工作指示灯 LED3 ;无中断请求,点亮 LED3 ;循环检查与判断

;熄灭 LED3

141

SJMP LOOP

;循环检查与判断

INT0_ISR:

JNB P1.0,No_Trouble_0 ;查询 0 号故障源,无故障转 No_Trouble_0,熄灭 LED0

第7章 中断处理

多道程序或多重任务的运行:分时中断处理。 多道程序或多重任务的运行:分时中断处理。

4. 中断源 任何能够引发CPU中断的事件都称为中 中断的事件都称为中 任何能够引发 中断的事件 断源。 断源。

二、多中断源情况下的特殊问题

1. 中断源的识别

对于软件中断而言,CPU对中断源的识别靠 对于软件中断而言, 对中断源的识别靠 软件中断指令( 来识别, 软件中断指令(INT n)中的中断号 来识别,并 )中的中断号n来识别 转到响应中断服务程序去执行。 转到响应中断服务程序去执行。 对于硬件中断,CPU只有一个 只有一个NMI和INTR引 对于硬件中断,CPU只有一个NMI和INTR引 当有多个外设要申请中断时, 脚,当有多个外设要申请中断时,就必须通过中 断接口电路来连接, 断接口电路来连接,同时给每个中断外设编排一 个中断号( 系统称为中断类型码)。 个中断号(8086系统称为中断类型码)。当任一 系统称为中断类型码)。当任一 外设有中断申请时, 外设有中断申请时,通过中断接口电路将外设中 断信号转发给CPU,然后再由 断信号转发给 ,然后再由CPU从中断接口电 从中断接口电 路读取该中断源的编号。 路读取该中断源的编号。

中 断 控 制 器

IRQ0 IRQ1

外设0 外设1

IRQn

外设n

软硬件结合的简易中断控制器

≥1

2. 中断优先级 对于多中断源而言, 对于多中断源而言,存在各中断源的优先级别 问题。当两个及以上的中断源同时申请中断时, 问题。当两个及以上的中断源同时申请中断时,最 先响应哪个中断源的中断请求, 先响应哪个中断源的中断请求,则由它们的优先级 别决定。 别决定。 可屏蔽中断源的优先级别由中断控制器决定。 可屏蔽中断源的优先级别由中断控制器决定。 8086系统中各类中断的优先级别如下: 系统中各类中断的优先级别如下: 系统中各类中断的优先级别如下

《单片机原理与技术》课件第7章-中断

1.定时器/计数器控制寄存器TCON

位7

位6

位5

位4

位3

位2

位1

位0

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

IT0:外部中断INT0触发方式选择 位。可由用户用软件选择。 • IT0=1:设定外部中断引脚信号为下降 沿触发方式。 •

IT1:外部中断INT1触发方式选择 位,其功能类似于IT0。 • IE0:外部中断INT0触发有效标志 位。 • IE1:外部中断INT1触发有效标志 位,其功能类似于IE0。 •

•

定时器0与定时器1标志为TF0与TF1, 在定时器溢出周期的S5P2设置。然后其值 在下一周期由电路查询。然而,定时器2标 志TF2是在S2P2设置且在定时器溢出的同 一周期内被查询。 Nhomakorabea•

若请求有效且响应的条件正确,至请 求的服务例程的硬件子例程调用将是下一 条要执行的指令。CALL自己需要两个周期。 因此,在外部中断请求的激活与服务例程 的第一条指令的执行开始之间,至少需要3 个完整的机器周期。图7-9所示为中断响应 时序。

图7-4 中断响应、服务及返回流程图

7.3 80C51中的中断结构

7.3.1 中断启用

图7-5 MCS-51中断源

图7-6 80C51中的IE(中断启用)寄存器

7.3.2

中断优先权

图7-7 80C51中的IP(中断优先级)寄存器

7.3.3

•

中断如何处理

在操作中,所有中断标志在每个机器 周期的S5P2期间被采样。在下一个机器周 期期间查询采样。若找到一启用的中断的 标志已设置,中断系统生成一LCALL至在 程序存储器中的适当单元,至中断服务例 程的LCALL的生成,由以下3个条件中的任 一个阻断:

ARM Cortex-A9多核嵌入式系统开发教程 第七章

Highest priority interrupt

CPU Interface 1

enable_c1[ ] match_c1[ ]

nfiq_c1 nfriq_c1

AMBA slave interface

AMBA interface

enable_dn[ ] match_dn[ ] ppi_cn[15:0] legacy_nfiq_cn legacy_nirq_cn

第7章 Exynos 4412中断系统

2、中断类型 (1) 软件生成的中断(SGIs):是通过向软件生成中断寄存器 写入SGI中断号生成的。SGI一般被用作核间中断,用于核 间通信。 (2) 私有外设中断(PPI),由一个单独的处理器私有的外 设生成。 (2) 私有外设中断,由一个单独的处理器私有的外设生成。

第7章 Exynos 4412中断系统

7.1.1 中断相关术语 1、中断状态 每个中断可以被认为处于以下4个状态之一:

(1) 未激活(Inactive),中断尚未激活或未挂起; (2) 挂起(Pending),中断已经由硬件或者软件产生,正等 待目标CPU响应; (3) 激活(Active),CPU已经应答(Acknowledge)来自GIC的 中断,该中断正在被CPU处理但尚未完成; (4) 激活并挂起(Active&Pending),CPU正在处理该中断, 此时GIC又收到来自该中断源的更高优先级的中断。

Exynos 4412中断系统

Exynos 4412的中断系统概述 Exynos 4412中断机制分析 中断控制相关寄存器 中断处理程序实例

第7章 Exynos 4412中断系统

7.1 中断系统概述

Exynos 4412 采用了通用中断控制器(Generic Interrupt Controller,GIC PL390)对其中断系统进行控制和管理。 Exynos 4412共支持160个中断,其中包括16个软件生成的 中断、16个CPU核的私有外设中断、128个CPU核共享的外 设中断。其中,软件生成的中断通过写一个专用寄存器 (ICDSGIR)生成,通常被用于内部处理器之间的通信。

第7章中断和中断程序设计

5)数据总线缓冲器

8位的双向三态缓冲器,用作8259A与系统总线的接口,传 送命令控制字、状态字和中断向量。

D0~D7:为双向数据线,数据缓冲器暂时保存在内部总线和 系统数据总线间进行传送的数据。

7.2 程序中断设备接口的组成和工作原理

第7章

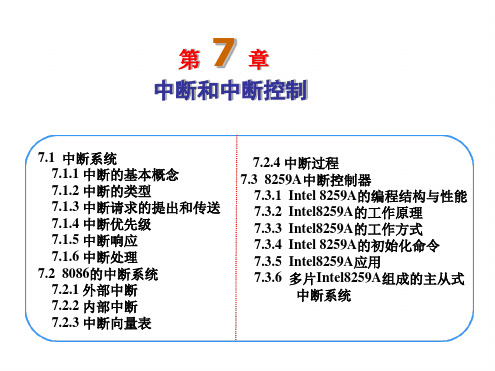

中断和中断控制

7.1 中断系统 7.1.1 中断的基本概念 7.1.2 中断的类型 7.1.3 中断请求的提出和传送 7.1.4 中断优先级 7.1.5 中断响应 7.1.6 中断处理

7.2 8086的中断系统 7.2.1 外部中断 7.2.2 内部中断 7.2.3 中断向量表

7.2.4 中断过程 7.3 8259A中断控制器

(1)关中断

进入不可再次响应中断的状态,由硬件自动实现。因为 接下去要保存断点,保存现场。 在保存现场过程中,即使有 更高级的中断源申请中断, CPU也不应该响应 ;否则,如果 现场保存不完整,在中断服务程序结束之后,也就不能正确 地恢复现场并 继续执行现行程序。

(2)保存断点和现场。

为了在中断处理结束后能正确地返回到中断点,在响应 中断时,必须把当前的程序计数器 PC中的内容(即断点)保 存起来。

7.1.5 中断处理

7.1 程序中断输人输出方式

2.多重中断处理

多重中断是指在处理某一个中断过程又发生了新的中 断请求,从而中断该服务程序的执行,又转去进行新的中 断处理。这种重叠处理中断的现象又称为中断嵌套。

一般情况下,在处理某级中的某个中断时,与它同级的 或比它低级的新中断请求应不能中断它的处理。而比它优 先级高的新中断请求却能中断它的处理。

微型计算机原理-第7章(3)微机原理与接口技术(第三版)(王忠民)

第7章 输入/输出与中断-中断技术

… …

…

D7 D0 CPU

INTR

中 断 寄 存 器

INT ≥1

INT1 INT2

INT8

图7.13 软件查询法的硬件电路

第7章 输入/输出与中断-中断技术

断点保护

INT1? Y N INT2? Y N

对1号中 断源服

务 对2号中 断源服

务

… …

INT8? Y N

1. 中断的定义

计算机在执行正常程序 过程中,当出现某种异常 事件或某种外部请求时, 处理器就暂停执行当前的 程序,而转去执行对异常 事件或某种外部请求的处 理操作。当处理完毕后, CPU再返回到被暂停执行的 程序,继续执行,这个过 程称为程序中断。

主程序

有中断请求

断点 继续执行

中断服务程序 中断处理

第7章 输入/输出与中断-中断技术

① 中断请求:是中断源向CPU发出的请求中断的要求。 软件中断源是在CPU内部由中断指令或程序出错直接

发中断; 硬件中断源必须通过专门的电路将中断请求信号送给

CPU,CPU也有专门的引脚接收中断请求信号。

第7章 输入/输出与中断-中断技术

② 中断响应:是指当计算机系统接收到中断请求后应作出的反 应。对于可屏蔽中断的响应要具备两个条件:一是中断允许触发器 的状态为1(即开中断),二是CPU在执行完现行指令之后。

返回断点

第7章 输入/输出与中断-中断技术

2. 中断系统 为实现中断功能而设置的硬件电路和与之相应的软件,称为中

断系统。 3. 中断源

引起中断的原因或发出中断请求的来源称为中断源。中断源可 分为硬件中断源和软件中断源两类。 4. 中断处理过程

单片机原理及接口技术 第3版课件(梅丽凤)第7章

MOV TH1,#0D8H;赋初值 MOV TL1,#0F0H MOV IE,#88H ;CPU开中断,TT1开中断 SETB TR1 ;启动T1工作 MOV 60H,#100;赋毫秒计数初值 MOV 61H,#60 ;赋秒计数初值 CLR 4FH ;清标志位 TT:JNB 4FH,TT ;等1min时间到 CLR 4FH ;1min到,清标志位 CPL P1.0 ;输出反相 AJMP TT ;反复循环 END

ORG 0030H ;主程序初始化 START:MOV SP,#60H ;置堆栈指针 SETB IT0 ;置边沿触发方式 MOV IP,#01H ;置为高优先级 MOV IE,#81H ;CPU开中断、开中断 MOV 30H,#00H ;里程计数器单元清0 MOV 31H,#00H MOV 32H,#00H LJMP MAIN ;转主程序执行,并等待中断 ORG 0100H ;中断程序,中断一次,里程加2 m INT:PUSH ACC ;保护现场 PUSH PSW MOV A,30H ;读里程计数器低8位 ADD A,#02 ;低8位计数器加2m(运转一圈) MOV 30H,A ;回存

【例7-3】 出租车计价器的计程方法是:车轮 每运转一圈产生一个负脉冲,从外中断 (P3.2)引脚输入,行使里程为轮胎周长× 运转圈数。假设轮胎周长为2m,试编程实时 计算出租车行使里程(单位:米),数据存 放到32H、31H、30H单元中。 编程: ORG 0000H ;上电、复位入口地址 L JMP START ;转向主程序初始化 ORG 0003H ;中断入口地址 LJMP INT ;转向中断服务程序

图7-4 中断处理过程流程图

7.3.4 中断请求的撤除

响应某中断请求后,其中断请求标志位应及时清除,否则 会引起另一次中断。各标志位清除方法不一样。

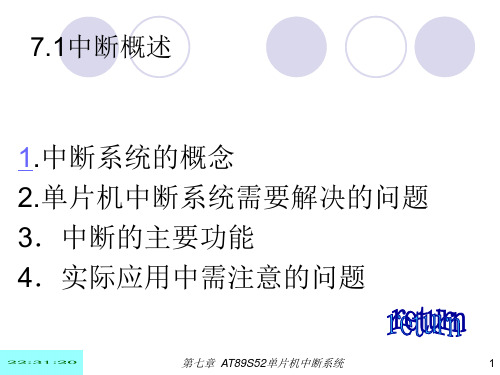

第七章AT89s52单片机中断系统

高 优 先 级

低 优 先 级

7

3.中断触发方式

①.电平触发方式 ②.下降沿触发方式

第七章 AT89S52单片机中断系统

8

7.2.2 中断标志与控制

单片机设置了5个专用寄存器用于中 断控制,用户通过设置其状态来管理中 断系统。5个专用寄存器包括:

定时器/计数器0,1控制寄存器TCON; 定时器2控制寄存器T2CON; 串行口控制寄存器SCON; 中断允许控制寄存器IE; 中断优先级控制寄存器IP。

第七章 AT89S52单片机中断系统

9

1.定时器/计数器0,1控制寄存器TCON

D7 D6 D5 D4 D3 D2 D1 D0

TCON TF1

TF0

IE1 IT1 IE0 IT0 字节地址:88H

位地址 8FH 8EH 8DH 8CH 8BH 8AH 89H 88H 可位寻址

TF1(TCON.7)—T1计数溢出,由硬件置位,响应中断

2

(2)中断源

中断源通常可分为以下几种: 设备中断 定时中断 故障源中断 程序性中断源

第七章 AT89S52单片机中断系统

3

(4) 中断识别方式

一般设有两种识别方式: 查询中断 矢量中断。

第七章 AT89S52单片机中断系统

4

(5) 中断的其它概念

中断请求、中断标志、中断允许、 中断入口地址(中断矢量)、中断 嵌套、中断保护、中断服务程序、 中断源清除、中断屏蔽、中断返回、 中断等待 。

当EA=1时,允许所有中断开放,总允许后,各中断的允许 或禁止由各中断源的中断允许控制位进行设置;

当EA=0时,屏蔽所有中断。

第七章 AT89S52单片机中断系统

14

第7章单片机的中断系统答案

一、选择题1、若要求最大定时时间为216×机器周期,则应使定时器工作于 B 。

A.工作方式0B.工作方式lC.工作方式2D.工作方式32、若要求最大定时时间为213×机器周期,则应使定时器工作于 A 。

A.工作方式0B.工作方式lC.工作方式2D.工作方式33、若要求最大定时时间为28×机器周期,则应使定时器工作于 C ,D 。

A.工作方式0B.工作方式1C.工作方式2D.工作方式34、定时器方式控制寄存器TMOD中MlM0为l l时,则设置定时器工作于 D 。

A.工作方式0B.工作方式lC.工作方式2D.工作方式35、6MHz晶振的单片机在定时工作方式下,定时器可能实现的最小定时时间是 B .A.1 u sB.2 u sC.4 u sD.8 u s ’6、12MHz晶振的单片机在定时工作方式下,定时器可能实现的最小定时时间是 A .A.1 u sB.2 u sC.4 u sD.8 u s7、12MHz晶振的单片机在定时工作方式下,定时器可能实现的最大定时时间是 B .A.4096 u sB.8192 u SC.1638 u sD.32768 u s8、定时器/计时器0的初始化程序如下:MOV TMOD,#06HMOV TH0.#0FFHMOV TLO,#0FFHSETB EASETB ET0执行该程序段后,把定时器/计时器0的工作状态设置为 D 。

A. 工作方式0,定时应用,定时时间2 u s,中断禁止B.工作方式l,计数应用,计数值255,中断允许C.工作方式2,定时应用,定时时间510 u s,中断禁止D.工作方式2,计数应用,计数值1,中断允许9、设串行口工作于方式l,晶振频率为6MHz,波特率为1200位/秒,SMOD=0,则定时器l的计数初值为 C 。

A.FlHB.F4HC.F3HD.FOH10、以下所列特点,不属于串行工作方式0的是 D 。

A.波特率是固定的,为时钟频率的十二分之一B.8位移位寄存器C.TI和RI都须用软件清零D.在通信时,须对定时器l的溢出率进行设置11、通过串行口发送或接收数据时,在程序中应使用 A 。

推荐-第7章中断系统中断的作用 精品

程序。

注意:在中断服务程序中,除完成正常的中断服务以外, 最后要执行IRET指令。IRET指令执行三个出栈操作,按次 序恢复断点处的IP和CS以及FLAGS的值,使程序恢复到断 点处继续执行。

8086获得中断类型码的途径

7.1.2 中断的基本概念

➢ 中断源:任何能引发中断的事件都称为中断源。

✓ 硬件中断源:I/O设备,系统时钟,故障源等 ✓ 软件中断源:程序中断指令(INT 21H),指令运行出错

(INTO)等

➢ 断点:主程序被中断的地方称为断点。

✓ 断点处的指令是CPU完成中断处理后返回主程序时恢复 执行的第一条指令,该指令的存储地址称为返回地址。

280868088的中断系统?8086有一个强有力的中断系统?向量型中断结构共256种中断类型?外部可屏蔽中断intr和非屏蔽中断nmi?内部多种软件中断特有的指令中断微型计算机技术?硬件提供优先级判优电路及中断类型码获得机构中断响应速度快

第7章 中断系统

➢ 中断的作用 ➢ 中断的基本概念 ➢ 中断系统的功能 ➢ 8086/8088的中断系统

✓ 返回操作:由硬件完成将断点弹出到程序计数器中的操 作,这种操作由中断返回指令来完成。

➢ 现场:是指进入中断服务程序之前CPU各个寄存器 的状态。

断点、返回地址与中断返回

正常程序 CS : IP 断点 CS : IP+1

继续执行

中断服务程序 中断 处理

返回断点

7.1.3 中断系统的功能

➢ 1、实现中断及返回

87H 段地址高8位 CS

86H 段地址低8位

85H 偏移量高8位 IP

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(2)软件中断:即根据某条指令或者对标志寄存器中某个标志 的设置而产生,它与硬件电路无关,常见的如除数为0,或 用INT n指令产生。

INT n指令 非屏蔽中断请求

NMI 中 断 逻 辑 INTR 中 断 控 制 系 统

( 8259A)

INT 3 INTO 指令 指令

单步 中断

除数为0 中断

。 。 。

2. 矢量地址

矢量地址 = (中断矢量类型号*4)

0000:007EH 0000:007FH 0000:0080H 0000:0081H 0000:0082H 0000:0083H 0000:0084H

… 12H 45H 10H 20H 30H 40H 52H

… 【例】某段内存空间的内容如右图所示。若已知中断的类型号 为20H, 求中断服务子程序的入口地址。 解:中断向量的存放位置为20H×4=80H,则在中断矢量地址 0000:0080H~0000:0083H中就应顺序放入10H、20H、30H、 40H(IP=2010H CS=4030H,即中断服务子程序的入口地址为 4030:2010 )。 当系统响应类型为20H号中断时,会自动查找中断向量, 找出对应的中断向量装入CS、IP,即转入该中断服务子程序。

7.1 概述

中断和异常是处理器处理突发事件时所采取的两种不同 的处理方法,具体来说,中断指的是处理器暂停当前的程序, 转而去处理中断事件;而异常虽然也会对异常事件作出反应, 但不一定会暂停当前的程序。 在8086/8088处理器时代,中断主要包括外部中断 和 内 部中断两种。 在386/486等32位处理器时代,内部中断的数量和功能被 扩充,习惯上,称内部中断为异常,而中断则主要指外部中 断。

连续2个

IF←0, TF ←0,禁止发生可屏蔽中断和单步中断 根据中断类型码求中断的入口地址CS:IP,转入 相应的中断子程序

堆栈

IRET

开中断为 了实现中 断的嵌套

外部可屏蔽中断的响应和处理过程

(3) CPU是否立即发中断响应信号 INTA ? 如果现行指令不是HLT或WAIT指令,则CPU执行完当前 指令后便向8259A发出中断响应信号( 响应该可屏蔽中断请求。 若现行指令为HLT,则中断请求信号INTR的产生使处理 = 0),表明CPU INTA

7.4 中断及异常的优先级 (p321)

当计算机系统中有多个中断源时,中断管理系统将规定一

套机制,用以解决多个中断源得到CPU服务的先后次序。 当80X86 CPU完成当前指令的执行后,

将先按照以下的顺序检查是否有中断(包括异常)请求:①

除法出错;② 中断指令INT n;③ 溢出中断;④ 非屏蔽中断 NMI;⑤ 可屏蔽中断INTR;⑥ 单步中断。 然后把优先级最高的中断或异常通知给系统,将优先级较 低的异常废弃,而将优先级较低的中断挂起;当把较高优先级

器退出暂停状态,响应中断,进入中断处理程序。

若现行指令为WAIT指令,且 TEST 引脚加入低电平信号, 则中断请求信号INTR产生后,便使处理器脱离等待状态,响 应中断,进入中断处理程序。

HLT: 暂停指令

(4) 8259A连续两次接收(2个总线周期) INTA = 0的中断 响应信号后,便通过总线将中断矢量号送CPU。 (5) 保护断点。将标志寄存器内容、当前CS内容及当前IP 内容压入堆栈: (SP)←(SP)-2

为什么要使用中断? 为了解决这个矛盾,提出了中断传送方式,即当CPU 进行主程序操作时,外设的数据已存入输入端口的数据寄 存器;或端口的数据输出寄存器已空,由外设通过接口电 路向CPU发出中断请求信号,CPU在满足一定的条件下, 暂停执行当前正在执行的主程序,转入执行相应能够进行 输入/输出操作的子程序,待输入/输出操作执行完毕之后 CPU即返回继续执行原来被中断的主程序。 这样CPU就避免了把大量时间耗费在等待、查询状态 信号的操作上,使其工作效率得以大大地提高。

软件中断是应用程序提出的中断,每一个软件中断 都对应一个标准的功能,如:在屏幕上显示一个字符串, 或者从键盘接受一个字符,等等。 本章所介绍的中断,如果没有特别说明,不包括软 件中断。

7.3 异常

p313

① 异常的定义:

异常是在指令执行期间检测到的不正常的或非法的

状态,使指令不能成功执行。 异常是与特定指令的执行相联系的。例如,当微处 理器执行除法指令时,若商太大,使目的寄存器容纳不 下,或是试图以零作除数,则称产生异常0。异常的发生 源于微处理器内部,且总是与微处理器操作同步。

7.2

中断的定义: p312

中断实质上是指一种处理过程。 当计算机在执行 正常程序的过程中,如果出现某些异常事件或某种外部 请求时,处理器就暂停执行当前的程序,而转去执行对 异常事件或某种外部请求的处理操作;当处理完毕后, CPU再返回到被暂停执行的程序,继续执行,这个过程 被称为程序中断,简称中断。 外部中断是由外部设备通过CPU的中断请求线(如 INTR)向CPU提出的。能够向CPU发出中断请求的设备 或事件称为中断源。

① 保护现场(由一系列的PUSH指令完成)。目的是为了保护那 些与主程序中有冲突的寄存器,(如AX,BX,CX等),如果中 断服务子程序中所使用的寄存器与主程序中所使用的寄存器等 没有冲突的话,这一步骤可以省略。 ② 开中断(由STI指令实现)。目的是为了能实现中断的嵌套。 ③ 中断服务 ④ 恢复现场是与保护现场对应的,但要注意数据恢复的次序,以 免混乱。 ⑤ 返回(使用中断返回指令IRET)。 中断处理程序执行完毕, 最后执行一条中断返回指令IRET,将原压入堆栈的标志寄存 器内容及断点地址重又弹出至原处。

中断向量和中断向量

000H

004H 008H IP偏移地址 CS段基地址 IP偏移地址 CS段基地址 IP偏移地址 CS段基地址

中断类型码0(除法错)

中断类型码1(单步中断) 中断类型码2(NMI中断)

00CH

014H

中断类型码3(断点中断)

中断类型码4(溢出中断)

· · · · · ·

中断类型码5(保留)

… …

系统保留中断

类型17~31

080H

…

用户自定义中断 类型32~255

3FFH

图示给出了中断类型码与中断向量所在位置之间的对 应关系。共有256个中断(00H~0FFH),其中: 类型00H~04H:专用中断; 类型05H~3FH:系统保留中断; 类型40H~0FFH:用户定义的中断。

BIOS: 基本输入输出系统 中断向量和中断向量表: 00H~04H----系统专用 10H~1FH----BIOS用( INT 21H 即为MS-DOS 的系统调用) 40H~FFH----用户用 08H~0FH----硬件中断 20H~3FH----DOS用

1. 中断矢量表: p322

8086中断系统中的中断向量表是位于0段的0~3FFH 的存贮区内,每个中断向量占四个单元,其中前两个单元存 放中断处理子程序的入口地址的偏移量(IP),低位在前,高 位在后;后两个单元存放中断处理子程序入口地址的段地址 (CS),也是低位在前,高位在后,整个中断向量的排列是按 中断类型号进行的。

第七章

中断和异常

7.1 概述 7.2 中断 7.3 异常 7.4 中断及异常的优先级 7.5 8086中断系统 7.6 中断优先级管理器8259A-PIC 习题与思考题

为什么要使用中断?

从查询较简单。但在此方式下,CPU要不 断地查询外设的状态,当外设未准备好时,CPU就只能 循环等待,不能执行其它程序,这样就浪费了CPU的大 量时间,降低了主机的利用率。

7.5.2 中断向量表(P322)

中断向量:把各个中断服务子程序的入口地址都称为一个 中断向量; 中断向量(矢量)表:将中断向量按一定的规律排列成一 个表构成中断向量表,当中断源发出中断请求时,即可查找该 表,找出其中断向量,就可转入相应的中断服务子程序。 向量表地址:中断向量在中断向量表中的位置。 实地址方式下,微处理器采用中断矢量表(Interrupt Vector Table, IVT)的方法来存储转入中断处理程序的入口地址。 中断矢量表起始于物理内存地址0,长度为1 KB,并依中 断矢量号为序连续存放256个中断的中断处理程序首地址。

IP中, 程序就被转入并开始执行中断处理程序。

(IP)←(4×N) (CS)←(4×N+2) (8) 中断处理子程序包括保护现场、中断服务、(开中断)、 恢复现场及返回等部分。

寄 存 器

即清除IF及TF(IF←0, TF←0),以便禁止其它可屏 蔽中断或单步中断发生为了 实现中断的嵌套。

图7-4 中断处理子程序

可 屏 蔽 中 断 请 求

软件中断

硬件中断

小结: 中断分类及中断类型码

8086/8088系统最多可处理256级不同类型的中断。

可屏蔽中断(INTR) 外部中断(硬件中断) 非屏蔽中断(NMI ,中断类型码2) 中断分类 单步中断(中断类型码1) 内部中断(软件中断) 断点中断(中断类型码3) 溢出中断(中断类型码4) Int n 中断

的中断处理完后,再按优先级次序响应和处理挂起的中断。

7.5 8086中断系统

7.5.1 中断分类及中断类型码

中断源 引起中断的原因或发出中断请求的设备称为中断源。

1. 中断分类 p314 中断源可以分为两大类,即外部(硬件)中断和内部(软件)中断。 (1)硬件中断:即通过外部的硬件产生的中断,如打印机、键 盘等。硬件中断又可分为:可屏蔽中断 和 非屏蔽中断。

②异常分类: 产生异常后,系统根据引起异常的程序是否可被恢复这一 原则,进一步又把异常分为故障(Fault)、陷阱(Trap)和中止 (Abort)三类。

故障是引起该故障的程序可被恢复执行的异常,它也是 在引起故障的指令执行之前就报告给系统的一种异常。 陷阱是在指令执行期间被检测到的,并在引起异常的指 令执行之后向系统报告的一种异常。 中止是微处理器面临严重错误时产生的异常。例如,系 统出现硬件错误或系统表中出现非法值或不一致的值时,便产 生中止异常,引起中止的指令无法确定。产生中止时,正执行 的程序不能被恢复。因而,产生中止异常后,系统需重建各种 系统表格,或需重新启动操作系统。