第六章嵌套向量中断

nvic嵌套向量中断控制器工作原理

一、引言Nvic嵌套向量中断控制器(Nested Vectored Interrupt Controller)是一种常见的中断控制器,它在嵌入式系统中扮演着重要的角色。

本文将介绍Nvic的工作原理,帮助读者更好地理解这一关键的硬件组件。

二、Nvic的基本概念Nvic是一种硬件组件,用于管理和分发系统中的中断请求。

在嵌入式系统中,当发生外部事件或者特定的处理器状态发生变化时,需要立即中断当前的程序执行,执行特定的中断服务程序。

而Nvic就是用来协调这些中断请求的,确保它们按照优先级和顺序得到正确的处理。

三、中断控制器的作用1.管理中断请求中断是在嵌入式系统中的一种重要的事件响应机制。

当外部设备(如传感器、通信接口等)产生需要处理的事件时,会向处理器发送中断请求。

而中断控制器就是负责接收、管理和分发这些中断请求的硬件组件。

2.中断优先级在一个嵌入式系统中,可能同时出现多个中断请求,此时中断控制器需要根据中断请求的优先级决定哪个中断将被优先处理。

Nvic通过优先级编码的方式,能够准确地确定中断的优先级,确保高优先级的中断能够得到及时处理。

四、Nvic的工作原理1.中断向量表Nvic通过中断向量表来实现对中断请求的管理。

中断向量表是一张表格,每个中断都有一个特定的中断向量号。

当中断控制器接收到中断请求时,根据中断向量号可以迅速定位到对应的中断服务程序的入口位置区域,从而进行中断处理。

2.中断优先级编码Nvic使用中断优先级编码的方式来确定中断的优先级。

在Nvic中,中断请求会按照其具体的中断向量号进行编码,从而确定其优先级。

当多个中断请求同时到达时,Nvic会根据优先级编码来决定哪个中断会被优先处理。

3.嵌套中断Nvic支持嵌套中断的机制,即在一个中断服务程序的执行过程中,如果遇到了更高优先级的中断请求,Nvic可以暂停当前中断服务程序的执行,转而处理更高优先级的中断请求。

这种机制可以确保高优先级的中断能够得到及时处理,提高系统的响应速度。

天脉(ACoreOS)操作系统培训第六章:异常、中断与定时器

启动(或)重启动看门定时器

STATUS wdStart (WDOG_ID wdId, int delay,

FUNCPTR pRoutine,int parameter )

wdId 看门狗ID,由创建wdCreate返回源自delay 延时的tick值

pRoutine 延时时间到时调用程序

23 parameter

wdStart() + semGive():更加健壮

28

查询警告

下列代码是正确的,只有当系统时钟频率是15Hz 的整数倍

void myWdISR() {

wdStart(myWdId,sysClkRateGet()/15,myWdISR,0); pollMyDevice(); }

为了防止系统在每个时钟tick开销过大,不能 够将系统时钟频率设置过高

中断的工作原理

10

中断处理示例-PowerPC

11

中断处理示例说明

PowerPC有单独的外部中断引脚。板级支持包 (BSP)可以支持外部中断控制器实现中断嵌套。

中断表中中断入口数量取决于BSP中中断控制器的 能力。目前中断向量表最多可支持256个。

外部中断的处理流程

保存CPU寄存器 从中断控制器中读取中断号 调用用户连接的中断处理程序(用户关心) 清中断控制器状态 12 恢复CPU寄存器并返回

fooDoWork()必须每 10秒运行,如果执行小 于10秒钟,看门狗重新 启动(fooISR()没有被 调用)。如果 fooDoWork()执行时间 超过10秒钟,则看门狗 程序fooISR()将被调用 处理紧急事件

停止看门狗

取消先前启动的看门狗 STATUS wdCancel (WDOG_ID wdId)

LPC1700 第6章 嵌套向量中断控制器

目录

第6章嵌套向量中断控制器 (1)

6.1特性 (1)

6.2描述 (1)

6.3中断源 (1)

第6章嵌套向量中断控制器

6.1特性

?ARM Cortex-M3内部包含有嵌套向量中断控制器;

?与内核紧密联系的中断控制器,可支持低中断延时;

?可对系统异常和外设中断进行控制;

?支持33个嵌套向量中断;

?32个可编程的中断优先级;

?硬件优先级屏蔽;

?可重定位的向量表;

?不可屏蔽中断;

?软件中断功能。

6.2描述

嵌套向量中断控制器(NVIC)是Cortex-M3的一个内部器件。

与CPU紧密结合,降低了中断延时,让新进中断可以得到高效处理。

可参考《ARM®Cortex TM-M3技术参考指南》来获取NVIC操作的详细描述。

6.3中断源

表6.1列出了每一个外设功能所对应的中断源。

每一个外围设备可以有一条或几条中断线连接到向量中断控制器。

多个中断源也可以共用一条中断线。

除过ARM内核指定的某些标准外,哪一条中断线连接到哪一个中断源是无关紧要的或没有优先级的。

表6.1连接到向量中断控制器(VIC)的中断源。

STM32中NVIC(嵌套向量中断控制)的理解

STM32中NVIC(嵌套向量中断控制)的理解NVIC,中文名嵌套中断向量控制器,是Cortex-M3 系列控制器内部独有集成单元,与CPU 结合紧密,降低中断延迟时间并且能更加高效处理后续中断。

举个例子,比如火车站买票,那些火车站的规章制度就是NVIC,规定学生和军人有比一般人更高优先级,它们则给你单独安排个窗口,同学与同学之间也有区别,那就是你也得排队,也就是你的组别(抢断优先级)和你的排队序号(响应优先级)决定你何时能买到票。

抢断优先级,顾名思义,能再别人中断是抢占别人中断,实现中断嵌套。

响应优先级则只能排队,不能抢在前面插别人的对,即不能嵌套。

STM32 中指定优先级的寄存器为4 位,其定义如下:第0 组:所有4 位用于指定响应优先级第1 组:最高1 位用于指定抢占式优先级,最低3 位用于指定响应优先级第2 组:最高2 位用于指定抢占式优先级,最低2 位用于指定响应优先级第3 组:最高3 位用于指定抢占式优先级,最低1 位用于指定响应优先级第4 组:所有4 位用于指定抢占式优先级以上定义也称作中断优先级分组,相关内容在STM32 固件库的misc.h 文件中有详细定义。

基础了解了就可以对中断进行操作了。

第一步:使用void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)函数对优先级分组配置。

NVIC_PriorityGroup 可以配置为NVIC_PriorityGroup_0 => 选择第0 组NVIC_PriorityGroup_1 => 选择第1 组NVIC_PriorityGroup_2 => 选择第2 组NVIC_PriorityGroup_3 => 选择第3 组NVIC_PriorityGroup_4 => 选择第4 组例如:NVIC_PriorityGroupConfig(NVIC_PriorityGroup_0)配置为0 组。

第六章嵌套向量中断

概述

LPC1700系列ARM具有4路外部中断,可以设置为2种类型: 边沿触发: 上升沿触发 下降沿触发 • 电平触发: 高电平触发 低电平触发

外部中断输入

• 边沿触发中断

下降沿触发类型中断的请求和清除时序。 T2时刻,中断信号有下降沿产生,中断控制器向 T1 时刻,CPU执行完成中断控制器的中断服务程序, CPU 发出中断请求。 清除中断,中断信号回复到高电平。

2. 能实现中断优先级管理。即当有多个中断源同时申请中断时,CPU 能够优先响应最紧急的中断申请。

3. 能实现中断嵌套。即当CPU正在为优先级较低的中断源服务时,具 有较高优先级的中断源提出中断申请,此时中断系统应当允许较 高优先级的中断源中断较低优先级的中断源,待较高优先级的中 断处理完成后,再接着处理较低优先级的中断。这种中断服务程 序再被中断的过程称为中断嵌套。一般的中断系统应能够处理多 级中断嵌套

寄存器

寄存器

中断使能设置寄存器 使能中断 决定当前使能的是哪个中断。 该寄存器的一个位对应一个中断(共32 个中断)。置位 中断使能设置寄存器的位可以使能相应的中断。 当挂起(pending)中断的使能位置位时,处理器会根据 其优先级将其激活。使能位清零时,虽然其中断信号有效 ,可以将中断挂起,但不管其优先级如何,该中断都不能 被激活。因此被禁能的中断可以当作一个被锁存的GPIO 位。用户无需调用中断就可以直接对它进行读取和清零操 作。 1= 使能中断 0= 禁能中断

相应位设置值 注意:在电平触发方式下,清除中断标志只有在引脚处于无效状态时才可 该寄存器控制着外部中断输入信号的有效触发方式,低四位分别对应 电平触发方式下:对应位为 0 时,低电平触发外部中断;对应位为1时, 设置该寄存器允许相应的外部中断将处理器从掉电模式唤醒。实现掉 若引脚上出现了符合要求的信号, EXTINT寄存器中对应的中断标志 设置说明 信号波形 极性控制寄存器 方式控制寄存器 实现。比如设置为低电平中断,则只有在中断引脚恢复为高电平后才能清 电唤醒不需要在向量中断控制器( 高电平触发外部中断。边沿触发方式下:对应位为 外部中断 3~0。对应位为 0时,电平触发外部中断;对应位为 VIC)中使能相应的中断。该寄存器的 0时,下降沿触发外部 1时,边沿 将被置位。向该寄存器的 EINT0 ~ EINT3 位写入 1 ,可将其清零。 (EXTPOLAR) (EXTMODE) 低四位( 中断;对应位为 触发外部中断。 EXTWAKE[3:0] 1时,上升沿触发中断。 )分别对应外部中断3~0。 除中断标志。 低电平触发 中断相关寄存器 控制寄存器 高电平触发 EXTPOLAR EXTWAKE EXTMODE EXTINT 下降沿触发 上升沿触发 7:4 —— 0(低) 0(电平) 3 2 1 0 1(高) 0(电平) EXTPOLAR3 EXTWAKE3 EXTMODE3 EINT3 EXTPOLAR2 EXTWAKE2 EXTMODE2 EINT2 EXTPOLAR1 EXTWAKE1 EXTMODE1 EINT1 EXTPOLAR0 EXTWAKE0 EXTMODE0 EINT0 0(下降) 1(边沿) 1(上升) 1(边沿)

中断嵌套的处理过程

中断嵌套的处理过程在我们的生活中,常常会遇到一些复杂的问题,需要我们不断地进行思考和处理。

有时候,这些问题会像迷宫一样,将我们困在其中,让我们无法找到正确的出口。

在这种情况下,我们需要学会中断嵌套的处理过程,以避免陷入无尽的循环中。

中断嵌套的处理过程可以理解为在处理一个问题的过程中,当我们发现自己陷入了一个循环或死胡同时,及时中断当前的思考方式,尝试新的思路和方法,以打破困境,找到解决问题的办法。

我们需要明确问题的核心,并将其拆解成更小的子问题。

这样做可以帮助我们更好地理解问题的本质,并找到解决问题的方向。

然后,我们需要对每个子问题进行分析和思考,寻找可能的解决方案。

在这个过程中,我们可以尝试不同的方法和角度,以寻找最佳的解决方案。

当我们在解决一个子问题的过程中遇到了困难,或者发现自己陷入了一个死胡同时,我们需要及时中断当前的思考方式。

这时,我们可以停下来,放松一下自己的大脑,转移一下注意力。

可以进行一些与问题无关的活动,比如散步、听音乐或者与朋友交流。

这样做可以帮助我们放松心情,重新调整思维方式。

在中断的过程中,我们可以尝试思考其他的问题,或者从其他的角度思考同一个问题。

这样做可以帮助我们打破思维的局限,寻找到新的解决方案。

同时,我们也可以寻求他人的帮助和建议,听取他们的观点和意见。

这样做不仅可以为我们提供新的思路,还可以促进我们的思维活跃。

当我们在中断嵌套的处理过程后,重新回到问题的解决过程中时,我们会发现自己的思维变得更加清晰,解决问题的能力也得到了提高。

我们可以重新审视之前的思考方式和解决方案,找出其中的问题和不足之处,并进行修正和改进。

通过不断地中断和调整,我们最终可以找到解决问题的最佳路径,并成功地解决问题。

中断嵌套的处理过程是一种寻找解决问题的新思路和方法的策略。

通过中断和调整,我们可以打破思维的局限,找到解决问题的新途径。

这种处理过程需要我们保持积极的心态和灵活的思维,同时也需要我们学会倾听他人的意见和建议。

单片机嵌套中断

分析嵌套中断1.引言所谓“中断”是处理事件的一个“过程”,这一过程一般是由计算机内部或外部某件紧急事件引起并向主机发出请求处理的信号,主机在允许的情况下响应请求,暂停正在执行的程序,保存好“断点”处的现场,转去执行中断处理程序,处理完中断服务程序后自动返回原断点处,继续执行原程序,这一处理过程称为“中断”。

以AT89S52为例,中断系统含有8个中断源,共有6个中断矢量:定时/计数器0、1、2,INT0、INT1和UART。

两级中断优先级,可实现两级中断嵌套。

用户可以很方便的通过软件实现对中断的控制。

既然系统含有8个中断源,就有可能出现数个中断源同时提出中断请求的情况,这样,设计人员必须事先根据它们的轻重缓急来为每个中断源确定CPU对其的响应顺序。

然而,对于中断优先级寄存器IP来说,只可能设定两级优先,即控制位为1时对应的中断源为高级中断,反之,控制位为0时对应的为低级中断。

这样就出现一个问题:如果一个中断正在执行,如何才能让它响应同级甚至是低级中断请求呢?2.中断多优先级的扩展根据AT89S52的结构特点,其中断系统中含有两个不可寻址的“优先级生效”触发器。

一个用于指出CPU是否正在执行高优先级的中断服务程序,这个触发器为1时,系统将屏蔽所有的中断请求;另一个则指出CPU是否正在执行低优先级中断服务程序,该触发器为1时,将阻止除高优先级以外的一切中断请求。

由此可见,若要响应同级甚至是低级中断请求,必须使得该“优先级生效”触发器清零。

但该触发器又是不可寻址的,所以无法用软件直接清零。

遍历系统所提供的111条指令,只有RETI可以达到此目的。

该指令可在CPU执行该指令时,一方面清除中断响应时所置位的“优先级生效”触发器,另一方面可从当前栈顶弹出断点地址送入程序计数PC,从而返回主程序。

一个系统若有n级中断,在MCU中就有n个中断请求触发器,总称为中断请求寄存器;与之对应的有n个中断屏蔽触发器,总称为中断屏蔽寄存器。

中断嵌套的概念

中断嵌套是指中断系统正在执行一个中断服务时,有另一个优先级更高的中断提出中断请求,这时会暂时终止当前正在执行的级别较低的中断源的服务程序,去处理级别更高的中断源,待处理完毕,再返回到被中断了的中断服务程序继续执行的过程。

简介其实就是更高一级的中断的“加塞”,处理器正在执行着中断,又接受了更急的另一件“急件”,转而处理更高一级的中断的行为!中断优先级定义优先级高的中断源可以中断优先级低的中断服务程序,这就形成了中断服务程序中套着中断服务程序的情况,即形成了所谓的中断嵌套。

MCU暂停现行程序而转去响应中断请求的过程称为中断响应;为使系统能及时响应并处理发生的所有中断,系统根据引起中断事件的重要性和紧迫程序,硬件将中断源分为若干个级别,称作中断优先级。

查询优先级中断的优先级有两个:查询优先级和执行优先级。

查询优先级是datasheet或书上的默认(IP寄存器不做设置,上电复位后为00H)的优先级:外部中断0> 定时/计数器0 > 外部中断1 > 定时/计数器1 > 串行中断或int0,timer0,int1,timer1,serial port 或 INT0、T0、INT1、T1、UART或PX0>PT0>PX1>PT1>PS>......其实都是查询优级。

首先查询优先级是不可以更改和设置的。

这是一个中断优先权排队的问题,是指多个中断源同时产生中断信号时,中断仲裁器选择对哪个中断源优先处理的顺序。

而这与是否发生中断服务程序的嵌套毫不相干。

当CPU查询各个中断标志位的时候,会依照上述5个查询优先级顺序依次查询,当数个中断同时请求的时候,会优先查询到高优查询先级的中断标志位,但并不代表高查询优先级的中断可以打断已经并且正在执行的低查询优先级的中断服务。

例如:当计数器0中断和外部中断1(按查询优先级,计数器0中断>外部中断1)同时到达时,会进入计时器0的中断服务函数;但是在外部中断1的中断服务函数正在服务的情况下,这时候任何中断都是打断不了它的,包括逻辑优先级比它高的外部中断0计数器0中断。

STM32NVIC嵌套向量中断控制器函数分析

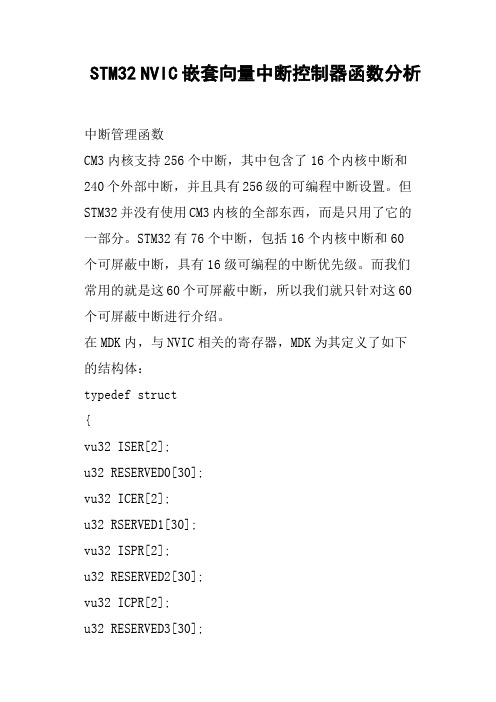

STM32 NVIC嵌套向量中断控制器函数分析中断管理函数CM3内核支持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

但STM32并没有使用CM3内核的全部东西,而是只用了它的一部分。

STM32有76个中断,包括16个内核中断和60个可屏蔽中断,具有16级可编程的中断优先级。

而我们常用的就是这60个可屏蔽中断,所以我们就只针对这60个可屏蔽中断进行介绍。

在MDK内,与NVIC相关的寄存器,MDK为其定义了如下的结构体:typedef struct{vu32 ISER[2];u32 RESERVED0[30];vu32 ICER[2];u32 RSERVED1[30];vu32 ISPR[2];u32 RESERVED2[30];vu32 ICPR[2];u32 RESERVED3[30];vu32 IABR[2];u32 RESERVED4[62];vu32 IPR[15];} NVIC_TypeDef;ISER[2]:Interrupt set enable registers中断使能寄存器组ICER[2]:interrupt clear enable registers 中断除能寄存器组ISPR[2]:interrupt set pending registers 中断挂起寄存器组ICPR[2]: interrupt clear pending registers 中断解挂寄存器组IABR[2]:interrupt active bit registers 中断激活标志寄存器组主要分析IPR[15]:interrupt priority registers 中断优先级控制寄存器组使用函数实现中断分组: 可选分组0--4MY_NVIC_PriorityGroupConfig(u8 NVIC_Group) {u32 temp,temp1;//设置中转变量temp1=(~NVIC_Group)&0x07; //取后3位temp1;AIRCR; //读取先前设置temp&=0x0000F8FF; //清空先前设置temp|=0x05FA0000; //插入密钥temp|=temp1; //分组设置赋值进SCB->;AIRCB=temp; //设置完的值赋值给中断分组寄存器}语句解读:temp1=(~NVIC_Group)&0x07; 由于所以组号取反与111 即得到分组所需寄存器值temp|=0x05FA0000;密钥使用函数实现中断优先级设置:void MY_NVIC_Init(u8 NVIC_PreemptionPriority,u8 NVIC_SubPriority,u8 NVIC_Channel,u8 NVIC_Group) {u32 temp;u8 IPRADDR=NVIC_Channel/4; //每组只能存4个得到组地址u8 IPROFFSET=NVIC_Channel%4; //得到组内偏移地址IPROFFSET=IPROFFSET*8+4; //得到确切地址MY_NVIC_PriorityGroupConfig(NVIC_Group); //设置分组temp=NVIC_Preemptionpriority;>;NVIC_Group); //设置响应优先级temp&=0xf; //取低4位if(NVIC_Channel;ISER[0]|=1;ISER[1]|=1;IPR[IPRADDR ]|=temptemp=NVIC_Preemptionpriority;>;NVIC_Group); //响应优先级在右边,根据响应位多少进行右移temp&=0xf; //得到分组值外部中断配置函数:STM32的EXTI控制器支持19个外部中断/事件请求。

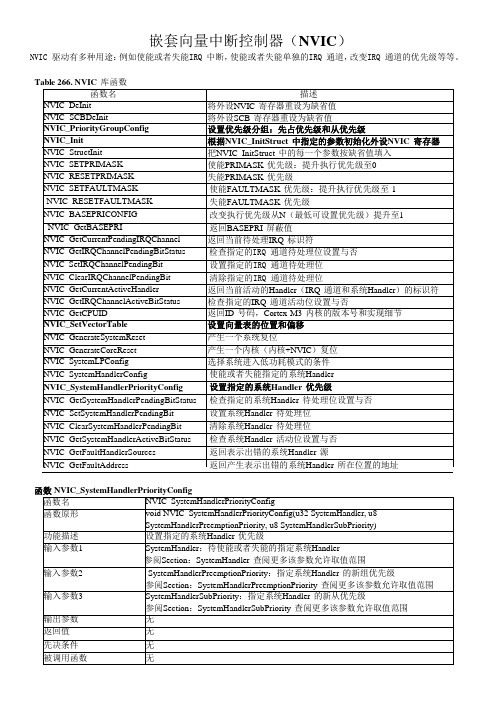

NVIC 库函数(嵌套向量中断控制器)

嵌套向量中断控制器(NVIC)NVIC 驱动有多种用途:例如使能或者失能I RQ 中断,使能或者失能单独的I RQ 通道,改变I RQ 通道的优先级等等。

Table 266. NVIC 库函数函数名描述NVIC_DeInit 将外设N VIC 寄存器重设为缺省值NVIC_SCBDeInit 将外设S CB 寄存器重设为缺省值NVIC_PriorityGroupConfig 设置优先级分组:先占优先级和从优先级NVIC_Init 根据N VIC_InitStruct 中指定的参数初始化外设N VIC 寄存器NVIC_StructInit 把N VIC_InitStruct 中的每一个参数按缺省值填入NVIC_SETPRIMASK 使能P RIMASK 优先级:提升执行优先级至0NVIC_RESETPRIMASK 失能P RIMASK 优先级NVIC_SETFAULTMASK 使能F AULTMASK 优先级:提升执行优先级至-1NVIC_RESETFAULTMASK 失能F AULTMASK 优先级NVIC_BASEPRICONFIG 改变执行优先级从N(最低可设置优先级)提升至1NVIC_GetBASEPRI 返回B ASEPRI 屏蔽值NVIC_GetCurrentPendingIRQChannel 返回当前待处理I RQ 标识符NVIC_GetIRQChannelPendingBitStatus 检查指定的I RQ 通道待处理位设置与否NVIC_SetIRQChannelPendingBit设置指定的I RQ 通道待处理位NVIC_ClearIRQChannelPendingBit清除指定的I RQ 通道待处理位NVIC_GetCurrentActiveHandler 返回当前活动的H andler(IRQ 通道和系统H andler)的标识符NVIC_GetIRQChannelActiveBitStatus 检查指定的I RQ 通道活动位设置与否NVIC_GetCPUID 返回I D 号码,Cortex-M3 内核的版本号和实现细节NVIC_SetVectorTable 设置向量表的位置和偏移NVIC_GenerateSystemReset 产生一个系统复位NVIC_GenerateCoreReset 产生一个内核(内核+NVIC)复位NVIC_SystemLPConfig 选择系统进入低功耗模式的条件NVIC_SystemHandlerConfig 使能或者失能指定的系统H andlerNVIC_SystemHandlerPriorityConfig 设置指定的系统H andler 优先级NVIC_GetSystemHandlerPendingBitStatus 检查指定的系统H andler 待处理位设置与否NVIC_SetSystemHandlerPendingBit 设置系统H andler 待处理位NVIC_ClearSystemHandlerPendingBit 清除系统H andler 待处理位NVIC_GetSystemHandlerActiveBitStatus 检查系统H andler 活动位设置与否NVIC_GetFaultHandlerSources 返回表示出错的系统H andler 源NVIC_GetFaultAddress 返回产生表示出错的系统H andler 所在位置的地址函数NVIC_SystemHandlerPriorityConfig函数名NVIC_SystemHandlerPriorityConfig函数原形void NVIC_SystemHandlerPriorityConfig(u32 SystemHandler, u8SystemHandlerPreemptionPriority, u8 SystemHandlerSubPriority) 功能描述设置指定的系统H andler 优先级输入参数1SystemHandler:待使能或者失能的指定系统H andler参阅S ection:SystemHandler 查阅更多该参数允许取值范围输入参数2SystemHandlerPreemptionPriority:指定系统H andler 的新组优先级参阅S ection:SystemHandlerPreemptionPriority 查阅更多该参数允许取值范围输入参数3SystemHandlerSubPriority:指定系统H andler 的新从优先级参阅S ection:SystemHandlerSubPriority 查阅更多该参数允许取值范围输出参数无返回值无先决条件无被调用函数无SystemHandler 类型该参数指定了待设置的系统HandlerNVIC_ VectTab 描述SystemHandler_MemoryManage 存储器管理H andlerSystemHandler_BusFault 总线错误H andlerSystemHandler_UsageFault 使用错误H andlerSystemHandler_SVCall SVCall HandlerSystemHandler_DebugMonitor 除错监控H andlerSystemHandler_PSV PSV HandlerSystemHandler_SysTick 系统滴答定时器H andler例:/* Enable the Memory Manage Handler */NVIC_SystemHandlerPriorityConfig(SystemHandler_MemoryManage, 2, 8);函数N VIC_PriorityGroupConfig函数名NVIC_PriorityGroupConfig函数原形void NVIC_PriorityGroupConfig(u32 NVIC_PriorityGroup)功能描述设置优先级分组:先占优先级和从优先级输入参数NVIC_PriorityGroup:优先级分组位长度参阅S ection:NVIC_PriorityGroup 查阅更多该参数允许取值范围输出参数无返回值无先决条件优先级分组只能设置一次被调用函数无NVIC_PriorityGroup 值,该参数设置优先级分组位长度NVIC_PriorityGroup 描述NVIC_PriorityGroup_0 先占优先级 0 位从优先级 4 位NVIC_PriorityGroup_1 先占优先级1位从优先级3位NVIC_PriorityGroup_2 先占优先级2位(值:0-3)从优先级2位(值:0-3)NVIC_PriorityGroup_3 先占优先级3位从优先级1位NVIC_PriorityGroup_4 先占优先级4位从优先级0位例:NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);函数N VIC_Init函数名NVIC_Init函数原形void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct)功能描述根据N VIC_InitStruct 中指定的参数初始化外设N VIC 寄存器输入参数NVIC_InitStruct:指向结构N VIC_InitTypeDef 的指针,包含了外设G PIO 的配置信息参阅S ection:NVIC_InitTypeDef 查阅更多该参数允许取值范围输出参数无返回值无先决条件无被调用函数无typedef struct{u8 NVIC_IRQChannel; //IRQ通道u8 NVIC_IRQChannelPreemptionPriority; //先占优先级取值u8 NVIC_IRQChannelSubPriority; //从优先级取值FunctionalState NVIC_IRQChannelCmd; //使能} NVIC_InitTypeDef;该参数设置了成员 N VIC_IRQChannel 中的先占优先级,Table. 273 列举了该参数的取值。

本科- 第六章中断优先级管理-M4

2 3

NVIC中断优先级分组

NVIC中断优先级设置

NVIC总结

2

什么是“中断”?

中 断 示 意 图

CPU 外 设 发申请 中断服务程序

发申请

中断服务程序

CPU执行程序时,由于发生了某种随机的事件(外部 或内部),引起CPU暂时中断正在运行的程序,转去执行 一段特殊的服务程序(中断服务子程序或中断处理程序), 以处理该事件,该事件处理完后又返回被中断的程序继 续执行,这一过程称为中断。 EG:吃饭时突然手机铃响…

21

2. 中断优先级设置

中断激活标志位寄存器组:IABR [8]

作用:只读,通过它可以知道当前在执行的中断是哪一个 如果对应位为1,说明该中断正在执行。

static __INLINE uint32_t NVIC_GetActive(IRQn_Type IRQn)

22

2. 中断优先级设置

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);

14

2. 中断优先级设置

分组设置好之后,怎么设置单个中断的抢占 优先级和响应优先级?

15

2. 中断优先级设置 中断设置相关寄存器

__IO uint8_t IP[240]; //中断优先级控制的寄存器组 __IO uint32_t ISER[8]; //中断使能寄存器组 __IO uint32_t ICER[8]; //中断失能寄存器组 __IO uint32_t ISPR[8]; //中断挂起寄存器组 __IO uint32_t ICPR[8]; //中断解挂寄存器组 __IO uint32_t IABR[8]; //中断激活标志位寄存器组

void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct);

第六章 中断技术-2

IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

INTA DB INT

从

SP/EN

CAS2 ~CAS0

IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

6-6 可编程中断控制器8259A

四、 8259A的工作流程 CPU

④

DB

⑥

8259A

INTA 中断类 IRR

中断被响应,则级别变最低

IR4 IR5 IR6 (级别最高) IR7 IR0 IR1 IR2 IR3 (级别最低)

4)优先级特殊循环方式: 编程指定初始队列最低优先级,其它依次排列

6-6 可编程中断控制器8259A

2、8259A中断结束方式

INTA

INT IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

6-6 可编程中断控制器8259A

一、 功能 1、单片8259A可对8个中断源控制,9片级联可扩展到64级;

2、能向CPU提供中断类型码; 3、可通过编程选择多种工作方式

IR0

8086 CPU

中断 类型码

INTR INTA

8259A

IR1

中断 控制 电路

IR7

6-6 可编程中断控制器8259A

二、内部结构

类型1入口

INT 1

MOV AX,0000H MOV DS,AX MOV BX,OFFSET INTPROC MOV [0120H ] ,BX MOV BX,SEG INTPROC MOV [0122H],BX 或用DOS功能

0000: 0120H 0121H 0122H 0123H

50 20 00 10

2、CAS2~CAS0----级联信号线 用作主片时,为输出线;用作从片时,为输入线;

微机原理第六章 输入输出和中断技术 part 2 (2)

中断处理的一般过程

6.4.3 8088/8086中断系统

8086/8088为每个中断源分配 一个中断类型码(中断向量码),其取值范围为 0~255,实际可处理56种中断。其中包括软件中断,系统占用的中断,已经开放 给用户使用的中断。所有中断又可分为两大类:内部中断和外部中断。

内部中断

6.4.2 中断处理的一般过程

1. 中断请求 2. 中断源识别及中断判优 3. 中断响应 4. 中断处理(服务) 5. 中断返回

1. 中断请求 ➢ INTR中断请求信号应保持到中断被处理为止 ➢ CPU响应中断后,中断请求信号应及时撤销

2. 中断源识别 ➢ 软件判优:由软件来安排中断源的优先级别。顺序查询中断请求,先查询的

➢ (4)能向存储器或外设发出读/写命令。 ➢ (5)能决定传送的字节数,并判断DMA传送是否结束。 ➢ (6)在DMA过程结束后,能向CPU发出DMA结束信号,将总线控制权交

还给CPU。

2. DMA控制器的工作过程 ➢ (1)当外设准备好,可以进行DMA传送时,外设向DMA控制器发出

“DMA传送请求”信号DRQ ➢ (2)DMA控制器收到请求后,向CPU发出“总线请求”信号HOLD ➢ (3)CPU在完成当前总线周期后会立即发出HLDA信号,对HOLD信号进

➢ (2)单步中断——1型中断,标志寄存器中有一位陷阱标志TF。 ➢ (3)断点中断——3型中断,专用于设置断点的指令INT 3,用于程序中设

置断点来调试程序。

➢ (4)溢出中断——4型中断,在算数指令的执行过程发出溢出 ➢ (5)用户自定义的软件中断——n型中断,执行中断指令INT n引起内部中

断。

需要时,CPU回到原来被中断的地方继续执行自己的程序。 优点: ➢ CPU效率高,实时性好 缺点 ➢ 程序编制相对较为复杂

微机原理与接口技术(楼顺天第二版)第六章习题解答

微机原理与接口技术(楼顺天第二版)习题解答第6章总线及其形成6.1答:内存储器按其工作方式的不同,可以分为随机存取存储器(简称随机存储器或RAM)和只读存储器(简称ROM)。

随机存储器。

随机存储器允许随机的按任意指定地址向内存单元存入或从该单元取出信息,对任一地址的存取时间都是相同的。

由于信息是通过电信号写入存储器的,所以断电时RAM中的信息就会消失。

计算机工作时使用的程序和数据等都存储在RAM中,如果对程序或数据进行了修改之后,应该将它存储到外存储器中,否则关机后信息将丢失。

通常所说的内存大小就是指RAM的大小,一般以KB或MB为单位。

只读存储器。

只读存储器是只能读出而不能随意写入信息的存储器。

ROM中的内容是由厂家制造时用特殊方法写入的,或者要利用特殊的写入器才能写入。

当计算机断电后,ROM 中的信息不会丢失。

当计算机重新被加电后,其中的信息保持原来的不变,仍可被读出。

ROM 适宜存放计算机启动的引导程序、启动后的检测程序、系统最基本的输入输出程序、时钟控制程序以及计算机的系统配置和磁盘参数等重要信息。

6.2 答:存储器的主要技术指标有:存储容量、读写速度、非易失性、可靠性等。

6.3答:在选择存储器芯片时应注意是否与微处理器的总线周期时序匹配。

作为一种保守的估计,在存储器芯片的手册中可以查得最小读出周期t cyc(R)(Read Cycle Time)和最小写周期t cyc(W)(Write Cycle Time)。

如果根据计算,微处理器对存储器的读写周期都比存储器芯片手册中的最小读写周期大,那么我们认为该存储器芯片是符合要求的,否则要另选速度更高的存储器芯片。

8086CPU对存储器的读写周期需要4个时钟周期(一个基本的总线周期)。

因此,作为一种保守的工程估计,存储器芯片的最小读出时间应满足如下表达式:t cyc(R)<4T-t da-t D-T其中:T为8086微处理器的时钟周期;t da为8086微处理器的地址总线延时时间;t D为各种因素引起的总线附加延时。

nvic嵌套向量中断控制器

提供中断控制器,用于总体管理异常,称之为“嵌套向量中断控制器:Nested Vectored Interrupt Controller (NVIC)”。

NVIC和处理器内核紧密相连.它提供以下特征。

[1]支持嵌套和向量中断自动保存和恢复处理器状态动态改变优先级简化的和确定的中断时间NVIC 依照优先级处理所有支持的异常,所有异常在“处理器模式”处理。

NVIC 结构支持32(IRQ[31:0]) 个离散中断,每个中断可以支持4 级离散中断优先级。

所有的中断和大多数系统异常可以配置为不同优先级。

当中断发生时,NVIC 将比较新中断与当前中断的优先级,如果新中断优先级高,则立即处理新中断。

当接受任何中断时,ISR的开始地址可从内存的向量表中取得。

不需要确定哪个中断被响应,也不要软件分配相关中断服务程序(ISR)的开始地址。

当获取中断入口地址时,NVIC 将自动保存处理状态到栈中,包括以下寄存器“PC, PSR, LR, R0~R3, R12” 的值。

在ISR结束时,NVIC 将从栈中恢复相关寄存器的值,进行正常操作,因此花费少量且确定的时间处理中断请求。

NVIC 支持末尾连锁”TailChaining”,有效处理背对背中断”back-to-back interrupts”,即无需保存和恢复当前状态从而减少在切换当前ISR时的延迟时间。

NVIC 还支持迟到“Late Arrival”,改善同时发生的ISR的效率。

当较高优先级中断请求发生在当前ISR开始执行之前(保持处理器状态和获取起始地址阶段),NVIC 将立即处理更高优先级的中断,从而提高了实时性。

Cortex ‐M3在内核水平上搭载了一颗中断控制器——嵌套向量中断控制器NVIC(Nested VectoredInterrupt Controller)。

它与内核有很深的“私交”——与内核是紧耦合的。

NVIC 提供如下的功能:z 可嵌套中断支持z 向量中断支持z 动态优先级调整支持z 中断延迟大大缩短z 中断可屏蔽。

微机原理第6章_3学分

第六章输入/输出方式与接口芯片第一节输入/输出方式第二节中断第三节可编程定时/计数器8254及其应用第四节可编程并行I/O接口芯片8255A及其应用第五节可编程中断控制器8259及其应用第一节输入/输出方式●教学目标介绍I/O 接口的基本概念介绍I/O端口的编址方式介绍CPU与外设间的数据传送关系●学习要求掌握I/O接口的基本功能,了解接口的一般结构熟悉I/O端口的编址方式,了解IN/OUT指令的执行过程掌握微机与外设的各种传送方式,了解DMA传送过程一、I/O接口1)I/O接口的基本概念I/O接口是连接CPU与外设的逻辑控制部件,它主要在CPU与外设间起着传输状态与命令信息,实现数据的缓冲、数据格式转换等作用。

它的主要功能有:选择外设对外设进行控制和监视进行数据寄存和缓冲进行数据格式转换进行信号电平转换I/O接口的分类并行I/O接口和串行I/O接口可编程接口和不可编程接口专用接口和通用接口2)I/O接口的基本结构主要包含有数据端口、状态端口和控制端口数据端口用于存放数据信息,包括数据输入寄存器和数据输出寄存器,主要作用是协调CPU和外设之间的数据传输速度。

控制端口用于存放控制信息,控制信息是CPU通过接口传送给外设的,其主要作用是控制外设工作,如控制输入输出装置的启/停等。

状态端口用于存放状态信息,即反映外设当前工作的状态信息,CPU可通过读取这些信息,了解外设当前的工作情况。

3)I/O端口的寻址方式在一个微机系统中既有存储单元地址又有I/O端口地址,根据两者地址的不同安排可分为以下两种寻址方式。

存储器统一编址在这种方式中,把I/O端口作为存储器的一个单元来对待,即每个端口占用一个存储单元地址。

此时,对I/O端口操作可以使用全部的存储器指令,而不必另设专门的I/O指令。

由于该方式是将I/O地址映射到了存储器地址空间,所以也称为存储器映像方式。

I/O端口独立编址在这种方式下,I/O端口与存储器各自独立编址,这样存储器地址和I/O端口地址可以重叠。

嵌套向量中断控制器(NVIC)详解

嵌套向量中断控制器(NVIC)详解引⾔在平时的⼯作中,我们经常会遇到这样的情况:有⼈来找你做⼀些事情,⽽且这些事情要⽐⼿头的⼯作更重要。

那现在就需要停下⼿中的⼯作,先去完成突然到来的这部分⼯作。

这样的情况也类似于图论中的关键路径中,突然在当前事件之前插⼊了⼀个新的事件,那我们不得不先去完成之前的那个任务,才能继续完成后⾯的⼯作。

上述情况是⾮常常见的,那在STM32中,我们如果遇到了⽐当前任务更紧急的事情需要去处理,我们应该怎么办呢?这个时候,我们需要通过中断来完成这样的任务。

在现实⽣活中,突然出现的任务⼀定有轻重缓急之分。

如果同时出现许多的临时任务,我们⼀定会⾸先评估他们谁更需要先被处理掉,然后再依次进⾏处理。

在STM32中,我们也需要这样的功能,多个中断来临的时候,我们需要⾸先判断这个中断紧不紧急,然后再考虑处理的先后顺序。

那我们是由什么来控制这样的顺序的呢?毫⽆疑问,这就是通过嵌套向量中断控制器(NVIC)完成的。

NVIC简介CM3内核⽀持256个中断,包括16个内核中断和250个外部中断,同时具有256级的可编程中断设置。

⽽STM32只使⽤了⼀部分。

STM32拥有84个中断,包括16个内核中断和68个可屏蔽中断(STM32F107系列才使⽤了68个可屏蔽中断),还拥有16级可编程的中断优先级。

STM32F103系列只使⽤了60个可屏蔽中断。

STM32中控制中断优先级的寄存器组是IP[240]。

是由240个8bit的寄存器组成的。

⽽STM32F103只⽤了前六⼗个(0 ~ 59)。

在STM32F103系列单⽚机中,这8bit也没有全部使⽤,⽽是只使⽤了其⾼四位(4 ~ 7位)。

下图是中断分组的分配情况。

优先级分组抢占优先级响应优先级⾼四位描述00级0 ~ 15级0bit⽤于抢占优先级4bit⽤于响应优先级10 ~ 1级0 ~ 7级1bit⽤于抢占优先级3bit⽤于响应优先级20 ~ 3级0 ~ 3级2bit⽤于抢占优先级2bit⽤于响应优先级30 ~ 7级0 ~ 1级3bit⽤于抢占优先级1bit⽤于响应优先级40 ~ 15级0级4bit⽤于抢占优先级0bit⽤于响应优先级响应优先级⼜称为⼦优先级。

中断优先级以及中断嵌套

中断优先级以及中断嵌套

中断优先级有两种,叫默认优先级和嵌套优先级,假如A,B两个中断,如果A比B 嵌套优先级(通过优先级寄存器设置)更高,就不需要看默认优先级了,A、B同时发生中断时A中断先执行而B后执行,而且B中断执行之间A可以抢断(嵌套)B的中断服务程序,B不可以抢断A;而如果嵌套优先级一样的话,只是A默认优先级比B更高(不需要设置),只能支持A、B同时中断时A先执行,而A不能嵌套B了,有的CPU甚至硬件上不支持嵌套,需要模拟嵌套,这个跟CPU平台有关。

关于嵌套的寄存器备份是这样进行的,进入一级中断便进行一次全套寄存器的压栈操作,压栈是把寄存器里面的值保存到栈区(属于内存区域,而并非你说的后背状态寄存器SPSR,其实后背状态寄存器SPSR也要一起压入栈区),每压入一个寄存器,SP会移动相应的距离,不会重叠;每退出一级中断便进行一次全套寄存器的出栈操作,这样就实现了保护现场和恢复现场。

可以通过编译器反汇编码窗口查看中断压栈、出栈的实现。

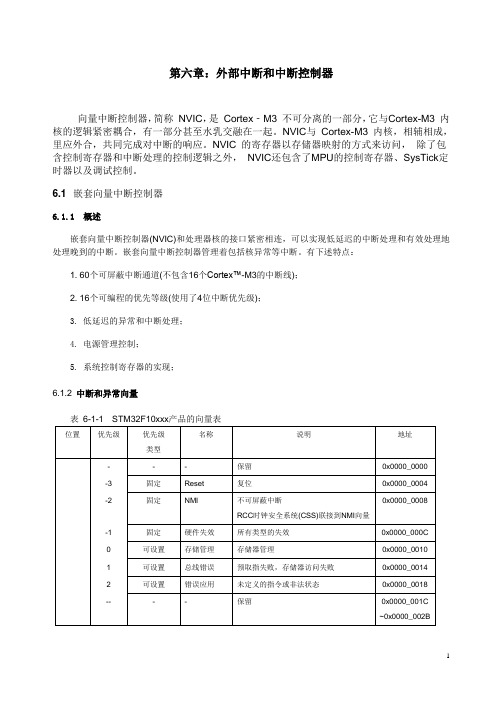

6.外部中断和中断向量

第六章:外部中断和中断控制器向量中断控制器,简称NVIC,是Cortex‐M3 不可分离的一部分,它与Cortex-M3 内核的逻辑紧密耦合,有一部分甚至水乳交融在一起。

NVIC与Cortex-M3 内核,相辅相成,里应外合,共同完成对中断的响应。

NVIC 的寄存器以存储器映射的方式来访问,除了包含控制寄存器和中断处理的控制逻辑之外,NVIC还包含了MPU的控制寄存器、SysTick定时器以及调试控制。

6.1嵌套向量中断控制器6.1.1 概述嵌套向量中断控制器(NVIC)和处理器核的接口紧密相连,可以实现低延迟的中断处理和有效处理地处理晚到的中断。

嵌套向量中断控制器管理着包括核异常等中断。

有下述特点:1. 60个可屏蔽中断通道(不包含16个Cortex™-M3的中断线);2. 16个可编程的优先等级(使用了4位中断优先级);3. 低延迟的异常和中断处理;4. 电源管理控制;5. 系统控制寄存器的实现;6.1.2中断和异常向量6.1.3 中断优先级介绍STM32(Cortex-M3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪一个。

既然每个中断源都需要被指定这两种优先级,就需要有相应的寄存器位记录每个中断的优先级;在Cortex-M3中定义了8个比特位用于设置中断源的优先级,这8个比特位可以有8种分配方式,如下:所有8位用于指定响应优先级最高1位用于指定抢占式优先级,最低7位用于指定响应优先级最高2位用于指定抢占式优先级,最低6位用于指定响应优先级最高3位用于指定抢占式优先级,最低5位用于指定响应优先级最高4位用于指定抢占式优先级,最低4位用于指定响应优先级最高5位用于指定抢占式优先级,最低3位用于指定响应优先级最高6位用于指定抢占式优先级,最低2位用于指定响应优先级最高7位用于指定抢占式优先级,最低1位用于指定响应优先级这就是优先级分组的概念。

第6章 NVIC[11页]

![第6章 NVIC[11页]](https://img.taocdn.com/s3/m/7c01298f0975f46527d3e1fd.png)

//配置控制寄存器

vu32 SystemPriority[3];

//系统处理优先级寄存器

vu32 SysHandlerCtrl;

//系统处理控制和状态寄存器

vu32 ConfigFaultStatus;

//配置出错状态寄存器

vu32 HardFaultStatus;

//硬件出错状态寄存器

vu32 DebugFaultStatus;

第六章 NVIC

嵌套向量中断控制器 (NVIC)

STM32嵌套向量中断控制器(NVIC)主要特

性如下:

• 具有43 个可屏蔽中断通道(不包含16 个 Cortex-M3 的中断线)。

• 具有16 个可编程的优先等级。 • 可实现低延迟的异常和中断处理。 • 具有电源管理控制。 • 系统控制寄存器的实现。

NVIC寄存器结构

typedef struct

{

vu32 Enable[2];

//中断置位使能寄存器

u32 RESERVED0[30];

vu32 Disable[2];

//中断清除使能寄存器

u32 RSERVED1[30];

vu32 Set[2];

//中断置位挂起寄存器

u32 RESERVED2[30];

{

vu32 CPUID;

//CPUID基寄存器

vu32 IRQControlState;

//中断控制状态寄存器

vu32 ExceptionTableOffset;

//向量表偏移寄存器

vu32 AIRC;

//应用中断/复位控制寄存器

vu32 SysCtrl;

//系统控制寄存器

vu32 ConfigCtrl;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中断信号

下降沿触发T1T2源自外部中断输入• 电平触发中断

低电平触发类型中断的请求和清除时序。 T3时刻, T2 时刻,中断控制器确认中断信号是低电平后,将向 CPU执行完成中断控制器的中断服务程序, T1时刻,中断信号开始由高电平转为低电平。 CUP发出中断请求。 清除中断,中断信号回复到高电平。

中断的具体行为

• 一个中断输入被认为有效后,就会被挂起。即使一段时间 后该中断的中断源取消了此次请求,挂起状态仍然会被保 存,直到此中断成为系统中最高的优先级时,就会得到处 理器的响应 • 但是,如果挂起中断在得到响应之前,其挂起状态被清除 了(通过修改PRIMASK 或FAULTMASK 寄存器),则此 次中断请求无效,中断的挂起状态在NVIC 的寄存器中是 可写的,用户通过修改相关寄存器可挂起一个中断,也可 清除一个中断。

中断源

每一个外围设备可以有一条或几条中断线连接到向量中断 控制器。多个中断源也可以共用一条中断线。除过ARM内 核指定的某些标准外,哪一条中断线连接到哪一个中断源 是无关紧要的或没有优先级的

寄存器

每个外部中断都在NVIC的下列寄存器中“挂号”: 使能与除能寄存器 挂起与“解挂”寄存器 优先级寄存器 活动状态寄存器 另外,下列寄存器也对中断处理有重大影响 异常掩蔽寄存器(PRIMASK, FAULTMASK以及 BASEPRI) 向量表偏移量寄存器 软件触发中断寄存器 优先级分组位段

3 2 1

中断信号

低电平触发

T1 T2

T3

外部中断输入

• 外部中断源

LPC1700系列微控制器几乎所有的外设部件都可以 产生中断。其中外部中断含有4个独立的中断输入。

外部中断源34 (EINT0) 嵌套 向量 中断 控制 器 (NVIC)

外部中断源35 (EINT1) 外部中断源36 (EINT2) 外部中断源37 (EINT3)

中断挂起清除寄存器 清除挂起中断 决定当前正在挂起哪个中断 该寄存器的一个位对应一个中断(共32 个中断)。置位 中断挂起清除寄存器的位可以让相应的挂起中断变为不激 活状态。 写中断挂起清除寄存器操作对那些已经激活的中断没有影 响,除非这些中断也正处于挂起状态。

外部中断输入

概述

LPC1700系列ARM具有4路外部中断,可以设置为2种类型: 边沿触发: 上升沿触发 下降沿触发 • 电平触发: 高电平触发 低电平触发

外部中断输入

• 边沿触发中断

下降沿触发类型中断的请求和清除时序。 T2时刻,中断信号有下降沿产生,中断控制器向 T1 时刻,CPU执行完成中断控制器的中断服务程序, CPU 发出中断请求。 清除中断,中断信号回复到高电平。

第三,CPU内部应处在开中断(允许中断)状态。

第四,CPU至少要在当前指令执行完成时才可能响应中断。

异常/中断

系统异常是Cortex-M3内核自带的一些异常,比如复位、 总线Fault和SysTick等等 外设中断是指制造CPU的厂家加入的,比如串口、定时器 中断等等 异常和中断都可以“中断”正常执行的代码流 区别在于: 异常是Cortex-M3内核产生的“中断”信号,在执行指令 或访问存储器时产生的,对Cortex-M3 内核来说是“同 步”的 而中断是Cortex-M3内核外部(片上外设或外部中断信号 )产生的“中断”信号中断请求信号一般来自内核的外部 ——片上外设或外扩的设备等,对Cortex-M3 内核来说 是“异步”的。

中断的具体行为

当某中断的服务例程开始执行时,就称此中断进入了“活 跃”状态,并且其悬起位会被硬件自动清除。在一个中断 活跃后,直到其服务例程执行完毕,并且返回(亦称为中 断退出)后,才能对该中断的新请求予以响应(单实例) 。当然,新请求在得到响应时,亦是由硬件自动清零其悬 起标志位。中断服务例程也可以在执行过程中把自己对应 的中断重新悬起

相应位设置值 注意:在电平触发方式下,清除中断标志只有在引脚处于无效状态时才可 该寄存器控制着外部中断输入信号的有效触发方式,低四位分别对应 电平触发方式下:对应位为 0 时,低电平触发外部中断;对应位为1时, 设置该寄存器允许相应的外部中断将处理器从掉电模式唤醒。实现掉 若引脚上出现了符合要求的信号, EXTINT寄存器中对应的中断标志 设置说明 信号波形 极性控制寄存器 方式控制寄存器 实现。比如设置为低电平中断,则只有在中断引脚恢复为高电平后才能清 电唤醒不需要在向量中断控制器( 高电平触发外部中断。边沿触发方式下:对应位为 外部中断 3~0。对应位为 0时,电平触发外部中断;对应位为 VIC)中使能相应的中断。该寄存器的 0时,下降沿触发外部 1时,边沿 将被置位。向该寄存器的 EINT0 ~ EINT3 位写入 1 ,可将其清零。 (EXTPOLAR) (EXTMODE) 低四位( 中断;对应位为 触发外部中断。 EXTWAKE[3:0] 1时,上升沿触发中断。 )分别对应外部中断3~0。 除中断标志。 低电平触发 中断相关寄存器 控制寄存器 高电平触发 EXTPOLAR EXTWAKE EXTMODE EXTINT 下降沿触发 上升沿触发 7:4 —— 0(低) 0(电平) 3 2 1 0 1(高) 0(电平) EXTPOLAR3 EXTWAKE3 EXTMODE3 EINT3 EXTPOLAR2 EXTWAKE2 EXTMODE2 EINT2 EXTPOLAR1 EXTWAKE1 EXTMODE1 EINT1 EXTPOLAR0 EXTWAKE0 EXTMODE0 EINT0 0(下降) 1(边沿) 1(上升) 1(边沿)

异常类型

Cortex-M3 在内核水平上搭载了一个异常响应系统,支 持11 种系统异常和240 个外部中断输入,如表2.9 所列 。其中,编号1~15 对应的是系统异常,大于等于16 的则 全是外部中断。除了个别异常有固定的优先级外,其它异 常的优先级都是可编程的。系统异常和外部中断通过不同 的寄存器组进行控制。

嵌套向量中断

中断的概念

• CPU正在执行程序时,单片机外部或内部发生的某一事件 ,请求CPU迅速去处理。 • CPU暂时中止当前的工作,转到中断服务处理程序处理所 发生的事件。 • 处理完该事件后,再回到原来被中止的地方,继续原来的 工作,这称为中断。 • CPU处理事件的过程,称为CPU的中断响应过程。

1 2 3 2 1 4 3

管脚 连接控制

外部中断 极性控制

EXTPOLAR

外部中断 方式控制

EXTMODE

中断标志

EXTINT

CPU 其它部件

PINSELx

• 寄存器汇总

中断信号波形与设置方式 外部中断标志寄存器(EXTWAKE) (EXTINT) :: : 外部中断唤醒寄存器 外部中断方式控制寄存器 外部中断极性控制寄存器 (EXTMODE) (EXTPOLAR) :

对事件的整个处理过程,称为中断处理(或中断服务,ISR)。

主程序

执行主 程序 中断请求 中断响应

执行 中断 处理 程序

中断返回

继续执行 主程序

中断方式优点:大大地提高了CPU的工作效率。

能够实现中断处理功能的部件称为中断系统

中断系统需要解决的问题:

1. 能实现中断响应、中断处理(服务)、中断返回和中断屏蔽。这 是中断系统最基本的功能。

中断的具体行为

• 如果在执行某中断的服务函数期间,中断源一直保持请求 信号有效,该中断就会在其服务程序返回后再次被挂起,

中断的具体行为

同样,若中断在服务例程执行过程中释放了请求,但在服 务例程返回前又发出了新的请求信号,则处理器会记住此 动作,将再次挂起该中断

中断的具体行为

如果中断在得到响应之前,其请求信号以脉冲的形式出现 若干次,则被视为只有一次请求

2. 能实现中断优先级管理。即当有多个中断源同时申请中断时,CPU 能够优先响应最紧急的中断申请。

3. 能实现中断嵌套。即当CPU正在为优先级较低的中断源服务时,具 有较高优先级的中断源提出中断申请,此时中断系统应当允许较 高优先级的中断源中断较低优先级的中断源,待较高优先级的中 断处理完成后,再接着处理较低优先级的中断。这种中断服务程 序再被中断的过程称为中断嵌套。一般的中断系统应能够处理多 级中断嵌套

寄存器

寄存器

中断使能设置寄存器 使能中断 决定当前使能的是哪个中断。 该寄存器的一个位对应一个中断(共32 个中断)。置位 中断使能设置寄存器的位可以使能相应的中断。 当挂起(pending)中断的使能位置位时,处理器会根据 其优先级将其激活。使能位清零时,虽然其中断信号有效 ,可以将中断挂起,但不管其优先级如何,该中断都不能 被激活。因此被禁能的中断可以当作一个被锁存的GPIO 位。用户无需调用中断就可以直接对它进行读取和清零操 作。 1= 使能中断 0= 禁能中断

NVIC 功能

2.向量中断支持 当开始响应一个中断后,Cortex-M3 会自动定位一张向 量表,根据中断号从表中找出相应中断的入口地址,然后 跳转过去执行 3.动态优先级调整支持 优先级在中断运行期间可以通过软件进行修改。在中断服 务例程执行完成前,中断是被锁定的,无法进行深度激活 ,避免了意外重入的风险。 4.中断延迟大大缩短 Cortex-M3 为了缩短中断延迟,引入了多个新特性。包 括中断现场的自动保护与恢复,“咬尾中断”和“晚到中 断”机制的支持 5 中断可屏蔽 通过设置BASEPRI、PRIMASK 和FAULTMASK 等寄 存器, 既可屏蔽优先级低于某个阈值的中断,也可以屏 蔽所有中断,保证时间关键的任务能在最后期限前完成。

系统异常是Cortex-M3 内核支持的基本异常,与具体的 芯片无关,而外部中断则是与芯片相关的,芯片厂商会根 据需要和用途设计中断源数目(1-240)和优先级的位数 。LPC1700 系列Cortex-M3 支持35 个外部中断和32 个 中断优先级。