基于FPGA的IP核8051上实现TCPIP的设计

基于8051单片机IP软核的优化设计及应用研究

speed,the program flow concept is

introduced and

instructions

applied.This refer to arithmetic

and log沁instructions,data

transfer

and

bit addressable instructions,To prove the possibility simulator. into FPGA

专用集成电路asicapplicationspecificintegratedcircuit的设计成本不断降低在功能上现代的集成电路已能实现单片电子系统socsystemonachip的功能810edaelectronicdesignautomation技术作为现代电子设计技术的核心它依赖功能强大的计算机在eda工具软件平台上对以硬件描述语言hdlhardwaredescriptionlanguage为系统逻辑描述手段完成的设计文件自动地完成逻辑编译逻辑化简逻辑分割逻辑综合结构综合布局布线以及逻辑优化和仿真测试直到实现既定的电子线路系统功能

and

SoC

based

on

8 bit

MCU

Key words:MCS一8051,SOC,FPGA,IP core

JV

西华大学硕七学位论文

申明

本人申明所呈交的学术论文是本人在导师指导下进行的研究工作及取得 的研究成果。除了文中特别加以标注和致谢的地方外,论文中不包含其他人已 经发表或撰写过的研究成果,也不包含为获得西华大学或其他教育机构的学位 或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献均已在 论文中作了明确的说明并表示谢意。 本学位论文成果是本人在西华大学读书期问在导师指导下取得的,论文成 果归西华大学所有,特此申明。

基于FPGA和8051单片机IP核的多功能频率计的设计与实现

基于FPGA和8051单片机IP核的多功能频率计的

设计与实现

频率是电信号中重要的物理量,在电子、通信系统中,信号的频率稳定度决定了整个系统的性能,准确测量信号的频率是系统设计的重要内容。

单片机广泛地应用于电子系统设计,其性价比高,大量的外围接口电路,使基于单片机的电子系统设计方便,周期缩短。

然而,单片机的串行工作特点决定了它的低速性和程序跑飞,另外还存在抗干扰能力不强等缺点。

EDA(Electronic Design AutomaTIon)技术以计算机为工具,在Quartus II软件平台上,对以硬件描述语言Verilog HDL/VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、综合及优化、逻辑仿真,直至对特定目标芯片的适配、编译、逻辑映射和编程下载等工作,FPGA是纯硬件结构,具有较强的抗干扰能力。

文中在FPGA芯片中嵌入MC8051 IP Core,作为控制核心,利用Verilog HDL语言进行编程,设计了以MC8051 IPCore为核心的控制模块、计数模块、锁存模块和LCD显示模块等模块电路,采用等精度测量法,实现了频率的自动测量,测量范围为0.1 Hz~50 MHz,测量误差小于0.01%。

攀枝花学院学生创新实验项目结题报告书(基于FPGA的8051单片机IP核设计及应用)

攀枝花学院学生创新实验项目结题报告书项目名称:基于FPGA的8051单片机IP核设计及应用承接单位:电气信息工程学院负责人:郭伟小组成员:刘建平、石磊指导教师:郝小江、范方灵、明立娟完成时间:2012年3月3日-----2012年11月10日教务处制二〇一二年十一月一、课题名称:基于FPGA的8051单片机IP核设计及应用二、课题提出的背景:近年来,随着微电子学和计算机科学的迅速发展,给EDA行业带来了巨大的挑战和变革。

电子设计自动化(EDA)是以计算机和微电子技术为先导,汇集了计算机图形学、拓扑学、逻辑学、微电子工艺与结构学和计算数学等多种计算机应用学科最新成果的先进技术。

片上系统SOC(System on a Chip)以其高集成度、高性能、低功耗、低成本等诸多优点受到越来越多的关注,系统级芯片SOC已成为集成电路发展的主流,基于FPGA的SOPC设计技术是当前电子系统设计领域最前沿的技术之一。

而IP正是实现SOC的核心技术,是SOC设计的关键。

在SOC设计中几乎都会将微处理器、存储单元等通用IP模块集成到FPGA中构成可配置的SOC 芯片。

基于IP核复用技术的设计方法能大大提高SOC开发效率,降低设计成本,从而逐渐成为一种主流设计方法。

在芯片设计中大量复用知识产权模块IP,可以使IC设计者把精力集中在更高层次上的设计上,从而加快芯片的开发速度。

三、课题研究的目的和意义:美国Intel公司生产的MCS-51系列单片机,由于其具有集成度高、处理功能强、可靠性高、系统机构简单、价格低廉等优点,在我国已经得到非常广泛的应用。

但单片机自身也有着许多固有缺点,一定程度上限制了它的使用,主要表现在:低速、PC的“跑飞”、开发周期长。

设计具有自主知识产权的8051软核成为了当前SOPC设计的一项重要课题,可以大大方便今后的EDA设计。

因此,如何克服单片机的固有缺点,设计开发出指令系统与8051单片机的指令系统完全兼容,并且能够应用于FPGA的8051IP核具有非常深远的意义。

TCP_IP通信技术在XilinxFPGA上的实现

TCP/IP通信技术在Xilinx FPGA上的实现鲍兴川(国网自动化研究院/南京南瑞集团公司,江苏 南京 210003)摘 要:研究了TCP/IP通信协议栈在Xilinx 公司现场可编程门阵列FPGA上的实现,介绍了其软硬件的系统组成和原理,提出一种不需操作系统的TCP/IP协议栈的高效工作模式,并在Spartan 3 FPGA上移植成功,通过建立测试平台进行测试,证明其工作方式具有更高的通信性能,为水利水电自动化系统设备开发提供新的思路。

关键词:TCP/IP;通信技术;FPGA;Spartan 3E;IPCore;MicroBlaze中图分类号:TN92 文献标识码:A 文章编号:1672-3279(2007)02-0020-03第2期 2007年6月水利水文自动化Automation in Water Resources and HydrologyNO.2 Jun.,20070 前言由于IEC 61850已成为电力自动化系统及变电站通信网络唯一的国际标准,其成为国家标准已是大势所趋,水利水电行业的自动化及通信网络系统标准必将参照或照搬其标准。

IEC 61850推荐在变电站层与间隔层、间隔层与过程层之间均采用以太网通信技术,以保证高速可靠的数据传输。

这样以太网和其支撑软件TCP/IP 通信协议栈被大量应用在水利水电自动化和通信系统产品中也将成为必然,目前国内主要的水利电力产品开发厂家已或将开始着手研发符合IEC 61850的带双以太网接口的新型水利电力自动化产品。

目前美国Xilinx 公司的现场可编程门阵列FPGA 和32位CPU 技术已在水利水电自动化产品中得到广泛应用,但各设备之间大量使用的仍然是RS -485或CAN -bus 通信总线搭建的通信网络,本文从实际出发,以已在Xilinx FPGA 的MicroBlaze IPCore (俗称软32位CPU )搭建的在片系统(System -on -Chip )之上实现的TCP/IP 通信协议栈LWIP 为例进行说明,详细介绍其软硬件的系统组成和原理,阐述了FPGA 的片上系统配置,和其驱动层和协议栈层软件的结构,并给出部分关键源码,使其能部分符合IEC 61850标准,使水利水电行业很快涌现出更多的TCP/IP 通信协议栈符合IEC 61850标准的自动化产品,并在实际水利水电工程中得到应用。

基于FPGA的多路采集与TCPIP传输系统设计

研制开发国家自然科学基金项目(61771410);国防科工局2014404B 002);中国空气动力研究-),男,硕士,主要研究方向为信息图1 系统总体结构具体地,16路模拟信号并行进入采集系统的信号调理模块,经过调理后的信号分成两组(每组入ADC 中进行转换,再由最后由FPGA 控制W5500PC 机。

图2 信号采集部分的结构数据传输系统设计UDP、IPv4、ICMP、ARP、IGMP10/100M以太网通信。

FPGA基内部的寄存器区和内存进行读用寄存器区和8个Socket_n )寄存器区组成。

通用寄存器区用于配置和源MAC地址等。

Socket_n端口号、模式、配置命令等,的状态和中断信息。

W5500的内存大,分为接收内存和发送内存,各占16 kB,图3 主状态机状态转移经过复位、寄存器区配置、建立TCP连接后,用户可由上位机下发采集配置信息,如低通滤波开关、通道选择和放大器增益等。

FPGA从W5500接收缓存读取用户配置信息,然后进行命令解析(将配置信息下发到信号采集部分),并启动采集。

16路数字信号并行进入FPGA,由异步FIFO转换为串行数据流写入W5500的发送缓冲。

待采集结束后,返回接收数据状态,继续等待一下组命令。

若TCP连接发生中断、超时等异常情况,FPGA将重启W5500。

TCP连接建立、数据接收和数据发送,是整个W5500控制状态机的核心。

选取机程序进行数据通信的端口。

(a)TCP连接建立的FPGA向Socke_0的配置寄“OPEN”和“LISTEN”命令,分别将初始化和配置为TCP服务器,通过检查状态寄存器Sn_SR[7:0],判断命令是否生效。

配置完成的务器将一直监听信道,等待客户端的连接请求。

(b)TCP数据接收的流程如图断寄存器Sn_IR[7:0]提供了Sn_IR[2]为“1”时,表示(a) TCP建立流程(b) 接收流程(c) 发送流程图 TCP建立和数据接收发送流程图5 TCP流量统计结果4.5 V,上位机显示采集信号的时域6所示,所采信号的增益精度满足本文设计了一种基于FPGA的多路采集与TCP/IPFPGA+W5500架构,可以实现基于硬协议通信,并详细介绍了系统的信号采集数据传输部分的设计方法。

基于FPGA的万兆以太网TCPIP协议处理架构

稿件编号:201909019

Engine)即 TCP/IP 卸 载 引 擎 ,TOE 技 术 采 用 硬 件 处

理 TCP/IP 协议,原本在网络协议栈中进行的 TCP 分

段、TCP 连接管理、检验和计算和检验等操作转移到

FPGA 中进行,以极小的硬件电路作为代价,大幅度

网 子 系 统 IP 核 将 万 兆 网 络 数 据 流 转 为 64bit AXI4-

1 系统设计

协议信息交于控制平面,由控制平面发出对各种网

CPU 处理高速网路数据流的问题。

Stream 数据流,通过包头检测与验证模块提取各层

CPU 资源占用率仅为 10%,光口有效数据吞吐率可达 9.034 Gbps。

关键词:万兆以太网;FPGA;TCP/IP 协议栈;TOE

中图分类号:TN30.14022/j.issn1674-6236.2020.09.018

文章编号:1674-6236(2020)09-0081-07

IP 协议处理架构。通过在处理架构中划分控制平面和数据平面,使各个逻辑电路模块的协同操

作,并结合高速的 I/O 处理和存储器处理,利用硬件实现了完整的 TCP/IP 协议栈,有效的解决了服

务器处理万兆网络流量的瓶颈问题。将所提出的架构应用于实际万兆以太网 TCP/IP 卸载板卡中,

其协议支持 ARP、ICMP、UDP、TCP 等,并且时延最低可达 0.288 μs,文件传输速率可达 933 MB/s,

作者简介:吴 惑(1995—),男,浙江宁波人,硕士研究生。研究方向:通信与信息系统,高数数字系统设计,网

络安全,网络协议。

- 81 -

《电子设计工程》2020 年第 9 期

基于FPGA的TCP设计与实现

• 168•5 测试及分析5.1 测试项目测试按照硬件电路的两部分即光伏供电模块和自动调光LED 驱动模块分别测试。

首先测试LED 驱动部分,LED 负载为20颗0.06W 的LED 并联,单颗LED 的管压降约为3V ,总电流限制在400mA 以内,即单颗LED 最大电流限制在20mA 以内,测试环境光照强度为0lux 。

取一独立光源模拟环境光照强度,设置总光照强度保持在396lux 到404lux 之间。

设Vcon 为DAC 模块输出电压,室内总光照强度设定值为SDZ 。

5.2 实际测试结果及误差分析表4.1 参数测试结果1序号环境光照强度/luxDAC输出电压/V恒流源输出电流值/mA16 1.69359250 1.53193133 1.1524543100.398354000.214464500.13277750本模块测试使用GY-30光照度传感器模块、51单片机控制电路、恒流源驱动电路。

LED 负载为20颗0.06W 的LED 并联。

通过传感器检测,根据室内光照度自动调节LED 灯串的亮度。

表4.1、4.2分别为总光照强度设置在400lux 与450lux 时测得的控制电压量和输出电流值。

系统根据不同的室内照度,调节DAC 输出电压从而改变LED 光亮度。

由于室内照度计探头位置放置和光照度传感器有一定的偏差,故数据存在一定的误差。

即环境光照强度小于设定值时,根据计算公式计算DAC 输出电压与万用表显示电压基本吻合;环境光照强度大于设定值时,无论室内光照度值是多少,DAC 输出电压均为零,LED 不照明。

将实验数据与理论值进行比较,考虑一定误差的情况下,基本吻合。

表4.2 参数测试结果2序号环境光照强度/luxDAC输出电压/V恒流源输出电流值/mA16 1.9404250 1.713633133 1.3628943100.612754000.214464500.132777506 结论设计的光伏供电自动调光LED 驱动器,采用太阳能电池供电,能根据环境光照强度自动调节输出光照强度,使环境中的总体光照强度稳定在合适的光照强度下。

tcp,ip协议,fpga

竭诚为您提供优质文档/双击可除tcp,ip协议,fpga篇一:tcp/ip协议的Fpga实现tcp/ip协议的Fpga实现基于Fpga实现tcp/ip协议,实现自动收发包,1g以太网速度达到900mbps。

有需求者,请联系qq:1014003606篇二:工业以太网协议栈Fpgaip核的实现冉冉红日的博客工业以太网协议栈Fpgaip核的实现随着物联网的广泛应用,在嵌入式系统中,越来越多的设备、传感器使用工业以太网作为通信媒介,因为工业以太网有着速度与安全可靠双重优势。

在较高端设备中,由于存在如dsp、aRm之类的处理器,指令代码运行处理速度很快,再有os进行管理,此时将以太网网卡芯片驱动程序和协议栈加入进来,比较简单方便,易于设备管理和功能更改,这种方案已经应用的非常成熟了。

在某些低端设备中,只有单片机作为处理器,如果还是像上述那样实现以太网的话,单片机的负荷势必会大大增加,对于与单片机相连的设备的实时性控制就会大大降低。

因此,在要加入以太网通信的设备中选用单片机作为处理器不是一种好方案。

除了单片机、dsp、aRm外,还有一种处理器也被广泛应用,那就是Fpga。

现在Fpga的功能越来越多,片内资源也越来越多。

像新出的alteRaFpga内部就已有aRm硬核,在alteRa的所有系列中都能实现软核cpu,此cpu的运行速度相比一般的单片机来说还要更快些。

但如果用它来管理tcp/ip协议栈,我觉得也就会像单片机一样,负载过重,就像让一个10岁的小孩挑50斤的担子一样。

此外,我个人觉得,软核cpu毕竟没有单片机稳定,在Fpga系统中,让软核cpu只做管理就好了,而像以太网协议栈的这样独立性强,又比较复杂的工作就由一个ip核来实现。

虽然这样的ip核实现起来不容易,但对于实时性要求高、数据传输速度要求高、稳定性要求高的设备,采用这种方案是非常好的。

因此,我想根据嵌入式设备的特点,简化tcp/ip协议栈的内容,实现嵌入式设备需要的功能,而不需要的就剔除掉。

在嵌入FPGA的IP核8051上实现TCP/IP的设计

这种 方法 对程 序存储 器不 再 做 内外之 分 ,因 为F G P A内部 存 储 容 量 已经 能 够 满 足要 求 . 同时 将程 序存 储 器 的容量 扩 大 了一倍 ( 为8 B ,以 变 K1 满足 大程 序 的容量 需求 ;为 了让 8 5 更为 强 大且 01 更具 有通用 性 ,可将 数据 存储器 R M的容量 扩大 A

N l td o al x

mc0 8

一

1 t 1 li N

iN m5 n一 c t 8a O i - Ol 1 u

mi tN 1

, ’ , 一

全 不影 响 l 1 l 条指 令 的正 确执 行 。对用 户 来 说 这

收稿 1 期 :0 6 0 — 6 5 1 2 0 — 9 0

只是 可 以使用 的内部R M增 加 了 ,控 制 并没有 任 A

20 . Wl .hnE Dnt 0 7 l C ia C . 4 Y W e

4 电手元 器 件 主用 4

中做 一些 改变而 已 。

的选 择 ,而这 个 即通用 又控 制 简单 的I核 最好 选 P

择8 5 微处理 器 。 01

在FG P A中植 入8 5 后 ,还 可在 上 面实 现 简 01 单 的T P P C h 协议 ,以支持远 程 访 问或 进行 远程 调

试 .这 只是 在 嵌 入 F G P A的8 5 上 的一 个 应 用 。 5 实 现 不 同 的控 制操 作 , 01

设 计 时 也 可 以采 用 一 个 外 部 f s 对 8 5 进 行 加 l h 01 a

载 .这样 .用户 只需 要将 编译好 的 汇编语 言 代码 加  ̄ f s就 可 以控制 8 5 的工 作 ,而此 时 用户 完 ] 1 ah l 01 全不需 要对 F G 进 行操作 就 能实 现简 单 的控制 , PA

单片机以太网节点及TCPIP协议栈设计

单片机以太网节点及TCPIP协议栈设计单片机以太网节点及T CP/I P协议栈设计■佳木斯大学姜重然陈文平单丽娜引言在工业过程控制领域,现场总线技术得到越来越广泛的应用,问题也随之产生。

各种现场总线技术有其专有的传输协议,互?兼容,无法实现相互之间的连接与通信。

工业以太网的出现和?断兴起,?但很好地解决了这些问题,而且也为现场总线技术的发展开辟了一个?为广阔的空间。

本文用单片机C8051F023和以太网控制芯片RTL8019AS,设计了以太网节点并且在此基础上实现精简的TCP/IP协议,实现了较完备的通信功能。

统MCS251完全兼容;然而在系统构架、外围设备等方面有了很大的改进,使得集成度?高,并且?再分系统时钟和机器时钟,指令直接按照系统时钟执?。

其他优点如下:◆集成J TAG调试器,可在线调试和下载,大大方?了调试过程;◆真正12位或10位、100ksps的8通道ADC,信号只需通过简单的阻容网络即可直接接入;◆64KB可在系统编程的Flash存储器,4352字节的片内RAM[1]。

鉴于以上优点,采用此型号的单片机后极大地简化了硬件电?,提高了系统的稳定性。

1节点功能描述所设计的以太网节点具有从站节点和网页服务器的两种功能。

作为从站节点,分时采集8?模拟?信号,按一定周期传给主站计算机,同时接收主站的控制命令。

作为网页服务器,接收客户端的网页请求,返回客户计算机所请求的Web页面。

因为单片机资源有限,又要求实现上述功能,在实现硬件电?的前提下,需要对TCP/IP协议族按需裁减,主要实现ARP、IP、ICMP、TCP 和。

2.2电?设计RTL8019AS是一种高度集成的以太网控制芯片,遵循IEEE802.3标准,是最常用的以太网硬件通信设备芯片。

它实现介质访问控制子层(MAC)的功能:为即将发送的数据进?以太网帧封装后,发送到网络上;对于接收到的数据帧,去掉其以太网帧头部并进?CRC校验,校验无误后存入接收缓存,等待主控制器读取;采用载波监听多?访问/冲突检测(CSMA/CD)来处?信道冲突。

基于8051 IP核的片上系统设计

输 出 口, 整体 模块根据单 片机 的结构划分为各个 子模 块 , 根 将 再 据各个子模块的功能来 通过 V D H L语言具体实现。 设计将整体模 块 划 分 为 C U 系统 模 块 、 时 / 数 器 模 块 、 口模 块 、 断 服 务 P 定 计 串 中 模 块 、 入 输 出端 口模 块 和 复 位 模 块 6部分 。 输

2 1 CP 系统 . U

1 85 0 1单片 机的 结构

典 型 的单 片 机 体 系 结 构 见 图 1 由 图 1 见 , 片 机 主 要 功 。 可 单 能 部件 有 :P 系统 、 P CU C U外 围单 元 ( 储 器 和 I 存 / 元 )基 本 功 O单 、 能单 元 ( 时 / 数 器 、 断 系 统 、 定 计 中 串行 接 口 )各 组 成 部 分 通 过 内 , 部 总线 紧密 连 在 一 起 。

C U是单片机 的核 心部分 ,其作用 是读 入和分析每一条 指 P 令 , 据 每 条 指 令 的功 能 要 求 控 制 各个 部 件 执行 相应 的操 作 。 根 根 据 C U 的组 成 划 分 ,P 系 统 模 块 为 算 术 逻 辑 单 元 (L ) 块 、 P CU A U模 控制单元模 块 、 程序存储器控制模块 、 数据存 储器控制模块 4部 分。 控制单元模块 的主要作用是译码指令 , 并产生适 当的控制信 号, 确保指令 的正确执行。算 术逻辑单元模块 的主要功能是进行 算术 逻辑 运算 、 完成数据传输 、 位变量处理等。 程序存储器控制模 块 主 要 是 实 现对 程 序 存 储 器 的控 制 , 主要 功 能 是 : 接 收 从 其 其 ① 他模 块传来 的信号 , 来形成正确的程序存储器地址 。②在适 当的

时刻发出对程序存储器 的读使能信号。 数据存储器控 制模块 主要 是实现对数据存储器 的控制 , 主要功能是 : 其 ①对数 据存 储器读 / 写的地址生成 。 在适 当的时刻发 出对数据存储器的读 / ② 写使能

MCU8051 IP core的设计

电子科技大学硕士学位论文MCU8051 IP core的设计姓名:焦原军申请学位级别:硕士专业:微电子学与固体电子学指导教师:罗佳慧20050301摘要本文研究使用VHDL语言设计实现MCU8051功能的软1Pcore。

设计的平台选用Altera公司的开发工具QuartusII40,在开发环境中完成软核的代码设计、综合、布局布线、芯片映射及时序分析,采用ModelSim工具进行功能、时序仿真验证,综合和验证选用Altera公司的Cyclone系列FPGA(FieldProgrammableGateArray)芯片,最终实现与Intelmcs805l功能完全兼容的MCU软核。

文章主要介绍了设计符合Intelmcs5lUser’SMANUL描述的单片机的功能及时序要求的软核。

首先从总体规划的角度介绍了整个系统的内部结构、模块划分及所采用的设计方法和编程风格,然后对各个模块的设计进行了详细的描述,最后给出了综合后的实现结果及测试方法、仿真波形图。

在系统方案设计过程中,仔细考虑了模块的合理划分及各个模块之间协同工作以使设计合理优化,按照自上而下的设计方法将各个模块逐一细化完成本模块的功能,各模块通过端口信号相通信,并根据设计的时序要求产生相应控制信号。

在编写代码时,尽量贴近硬件的实现方式,充分考虑FPGA芯片内部资源的合理开销及VHDL语言的特点,力求做到面积小而速度块,以满足功能和实用性的要求。

采用硬件描述语言设计的电子系统是近年来十分流行的方法,在SoC(SystemOnChip)设计中几乎都会将微处理器、存储单元等通用IP模块集成到FPGA中构成可配置的SoC芯片,无论是微电子集成,还是FPGA的可编程设计,或是单片机的模拟混合集成,目的都是SoC,手段也会逐渐形成基于处理器内核加上外围IP单元的模式。

MCS.51是Intel公司创建的8位机的经典系列结构,并实施技术开放政策,为众多厂家承认,并广泛用于SoC的处理器内核,使这个系列保持着生命力,在未来SoC发展中,作为8位经典结构的8051将担任8位CPU内核的重任。

一种基于FPGA的流水线8051IP核的设计与实现

一种基于FPGA的流水线8051IP核的设计与实现作者:王发栋杜慧玲史翔来源:《现代电子技术》2014年第05期摘要:给出一种基于FPGA的8051MCU的IP核设计方案,指令集与标准8051系列处理器完全兼容。

采用译码——执行两级流水结构,并通过了仿真与综合,理论速度较传统8051MCU有6~10倍的提升。

针对CISC流水线设计的复杂性,提出了一种高效的实现方案,可以使执行结构近满状态运行,且简便有效地解决了传统流水线所必须面对的三种冲突。

设计采用Verilog HDL语言描述,并采用ModelsimSE 6.2进行功能和时序验证,将代码下载到Xilinx公司的FPGA上进行物理验证,测试了一个LED流水灯程序,结果表明软核达到了预期的效果。

关键字: 8051微处理器;流水线; FPGA;控制冒险中图分类号: TN710⁃34 文献标识码: A 文章编号: 1004⁃373X(2014)05⁃0080⁃030 引言自51单片机应用以来,对其进行功能改进和性能提升的芯片设计层出不穷。

但由于其CISC的架构,对其流水线化始终局限于将CISC指令转换为可以在一周期内完成的类RISC指令,然后使用RISC指令流水作业的方式,这虽然可以让多条指令同时执行,但增加了译码结构的复杂程度,而且需要复杂的控制逻辑解决指令同时执行带来的传统流水线所必须面对的三种冲突。

本文原创性地提出一种新的实现方案,该方案解决了这三种冲突,且在FPGA的平台下最大限度地做到填充执行结构,使得指令可以流畅运行。

1 MCU结构与FPGA平台本文设计的8051 IP核是与传统8051指令集兼容的MCU内核,不包含定时器等模块但通过总线预留接口。

其结构如图1所示。

(1)译码器。

负责将读入的指令译成可供流水线执行结构执行的控制码,同时向其发送执行所需的地址和数据。

它包含4个控制码队列,在译码过程中循环地向四个队列中写入当前指令的控制码,因此可以不必等待指令执行完毕再继续下一条指令的译码。

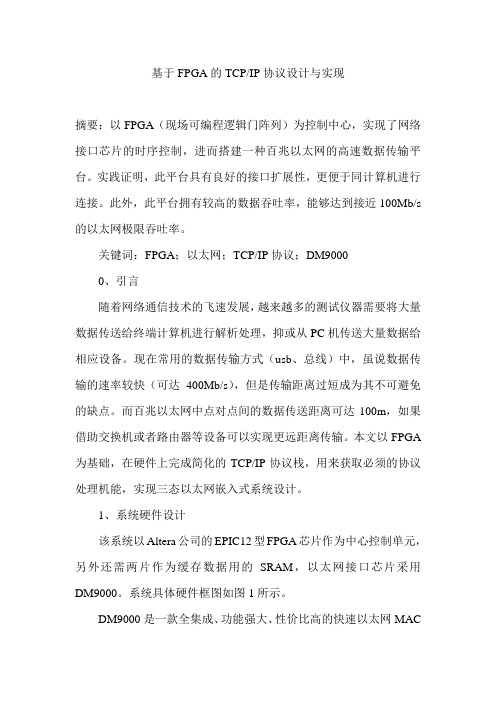

基于FPGA的TCP IP协议设计与实现

基于FPGA的TCP/IP协议设计与实现摘要:以FPGA(现场可编程逻辑门阵列)为控制中心,实现了网络接口芯片的时序控制,进而搭建一种百兆以太网的高速数据传输平台。

实践证明,此平台具有良好的接口扩展性,更便于同计算机进行连接。

此外,此平台拥有较高的数据吞吐率,能够达到接近100Mb/s 的以太网极限吞吐率。

关键词:FPGA;以太网;TCP/IP协议;DM90000、引言随着网络通信技术的飞速发展,越来越多的测试仪器需要将大量数据传送给终端计算机进行解析处理,抑或从PC机传送大量数据给相应设备。

现在常用的数据传输方式(usb、总线)中,虽说数据传输的速率较快(可达400Mb/s),但是传输距离过短成为其不可避免的缺点。

而百兆以太网中点对点间的数据传送距离可达100m,如果借助交换机或者路由器等设备可以实现更远距离传输。

本文以FPGA 为基础,在硬件上完成简化的TCP/IP协议栈,用来获取必须的协议处理机能,实现三态以太网嵌入式系统设计。

1、系统硬件设计该系统以Altera公司的EPIC12型FPGA芯片作为中心控制单元,另外还需两片作为缓存数据用的SRAM,以太网接口芯片采用DM9000。

系统具体硬件框图如图1所示。

DM9000是一款全集成、功能强大、性价比高的快速以太网MAC控制器。

该芯片拥有一个通用处理器接口、10/1()()PHY、EEPROM 和16kB的SRAM。

DM9000支持8位、16位以及32位的接口访问内部存储器,可以支持不同型号的处理器。

该芯片的PHY协议层接口完全可以使用10MBps下的3/4/5类非屏蔽双绞线和100MBps下的5类非屏蔽双绞线,很好地对应IEEE 802.3u规范。

DM9000实现以太网媒体介质访问层(MAC)和物理层(PHY)的功能,其中包含MAC数据帧的组装/拆分与发送接收、地址的识别、CRC编码/校验、MLT-3编码器、接收噪声抑制、输出脉冲形成、超时重传、链路完整性测试、信号极性检测与纠正等。

基于fpga的8051ip核的设计与验证研究

苏州大学硕士学位论文基于FPGA的8051IP核的设计与验证研究姓名:薛迎春申请学位级别:硕士专业:电子与通信工程指导教师:胡剑凌2010-12-31基于FPGA的8051IP核的设计与验证研究中文摘要基于FPGA的8051IP核的设计与验证研究中文摘要单片机自1976年问世以来,作为微型计算机一个很重要的分支,受到了人们的广泛关注和重视,尤其是美国Intel公司生产的MCS-51系列单片机,由于其具有集成度高、处理功能强、可靠性高、系统结构简单、价格低廉等优点,在我国已经得到了非常广泛的应用。

本论文主要的研究任务就是以8051单片机为蓝本,并与FPGA 内部结构相结合,使用硬件描述语言VHDL来实现整个系统的逻辑描述,开发出能够应用于FPGA的8051IP核。

本论文首先介绍了FPGA的相关基本知识和EDA开发工具,对8051单片机进行原理分析及各模块的功能介绍。

利用自顶向下的设计方法对8051CPU进行了IP核模块划分,对各模块进行了VHDL编程实现,设计了相应的测试数据,在modelsim仿真平台上完成了各模块的时序和功能验证,所实现的指令系统与8051单片机的指令系统完全兼容,实现了预期的效果。

论文最后在Altera公司的EP1K100FC484芯片上对整个8051IP核进行了综合仿真,搭建了简单的应用电路,完成了IP核的验证。

本论文在阐述可编程逻辑器件及其发展的基础上,结合了国内外对FPGA的使用限制,引出了在FPGA上开发嵌入式模块程序的理念并提出了设计实现方法和验证实例。

该设计具有很高的实用性,可以促进单片机技术和可编程逻辑器件课程的教学工作。

实现的8051IP核也可以在某些方面加快教育信息化的发展,进一步扩大了可编程逻辑器件的使用范围,将复杂专有芯片推向高端和超复杂应用,使得IP资源复用理念得到更普通的应用,为基于FPGA的嵌入式系统设计提供了广阔的思路。

关键词:FPGA、VHDL、8051 IP核作者:薛迎春指导教师:胡剑凌Abstract design and verification of 8051IP core based on FPGA Design and Verification of 8051IP Core Based on FPGAAbstractAs a very important branch of computer, single-chip microcomputer(SCM) has received significant attention since it was invented in 1976. Particularly the MCS-51 series SCM which was produced by the USA Intel company, has been widely used in varies industries in our country for its high integration, robustness, flexibility, low cost, and so on. This thesis implements the IP core of 8051 MCU using VHDL, and the FPGA is selected as the simulation platform.This paper firstly introduces the related basic knowledge of FPGA and the development tools of EDA, the principle analysis of 8051SCM and the function of each module. By using top-down design method for 8051 CPU conducted IP core module partition, using VHDL language to program of each module, and designing the corresponding test data. In the modelsim simulation platform, the timing and function verification of each module were completed. The accomplished instruction set is fully compatible with the 8051 single-chip Microsoft instruction, so this design is achieved the desired result. Finally, this paper conducted a comprehensive simulation to the whole 80C51IP core in Altera company EP1K100FC484 chip, and built a simple application circuit to complete the IP core validation.The realization of 8051IP core can accelerate the development of education informatization in some respect, and further expand the programmable logic devices scope of application, complex proprietary chip to high-end and complicated application, making the concept of IP resources to be more reuse common application, the application of the embedded system based on FPGA design provides a broad avenue of research. Keywords: FPGA, VHDL, 8051 IP coreWritten by Xue YingchunSupervised by Hu Jianling基于FPGA的8051IP核的设计与验证研究第一章前言第一章前言单片机的出现是计算机技术的里程碑事件,因为单片机的诞生标志着计算机正式形成了通用计算机系统和嵌入式计算机系统两大分支。

基于FPGA的8051IP核的设计与实现

基于FPGA的8051IP核的设计与实现

徐慧;王金海;王巍

【期刊名称】《计算机技术与发展》

【年(卷),期】2009(19)3

【摘要】裁减并完善了与MCS-51系列微处理器指令集完全兼容的8051IP核,减少了设计面积,提高了处理速度.按照自顶而下的设计原则,分别设计了算术逻辑单元、中心控制器、定时/计数器、串行口、RAM和ROM单元.设计采用VHDL语言进

行描述并且用ModelsimSE6.0进行功能和时序验证.将8051IP核下载到Xilinx公司的FPGA(XC3SSOOE-4FG320C)上进行物理验证,测试了一个LED流水灯程序,

结果表明软核达到预期的效果.本设计作为可移植的IP核,可以组成片上系统,用于

嵌入式系统领域.

【总页数】4页(P42-45)

【作者】徐慧;王金海;王巍

【作者单位】天津工业大学,信息与通信工程学院,天津,300160;天津工业大学,信息与通信工程学院,天津,300160;天津工业大学,信息与通信工程学院,天津,300160【正文语种】中文

【中图分类】TP302

【相关文献】

1.基于Xilinx FPGA IP核的浮点频域脉冲压缩算法的设计与实现 [J], 邢冠培;孟凡利

2.基于FPGA与8051IP核的宽带数字频率计系统设计 [J], 孙锐;朱军;丁大为;

3.基于FPGA与8051IP核的宽带数字频率计系统设计 [J], 孙锐;朱军;丁大为

4.基于FPGA的模板滤波IP核的设计与实现 [J], 李东;敖晟;田劲东;田勇

5.基于FPGA IP核的FIR滤波器设计与实现 [J], 李奇;尹倩;姚硕;孙杨

因版权原因,仅展示原文概要,查看原文内容请购买。

8051 IP 核与 CAN IP 核的接口技术

8051 IP 核与 CAN IP 核的接口技术

薛鹏举;倪霞林

【期刊名称】《机械制造与自动化》

【年(卷),期】2014(000)004

【摘要】利用SOPC技术,将8051 IP核与CAN IP核有机融合,提出了一种创新型的控制器局域网( CAN)节点设计方案。

介绍了如何使用硬件描述语言( HDL)实例化8051 IP 核和CAN IP核,描述了这两个软核的接口类型及它们之间的握手细节。

编写测试程序,综合整个工程,并将生成的工程代码下载至FPGA运行。

结果表明:使用SOPC技术设计的CAN节点通信良好,利用可重配置的IP核技术,可以实现更加复杂的功能,系统的设计也会更加灵活、稳定、可靠。

【总页数】3页(P196-198)

【作者】薛鹏举;倪霞林

【作者单位】福州大学机械工程及自动化学院,福建福州350108;福州大学机械工程及自动化学院,福建福州350108

【正文语种】中文

【中图分类】TN914.3

【相关文献】

1.在嵌入FPGA的IP核8051上实现TCP/IP的设计 [J], 罗侄敬

2.开放核协议--IP核在SoC设计中的接口技术 [J], 焦原军;李广军;罗佳慧

B 2.0设备接口IP核的OPB接口技术研究和实现 [J], 杨娟;李晓潮;郭东辉

B2.0设备控制器 IP核的AHB接口技术 [J], 左宏权

5.基于XML的IP核通信接口建模技术 [J], 童琨;边计年;王海力

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的IP核8051上实现TCP/IP的设计引言随着芯片规模的越来越大、资源的越来越丰富, 芯片的设计复杂度也大大增加。

事实上, 在芯片设计完成后, 有时还需要根据情况改变一些控制, 这在使用过程中会经常遇到。

这时候如果再对芯片设计进行改变将是很不可取的, 因为需要设计人员参与这种改变, 这无论是对设计者还是用户都是不能接受的。

于是就有必要让这种可以改变的简单控制在芯片设计时就存在, 而且同时还应该使这种改变相对容易, 比较通用, 并且与芯片的其它设计部分尽量不相关。

为了满足上述的要求, 在FPGA中嵌入一个比较理想的选择, 而这个即通用又控制简单的IP核最好选择8051微处理器。

在FPGA中植入8051后, 还可在上面实现简单的TCP/IP协议, 以支持远程访问或进行远程调试, 这只是在嵌入FPGA的8051上的一个应用。

为了保证用户能够对8051实现不同的控制操作,设计时也可以采用一个外部flash对8051进行加载, 这样, 用户只需要将编译好的汇编语言代码加到flash就可以控制8051的工作, 而此时用户完全不需要对FPGA进行操作就能实现简单的控制,而这需要的仅仅只是keil的编译环境。

1 IP核8051的FPGA实现现在有许多免费的8051核可以利用, 这些核都可通过硬件描述语言来实现, 并且基本上都可综合, 也就是直接拿来就能用, 需要的只是根据自身的具体需求做一些简单修改即可。

总的说来, IP核8051的移植是比较简单的。

本系统的设计与实现可以采用oregano system的mc8051内核, 并且加入定时计数的和串口模块, 8051单片机的设计结构框图如图1所示。

在8051核的FPGA设计中, 完全可以实现包括计时/计数、中断、串口、数据及程序存储器、特殊寄存器、布尔处理的位处理机等的所有功能, 而且兼容所有指令, 只是在具体的移植过程中做一些改变而已。

这种方法对程序存储器不再做内外之分, 因为FPGA内部存储容量已经能够满足要求, 同时将程序存储器的容量扩大了一倍(变为8KB), 以满足大程序的容量需求; 为了让8051更为强大且更具有通用性, 可将数据存储器RAM的容量扩大一倍, 变为256字节。

可以看出, 在设计过程中将8051的功能也进行了加强, 但是并不影响对它的控制, 仅仅是在硬件上对存储器的容量进行了扩大, 而这种扩大只是改变了地址线的宽度, 完全不影响111条指令的正确执行。

对用户来说这只是可以使用的内部RAM增加了, 控制并没有任何改变。

当然, 在资源比较紧张, 而且程序容量比较小时, 也可以将存储器的容量改小, 这种改变也相当方便, 只需要改变地址线的宽度就能达到目的。

由此可见, 设计时完全可以根据需要改变IP核的设计, 而不局限于8051。

虽然整个8051IP核能正确执行所有指令, 并能实现串口、计时器及中断控制, 且整个IP的核工作时钟也在20 MHz以上, 但是, 由于这时候的所有指令周期并不与真实的8051完全一致, IP核中有的指令需要比真正的8051多执行几个周期才能完成, 这就使得分析IP核的工作时钟复杂起来了, 因为相对于真正的8051不能有一个精确的工作时钟对比。

但是经过分析仍然可以认为, IP核应该可以工作在15 MHz左右, 也就是比真实的8051快了15倍左右。

这对于芯片整体来说, 其速度可能相对较低, 但是由于这部分与芯片其它部分的逻辑相关性极小, 所以并不会影响芯片的整体性能, 而对于一些简单控制来说, 这个速度还是能够满足要求的。

2 UIP协议栈2.1 UIP简介在FPGA中实现TCP/IP协议的主要目的是为了满足设计人员对芯片的远程调试。

而满足这种要求实际上并不需要很强大和快速的传输功能。

功能过于强大将会占用过多的资源, 而且实际上, 很多功能并没有实际作用; 同时也不需要很快的传输速度。

毕竟对于一个芯片的设计来说,无论是设计文档或是设计程序, 容量都是非常有限的。

综合考虑, 则应选择一个实现简单、占用资源少, 但能够比较稳定地进行数据传输的协议, 为此, 本文选择了相对简单的UIP协议栈,而放弃了功能比较强大的LWIP协议栈。

选择UIP还有一个好处, 就是这个协议栈是专门针对单片机等微控制器设计的TCP/IP协议栈, 它能够利用嵌入的IP核8051来实现TCP/IP协议, 而不再需要额外的逻辑单元。

UIP的特点是代码量和数据量都比较小, 因而可以为存储器比较紧张的地方提供合适的实现方案, 包括TCP/IP所需的最小实现方案和只包含TCP、IP、ICMP (ping) 以及简单的UDP协议, 其具体的实现方法如图2所示, 图2中, 带“×”的表示已经实现。

2.2 UIP协议栈的实现方法通过UIP可实现TCP/IP协议集的四个基本协议, 包括ARP地址解析协议、IP网际互联协议,ICMP网络控制报文协议和TCP传输控制协议。

为了在8位、16位处理器上应用, UIP 协议栈在实现各层协议时采用有针对性的方法来保证代码大小和存储器使用量最小。

实现ARP地址解析协议时, 为节省存储器,ARP应答包可直接覆盖ARP请求包; 而在实现IP网络协议时, 则对原协议进行了极大的简化, 并没有实现分片和重组; 当实现ICMP网络控制报文协议时, 只需实现echo (回响) 服务。

UIP在生成回响报文时, 并不重新分配存储器空间, 而是直接修改echo请求报文来生成回响报文。

设计时可将ICMP类型字段从“echo”改变成“echo re-ply”类型, 并重新计算校验和修改校验和字段。

UIP里的TCP没有实现发送和接收数据的滑动窗口。

每个TCP连接的状态均由uip_conn结构保存。

uip_conn结构包括当地和远端的TCP端口编号、远程主机的IP地址、重发时间值、上一段重发的编号以及连接段的最大尺寸等信息。

uip_conn结构数组可用于保存所有的连接, 数组的大小等于可支持同时连接的最大数量。

为了减少储存器的使用量, 在处理重发时, UIP并不缓存发送的数据包, 而是由应用程序在需要重发时重新生成发送的数据。

2.3 UIP协议栈的接口为了UIP协议栈能具有最大的通用性, 在实现时可将底层硬件驱动和顶层应用层之外的所有协议集“打包”在一个“库”里。

协议栈通过接口与底层硬件和顶层应用进行通信。

通过这种方式可使uIP具有极高的通用性和独立性, 以便移植到不同的系统和方便地实现不同的应用, 很好的体现TCP/IP协议平台无关性的特点。

UIP协议栈与系统底层和应用程序之间的接口如图3所示。

图中, 各接口之间都是由一系列函数来实现的。

3 UIP协议栈在IP核8051上的实现3.1 UIP协议栈在IP核8051上的移植由于UIP协议栈是专门针对微处理器编写的,所以移植也是非常的方便, 但需注意以下几点:(1) 协议栈是用C语言编写的, 故在移植时需要再加上两个头文件, 一个是8051的头文件, 另一个是8051的硬件初始化头文件;(2) 通过keil c编译器编译时, 在选器件时需要注意, 只有选取数据寄存器为256个字节才能顺利通过编译, 这也是为什么前面8051IP核的数据存储器RAM需要扩展至256个字节的原因。

不对RAM进行扩展, 就会出现“不能写B9地址”的错误, 因为在没有对RAM扩展前, 根本不存在B9地址;(3) 将软件keil编译生成的hex文件送入到8051的程序存储器, 即可在IP核8051上实现简单的TCP/IP协议。

这在软件测试时, 与实际工作将有所不同。

软件测试时需要将hex文件作为程序存储器的初始化输入, 即在EDA软件编译8051时, 将程序存储器的初始化文件mif的路径设置为hex所在的路径, 在完成综合布线后, hex文件的内容就进入了程序存储器。

这样, 仿真时就能在8051IP上实现TCP/IP协议了。

3.2 UIP的工作流程TCP/IP协议在嵌入到FPGA的IP核8051上的工作流程, 实际上也是简化后的TCP/IP协议的工作流程, 这跟正式的TCP/IP协议有所不同。

下面的工作流程以输入一个同步帧(即: 三向握手的第一次握手) 为例。

对于8051实现的UIP来说, 它属于被动建立连接, 其正确的输出结果应该是三向握手的第二次握手, 送出一个确认同步帧是所期望的结果。

下面简单介绍UIP的整个工作流程:(1) 在P0端口有数据前, 读取数据函数并反复执行, 以对P0端口进行监视(此种情况只是在测试时, 实际工作中物理层通过控制信号通知读数函数P0口是否有数据);(3) 为信号的第8级分解小波模极大值图; (4) 为信号各级(共9级) 的高频分量即小波系数。

由图4可以看出, 该故障信号分析仪能有效采集实时故障信号, 并可在对信号经过小波分析后有效的提取故障特征, 而且故障点定位明显。

5 结束语该便携式接触网故障信号分析仪采用图形化程序设计语言LabVIEW开发设计, 可实现数据的高速实时采集、在线分析、自动存储、显示等功能。

高速数字化仪NI PXI- 5112卡采样速度高、性能稳定可靠, 适宜对高速变化信号的实时监测。

将软件安装在PXI- 1042工控机上, 具有体积小、抗干扰能力强、携带方便等特点, 同时具有故障性质判断、故障定位功能。

该系统目前已经在石家庄变电所现场运行, 效果良好。

参考文献[1] 刘君华.基于LabVIEW的虚拟仪器设计[M].北京: 电子工业出版社,2003:115- 127.[2] Rober H. bVIEW6i 实用教程[M].北京: 电子工业出版社,2003:209- 265.[3] LabVIEW Data Acqusition Basics Manual on NI- 5112[M].National Instrument Corpration,1998.[4] Mok Aloysius K,Srusrt Douglas.RTT seman tics forLabVIEW.IEEE Aerospace Applications ConrerenceProceedings,1998:61- 71.[5] 杨乐平, 李海涛,等.LabVIEW高级程序设计[M].北京:清华大学出版社,2003:390- 392.。