使用modelsin对quartus II仿真时遇到问题的解决方法

Quartus-II调用modelsim仿真方法

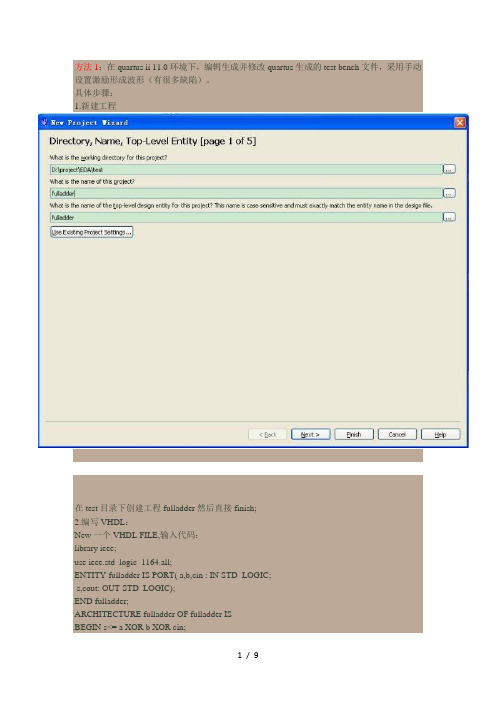

方法1:在quartus ii 11.0环境下,编辑生成并修改quartus生成的test bench文件,采用手动设置激励形成波形(有很多缺陷)。

具体步骤:1.新建工程在test目录下创建工程fulladder然后直接finish;2.编写VHDL:New一个VHDL FILE,输入代码:library ieee;use ieee.std_logic_1164.all;ENTITY fulladder IS PORT( a,b,cin : IN STD_LOGIC;s,cout: OUT STD_LOGIC);END fulladder;ARCHITECTURE fulladder OF fulladder ISBEGIN s<= a XOR b XOR cin;cout <=(a AND b) OR (a AND cin) OR (b AND cin);END fulladder;保存在test目录下,文件名为默认fulladder。

3. 在Quartes II 11.0界面菜单栏中选择 Tools-->options选项卡中选中EDA tool options,在该选项卡中下面的ModelSim-Altera一项指定安装路径为(如d:/Altera/11.0/modelsim_ae/win32aloem)4.在Quartes II 11.0界面菜单栏中选择Assignments->Settings。

选中该界面下EDA Tool settings中的Simulation一项;Tool name中选择ModelSim-Altera;Format for output netlist中选择开发语言的类型VHDL或其它,如图:然后点击APPLY应用和OK。

5.设置完成后,编译工程:在Quartus II 11.0界面菜单栏中选择菜单栏选择Processing-->start Compilation,等待编译,无错后会在test目录下生成simulation目录,执行下一步。

quartus ii 常见的19个错误、28个警告

(一) Q uartus警告解析1.Found clock-sensitive change during active clock edge at time<time> on register"<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated with size <number> tomatch size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed byoptimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -changes to thisconnectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋…0‟,便会被接地,赋…1‟接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning5.Found pins functioning as undefined clocks and/or memory enables原因:是你作为时钟的PIN没有约束信息。

Quartus使用问题及解决方法总结

Quartus使用问题及解决方法总结(转载)在QuartusII下进行编译和仿真的时候,会出现一堆warning,有的可以忽略,有的却需要注意,虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚,大家群策群力,把自己知道和了解的一些关于警告的问题都说出来讨论一下,免得后来的人走弯路.下面是我收集整理的一些,有些是自己的经验,有些是网友的,希望能给大家一点帮助,如有不对的地方,请指正,如果觉得好,请版主给点威望吧,谢谢1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated value with size <number> to match size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

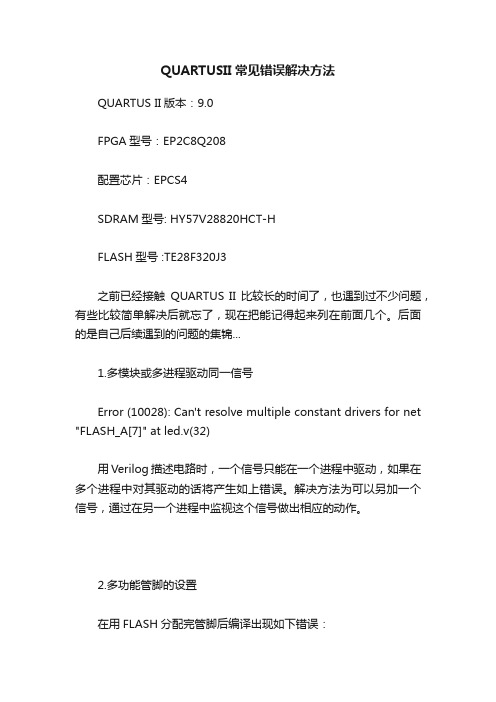

QUARTUSII常见错误解决方法

QUARTUSII常见错误解决方法QUARTUS II版本:9.0FPGA型号:EP2C8Q208配置芯片:EPCS4SDRAM型号: HY57V28820HCT-HFLASH型号 :TE28F320J3之前已经接触QUARTUS II比较长的时间了,也遇到过不少问题,有些比较简单解决后就忘了,现在把能记得起来列在前面几个。

后面的是自己后续遇到的问题的集锦...1.多模块或多进程驱动同一信号Error (10028): Can't resolve multiple constant drivers for net "FLASH_A[7]" at led.v(32)用Verilog描述电路时,一个信号只能在一个进程中驱动,如果在多个进程中对其驱动的话将产生如上错误。

解决方法为可以另加一个信号,通过在另一个进程中监视这个信号做出相应的动作。

2.多功能管脚的设置在用FLASH分配完管脚后编译出现如下错误:Error: Can't place multiple pins assigned to pin location Pin_108 (IOC_X34_Y2_N0)Info: Fitter preparation operations ending: elapsed time is 00:00:00Error: Can't fit design in deviceError: Quartus II Fitter was unsuccessful. 2 errors, 0 warnings Error: Quartus II Full Compilation was unsuccessful. 4 errors, 56 warnings原因是不能分配给多功能管脚PIN_108。

这是由于PIN_108是一个多功能管脚,还有一个功能是nCEO,也是默认的功能。

如果要用它当普通IO,需要提前设置一下:assignments>device>device and pin options>dual-purpose pins 里面把nCEO设置成use as regular i/o就可以了。

quartus ii 常见的19个错误、28个警告

(一) Q uartus警告解析1.Found clock-sensitive change during active clock edge at time<time> on register"<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated with size <number> tomatch size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed byoptimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -changes to thisconnectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning5.Found pins functioning as undefined clocks and/or memory enables原因:是你作为时钟的PIN没有约束信息。

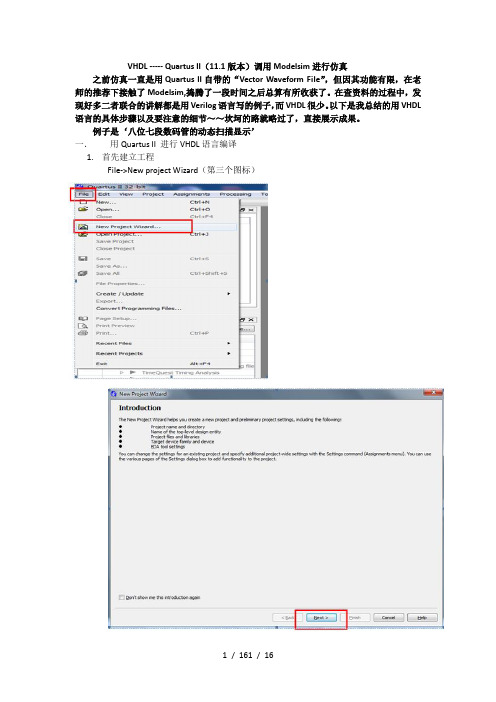

VHDL--Quartus-II调用Modelsim进行仿真只是分享

VHDL ----- Quartus II(11.1版本)调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“Vector Waveform File”,但因其功能有限,在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL 语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是‘八位七段数码管的动态扫描显示’一.用Quartus II 进行VHDL语言编译1.首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置具体的实验器件根据提供的实验板设定Assignment->Device4.引脚分配Assignment->Pin Planner在Location下的方格中填入对应的硬件引脚,也是根据实验板而定6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim1、设置仿真工具为Modelsim-alteraTool->Options->EDA Tool Options,在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用Quartus II生成的模板Processing->start->Start TestBench Template Writer,显示成功后关闭生成报告。

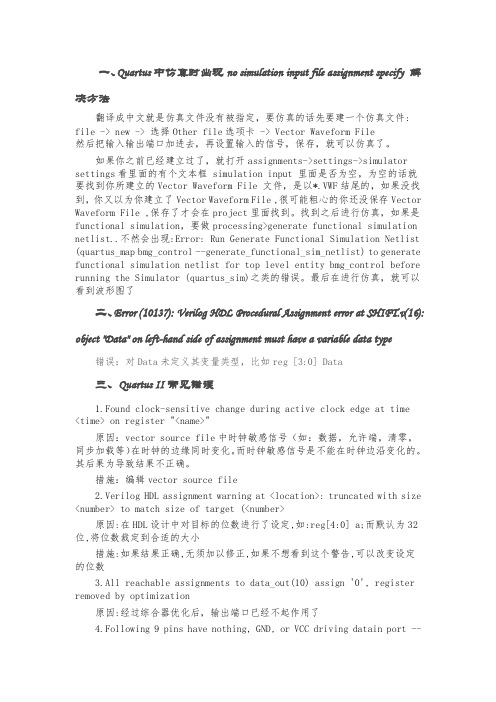

Quartus 中仿真出现错误解决方案汇总

一、Quartus中仿真时出现no simulation input file assignment specify 解决方法翻译成中文就是仿真文件没有被指定,要仿真的话先要建一个仿真文件: file -> new -> 选择Other file选项卡 -> Vector Waveform File然后把输入输出端口加进去,再设置输入的信号,保存,就可以仿真了。

如果你之前已经建立过了,就打开assignments->settings->simulator settings看里面的有个文本框 simulation input 里面是否为空,为空的话就要找到你所建立的Vector Waveform File 文件,是以*.VWF结尾的,如果没找到,你又以为你建立了Vector Waveform File ,很可能粗心的你还没保存Vector Waveform File ,保存了才会在project里面找到。

找到之后进行仿真,如果是functional simulation,要做processing>generate functional simulation netlist..不然会出现:Error: Run Generate Functional Simulation Netlist (quartus_map bmg_control --generate_functional_sim_netlist) to generate functional simulation netlist for top level entity bmg_control before running the Simulator (quartus_sim)之类的错误。

最后在进行仿真,就可以看到波形图了二、Error (10137): Verilog HDL Procedural Assignment error at SHIFT.v(16): object "Data" on left-hand side of assignment must have a variable data type 错误:对Data未定义其变量类型,比如reg [3:0] Data三、Quartus II常见错误1.Found clock-sensitive change during active clock edge at time<time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

VHDLQuartusII调用Modelsim进行仿真

VHDL ----- Quartus II(11.1版本)调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“Vector Waveform File”,但因其功能有限,在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL 语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是‘八位七段数码管的动态扫描显示’一.用Quartus II 进行VHDL语言编译1.首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

3.编译快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置具体的实验器件根据提供的实验板设定Assignment->Device4.引脚分配Assignment->Pin Planner在Location下的方格中填入对应的硬件引脚,也是根据实验板而定6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim1、设置仿真工具为Modelsim-alteraTool->Options->EDA Tool Options,在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用Quartus II生成的模板Processing->start->Start TestBench Template Writer,显示成功后关闭生成报告。

QuartusII13.1下仿真NativeLink Error错误解决方法

QuartusII11.0工程升级为QuartusII13.1 仿真NativeLink Error错误解决方法(北京郭树忠)因系统功能扩展,需要重新对某一程序模块进行仿真,由于目前使用的QuartusII13.1仿真软件与原工程软件使用的QuartusII11.0仿真软件版本不同,在工程升级编译完成后运行仿真软件时,出现了NativeLink Error错误,经过反复检查,找到了原因,问题得以顺利解决。

为此,整理了此文档,分享给大家,希望给开展类似工作的同学们节省部分时间。

一、过程原工程环境:QuartusII11.0,ModelSim SE-64 10.0c;新工程环境:QuartusII13.1,ModelSim-Altera starter Edition 13.1.0.162。

在将QuartusII11.0的软件工程在QuartusII13.1下编译完成后,选择Tools->Run Simulation Tool->RTL Simulation,运行仿真软件,如图1.启动仿真窗口所示。

图1.启动仿真窗口仿真软件窗口出现错误提示:NativeLink Error.You selected ModelSim as Simulation software in EDA Tool Settings, However NativeLink Found ModelSim-Altera in the path –correct path or change EDA Tools Settings and try again.如图2.NativeLink Error错误提示窗口。

图2. NativeLink Error错误提示窗口因仿真软件版本不同,仿真软件安装目录也不同,因此出NativeLink Error 错误提示后首先想到的是在EDA Tools Settings中配置仿真软件路径,并在全局变量中设置license_file 文件路径LM_LICENSE_FILE=c:\altera\13.1\ modelsim_ase\LICENSE_DELLXPX.TXT。

VHDL--QuartusII调用Modelsim进行仿真..doc

VHDL —— Quartus 11(11.1版本调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“ Vector Waveform File但因其功能有限, 在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是八位七段数码管的动态扫描显示’一.用Quartus II进行VHDL语言编译1. 首先建立工程File->New project Wizard(第三个图标IntroductionT»w WUartf hctw OMt* ■ new preyed preAwurr prwfM rdj^rvg the <oi> i —Cf New Pt eel WLurdDirectory, Nd ok?, f op I eve! t fit Hy [ 1 ol 5JWwt • fw B^grtany »«ClDr 簞 2 *W prqgKl?U r'^Ww FMhag 厚叫<™« 电「申mjrdjQ口»**#1 4 ** e* tw >a^4r-*l *rtir r g W p轉W TIM « *» «*"*«** *B«C*r ・W enfliv*M»W ** 華«*h^ru填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish撚后单击yes。

新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法电|脚弧{} ts ts e 代%处处 » n 创1鑼a l =*二二imlibrary ieee;use ieee .std_logic_1164.all;use ieee.std_logic_unsigned.all; □ entity hexx is日 port (clk:xn std_logic;―时神信号输入key:in std_logic_vector (3 downto 0) ;■-四位信号若入 ag : out std^logic^vector (6 downto 0);―7段值号辕出 • sei:out std_logic_vector (2 downto 0)) ;-■数码管送择 end;22 sel<«ql; end if;1C 11 12□ architecture a of hexx is 曰begnn□process (elk)variable ql :std logic vector (2 downto 0):■R 000R ; 1€ n19 2C 21 曰曰卜beginif elk*event and clk«thenif ql-w lll H then ql:"000”; else qls-ql*1!*; end if ; 24电i nend process; 细(} tFS / ® 口创圖2 I r = we 789 10library ieee;use ieee.std IoqIc 1164.all;use ieee.5td_logic_unaignedeall: Bentity hexx is曰 port (clk:in std_logic;一时神(8号辐入key: m std logic tor (3 downto 0) ;一Qfifll 号输入sg:ouc std_logic_vector (6 downs 0); -」段(B 号•出 sellout scd_logxc_vector (2 downto 0));■■数冯苣送择 end; 11 Barchitectuxe a of hexx is 12 Qtegin三曰卜曰□process (cllc)variable ql:std_lo^ic —vector (2 downto 0): beginif elk 'event and clJc**!* then If ql —ill- then ql : —000": else •000- end if ; sel<*ql; end if; end process;-HD —曰 6 7 8 2 2 2 ••X•■“ ■八1 2 3 q注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

使用modelsin对quartusII仿真时遇到问题的解决方法

使用modelsin对quartusII仿真时遇到问题的解决方法1、FFT core可以设置成两种不同的引擎结构,四输出(Quad——output)和单输出(signal output),对于要求转换时间尽量小的应用,四输出的是最佳的结构,对于要求资源尽量小的应用,单输出的引擎结构比较合适,为了增加吞吐量,可以采用并行引擎结构。

FFT core支持的数据流:FFT core支持三种I/O数据流结构,连续(streaming)、缓冲突发(buffered burst)、突发(burst)。

连续I/o数据流允许处理连续输入数据,输出连续复数数据流,而不中断输入和输出数据;缓冲突发结构于连续相比,需要更少的存储资源,但是这是以减少平均吞吐量为代价的;突发数据流的操作于缓冲突发的方法基本上一致,但是突发方式需要更少的存储资源,这也是以降低吞吐量为代价的、。

2、用modelsim对fft模块进行仿真的时候出现此类问题的解决方法:** Error: (vsim-3033) E:/Quartus II projects/fft_1024_t/fft_1024_ip.v(92): Instantiation of 'asj_fft_sglstream_fft_130' failed. The design unit was not found.出现这种情况,第一可能是quartus破解不完整,导致有些库已经器件不能够使用,重新破解,在破解的时候有时候可能有好几个网卡,则选择前两个网卡号对license.dat进行破解。

在完整破解的时候,在仿真的时候需要加进去.vo文件以及测试文件,顶层文件,同时将生成fft核的时候产生.hex,.txt文件,在进行仿真的时候需要将其放到所建的modelsim工程文件夹下面。

第二种情况就是在不同版本的quartus上建立了ip核,比如说在9.0上建立的文件,在8.0上进行综合编译,就会出现这样的问题。

ModelSim6.5与quartus联合仿真的路径问题解决

二、有关quartusIபைடு நூலகம்出现

“Error: Can't launch the ModelSim software – the

path to the location of the executables for the ModelSim software were not specified or the executables were not

found at specified path.

Error: You can specify the path in the EDA Tool Options page of the Options dialog box or using the Tcl command set_user_option.

Error: NativeLink simulation flow was NOT successful.”

这样的错误的解决办法。

Solutions:

点击tools 选择opinions:点击EDA Tool opinions

如图所示:在location of Executable下,

路径一定要有“modelsim.exe”的文件夹,

modelsim6.5与quartus联合仿真的路径问题解决 二,有关quartusii出现 "error: can't launch the modelsim software– the path to the location of the executables for the modelsim software were not specified or the executables were not found at specified path. error: you can specify the path in the eda tool options page of the options dialog box or using the tcl command set_user_option. error: can't launch the modelsim software -- the path to the location of the executables for the modelsim software were not specified or the executables were not found at s pecified path. error: nativelink simulation flow was not successful." 这样的错误的解决办法. solutions: 点击tools选择opinions:点击eda tool opinions 如图所示:在location of executable下, 路径一定要有"modelsim.exe"的文件夹, 个人建议选择你安装modelsim的位置.

quartus仿真出现的问题

quartus仿真出现的问题在QuartusII下进行编译和仿真的时候,会出现一堆warning,有的可以忽略,有的却需要注意,虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚,大家群策群力,把自己知道和了解的一些关于警告的问题都说出来讨论一下,免得后来的人走弯路.下面是我收集整理的一些,有些是自己的经验,有些是网友的,希望能给大家一点帮助,如有不对的地方,请指正,如果觉得好,请版主给点威望吧,谢谢1.Found clock-sensitive change during active clock edge at time on register ""原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at : truncated value with size to match size of target (原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results 原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

quartus 仿真出现的问题

在QuartusII下进行编译和仿真的时候,会出现一堆warning,有的可以忽略,有的却需要注意,虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚,大家群策群力,把自己知道和了解的一些关于警告的问题都说出来讨论一下,免得后来的人走弯路.下面是我收集整理的一些,有些是自己的经验,有些是网友的,希望能给大家一点帮助,如有不对的地方,请指正,如果觉得好,请版主给点威望吧,谢谢1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated value with size <number> to match size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

ModelSim常见错误原因及解决

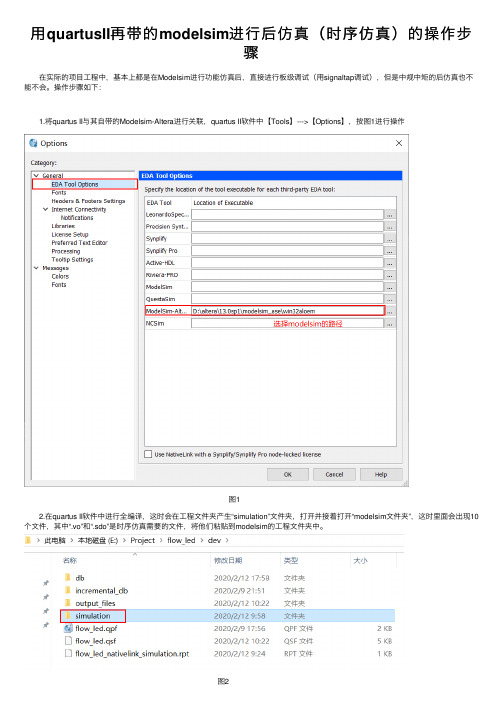

1.常见错误:Failed to find INSTANCE ...,问题出在下面所示的第2步或第4步。

正确处理步骤:(1)Quartus中编译测试码欲调用的顶层模块(设模块名:xxx),设置EDA tool 的simulation 工具,如verilog ,以产生xxx.vo文件及xxx_v.sdo延时文件;(2)打开modelsim,新建工程,添加xxx.vo文件、测试用激励波形文件testbench.v、所用器件的网表文件(以cyclone为例:$Quartus\eda\sim_lib\cyclone_atoms.v)。

全部编译。

!!:确认testbench.v中不包含顶层模块xxx代码。

(3)xxx_v.sdo复制到modelsim工程目录。

(4)最后,建立仿真配置文件:在workspace的project页中右键单击,选simulation configuration,如下图于是,workspace中得到simulation 1。

按下图设置:注意,上面的框中添加xxx_v.sdo,下面的文本框中设置作用域,格式为:\testbench模块名\xxx的实例名。

(5)`timescale 影响仿真结果显示效果。

=================例===================[1]//文件count4.vmodule count4(out,reset,clk);output[3:0] out;input reset, clk;reg[3:0] out;always @(posedge clk)beginif (reset)out <= 0;elseout <= out + 1;endendmodule[2]//测试文件count_tp.v`timescale 1ns/1nsmodule count_tp;reg clk,reset;wire[3:0] out;parameter DELY = 100;count4 mycount(out,reset,clk);always #(DELY/2) clk = ~clk;initialbeginclk = 0; reset = 0;#DELY reset = 1;#DELY reset = 0;#(DELY*20) $finish;endinitial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out); endmodule[3]所用器件:cyclone[4]结果:明显产生了时延p.s.-----------------------网上有朋友指出勾选SDF中的两个选项,将原来的警告禁止,将原来的错误变为警告, 可以成功地进行反标注并运行仿真,但这样做并没有解决实际问题,只能产生功能仿真,没有得到带时延的时序仿真2.** Error: D:/ModelSim_6.5/ModelSimnear "'t": Illegal base specifier in numeric constant.syntax error, unexpected "BASE", expecting "class"错误原因:不是’timescale 而是`timescale,那个是键盘左上角的点,不是一撇。

quartus2和modelsim连接时遇到的错误

RTL,其实就是指你写的程序代码。

所以RTL仿真,就是程序仿真的意思,一般指综合前的逻辑仿真,也就是不加入电路时延的仿真。

用quartus2和modelsim连接仿真时,当你在时序仿真编译启动modelsim时,有时会遇到这种问题,Error: Can't launch the ModelSim-Altera software -- the path to the location of the executables for the ModelSim-Altera software were not specified or the executables were not found at specified path.

Error: You can specify the path inthe EDA Tool Options page of the Options dialog box or using the Tcl command set_user_option.

Error: NativeLink simulation flow was NOT successful

这是由于设置没有成功的原因,解决方法是,打开quartus2菜单中的tools中的option,会出现以下对话框

然后点击EDA Tool Options,会出现上图中的对话框,在EDA tool中的modelsim的右面,双击以下,在文件浏览中找到自己安装好的modelsim的文件夹,如上图所示即可。

Quartus II使用常见问题

Quartus II使用常见问题在Quartus II下进行编译和仿真的时候,会出现一堆warning,有的可以忽略,有的却需要注意,虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚,大家群策群力,把自己知道和了解的一些关于警告的问题都说出来讨论一下,免得后来的人走弯路.1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated value with size <number> to match size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

用quartusII再带的modelsim进行后仿真(时序仿真)的操作步骤

⽤quartusII再带的modelsim进⾏后仿真(时序仿真)的操作步

骤

在实际的项⽬⼯程中,基本上都是在Modelsim进⾏功能仿真后,直接进⾏板级调试(⽤signaltap调试),但是中规中矩的后仿真也不能不会。

操作步骤如下:

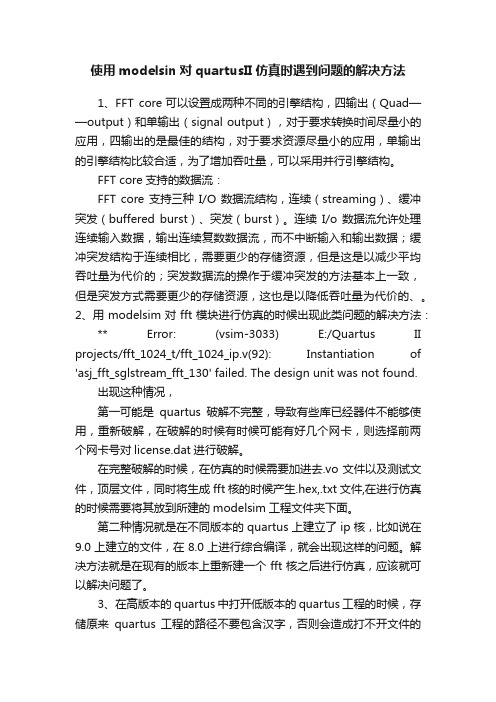

1.将quartus II与其⾃带的Modelsim-Altera进⾏关联,quartus II软件中【Tools】--->【Options】,按图1进⾏操作

图1

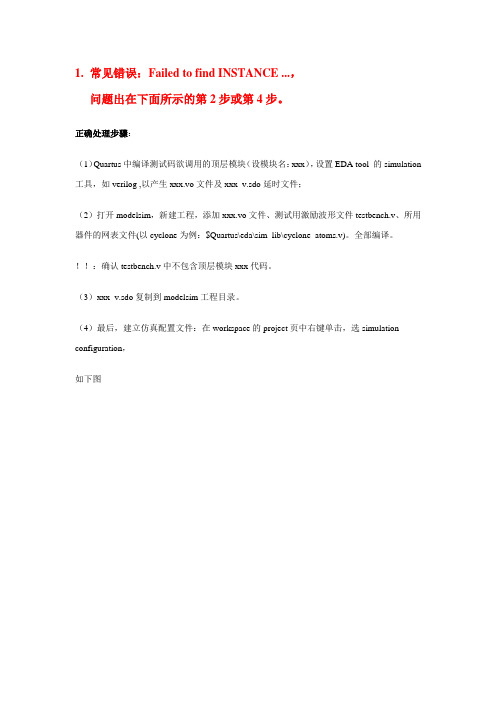

2.在quartus II软件中进⾏全编译,这时会在⼯程⽂件夹产⽣“simulation”⽂件夹,打开并接着打开“modelsim⽂件夹”,这时⾥⾯会出现10个⽂件,其中“.vo”和“.sdo”是时序仿真需要的⽂件,将他们粘贴到modelsim的⼯程⽂件夹中。

图2

图3

3.接下来还需要Altera的器件库

其中Altera的器件库⽂件在:D:\altera\13.0sp1\modelsim_ase\altera\verilog\altera

D:\altera\13.0sp1\modelsim_ase\altera\verilog\cycloneive

图4

4.将testbench⽂件和“.vo”⽂件加到⼯程上,然后编译,然后右键选择【Add to project】-->【Simulation Configuration】,选择【Work】中的"xxx_tb"⽂件,然后选择【Libraries】中加载刚在粘贴的2个Altera器件库,然后在【SDF】中加载刚才粘贴的“xx.sdo”⽂件,然后点【Save】,最后点击“Simulation”即可进⾏时序仿真。

如图5 、6、7所⽰:

图5

图6

图7 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、FFT core可以设置成两种不同的引擎结构,四输出(Quad——output)和单输出(signal output),对于要求转换时间尽量小的应用,四输出的是最佳的结构,对于要求资源尽量小的应用,单输出的引擎结构比较合适,为了增加吞吐量,可以采用并行引擎结构。

FFT core支持的数据流:

FFT core支持三种I/O数据流结构,连续(streaming)、缓冲突发(buffered burst)、突发(burst)。

连续I/o数据流允许处理连续输入数据,输出连续复数数据流,而不中断输入和输出数据;缓冲突发结构于连续相比,需要更少的存储资源,但是这是以减少平均吞吐量为代价的;突发数据流的操作于缓冲突发的方法基本上一致,但是突发方式需要更少的存储资源,这也是以降低吞吐量为代价的、。

2、用modelsim对fft模块进行仿真的时候出现此类问题的解决方法:

** Error: (vsim-3033) E:/Quartus II projects/fft_1024_t/fft_1024_ip.v(92): Instantiation of 'asj_fft_sglstream_fft_130' failed. The design unit was not found.

出现这种情况,

第一可能是quartus破解不完整,导致有些库已经器件不能够使用,重新破解,在破解的时候有时候可能有好几个网卡,则选择前两个网卡号对license.dat进行破解。

在完整破解的时候,在仿真的时候需要加进去.vo文件以及测试文件,顶层文件,同时将生成fft核的时候产生.hex,.txt文件,在进行仿真的时候需要将其放到所建的modelsim工程文件夹下面。

第二种情况就是在不同版本的quartus上建立了ip核,比如说在9.0上建立的文件,在8.0上进行综合编译,就会出现这样的问题。

解决方法就是在现有的版本上重新建一个fft核之后进行仿真,应该就可以解决问题了。

3、在高版本的quartus中打开低版本的quartus工程的时候,存储原来quartus 工程的路径不要包含汉字,否则会造成打不开文件的情况。

4、在modelsim中对rom核进行仿真的时候可能会出现这样的问题:

#warning:(vsim—3524)【FOFIR】—Failed to open file’simulation_ip.hex’for reading. #No such file for directory.(error=ENOENT)

出现这样的情况是因为在quartus 中建立的是.mif的文件,但是在modelsim中

进行仿真的时候识别的是.hex文件,不会识别.mif文件,所以需要首先将他们转换成.hex格式的文件,然后将其拷到modelsim工程下面。

同时,缺少一个文件,convert_hex2ver.dll,所以需要将其加到modelsim下的win32目录中,同时在modelsim中找到modelsim.ini文件,找到List of dynamically loaded objects for Verilog PLI applications;然后在下面一行中加上

Veriuser =D:\modelsim\program\win32\convert_hex2ver.dll(convert_hex2ver.dll 的保存路径)。

这样处理之后就可以进行modelsim的仿真了。

5、在verilog中进行编译的时候可能会出现这样的警告:

Warning (10230): Verilog HDL assignment warning at mult.v(98): truncated value with size 32 to match size of target (15)。

这是因为在前面的语句中没有指定出错的这条语句的位宽,所以会导致出现这样的错误,按照定义的位宽的长度指定所需要变量的位宽,这样的警告就会消失。

6、verilog中如何进行截位:

在quartus中,做完fft或者ifft操作之后,会使得结果的位宽比输入数据的位宽扩大一倍,在进行处理时,会造成fpga的资源的大量消耗,为了避免这个问题,就需要对操作完的数据进行截位处理,处理方法如下:

首先在matlab中得到操作完成之后的复数的实部和虚部的绝对值的最大两个数,变成二进制之后看其位宽,对于无符号数,这个数如果超过了65535,则用这个数除以2^n,选择合适的n值,使得结果在0—65535之间,然后需要截位的部分就是(m:n),m为最大的这个值的位宽。

具体的verliog语言的书写方式为:Datin_width=16,Datout_width=31;

Assign datout_real[Datin_width-1]=source_real[Datout_width-1];

assign datout_real[Datin_width-2:0]=source_real[29:15];

assign datout_imag[Datin_width-1]=source_imag[Datout_width-1];

assign datout_imag[Datin_width-2:0]=source_imag[29:15];

如上例中,输入数据位16位,进行fft运算之后的结果最大的值是29位的,所以从15—29进行截位操作。

6、verilog语言中模块之间是并行的,但是在always模块中逻辑是按照指定的顺

序执行的。

Initial块只执行一次,而always块不断的反复执行,直到整个仿真过程的结束.

7、interger型为整形寄存器,存储有符号的整形数。