ESD静电放电保护元件

esd器件 用途

esd器件用途ESD器件的用途ESD(Electrostatic Discharge)器件是一种用于保护电子设备免受静电放电损害的关键元件。

静电放电是指在电子设备的使用过程中,由于人体静电或其他原因导致的电荷累积和释放过程。

如果没有适当的保护措施,静电放电可能会对电子设备造成严重的损坏,甚至导致设备失效。

ESD器件的主要用途是在电子设备的输入/输出端口和电源线路等关键位置提供保护。

以下是ESD器件的几个常见用途:1. 保护接口电路:ESD器件通常被用于保护各种接口电路,如USB、HDMI、以太网等。

这些接口在连接外部设备时容易受到静电放电的影响。

通过在接口电路上设置ESD器件,可以有效地吸收和分散静电放电,保护设备免受损坏。

2. 保护电源线路:ESD器件还可以用于保护电子设备的电源线路。

在设备的电源输入端,ESD器件可以防止静电放电进入设备,从而保护设备的电源电路。

这对于提高设备的可靠性和稳定性非常重要。

3. 保护传感器和芯片:许多传感器和芯片在工作过程中对静电放电非常敏感。

ESD器件可以被用于保护这些敏感器件和芯片,防止静电放电对其产生损害。

例如,在光电传感器和压力传感器的输入端设置ESD器件,可以有效地保护它们免受静电放电的影响。

4. 保护显示屏:现代电子设备通常配备有高分辨率的液晶显示屏。

这些显示屏对静电放电非常敏感,容易受到损坏。

通过在显示屏周围设置ESD器件,可以保护显示屏免受静电放电的影响,延长其使用寿命。

5. 保护数据存储:数据存储设备,如硬盘驱动器和闪存,对静电放电也非常敏感。

静电放电可能导致数据丢失或设备损坏。

通过在数据存储设备的接口电路上设置ESD器件,可以有效地保护数据存储设备免受静电放电的影响。

6. 保护电源管理电路:电源管理电路对静电放电也很敏感。

通过在电源管理电路中使用ESD器件,可以保护电源管理电路免受静电放电的影响,确保设备的正常工作。

总的来说,ESD器件在电子设备中的用途非常广泛,可以有效地保护设备免受静电放电的损害。

esd管 打静电后微短路

ESD管打静电后微短路

ESD管是一种电子元件。

用于保护电路免受静电放电的影响。

如果ESD 管在打静电后出现微短路的情况,可能是由于静电放电导致管内的某些部分受损或出现故障。

出现这种情况时,建议采取以下措施:

1.检查ESD管的外观:查看ESD管是否有明显的物理损伤,例如裂纹、烧伤或变色等。

如果有明显的物理损伤,则可能需要更换新的ESD管。

2.使用万用表测试ESD管的电阻:通过测量ESD管的两个引脚之间的电阻值,可以初步判断其是否正常工作。

如果电阻值异常,则可能需要更换新的ESD管。

3.检查电路的其它部分:静电放电可能会对电路的其他部分造成影响,例如电路板上的其他元件或连接线等。

检查整个电路是否有异常情况,并进行必要的修复。

如果以上措施无法解决问题,或者您不确定如何处理这种情况,请联系专业的电子维修人员或相关技术支持团队进行进一步的帮助和指导。

泰科电子推出新的PESD静电保护元件

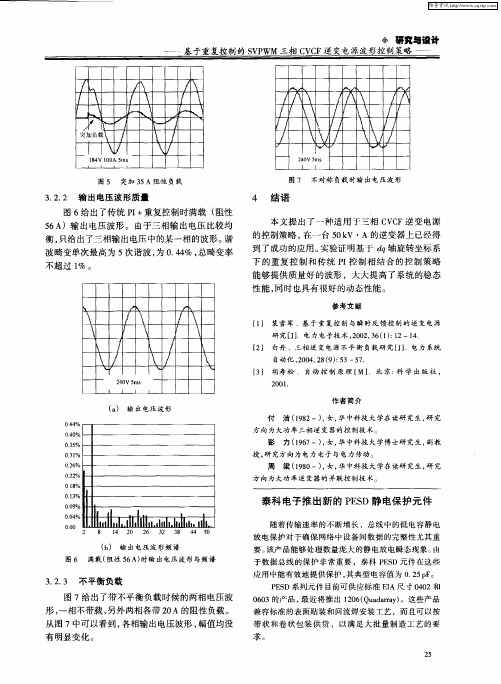

32 3 不平衡负载 . , 图 7 出了带不平衡负载时候的两相电压波 给 形, 一相不带载 , 另外两相各带 2 A的阻性负载。 0 从图 7中可以看到 , 各相输出电压波形 、 幅值均没

有 明显变化 。

兼容标准的表面贴装和回流焊安装工艺 ,而且可以按 带状 和卷状包 装供货 ,以满足大批量 制造工艺的要

8 V 1 0 m s 4 0A 5

2 V 40 5ms I 『

图 5 突加 3 阻性 负载 5 A

图 7 不 对 称 负载 时输 出电 压 波 形

322 输 出电压 波形 质量 ..

4 结 语

本 文 提 出 了一种 适 用 于三 相 C C V F逆 变 电源

方 向 为 大功 率三 相 逆 变 器的 控 制 技 术 。

授 . 究 方 向 为 电 力 电子 与 电 力 传动 。 研

方 向 为 大功 率 逆 变 器的 并联 控 制技 术 。

泰科 电子推 出新的 P S E D静 电保护元件

随着传输速率 的不断增 长,总线中的低 电容静电 放电保护对于确保 网络中设 备间数据的完整性尤其重 要。 该产品能够处理数量庞大的静电放电瞬态现象 。 由

于 数据 总线 的保 护 非 常重 要 ,泰科 P S E D元 件在 这些 应 用 中能有 效地 提供 保护 , 其典 型 电容值 为 02 。 .5 F p PS E D系列元 件 目前 可供 应标 准 EA尺 寸 0 0 和 I 42 00 63的产 品 , 最近 将推 出 10 ( udr y 。这些 产 品 26 Q aa a) r

| i | l } f , } , | . \ | f } i ’ | { { j

、_ , 、

esd的原理

esd的原理ESD的原理一、引言静电放电(Electrostatic Discharge,简称ESD)是指由于物体间的静电引起的突然放电现象。

静电放电是电子设备中常见的故障之一,它对芯片、集成电路等电子元件造成的损害是不可逆转的。

为了保护电子设备免受静电放电的伤害,人们研究并应用了ESD保护技术。

本文将介绍ESD的原理及其相关保护技术。

二、ESD的原理ESD是由于两个物体之间的电位差引起的,其中一个物体带有过高的电荷,导致电荷通过空气或介质释放。

静电放电的能量非常强大,其幅值可达数千伏特,持续时间极短,仅为纳秒级别。

这种高能量、瞬间释放的电流会瞬间加热电路,导致电子元件的损坏。

ESD的放电路径主要有三种:人体放电、设备间放电和设备内部放电。

在人体放电中,人体作为一个导体,当人体与带电物体接触时,电荷会通过人体释放,对设备造成损害。

设备间放电是指两个或多个设备之间的电荷差导致的放电现象。

设备内部放电是指设备内部电路中的电荷差导致的放电现象。

三、ESD的保护技术为了保护电子设备免受ESD的侵害,人们研究并应用了多种ESD保护技术。

1. 防静电衣物在一些特殊场所,如电子元器件生产车间、实验室等,人们需要穿着防静电衣物来减少静电的产生和释放。

防静电衣物能够防止人体与周围环境产生静电摩擦,从而减少ESD的发生。

2. 防静电地板防静电地板是一种通过导电材料制成的地板,它能够将人体的静电荷导入地下,从而减少人体放电对设备的影响。

防静电地板广泛应用于电子元器件生产车间、实验室等场所。

3. 静电消除器静电消除器是一种能够快速消除物体表面静电荷的装置。

它通过释放相反电荷来中和物体表面的静电荷,从而减少静电放电的发生。

静电消除器通常用于电子元器件生产线、实验室等场所。

4. ESD保护器件ESD保护器件是一种专门用于保护电子设备免受ESD侵害的元件。

常见的ESD保护器件包括二极管、MOS管等。

当电压突变时,ESD保护器件能够迅速启动,将过高的电压转移到地面,保护电子设备的安全。

esd保护电路原理

esd保护电路原理

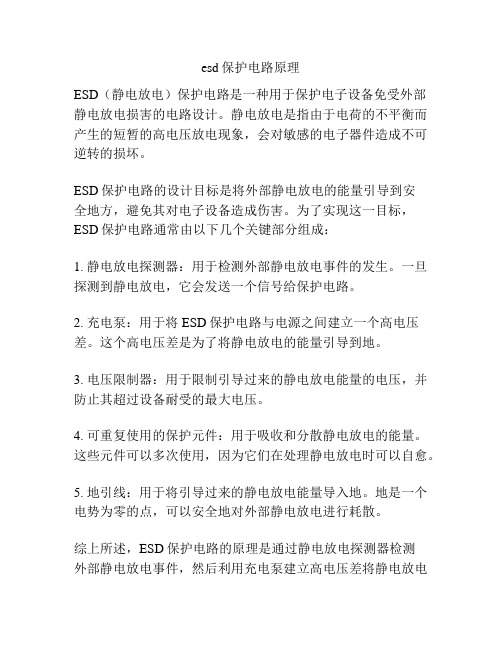

ESD(静电放电)保护电路是一种用于保护电子设备免受外部静电放电损害的电路设计。

静电放电是指由于电荷的不平衡而产生的短暂的高电压放电现象,会对敏感的电子器件造成不可逆转的损坏。

ESD保护电路的设计目标是将外部静电放电的能量引导到安

全地方,避免其对电子设备造成伤害。

为了实现这一目标,ESD保护电路通常由以下几个关键部分组成:

1. 静电放电探测器:用于检测外部静电放电事件的发生。

一旦探测到静电放电,它会发送一个信号给保护电路。

2. 充电泵:用于将ESD保护电路与电源之间建立一个高电压差。

这个高电压差是为了将静电放电的能量引导到地。

3. 电压限制器:用于限制引导过来的静电放电能量的电压,并防止其超过设备耐受的最大电压。

4. 可重复使用的保护元件:用于吸收和分散静电放电的能量。

这些元件可以多次使用,因为它们在处理静电放电时可以自愈。

5. 地引线:用于将引导过来的静电放电能量导入地。

地是一个电势为零的点,可以安全地对外部静电放电进行耗散。

综上所述,ESD保护电路的原理是通过静电放电探测器检测

外部静电放电事件,然后利用充电泵建立高电压差将静电放电

能量引导到地引线,并通过电压限制器和可重复使用的保护元件保护电子设备免受损害。

几种ESD器件的特性及选型原则

几种ESD器件的特性及选型原则ESD(Electrostatic Discharge)器件是一类用于保护电子设备免受静电放电(ESD)所引起的瞬态电压损害的设备。

在电子设备中,静电放电可能会导致电路故障、芯片损坏甚至整个系统的瘫痪,因此使用ESD器件来保护电子设备非常重要。

本文将介绍几种常见的ESD器件的特性及选型原则。

1. ESD二极管(ESD Diode)ESD二极管是一种常见的ESD保护器件,其特点是具有良好的ESD耐受能力和低电压保护阈值。

选择ESD二极管时,需要考虑以下几个方面:-阈值电压:ESD二极管在保护时会产生导通电压,选择时需要确保其阈值电压低于保护的系统工作电压。

-规格:根据被保护器件的功耗和工作电压,选择适当的二极管规格。

-快速响应时间:ESD二极管需要具备快速响应速度以保护被保护器件免受瞬态电压冲击。

-低电流泄漏:选择具有低电流泄漏的ESD二极管,以确保长时间使用时不影响系统性能。

2. ESD引线积层器件(ESD Suppressor)ESD引线积层器件是一种用于保护集成电路引脚免受静电放电的器件。

其特点如下:-高响应速度:ESD引线积层器件需要具备快速响应时间,以迅速疏散和吸收ESD电流。

-低引脚电容:选择低引脚电容的ESD引线积层器件可减少对信号传输的干扰。

-高ESD耐受能力:确保所选ESD引线积层器件的ESD耐受能力高于所保护系统的工作环境。

3. ESD防护网络(ESD Protection Network)ESD防护网络是由多个器件组成的网络,用于对整个电子设备或电路板提供全面的ESD保护。

在选择ESD防护网络时,需要考虑以下几个因素:-多级保护:选择具有多级保护的ESD防护网络,以提供更强的ESD保护性能。

-电路布局:根据整个电路板的布局和器件的连接方式,选择适合的ESD防护网络。

-抑制能力:确保所选ESD防护网络的ESD抑制能力符合所保护系统的工作环境。

4. ESD晶体管(ESD Transistor)ESD晶体管是一种具有高ESD耐受能力的晶体管,用于保护芯片的输入和输出端口。

esd电阻范围

esd电阻范围摘要:1.ESD电阻的定义和作用2.ESD电阻的分类3.ESD电阻的选择原则4.ESD电阻的应用领域5.总结正文:在我们生活的数字化时代,静电放电(ESD)成为一个不容忽视的问题。

ESD电阻作为一种电子元器件,具有保护电子设备免受静电放电损害的作用。

本文将介绍ESD电阻的范围、分类、选择原则以及应用领域。

一、ESD电阻的定义和作用ESD电阻,又称静电保护电阻,是一种具有高电阻值、低容抗的电子元器件。

其主要作用是在静电放电过程中,限制电流的大小,降低电压,从而保护电子设备免受损害。

二、ESD电阻的分类根据电阻材质,ESD电阻可分为陶瓷电阻、金属膜电阻、碳膜电阻等。

此外,根据电阻功率,可分为小功率电阻和大功率电阻。

不同类型的ESD电阻具有不同的性能和适用范围,需根据实际需求选择。

三、ESD电阻的选择原则1.电阻值:根据被保护设备的耐压值和允许的电流大小,选择合适的电阻值。

2.电阻材质:根据应用环境和工作温度,选择具有良好稳定性、耐热性和抗腐蚀性的电阻材质。

3.功率:确保ESD电阻的功率大于预期最大静电放电电流的峰值电流。

4.封装形式:根据实际应用场景和安装空间,选择合适的封装形式。

四、ESD电阻的应用领域ESD电阻广泛应用于电子产品、通信设备、家电、汽车电子等领域。

在这些领域中,ESD电阻发挥着保护电子设备免受静电放电损害的重要作用。

五、总结ESD电阻作为一种重要的电子元器件,在防止静电放电对电子设备的损害方面具有重要价值。

在实际应用中,根据需求选择合适的ESD电阻,能有效保护设备,延长使用寿命。

esd保护二极管原理

esd保护二极管原理

ESD保护二极管是一种用于保护电子设备免受静电放电(ESD)损害的元件。

其原理基于二极管的非线性特性。

当ESD事件发生时,静电放电过电压会引起二极管中的电荷

极化,使其工作于反向击穿区域。

反向击穿会导致二极管形成一条低阻抗的通路,将电流引流到地。

这将防止电流进一步沿着电路路径流动,保护后续电子元件免受损害。

ESD保护二极管具有快速响应时间和较高的耐受能力,能够

有效地吸收和分散ESD过电压,保护电子设备的稳定运行。

常见的ESD保护二极管包括Zener二极管和Avalanche二极管。

Zener二极管在正向工作模式下,具有特定的电压(即Zener

电压),当电压超过该值时,二极管将工作于反向击穿模式,并将电流引导到地。

这种二极管通常用于对较低电压的ESD

过电压进行保护。

Avalanche二极管在正向工作模式下,具有高压击穿电流和高

耐受电压能力。

它可以处理较高电压的ESD过电压,具有较

大的击穿电流和能量吸收能力。

ESD保护二极管通常安装在电路的输入/输出端口和敏感元件

周围,以最大程度地保护设备免受ESD损害。

同时,在电路

设计中,还可以采取其他的ESD保护措施,如使用避雷器、

滤波器等。

综合应用各种保护措施可以提供更全面的ESD保护,并确保电子设备的可靠性和稳定性。

esd芯片

esd芯片ESD芯片是一种专门设计用于保护电子产品免受静电放电(ESD)所引起的损害的芯片。

在现代电子设备中,静电放电是一个常见的问题,可以导致电子元件的损坏甚至完全失效。

因此,使用ESD芯片来提供保护是非常重要的。

ESD芯片的主要功能是通过吸收和分散静电放电,使其不会对电子元件产生任何有害的影响。

这些芯片通常被集成到电路板上,以提供对整个电子系统的保护。

它们具有很高的灵敏度,可以迅速地响应静电放电,并将其导向地面,从而防止其对电子元件的损坏。

ESD芯片通常由多个保护电路组成,每个电路都具有不同的保护特性。

其中一个常见的保护电路是二极管保护电路。

这种电路通过在电子元件和地之间放置二极管,将静电放电通向地面,防止其对电子元件的损害。

此外,ESD芯片还可以包含电阻、电容和放大器等其他电路,以提供更全面的保护。

ESD芯片还具有其他功能,例如过压保护和过流保护。

过压保护电路可以检测到电路中的过电压情况,并通过断开电路或将其导向地来防止对电子元件的损害。

过流保护电路则可以检测电路中的过电流情况,并采取相应的措施,以防止电子元件过载而损坏。

此外,ESD芯片还可以提供对电子系统在不同工作条件下的保护。

例如,在高温、低温或湿度环境下,电子元件对静电放电更加敏感。

ESD芯片可以根据不同的环境条件进行调整,以提供适当的保护。

总之,ESD芯片是一种专门设计用于保护电子产品免受静电放电所引起的损害的芯片。

它们具有高灵敏度和快速响应的特点,并通过吸收和分散静电放电,防止其对电子元件的损坏。

此外,ESD芯片还可以提供过压保护、过流保护和根据不同环境条件的保护。

这些特点使得ESD芯片在电子设备中非常重要,能够确保设备的稳定性和可靠性。

二极管esd保护原理与电路结构

二极管esd保护原理与电路结构

二极管ESD(静电放电)保护原理是利用二极管的特性,将ESD 电流通过二极管导通通路的方式,将静电电荷迅速引入地或电源线,从而保护被保护元件免受ESD的损害。

二极管ESD保护电路一般包括两个二极管以及一些辅助元件组成。

其中一个二极管作为负载二极管,负责接收ESD电流,另一个二极管则作为反向二极管,负责将ESD电流引入地或电源线。

辅助元件可以包括基准电阻、抑制电容等,用于实现对ESD电流的滤波、限流等功能。

常见的二极管ESD保护电路结构有以下几种:

1. 单向保护二极管结构:使用两个二极管分别连接在信号线与地线之间,通过引入地将ESD电流导向地。

2. 双向保护二极管结构:使用两个二极管连接在信号线和地线之间,一个二极管是正向导通的,另一个二极管是反向导通的,通过将ESD 电流引入地线或电源线保护信号线。

3. 串联二极管结构:将多个二极管串联在一起,通过增加二极管数量来提高ESD保护能力。

需要注意的是,二极管ESD保护电路的设计需要根据具体的应用场景和保护需求进行选择和优化,以确保有效地保护被保护元件免受ESD的损害。

ESD保护器件的主要特性参数分析及典型应用

ESD保护器件的主要特性参数分析及典型应用ESD保护器件是一种用于保护电子设备和电路免受静电放电损害的电子元件。

它们可以在电路中实现静电放电的引流和吸收,减小对IC器件的损害,提高系统的可靠性。

下面将对ESD保护器件的主要特性参数进行分析,并介绍其典型应用。

1. 静电放电等级 (ESD Rating):静电放电等级是ESD保护器件能够承受的最大静电放电能量。

该等级通常以KV表示,例如4KV。

ESD保护器件的静电放电等级决定了其能够保护器件免受不同程度静电放电的能力。

2. 保护电流 (Clamping Voltage):保护电流是指ESD保护器件在正常工作状态下对电路传导的最大电流。

当静电放电事件发生时,ESD保护器件能够引导其中大部分能量,并将其吸收释放。

保护电流的大小取决于ESD保护器件的设计和制造工艺。

3. 响应时间 (Response Time):响应时间是指ESD保护器件在检测到静电放电事件时,从无状态到达保护状态的时间。

较低的响应时间意味着ESD保护器件能更快地响应和吸收静电放电能量,从而减小对IC器件的损害。

4. 工作电流 (Operating Current):工作电流是指ESD保护器件在正常工作状态下的最大电流。

它通常取决于ESD保护器件的结构和材料。

典型应用:1.数字电路保护:ESD保护器件可以用于保护数字电路中的IC器件,如芯片、微控制器和FPGA等,免受静电放电损坏。

在数字电路中,静电放电可能导致芯片损坏、数据丢失或系统崩溃,使用ESD保护器件可以有效减小这些风险。

2.通信设备保护:ESD保护器件可以应用于通信设备中的接口和接口电路,如USB、HDMI、以太网和UART等。

这些接口通常需要与外部设备进行连接,而外部设备中的静电放电可能会对接口电路造成损坏,使用ESD保护器件可以防止这种损坏。

3.功率电子保护:ESD保护器件还可以应用于功率电子设备和电路中。

例如电源适配器、电池管理系统和电机驱动器等。

ESD保护元件的对比分析及大电流性能鉴定

ESD保护元件的对比分析及大电流性能鉴定ESD保护元件的对比分析及大电流性能鉴定在人们的日常工作生活中,静电放电(ESD)现象可谓无处不在,瞬间产生的上升时间低于纳秒(ns)、持续时间可达数百纳秒且高达数十安培的电流,会对手机、笔记本电脑等电子系统造成损伤。

对于电子系统设计人员而言,如果没有采取适当的ESD保护措施,所设计的电子产品就会有遭到损伤的可能。

因此,电子系统设计中的一项重要课题便是确保使其能够承受ESD的冲击,并继续正常工作。

ESD保护方法为了给电子系统提供ESD保护,可以从不同的角度来着手。

一种方法是在半导体芯片内建ESD保护架构。

不过,日趋缩小的CMOS芯片已经越来越不足以承受进行内部2 kV等级的ESD保护所需要的面积。

安森美半导体标准产品部亚太区市场营销副总裁麦满权指出:真正有效的ESD保护是不能完全集成到CMOS芯片之中的!其次,也可以在物理电路设计方面下功夫,较敏感的电路元件应该尽量远离通孔或接缝处,如果可能的话,线缆连接器的接地应该要在系统信号引脚接触前先连接到系统的接地,通过这样的方式,线缆上所发生的放电事件就比较不会造成干扰或破坏。

此外,软件也能够为ESD设计作出贡献。

系统连接的感测器比较容易受到ESD的冲击,造成接口电路的锁住情况,而能够感测锁住情况的软件则可以用来重置接口电路且无须操作人员的接入。

不过,总是有部分电路点较为敏感,同时也很难与外部隔离。

因此,最有效的方法是使用保护元件来将电流导离较敏感的元件。

也就是在电子系统的连接器或端口处放置ESD保护元件,使得电流流经保护元件,且不流经敏感元件,以维持敏感元件的低电压,使其免受ESD应力影响,进入有效控制ESD事件的发生,如图1所示。

当然,合格的ESD元件必须具有低泄漏和低电容,且在多重应力作用下功能不下降,从而不降低电路的功能。

图1:典型的ESD保护元件应用电路图常见ESD保护元件分类安森美半导体来自美国的ESD保护专家Robert Ashton博士说,一般而言,ESD 保护元件的分类可以通过其保护策略与方向性来进行,主要包括压敏电阻、聚合物和瞬态电压抑制器(TVS)等,如表1所示。

电路中的ESD保护

❖电路中的ESD保护ESD的意思是“静电释放".集成电路器件工作在一定的电压、电流和功耗限定范围内,大量聚集的静电荷在条件适宜是就会产生高压放电,静电放电通过器件引线的高压瞬时传送,可能会使氧化层断开,造成器件的功能失常。

静电的产生主要包括:摩擦起电、感应起电和接触起电。

ESD保护器件的原理,ESD保护二极管是一种新型的集成化的静电保护器件,其内部相当于是一个齐纳稳压二极管,当输入电流超过它的额定电压时,就会被击穿,把过多的电能量导回大地,以起到保护电路的作用。

ESD保护器件一般接在外部接口处,防止外部产生的静电对电路内部造成影响。

ESD器件的主要性能参数1、最大工作电压,即是允许长时间连续施加在保护器件两端的电压,在此工作状态下,ESD保护器件不导通,保持高祖状态。

2、击穿电压,即是ESD器件开始工作时的导通电压。

3、钳位电压,即是ESD器件流过峰值电流时,其两端呈现的电压,超过此电压,可能造成ESD器件的永久性损伤.4、漏电流,在指定的直流电压下,通过ESD器件的电流,一般是nA级的,此电流越小,对被保护电路的影响越小。

5、电容,在给定电压、频率条件下测得的值,此值越小,对被保护的信号传输影响就越小。

6、响应时间,指ESD器件对输入电压钳制到预定电压的时间。

ESD保护器件TVS管即瞬态抑制二极管是一种二极管形式的高效保护器件,利用P-N结的反向击穿工作原理,将静电高压导入大地,从而保护了电器内部对静电敏感的器件.当TVS二极管的瞬时电压超过电路正常工作电压时,TVS二极管便发生雪崩,提供给瞬时电流一个超低电阻通路,其结果就是瞬时电流通过二极管被引开,避开可被保护器件,并且在电路恢复正常值之前使被保护回路一直处于截止状态,当瞬时脉冲结束以后,TVS二极管自动回复高阻状态,整个回路进入正常电压. TVS二极管的工作特性曲线如下图所示TVS管的选型(1)、TVS的最大反向钳位电压应小于被保护电路的损坏电压。

静电放电(ESD)保护器件的模拟与仿真

编号本科生毕业设计(论文)题目:静电放电(ESD)保护器件的模拟与仿真物联网工程学院微电子学专业二〇一四年六月摘要静电放电(Electrostatic Discharge,ESD)是组成集成电路靠得住性的主要因素之一,存在于生产到利用的每一个环节,并成为开发新一代工艺技术的难点之一,最近几年来,对ESD的研究也因此愈来愈受到重视,仿真工具在ESD领域的应用使得ESD防护的研究变得更为便利,可大幅缩短研发周期.但是,由于ESD现象复杂的物理机制,极端的电场及温度条件,和ESD仿真中频繁的不收敛现象,都使得ESD的仿真变得极为困难.本文详细论述了ESD的来源、造成的危害和如何测试集成电路的防静电冲击能力,并基于Sentaurus软件,对ESD防护器件展开了的分析、研究,内容包括:1)掌握ESD保护的大体理论、测试方式和防护机理.2)研究了工艺仿真流程的步骤和网格概念在工艺仿真中的重要性,并对网格概念的方式进行了探讨.3)研究了器件仿真流程和器件仿真中的物理模型和模型函数,并对描述同一物理机制的的各类不同模型展开对比分析.主要包括传输方程模型、能带模型、各类迁移率退化模型、雪崩离化模型和复合模型.4)研究了双极型晶体管和可控硅(Silicon Controlled Rectifier,SCR)防护器件的仿真,并通过对仿真结果的分析,研究了ESD保护器件在ESD应力作用下的工作机理.关键词:静电放电;网格;器件仿真;双极型晶体管;可控硅ABSTRACTESD is one of the most important reliability problems of IC products which lies in every flow of IC production, and it is also one of the most difficult problems of developing new generation technology, therefore, the research on ESD protection design has attracted more and more attention. The applications of simulation tools on ESD area make the design of ESD protection devices more convenient, and greatly shorten the development cycle.However, due to the complicated physical mechanism of ESD, the extremely high field and high temperature when ESD happened, and the frequently convergence problem in ESD simulation, it becomes difficult to carry out the ESD simulation. So this paper particularly explain show ESD comes from, what harm will bring, how to test the integrated circuit's ability to prevent from the static, also concentrates on the simulation of ESD protection devices, based on the Sentaurus TCAD platform. And the main content of this paper include:First, this paper points out the basic theory, test methods and protective mechanism of ESD protection.Second, study the importance of the grid to define the steps and process simulation processes in the process simulation, and the method of the grid defined discussed.Third, in device simulation process and device simulation is studied in physical model and the model function, and to describe the same physical mechanism of the various models of comparative analysis. Mainly includes the transmission equation model, the energy band model, all kinds of mobility degradation model, avalanche ionization model and composite model.Forth, Study BJT and SCR protection device simulation, and the simulation results through analysis, research the working mechanism of the ESD protection device under ESD stress effects.Keyword: ESD; Grid; Device simulation; BJT; SCR目录摘要 (I)ABSTRACT (II)目录 (I)第1章绪论 (1)课题的研究背景及意义 (1)国内外概况 (1)本课题的研究内容 (2)第2章 ESD的常常利用保护器件及测试方式 (3)ESD简介 (3)ESD防护器件 (5)二极管的ESD防护器件 (5)NMOS管的ESD防护器件 (5)SCR的ESD防护器件 (7)ESD的测试方式 (8)ZAPMASTER的ESD测试方式 (10)TLP技术的ESD测试方式 (11)ZAPMASTER测试与TLP测试的关联性 (12)第3章 SENTAURUS软件仿真流程 (14)仿真工具简介 (14)工艺仿真 (14)工艺仿真流程 (15)结构操作及保留输出 (16)网格概念 (16)器件仿真及其物理模型的选择 (17)器件仿真流程 (17)物理模型选择 (18)第4章常常利用ESD防护器件的仿真与分析 (26)BJT的仿真与分析 (26)LSCR的仿真与分析 (28)N+_MLSCR的仿真与分析 (30)第5章结论与展望 (34)结论及不足的地方 (34)展望 (34)参考文献 (36)致谢 (37)第1章绪论课题的研究背景及意义随着集成电路朝着高性能大规模等方面迅速发展的同时,在所有集成电路的失效产品中,由于ESD造成的失效占据相当大的比例.因此,ESD保护器件的研究愈来愈受到人们的重视.ESD保护器件的工作原理为:在器件正常工作进程当中,ESD仅是表现为容值极低的(正常<5 pf)容抗特性,并非会对正常的器件特性产生影响,而且不会影响电子产品的信号及数据传输;当器件两头的过电压抵达预定的崩溃电压时,ESD防护器件快速(纳秒级)做出反馈,并放大极间漏电流通过,从而达到吸收、减弱静电对电路特性的干扰和影响.同时,因为ESD保护器件的组成材质十分特殊,ESD往往是通过对静电进行吸收和耗散,即表现为一个充放电的进程,达到对设备进行静电防护的作用,因此设备中的ESD保护器件都不容易老化损坏.可是,因为ESD现象所涉及的物理机制特别复杂,人工计算很宝贵到防护器件性能参数的精准值,仅能通过流片验证取得ESD防护器件的性能参数,但流片验证花费的大量时间将会使公司在激烈的竞争中处于不利的地位.因此在ESD领域中,工艺和器件模拟TCAD 仿真工具的应用慢慢被重视.目前,Sentaurus TCAD是世界上最先进的TCAD工具,它是Synopsys公司收购瑞士ISE(Integrated Systems Engineering)公司以后发布的产品.Sentaurus TCAD全方面继承了Tsuprem4、ISE TCAD和Medici的所有特性和优势,可以用来模拟仿真集成器件的工艺制造进程,器件物理特性和互连线特性等,它包括众多组件,主要由Sentaurus Process 模块、Sentaurus Strucure Editor模块、Sentaurus device模块、和Sentaurus Workbench 等模块组成.本论文中,通过利用Sentaurus TCAD仿真工具对ESD保护器件进行仿真,能够找出ESD现象的各个阶段器件内部的电场散布、电流密度及流向、温度散布和其他相关物里参量的转变,分析ESD器件在防护进程中的工作机理和失效原因,不但可以缩短研发时间,而且对研究工作具有极为重要的指导意义.国内外概况从20世纪80年代开始,国外的很多学者就开始注意到ESD现象并提出了一些减缓ESD 对IC芯片危害的办法,TCAD仿真工具也已经作为商业化的软件开始推行.随着集成电路快速发展的同时,集成电路中的ESD防护问题愈来愈严重,ESD的防护设计也愈来愈困难,只依托工程师的经验,很宝贵到适合的防护器件,而不断地流片验证又费时费力,因此在20世纪末21世纪初期,ESD研究和TCAD仿真软件开始真正结合起来.1991年,瑞士集成系统实验室的Andreas 等人开始了有关ESD仿真的研究,美国伊利诺斯大学的Alert 教授也开始利用混合仿真的方式研究ESD防护器件的性能,2001年,徳国汉堡大学的KAIESMARK等人利用直流仿真和单脉冲TLP波形的仿真系统研究GGNMOS (Gate-Grounded NMOS,栅接地NMOS)的性能,以后法国图卢兹的等人也有过相关方面的论文报导,美国中佛罗里达大学的教授也有相关方面的研究.以上的报导大体上是基于GGNMOS器件的仿真,或是在比较复杂的SCR器件基础上,利用单脉冲TLP(TransimmisonLine Pusle,传输线脉冲技术)波形仿真或混合仿真等方式,并非能对较复杂的SCR器件的性能做出准确的预测.国内对ESD的研究起步比较晚,很少有专门的ESD研究单位(除浙江大学和美国UCF 大学的ESD联合实验室外),但很多高校都在进行对于ESD防护相关问题的研究,对ESD 仿真研究的报导也偶尔可见[1-2],可是由于收敛性等方面的原因,目前国内对ESD仿真研究大体上是基于单脉冲TLP波形仿真,这种方式因为电压过冲等原因,并非能准确仿真触发电压等相关参数.本课题的研究内容本课题主要研究ESD防护器件的仿真,利用Sentaurus仿真工具,主要针对BJT和SCR 结构的防护器件进行仿真分析.本文的第二章介绍了ESD的大体概念,主要讲述ESD事件的模型、不同类型的ESD防护器件和测试方式;第三章介绍网格概念在工艺仿真中的作用、网格概念方式、各个工艺步骤模拟所用的模型,而且重点介绍了器件仿真的物理模型,讲述各类物理模型的适用条件,深切分析模型函数和不同模型之间的不同性;第四章主要讲述双极型晶体管和可控硅防护器件的仿真与分析,研究了ESD保护器件在ESD应力作用下的内部电场散布、电流密度及流向等相关物理参量的转变.第2章 ESD的常常利用保护器件及测试方式ESD简介静电是一种电能,它存在于物体表面,是正负电荷在局部失衡时产生的一种现象.静电现象是指电荷在产生与消失进程中所表现出的现象的总称,如摩擦起电就是一种静电现象.静电产生原因有接触分离起电、摩擦起电、感应起电和传导起电等.当带了静电荷的物体(也就是静电源)跟其它物体接触时,这两个具有不同静电电的物体依据电荷中和的原则,存在着电荷流动,传送足够的电量以抵消电压.这个高电量的传送进程中,将产生潜在的破坏电压、电流和电磁场,严重时将其中物体击这就是静电放电.国家标准是这样概念的:“静电放电:具有不同静电电位的物体彼此靠近或直接接触引发的电荷转移(GB/T4365---1995)”,一般用ESD表示.ESD是代表英文Electrostatic Discharge,即“静龟放电”的意思.它是EOS(electrical over-stress)的一种,EOS家族还包括闪电和电磁脉冲(electromagnetic pulses,EMP) .EOS是指那些时间在微秒和毫秒范围的事件,相较而言ESD是l00 ns的范围.ESD是现今MOS集成电路中最重要的靠得住性问题之一.高密度集成电路器件具有线问距短、线细、集成度高、运算速度快、低功率和输入阻抗高的特点,因此致使这种器件对静电较敏感,称之为静电敏感(ESD Sensitive,ESDS)器件.静电放电的能量,对传统的电子元件的影响甚微,人们不易觉察,可是这些高密度集成电路元件则可能因静电电场和静电放电电流引发失效,或造成难以被人们发现的“软击穿”现象,致使设备锁死、复位、数据丢失和不靠得住而影响设备正常工作,使设备靠得住性降低,乃至造成设备的损坏.集成电路工业由ESD致使的损失是一个超级严重的问题.基于ESD产生的原因及其对集成电路放电的不同方式,通常将静电放电事件分为以下三类模型:1)人体模型(Human Body Model, HBM)2)机械模型(Machine Model, MM)3)带电器件模型(Charged Device Model, CDM)HBM是目前最常常利用的模型,同时也是在产品的靠得住性查验中必需通过的检测项目.HBM是指因人体在地上走动磨擦或其它因素在人体上已积累了静电后接触芯片,人体上的静电就会刹时从芯片上的某个端口进入芯片内,再经由芯片的另一端口泄放至地,该放电的进程会在短到几百纳秒的时间内产生数安培的刹时电流,该电流会把芯片内的器件烧毁.有关于HBM的ESD已有工业测试的标准,它是现今各国用来判断集成电路ESD靠得住性的重要依据.图2-1为工业标准(MIL-STD-883C method 的等效电路图,其中人体的等效电容(CC )规定为100 pF,人体的等效放电电阻(RS)为1500 Ω.按照人体模型的测试标准MIL-STD-883C method ,其ESD的耐压敏感度可分成三个品级,见表2-1.Cc图2-1 被测器件在HBM,MM和CDM模型下的ESD应力波形产生的集总电路表2-1 人体模型的工业测试标准耐压级别耐压等级耐压灵敏度等级一0~1999 伏特等级二2000~3999 伏特等级三4000~15999 伏特MM及其标准由日本制定,在芯片的制造进程中,积累在机械手臂上的电荷接触芯片时通过芯片的管脚刹时泄放静电电流.由于大多数机械都是用金属制的,其机械放电模式的)规定为200 pF,因为机械放电模式的等效电阻等效电阻(Rs)约为0 Ω,但其等效电容(CC小,所以其放电的进程更短,在几纳秒到几十纳秒之内产生数安培的刹时电流.CDM是在芯片的制造和运输进程中因为摩擦生电积累静电荷,但在电积累的进程中集成电路并无被损伤.带有静电的芯片在处置进程中,当其管脚与地触的刹时,芯片内部的静电就会由经管脚向外泄放电流.此模式放电的时间更短,只有几纳秒之内,而且很难真实模拟其放电现象.由于芯片内部的静电会因为芯片器件本身地的等效电容而变,芯片所用的封装形式和芯片摆放的角度都会造成不同的等效电容.因为多项转变因素难以肯定,因此有关此模式放电的工业测试标准仍在协议中,但已有此测试机械在销售中.各模型的集总测试网络和其参数范围别离如图2-1和表2-2所示.CMOS集成电路对静电放电防护能力的规格见表2-3.表2-2 各类ESD测试模型的电感、电容、电阻参数值ESD Model Cc Ls Rs Cs CsHBM100pF5~12nH1500Ω1pF1pFMM200pFΩNA NACDM10pF<10nH<10ΩNA NA表2-3 集成电路产品的ESD规格ESD Model HBM MM CDMOK2000 V200 V1000 VSafe4000 V400 V1500 VSuper10000 V1000 V2000 VESD 防护器件二极管的ESD 防护器件二极管是最简单的有源电压箝位电路,它有正向和反向两个工作区域.在二极管两头加上正向电压时,二极管在 V 时开始导通,导通电阻约为1~5 Ω.在反向工作时,开始只有漏电流,电阻增大.当P-N 结雪崩击穿时产生倍增电流,雪崩电压与N 或P 的搀杂浓度有关,在深亚微米工艺中,一般为10~20 V.二极管在小注入时,I-V 特性与搀杂浓度有关;当大注入时,阱区往往进入电导调制区,I-V 特性与搀杂浓度无关.图2-2所示的两种常常利用P-N 结二极管的横截面结构图.图2-2(a) 结面积小的二极管结构图 图2-2(b) 结面积大的二极管结构图图2-2 常常利用P-N 结二级管的横截面结构图以上两种结构的结面积不同,由于图2-2(b)结构的P-N 结面积更大,使ESD 能量释放时,能量密度较小,具有更强的ESD 保护能力,在实际应历时常常采用这种结构的二极管. NMOS 管的ESD 防护器件栅极接地NMOS 晶体管是最常常利用的ESD 防护器件之一.GGNMOS 晶体管的栅极、源极和衬底都是接地的,其ESD 保护机制基于负阻效应(Snapback Effect).图2-3所示的是一个GGNMOS 晶体管器件的横截面图.从图中可以看到,NMOS 晶体管存在一个寄生横向NPN 晶体管,其集电极为NMOS 晶体管的漏极,发射极为NMOS 晶体管器件的源极,基极为NMOS 晶体管的P 型衬底.当一个正向的ESD 脉冲作用于器件的漏极,这会使得漏衬结(DB 结)一直处于反向偏置直到发生雪崩击穿,此时由于发生雪崩倍增效应而会产生大量的电子空穴对.当雪崩效应产生的空穴电流I sub 通过衬底流向地的时候,会在横向寄生衬底电阻R sub 的两头产生一个电压降,该压降会使得衬底局部电势V R 上升.随着V R 上升,源衬结(BS 结)导通,最终触发寄生的横向NPN 晶体管导通,当寄生横向NPN 晶体管导通后,已再也不需要一个很强的漏极电场将离子注入到漏极来产生较大的电流,这就会使得漏极电压下降,从而发生负阻现象(Snapback Effect).负阻区处于不稳定状态,只是高阻区和低阻区两个稳定区之间的过渡.一旦寄生横向NPN 晶体管导通后,由于衬底的电导调制作用,电阻又变成正值.当电流进一步增大,产生自加热,使器件内部温度升高.当达到硅的熔点1685℃时,器件会发生不可逆转的转变,器件会受到损伤,该现象称为二次击穿或热击穿.图2-3 栅极接地NMOS晶体管器件的横截面示用意VDIDBVox1区3区4区1/Ron(It2,Vt2)(It1,Vt2)(Ih,Vh)图2-4 典型GGNMOS晶体管器件的I-V特性曲线GGNMOS晶体管的I-V特性曲线如图2-4所示,该曲线可以分成4个工作区域:1区和2区别离为线性区和饱和区,这两个区的I-V曲线可以用标准NMOS的I-V公式来进行描述;3区为负阻区,4区为高电流区,这两个区的I-V曲线已不能用标准NMOS的I-V公式来进行描述.在发生ESD时,GGNMOS晶体管工作于3区和4区.图2-4同时也表示了利用传输线脉冲(TLP)技术进行测量而取得的典型GGNMOS晶体管的负阻特性曲线.该曲线所反映出的负阻特性参数,如Vt1、Vh、It2和Ron等,这些参数对于器件ESD失效阈值电压(ESDV)大小的测量是超级关键的:1)(It1,Vt1)是第一次击穿触发点,该点决定了ESD保护器件在何时将开启.Vt1可以如式(2-1)表达.()nI I R q T K BV V 11111⎪⎪⎪⎪⎪⎭⎫ ⎝⎛⎪⎪⎭⎫ ⎝⎛++*-*=dc c sub B BD ti α (2-1) 必需使开启电压V t1低于栅氧化层击穿电压BV ox ,同时必需使开启电压V t1高于最差情况下的电源电压VDD ,并留有必然的设计裕度(VDD+10%),避免由于电源过冲噪声而引发意外的击穿触发.在实际ESD 保护电路设计,一般通过提高衬底电压或栅极电压,来降低V t 的值;2) (I h ,V h )是维持点,是低阻ESD 电流开始泄放的起始点.采用较低的V h 值确保适当的电压钳位,避免内部器件的栅氧化层被击穿,同时可以减少ESD 电流泄放时的电源功率消耗(Power=V h *I ESD ).维持电压V h 应该高于电源电压以避免发生闩锁效应;3) R on 是导通电阻,其表达如式(2-2):ds ds on I V R ∂∂= (2-2) 尽可能小的导通电阻R on 可确保该ESD 器件具有较大的电流泄放能力,同时可以避免器件过早热击穿;4) (I t2,V t2)为器件的二次击穿点,器件ESDV 电压值的大小可由二次击穿电流I t2来表示.对于HBM 测试下的GGNMOS ESD 器件,其ESDV 电压值的近似表达如式(2-3):()t2on Level ESD HBW I R V ⨯+=1500 (2-3)由GGNMOS 晶体管的负阻(Snapback)特性曲线,设计者可以在硅验证之前预测出对应于HBM 模型的ESDV 电压值.SCR 的ESD 防护器件由于可控硅(Semiconductor controlled Rectifiers ,SCR )触发前后,电阻转变很大,所以在功率器件中,用来承载大电流.一样SCR 可以用于设计ESD 保护结构,其结构和等效线路图如图2-5所示.AnodeT1T1T2RnwellRpwellCathode图2-5(a) SCR 的截面图 图2-5(b) SCR 结构的等效线路图图2-5 SCR 结构的截面图和等效线路图SCR在ESD冲击发生时也作为一个二端网络,其中阳极(Anode)和N阱短接,阴极(Cathode)和P阱短接.Anode与静电源相接,当ESD冲击发生时,加在N阱和P阱的P-N 结上的反向电压降足以使P-N结雪崩击穿.雪崩击穿后,SCR触发将有两种可能:1)雪崩击穿产生的空穴电流流过P阱体电阻RP-WELL,使P衬底电压升高,寄生的NPN 管开启.2)雪崩击穿产生的电子电流流过N阱体电阻RN-WELL,使寄生的PNP的EB结正偏,PNP 导通.通常NPN管的β高于PNP管的β,所以NPN管比PNP管更易开启.VTRIG为N阱和P阱的P-N结雪崩击穿电压.通常N阱/P阱的击穿电压在40V,一旦触发,再也不需要Anode 上提供偏置,二端点的电压V开始降低,V的最小值概念为需要提供足够的电流流过P阱体电阻以保证NPN管导通,VH与NPN管和PNP管的基区宽度L有关,对应的I-V曲线如图2-6所示.I图2-6 SCR的回扫特性曲线SCR有两个重要参数,ITRIG 和由P阱体电阻,即外延层厚度和P阱的搀杂浓度决定,VH与L和N阱体电阻有关.此刻的CMOS工艺中,VH的典型值为2~5V,由于SCR一旦触发,Anode和Cathode之间完全处于电导调制区,导通电阻仅为1Ω,作为ESD保护电路时,能很好地耗散能量.以上介绍了各类器件在ESD情况下表现的特性.在设计ESD保护电路结构时,就是利用器件的这些特性,按照不同的要求或工艺条件,选用不同的器件来实现符合要求的ESD 保护结构.例如,NMOS和SCR在ESD条件在都可能触发还归击穿,在CMOS工艺时可用NMOS 的回归特性来作ESD保护,但如果要求有更快的保护速度,可考虑用SCR来实现ESD保护结构.ESD的测试方式ESD的测试可以分为查验型测试和研究型测试两类.查验型测试体此刻产品的后端靠得住性测试中,为了保证芯片产品的优良率,在产品的靠得住性查验中,ESD查验是一个重要环节,以集成电路中的人体模型工业测试标准(见表2-3),芯片通过必然值(一般为2 kV)的ESD查验才算合格.当前芯片的ESD查验大多采用ZAPMASTER测试仪.系统级的ESD查验大多采用电子枪.研究型测试偏重于芯片研发的前期,为了预测产品的ESD经受能力,从根本上保证芯片产品的优良率,以降低封装及测试本钱并提高产品的研发效率,就必需在芯片的研发前期为芯片设计良好的ESD防护器件,而不是在产品的靠得住性实验中发现问题以后再补救.为了取得ESD防护器件的关键性能指标,TLP是研究型测试中不可缺少的一种手腕.无论是查验型测试仍是研究型测试,都基于下面三种测试连接模式[3]:1)I/O口到VDD或VSS的测试:通常包括PS、PD、NS和ND模式.其中P代表Positive,表示引脚接的是正电压,N代表Negative,表示引脚接的是负电压.D和S别离代表VDD和VSS,表示的是参考点的选择,实际测试时,参考点接地.PS是对VSS是正脉冲,PD是对VDD的正脉冲,NS是对VSS的负脉冲,ND是对VDD的负脉冲.这四种测试连接方式示用意如图2-7所示.图2-7(a) PS测试模式图图2-7(b) PD测试模式图图2-7(c) NS测试模式图图2-7(d) ND测试模式图图2-7 I/O口的四种测试连接模式2)I/O到I/O的测试,包括正向和负向的电压,被测引脚接测试电压,其他接地,VDD和VSS悬空,如图2-8所示.图2-8(a) 正电压模式图2-8(b) 负电压模式图2-8 I/O到I/O的测试连接模式3)VDD到VSS的测试,包括正向和负向的电压,如图2-9所示.图2-9(a) 正电压模式图2-9(b) 负电压模式图2-9 VDD到VSS的测试连接模式ZAPMASTER的ESD测试方式不同的测试标准对应不同的测试模型,同一测试模型可以对应多种测试标准.工业界商用的ESD测试仪器有很多种.本文中采用Thermo KeyTek公司生产的ZAPMASTER测试系统对HBM模型进行ESD测试,ZAPMASTER测试设备由中国电子科技集团第五十八研究所提供.对应的测试标准为GJB548A方式3015.短路测试波形要求上升时间小于10 ns,下降时间大约为150±20 ns.每次测试在管脚正负冲击三次,冲击时间距离为一秒.2000 V的HBM 电压相当于 A的尖峰电流.ESD冲击测试是检测IC的ESD耐压,而不是洞察其失效机理,因为它仅仅是报告芯片是不是能通过给定ESD电压冲击值.按照具体要求,通过在电脑终端软件设定ZAPMASTER可以对IC产品进行步进电压或恒定电压的ESD查验.从查验报告单中可得知各个失效的管脚组合和可能失效的三种模式.这三种失效模式别离为:开路失效(OC)、包络线失效(ENV)和短路失效(SG).当被冲击管脚之间加上的电压为工作电压的倍时,直流通路电流达到1μA时概念为失效,包络线的有效范围是指在概念的失效电流正负15%的偏移范围之间.失效电流的检测可以通过电脑终端设置在每三个正负脉冲冲击完毕后检测,或只在单个正或负脉冲冲击完毕后检测. TLP技术的ESD测试方式芯片的ZAPMASTER ESD质量检测取得的只是其ESD耐压.要优化器件的ESD防护性能需要全面掌握防护器件的电学参数,而且一种典型的描述模型或单个工作优良系数并非能保证其能通过所有的EOS/ESD故障.例如一个芯片通过了CDM模型检测却在做HBM模型检测时失效.乃至器件在HBM模型测试下有1 kV和2~6 kV的ESD耐压,却在1~2 kV的范围内失效[4].如何准确测量ESD的有关参数尤其重要.因为直流大电流会引发器件的自加热,不能代表ESD事件的瞬态特性,因此在ESD防护器件的研究中,脉冲特性是必要的.器件在ESD事件下,其电流电压和时间的特性称为动态或准静态特性,在研发ESD防护器件中,TLP技术是一个必备手腕.图2-10描述了待测器(Device Under Test,DUT)的脉冲特性,递增的脉冲信号加载在DUT上,此处为一个回滞(Snapback)特性的NMOS管防护器件.从其TLP I-V曲线中可知此NMOS管的触发点,维持点和热击穿点,和NMOS管的导通电阻和漏电流[4].图2-10 持续脉冲方波的脉冲特性原理4002型TLP测试仪是美国Barth电子公司制造的,其主要组成部份有:Barth 40031传输线脉冲产生器控制盒、Tekronix 500 MHz数字示波器、Keithley 487皮安/电压源和斯坦福PS350高压电源供给器.其系统构架通过通用仪器总线(GPIB)由控制器控制,系统框图如图2-11所示.4002型TLP测试系统产生的脉冲波的上升时间可调整为 ns,2 ns和10 ns,脉宽可调为75 ns或100 ns.脉冲信号通过传输线传出,可对圆片或封装好的测试器件或芯片进行测试.图2-11 Barth 4002型传输线脉冲测试系统框图ZAPMASTER测试与TLP测试的关联性一般来讲,由于封装好的芯片在管脚处的部份寄生电容和电感可以减小内部ESD防护器件的ESD敏感度,ZAPMASTER的芯片测试结果常优于TLP的WAFER测试结果.表2-4比较了同一器件的ZAPMASTER测试结果和从TLP测试结果换算的耐压值.ZAPMASTER的测试采用人体模型国军标548A-96测试方式,电压以500 V步进从500 V到6500 V,恒定正脉冲冲击.TLP的测试采用Barth 4002型TLP测试系统的默许模式,即脉冲的上升时间为10 ns,).通过人脉宽为100 ns,脉冲电压从 V开始递增一直到器件失效,取得热击穿电流值(It2).可见体模型的转化公式TLPV(v)≈la(A)X(1500+Ron)(Ω),计算取得TLP耐压值(Vt2 ZAPMASTER的测试结果优于TLP的测试结果,由于ZAPMASTER测试的步进电压为500 V,所以误差在1000 V内是合理的.实验中的失效模式都为短路.表2-4 ZAPMASTER和TLP测试的关联性比较DUT It2(A)TLPV(V)ESDV(V)DIODE41515000GGNMOS23573000。

静电放电电阻电容

静电放电电阻电容

静电放电电阻和电容是两种不同的电子元件,它们在静电放电(ESD)保护电路中都起到关键作用。

1. 静电放电电阻:ESD放电电阻是指在静电放电过程中起到限制电流流动的作用。

它是保护电子器件的关键组成部分。

ESD放电电阻的阻值通常在几十到几百欧姆之间。

当静电放电发生时,ESD放电电阻可以通过限制电流的大小来保护器件免受损坏。

ESD放电电阻的阻值越小,其对电子器件的保护作用越好。

2. 静电放电电容:在潜在损坏的情况下,ESD事件不会被注意到,并且设备会继续正常运行,但会受到中度损坏。

潜在损坏会缩短电子元件的负载寿命,对受ESD影响的元件施加操作应力最终会导致性能退化和器件故障。

这种类型的ESD损坏在重新测量和目视检查中无法检测到。

总的来说,静电放电电阻和电容都是为了防止电子设备受到静电放电

的影响。

但请注意,以上信息仅供参考,如有需要,建议咨询专业技术人员。

esd电阻

ESD电阻简介ESD(Electrostatic Discharge)电阻是一种用于保护电子设备免受静电放电影响的特殊电阻。

静电放电是指当人体与物体摩擦或接触时,产生静电并导致电荷的不平衡,进而形成放电的现象。

静电放电可能会对电子设备造成严重的损害,甚至损坏IC芯片等关键部件。

为了防止静电放电对电子设备的影响,ESD电阻被设计用来吸收和分散放电过电流,从而保护电子元件和电路不受损害。

ESD电阻通常被用作保护电路的一部分,以确保设备在遭受静电放电时能够继续正常工作。

ESD电阻的工作原理ESD电阻基于电阻元件的原理来工作。

它内部包含一个由金属或碳材料制成的电阻体,该电阻体的电阻值可以根据需要进行调整。

当静电放电发生时,ESD电阻会将放电电流导向电阻体,通过其分散和吸收这些过电流,从而保护设备免受损害。

此外,ESD电阻还具有二极管特性。

当静电放电电压超过其正常工作电压时,ESD电阻的二极管将被激活,形成一条低阻路径,将电荷流导向地。

这种二极管的特性可以额外地保护设备免受高压静电放电的威胁。

ESD电阻的应用ESD电阻广泛应用于各种电子设备和电路中,主要用于保护集成电路、传感器、触摸屏、存储器等对静电放电特别敏感的部件。

一些常见的应用场景包括: - 电子产品:智能手机、平板电脑、计算机等消费类电子设备中,ESD电阻常用于保护触摸屏、IC芯片和其他关键元件。

- 工业控制设备:在工业环境中,静电放电也是一个常见的问题。

ESD电阻可用于保护工业自动化设备、传感器和PLC等设备。

- 医疗设备:静电放电可能对医疗设备的可靠性产生负面影响。

因此,ESD电阻被广泛应用于各种医疗设备,如心电图仪、手术器械等。

ESD电阻的选择和参数选择合适的ESD电阻通常需要考虑以下几个参数: - 阻值(Resistance):ESD电阻的阻值应根据应用需求进行选择。

阻值的选取决定了ESD电阻在电路中的功耗和保护性能。

- 频率特性(Frequency Characteristics):ESD电阻的频率响应特性直接影响其工作在不同频率下的效果。

静电放电(ESD)保护器件的模拟与仿真.

First, this paper points outthe basic theory, test methods and protective mechanism of ESD protection.

Second, study the importance of the grid to define the steps and process simulation processes in the process simulation, and the method of the grid defined discussed.

Keyword:ESD;Grid; Device simulation;BJT;SCR

第

1.1课题的研究背景及意义

随着集成电路朝着高性能大规模等方面迅速发展的同时,在所有集成电路的失效产品中,由于ESD造成的失效占据相当大的比例.因此,ESD保护器件的研究越来越受到人们的重视.ESD保护器件的工作原理为:在器件正常工作过程当中,ESD仅是表现为容值极低的(正常<5 pf)容抗特性,并不会对正常的器件特性产生影响,并且不会影响电子产品的信号及数据传输;当器件两端的过电压到达预定的崩溃电压时,ESD防护器件快速(纳秒级)做出反馈,并放大极间漏电流通过,从而达到吸收、削弱静电对电路特性的干扰和影响.同时,因为ESD保护器件的构成材质十分特殊,ESD往往是通过对静电进行吸收和耗散,即表现为一个充放电的过程,达到对设备进行静电防护的作用,因此设备中的ESD保护器件都不容易老化损坏.

esd clamp原理

ESD Clamp原理解析什么是ESD?ESD(Electrostatic Discharge)是静电放电的缩写,指的是电荷由一个物体传递到另一个物体的过程。

当两个物体之间存在电势差时,静电放电就会发生。

静电放电可以引起许多问题,尤其是对于电子设备来说,静电放电可能会导致设备损坏或故障。

为什么需要ESD Clamp?静电放电对电子设备的损害是非常严重的。

在电子设备制造和使用过程中,由于人体或其他物体的静电放电,可能会产生高达数千伏的电压。

这种高电压会导致电子元件受损,甚至完全烧毁。

因此,为了保护电子设备免受静电放电的影响,需要采取措施来限制和控制静电放电。

ESD Clamp是一种用于保护电子设备的电路器件,其主要功能是在静电放电过程中提供一条低阻抗的路径,将静电放电电流引导到地,从而保护电子设备免受静电放电的影响。

ESD Clamp通常用于电子设备的输入/输出端口或电源线路,以限制和消除静电放电。

ESD Clamp的基本原理ESD Clamp的基本原理是通过将一个或多个二极管连接到电路中,在静电放电时提供一条低阻抗的路径,将静电放电电流引导到地。

ESD Clamp通常由两个主要部分组成:二极管和电阻。

1. 二极管二极管是ESD Clamp的核心部件之一。

它的作用是在静电放电过程中提供一条低阻抗的通路,将静电放电电流引导到地。

在正常工作状态下,二极管处于高阻抗状态,不会对信号产生影响。

但是,当静电放电时,二极管会迅速变为低阻抗状态,形成一条通路,将静电放电电流引导到地,从而保护电子设备。

2. 电阻电阻是ESD Clamp的另一个重要组成部分。

它的作用是限制静电放电过程中的电流。

在正常工作状态下,电阻的阻值相对较大,不会对信号产生较大的影响。

但是,在静电放电时,电阻的阻值会变得较小,以便通过电阻引导静电放电电流。

电阻的选择需要根据具体应用场景和要求进行,以确保能够在静电放电时提供足够的电流引导能力。

静电保护二极管符号

静电保护二极管(ESD diode)的符号和应用静电保护二极管是一种用于保护电子元器件免受静电放电(Electrostatic Discharge,简称ESD)损害的设备。

它具有很高的反向击穿电压,可以快速地将静电释放到地线,从而保护电路中的敏感元件。

在电子设备中广泛使用了静电保护二极管,以防止静电对电路产生严重的影响。

静电保护二极管的符号静电保护二极管的符号如下所示:|-----|------ 接地线|符号中的横线代表二极管,而下方的直线表示接地线。

这是一种简化表示方法,用于表示该二极管用于将静电放电到接地线。

静电保护二极管的工作原理静电保护二极管的工作原理基于二极管的特性。

二极管是一种具有两个电极(也称为端子)的电子元件,分别为正极(Anode)和负极(Cathode)。

当正极电压高于负极电压时,二极管处于导通状态;当负极电压高于正极电压时,二极管处于截止状态。

静电保护二极管的正极通常连接到需要保护的电路,而负极通过接地线与地线连接。

当静电放电发生时,负极电压会迅速上升,导致二极管处于导通状态。

由于静电保护二极管具有很高的反向击穿电压,它可以承受静电放电产生的高电压,同时将静电放电流快速地引导到接地线,从而保护电路中的敏感元件。

静电保护二极管的应用静电保护二极管在电子设备中应用广泛,特别是用于保护敏感电子元件、集成电路和其他高频或高精度电路。

以下是一些常见的应用场景:1.通信设备:静电保护二极管可以用于保护电信设备中的射频电路、天线端口和其他高频信号处理电路。

它们能够预防静电放电对设备造成的干扰和损坏。

2.电脑和移动设备:静电保护二极管常常用于保护计算机、笔记本电脑和智能手机等设备中的各种接口,如USB、HDMI、以太网等。

这些设备对静电非常敏感,因此需要静电保护二极管来防止静电损害和干扰。

3.工业自动化设备:在工业环境中,静电放电会对自动化设备和控制系统产生不良影响。

静电保护二极管可用于保护传感器、执行器、PLC等设备的输入输出接口,确保它们的可靠工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ESD

ESD

ElectroStatic Discharge Protection Devices

ElectroStatic Discharge Protection Devices

静电放电保护元件

静电放电保护元件

1.结构

专用于静电放电保护的过压保护器件,存在分立式和阵列式两种,内部主要是有TVS的阵列构成。

2.特点

专用于ESD防护的限压型过压保护器

反应速度小于0.5ns;

导通击穿电压低;

体积小,集成度高,可以同时保护多条数据线路;

一般电压规格有2.8V、3.3V、5V、12V、15V、24V、36V;

电容值低,可达0..4pF,是理想的数据线保护器材;

漏电流低,一般在几个µA甚至更低;

封装多样化有SOT-323 SOT-23 SOT-143 SOT-353 SOT-363 SOT23-6L SOT23-6L SOIC-08 SOIC-16 SOD-923 SOD-723 SOD-523 SOD-323 SOD-123。

ESD U-I特性曲线

3.技术参数

P PPM(Peak Pulse Power 额定脉冲峰值功率):可施加的不引起ESD器件失效的脉冲峰值功率最大值。

V RWM(Reverse Stand-off V oltage截止电压):ESD元件无明显动作的最大电压

V BR(Breakdown V oltage击穿电压):在规定的脉冲直流电流I BR或接近发生雪崩的电流条件下,ESD浅见两端的电压

I BR(Breakdown Current 击穿电流):测试V BR大小的脉冲直流电流。

V C(Maximum Clamping V oltage 钳位电压):施加规定波形的脉冲峰值电流I PP时,ESD器件两端测得的峰值电压

I R(Reverse Leakage 漏电流):在截止电压V RWM下,流过ESD器件I/O口的电流。

C J(Typical Capacitance典型电容值):ESD端口间的极间电容值。

4.命名方式

SET23A05L02

S:表示电容为标准型,电容值大于30pF(L:电容值大于5pF,小于30pF)

(U:电容值小于5pF)E:表示功率,用A,B,C,D…依次表示小于100W,200W,300W,400W…;

T23:表示封装为SOT-23;

A:表示为单向保护(C表示双向);

05:表示截止电压为5V;

L02:表示对地保护线路数。

5.封装类型

T32 SOT-323 T23 SOT-23

T14 SOT-143 T35 SOT-353

T36 SOT-363 T25 SOT23-5L

T26 SOT23-6L S08 SOIC-08

S14 SOIC-14 S16 SOIC-16

D92 SOD-923 D72 SOD-723

D52 SOD-523 D32 SOD-323

D12 SOD-123

6.应用

专用于静电放电保护的限压型过压保护器件,可以用在各种电子产品,集成电路,对低能量的浪涌也有一定的保护作用。

7.选型规则

1.截止电压要大于线路上的最大正常工作电压;

2.最大箝位电压要低于被保护器件的最大安全电压;

3.高频电路中,电容值大小不要影响线路正常工作;

4.瞬态功率要大于外界有可能出现的最大异常瞬态功率;

5.封装大小是否适合于线路的设计与安装原则。