8位CPU的设计

8位移位寄存器的电路设计与版图实现要点

8位移位寄存器的电路设计与版图实现要点8位移位寄存器的电路设计与版图实现摘要电⼦设计⾃动化,缩写为EDA,主要是以计算机为主要⼯具,⽽Tanner EDA则是⼀种在计算机windows平台上完成集成电路设计的⼀种软件,基本包括S-Edit,T-Spice,W-Edit,L-Edit与LVS等⼦软件,其S-Edit以及L-Edit为常⽤软件,前者主要实现电路设计,后者主要针对的是已知电路的版图绘制,⽽T-Spice主要可实现电路图及版图的仿真,可以⽤Tanner EDA实现电路的设计布局以及版图实现等⼀系列完整过程。

本⽂⽤Tanner EDA⼯具主要设计的是8位移位寄存器,移位寄存器主要是⽤来实现数据的并⾏和串⾏之间的转换以及对数据进⾏运算或专业处理的⼯具,主要结构构成是触发器,触发器是具有储存功能的,可以⽤来储存多进制代码,⼀般N 位寄存器就是由N个触发器构成,移位寄存器⼯作原理主要是数据在其脉冲的作⽤下实现左移或者右移的效果,输⼊输出的⽅式表现为串⾏及并⾏⾃由组合,本设计就是在Tanner EDA的软件平台上进⾏对8位移位寄存器的电路设计仿真,再根据电路图在专门的L-Edit 平台上完成此电路的版图实现,直⾄完成的结果和预期结果保持⼀致。

关键词:Tanner EDA;L-Edit;移位寄存器,S-Edit8 bits shift register circuit design and layoutAbstractElectronic design automation,referred to as EDA,it is based on computers as the main tool,and Tanner EDA is a kind of software that complete the integrated circuit design on Windows platforms.Its Sub-Softwares include S-Edit,T-Spice,W-Edit,L-Edit and LVS and so on.S-Edit and L-Edit are commonly used software,S-Edit is primarily designed to achieve circuit,the latter is aimed primarily known circuit layout drawing,T-Spice can achieve schematic and layout simulation.We can achieve layout of the circuit design and a series of complete process layout used Tanner EDA tools.In this paper, Tanner EDA tools are mainly designed an 8-bit shift register.The shift register is mainly used for data conversion between parallel and serial, and the data processing tool operation or professional,its main structure is the trigger composition,flip-flop is a storage function,it can be used to store more hexadecimal code,In general N-bits register is composed of N trigger.Working principle of the shift register data under the action of the pulse, mainly the effect of the shift to the left or right,input and output of the way of serial and parallel free combination.This design is in Tanner on the EDA software platform to 8 bits shift register circuit design and simulation,then according to the circuit diagram on special L - Edit platform to complete the circuit layout implementation,until the finish is consistent with the results and expected results.Keywords:Tanner EDA;L-Edit;Shift register,S-Edit⽬录1 前⾔ (1)1.1 课题的背景和⽬的 (1)1.2课题的设计内容 (1)2 设计软件简介 (2)2.1EDA技术的介绍 (2)2.2T ANNER EDA T OOLS的简述 (2)2.3T ANNER软件的组成及发展 (3)2.3.1 Tanner的设计流程 (4)2.3.2 Tanner软件的发展 (5)2.3.3 L-Edit软件的介绍 (6)2.48位移位寄存器的⼯作原理和设计要求 (9)2.4.1 ⼯作原理 (9)2.4.2 电路结构与设计 (11)3 8位移位寄存器的电路设计与版图实现过程 (13)3.1各个模块的设计与仿真 (13)3.1.1 带复位端D触发器的设计与版图实现 (13)3.1.2 与或⾮门的设计与版图实现 (16)3.28位移位寄存器的电路设计与版图实现 (18)3.2.1 8位移位寄存器的电路结构 (18)3.2.2 8位移位寄存器的版图实现 (19)3.2.3 LVS对⽐ (21)4 结束语 (21)参考⽂献 (22)巢湖学院2013届本科毕业论⽂(设计)1 前⾔1.1 课题的背景和⽬的随着科技的进步,近⼏个世纪寄存器技术不断成熟,在数字电路中,寄存器已经是⼀个经常被提出的概念,它主要指的是⽤来存放⼆进制数据或者代码的电路。

简单cpu的电路连接图

使用MAX+PLUS II绘制CPU中的部分电路选下列题目之一进行实验:(每个实验都有一项要求是属于较高要求选作的)1、绘制“非常简单CPU”数据通路2、绘制移位——相加乘法电路附1:绘制“非常简单CPU”数据通路在实验资料中已给出6位寄存器、6位计数器两个元件的设计文件:reg6.gdf和cou6.gdf。

绘制“非常简单CPU”数据通路步骤及指导:非常简单CPU的寄存器:一个8位累加器AC,一个6位的地址寄存器AR,一个6位的程序计数器PC,一个8位的数据寄存器DR,一个2位的指令寄存器IR。

其数据通路详见教材。

1、零件制作6位寄存器reg6.gdf (自行设计)类似于8位寄存器,6位寄存器是由6个d触发器连接成的6位计数器cou6.gdf (自行设计)8位寄存器(可选择74系列宏函数74273)将八个d触发器如图连接起来,构成八位寄存器8位计数器(由两个74161构成)2位寄存器(由D触发器构成,自行设计)6三态缓冲器(自行设计,可由74244内部逻辑修改而成)8三态缓冲器(选择74系列宏函数74244,或作修改)alu模块(自行设计,限于时间,其内部逻辑不作要求)此为选择器,根据ttl选择的已有器件此为两个加法器相连,充当alu部分的八位并行加法器此为八位与门此为alu整体部件的电路图2、选择器件,加入数据通路顶层图8位累加器AC:选择8位计数器6位地址寄存器AR:reg66位的程序计数器PC:cou68位的数据寄存器DR:选择8位寄存器2位的指令寄存器IR:选择2位寄存器3、为PC、DR加入三态缓冲器。

4、调整版面大小,器件位置。

5、设计地址引脚、数据引脚、8位内部总线,加入数据引脚到内部总线的缓冲器。

6、连接各器件之间以及到内部总线的线路,设计并标注各控制信号。

7、实验报告中应给出各元部件的实现方法、内部逻辑贴图、打包符号说明及顶层的“非常简单CPU”数据通路图。

下图即为简单cpu的连接图,并通过编译。

8位骨灰级CPU电路图

9 10

12 13

2 1

1 2 13

U 29A 12 74F 10

Y1

1 3 74F 02 U 24B 5 4 6 74F 02 U 24C 8 10 9 74F 02

R1 锁存

3 1 74F 86

DB 7 DB 6 DB 5 DB 4

DB 3 DB 2 DB 1 DB 0

DB 7 DB 6 DB 5 DB 4 DB 3 DB 2 DB 1 DB 0

19 16 15 12 9 6 5 2

U 10E 74F 04 10 12

U 10F 74F 04 8

2Y 4 2Y 3 2Y 2 2Y 1

6

8

6

B4 B3 B2 B1 2G

17 15 13 11 19

A LU _A7 A LU _A6 A LU _A5 A LU _A4 A LU _A3 A LU _A2 A LU _A1 A LU _A0

3 5 7 9

12 14 16 18

2

U 11B 74F 20

U 26A 74F 20

U 27 74F 30

U 26B 74F 20

U 28A 74F 20

U 23B 74F 00

B

11

3

3 5 7 9

1 2

4 5

1 2 3 4

1 2

4 5

4

累加器到 RA M 传送指令 累加器到寄存器传送指令 加法指令

8 13 12

8 10 74F 32

A4 A3 A2 A1 1G

执行1电平 2

执行 1脉冲3

U 4C 9

1 11

3 4 7 8 13 14 17 18

3 5 7 9

8位CPU的设计与实现

计算机组成原理实验题目8位CPU得系统设计学号1115106046姓名魏忠淋班级 11电子B 班指导老师凌朝东华侨大学电子工程系8位CPU得系统设计一、实验要求与任务完成从指令系统到CPU得设计,编写测试程序,通过运行测试程序对CPU设计进行正确性评定。

具体内容包括:典型指令系统(包括运算类、转移类、访存类)设计;CPU结构设计;规则文件与调试程序设计;CPU调试及测试程序运行。

1。

1设计指标能实现加减法、左右移位、逻辑运算、数据存取、有无条件跳转、内存访问等指令;1、2设计要求画出电路原理图、仿真波形图;二、CPU得组成结构三、元器件得选择1.运算部件(ALU)ALU181得程序代码:LIBRARY IEEE;USEIEEE、STD_LOGIC_1164。

ALL;USEIEEE、STD_LOGIC_UNSIGNED.ALL;ENTITY ALU181 ISPORT(S: IN STD_LOGIC_VECTOR(3 DOWNTO0 );A:IN STD_LOGIC_VECTOR(7 DOWNTO0);B: INSTD_LOGIC_VECTOR(7DOWNTO 0);F : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);ﻩCOUT:OUTSTD_LOGIC_VECTOR(3 DOWNTO0);M :INSTD_LOGIC;CN : IN STD_LOGIC;CO,FZ:OUT STD_LOGIC );END ALU181;ARCHITECTURE behav OF ALU181 ISSIGNALA9 :STD_LOGIC_VECTOR(8DOWNTO 0);SIGNAL B9 : STD_LOGIC_VECTOR(8 DOWNTO0);SIGNALF9: STD_LOGIC_VECTOR(8 DOWNTO0);BEGINA9<= '0'& A; B9 <= ’0’&B;PROCESS(M,CN,A9,B9)BEGINCASE S ISWHEN "0000" =〉IF M='0’THEN F9<=A9 + CN ; ELSE F9<=NOT A9; E NDIF;WHEN "0001" =>IF M='0’THEN F9<=(A9 orB9)+ CN ;ELSE F9〈=NOT(A9OR B9);END IF;WHEN ”0010"=> IF M=’0’THEN F9〈=(A9 or(NOT B9))+C N; ELSE F9<=(NOT A9) ANDB9; ENDIF;WHEN "0011"=> IF M='0’THEN F9<= ”000000000"—CN ;ELSEF9<="000000000”;END IF;WHEN"0100”=> IFM='0'THENF9<=A9+(A9 ANDNOT B9)+ CN; ELSE F9〈=NOT(A9 ANDB9);END IF;WHEN ”0101”=>IFM='0' THENF9<=(A9orB9)+(A9 AND NOTB9)+CN ;ELSEF9<=NOT B9; END IF;WHEN"0110" =>IFM=’0’THEN F9〈=(A9- B9) -CN ;ELSE F9〈=A9XOR B9; ENDIF;WHEN”0111"=>IF M='0' THEN F9〈=(A9 or(NOT B9)) -CN ;ELSE F9<=A9 and (NOT B9); END IF;WHEN"1000" =>IFM='0'THEN F9<=A9+ (A9AND B9)+CN ; ELSE F9〈=(NOTA9)and B9; END IF;WHEN "1001”=> IF M=’0’THEN F9〈=A9+ B9 + CN ; ELSE F9<=NOT(A9 XOR B9); ENDIF;WHEN ”1010"=>IF M=’0'THEN F9〈=(A9or(NOTB9))+(A 9AND B9)+CN ; ELSEF9<=B9;END IF;WHEN "1011”=〉IF M='0'THENF9<=(A9 AND B9)- C N; ELSE F9<=A9 ANDB9; ENDIF;WHEN ”1100”=〉IF M='0'THENF9<=(A9 +A9) + CN; ELSEF9〈="000000001"; END IF;WHEN "1101”=〉IF M='0' THEN F9〈=(A9or B9)+ A9 + CN;ELSEF9〈=A9 OR (NOTB9); END IF;WHEN "1110"=>IF M='0'THENF9<=((A9 or (NOTB9)) +A9) + CN; ELSE F9〈=A9OR B9;END IF;WHEN”1111”=〉IFM=’0'THENF9<=A9 —CN ;ELSE F9<=A9 ; END IF;WHEN OTHERS=> F9<= ”000000000" ;ENDCASE;IF(A9=B9) THENFZ<=’0';END IF;ﻩEND PROCESS;F<=F9(7DOWNTO0) ;CO<= F9(8) ;COUT<="0000"WHEN F9(8)=’0'ELSE"0001";END behav;ALU得原理图:2、微控制器实现信息传送要靠微命令得控制,因此在CPU 中设置微命令产生部件,根据控制信息产生微命令序列,对指令功能所要求得数据传送进行控制,同时在数据传送至运算部件时控制完成运算处理。

8位ALU设计

8位算术逻辑单元设计电子12-112060401248位算术逻辑单元设计1.概述算术逻辑单元(arithmetic and logic unit) 是能实现多组算术运算和逻辑运算的组合逻辑电路,简称ALU。

算术逻辑单元(Arithmetic&logical Unit)是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由"And Gate"(与门)和"Or Gate"(或门)构成的算术逻辑单元,主要功能是进行二位元的算术运算,如加减乘(不包括整数除法)。

基本上,在所有现代CPU体系结构中,二进制都以补码的形式来表示。

通常而言,ALU具有对处理器控制器、内存及输入输出设备的直接读入读出权限。

输入输出是通过总线进行的。

输入指令包含一个指令字,有时被称为机器指令字,其中包括操作码,单个或多个操作数,有时还会有格式码;操作码指示ALU机要执行什么操作,在此操作中要执行多少个操作数。

比如,两个操作数可以进行比较,也可以进行加法操作。

格式码可与操作码结合,告知这是一个定点还是浮点指令;输出包括存放在存储寄存器中的结果及显示操作是否成功的设置。

如操作失败,则在机器状态字中会有相应的状态显示。

大部分ALU都可以完成以下运算∶整数算术运算(加、减,有时还包括乘和除),位逻辑运算(与、或、非、异或),移位运算。

2.ALU设计2.1设计目标设计要求该处理器的数据宽度是8bit,可以实现算术加法、算术减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。

2.2逻辑分析依照ALU的原理与逻辑结构原理图,用超前进位的方法能实现下面八种功能操作的4位ALU,并对电路进行封装。

设定:输入信号:A4-A1、B4-B1、F3-F1、低位进位端C0、(级联控制端G);输出信号:S4-S1、进位C4 4位ALU的八种功能如下:把低位的进位连接到高一位的本位上,而当F3F2F1的值为001、011、101 时,C0的值为1,其余为0,于是C0应满足:C0=GF1/F1F2F3+C0/G。

8位CPU总线采样记录仪的设计

4 2・

《 测控技 术 ̄0 2年 第 3 21 1卷 第 2期

8位 C U总 线 采 样 记 录仪 的 设 计 P

程 耀 林 ,魏 华 兵 ,伍 时促 ,王 锐 ,陈 锟

( 中南 民族大学 电子信息工程学 院 , 湖北 武汉 4 07 ) 3 0 4

摘要 : 计 了一种 8位 C U 总线 采样 记 录仪 , 5 设 P 对 l单 片机 总 线进 行 采样 , 中提 取 如 下 4种信 息并 存 从

The De in fBu t a pl n S o i n t um e o sg o sDa a S m i a d t rng I sr ng ntf r

CPU t 8 bi S wih . t BU

C HENG o l , EI Hu - i g W U S iC , ANG i C Ya —i W a b n , n h— U W Ru , HE Ku N n ( c ol f l t nca d If m t n E gn eig S uhC nrl n es yfr a o a t s Wu a 3 0 4 C i ) S h o o e r i n n r ai n i r , o t— e t i ri t n li , h n4 0 7 , hn E co o o e n a U v t o N i ie a

储 : 外程 序代 码 和地 址 、 片 片外 数据 存储 器的数据 和地 址 。 它基 于 A t a 司提 供 的 D 0开发 板 , lr 公 e E 外接

A 8 S2单 片机 最 小 系统 , T95 带触摸 L D和 s C D卡 , F G 内实现 总线采 集模 块 , 同构 建 了一 个 S P 在 PA 共 OC 系统 , 过 在 No 通 i I s I中运 行 的软件 对数据进 行 存储 、 处理 。测试 结 果表 明 , 采集 的数 据 可使 用 T T文件 X

8位加法器设计程序过程

8位加法器设计程序过程八位加法器是一种组合逻辑电路,用于计算两个八位二进制数的和。

在设计过程中,需要确定输入和输出的位数、电路逻辑、输入输出关系等。

下面是一个八位加法器设计程序的详细过程。

1.确定输入和输出的位数:首先,我们需要明确八位加法器的输入和输出的位数。

在这个例子中,我们使用八位二进制数作为输入,并需要输出一个八位的和。

因此,输入和输出的位数均为8位。

2.确定输入和输出的表示形式:在计算机中,二进制数通常以补码形式进行表示。

因此,在这个例子中,我们将使用补码表示输入和输出。

3.分析电路逻辑:一个八位加法器由八位的全加器以及一个进位逻辑组成。

全加器用于计算两个相应位数相加的结果,而进位逻辑负责处理进位位。

因此,我们需要设计八个全加器和一个进位逻辑。

4.设计全加器电路:全加器是八位加法器的核心部分,用于计算两个位的和以及进位。

全加器的输入包括两个加数位和一个来自前一位的进位位。

输出包括和位以及进位位。

以下是一个典型的全加器电路:- 输入:A、B和C_in- 输出:Sum和C_out-逻辑表达式:Sum = A 异或 B 异或 C_inC_out = (A and B) 或 (C_in and (A 异或 B))设计八个这样的全加器电路,分别用于计算八个相应位数的和以及进位。

5.设计进位逻辑电路:进位逻辑电路负责处理来自各个位的进位。

具体来说,进位逻辑电路需要计算进位位以及进位到下一位的值。

以下是一个典型的进位逻辑电路:- 输入:C_in、C_0、C_1、C_2、C_3、C_4、C_5、C_6 和 C_7- 输出:C_out 和 C_next-逻辑表达式:C_out = C_7C_next = (C_6 and C_7) 或 (C_5 and (C_6 or C_7)) 或 (C_4 and (C_5 or (C_6 or C_7))) 或 ......(C_1 and (C_2 or (C_3 or (C_4 or (C_5 or (C_6 or C_7))))))其中,C_out代表从最高位传出的进位,C_next代表传递给下一位的进位。

8位ALU设计简介

8位A L U设计简介-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN

8位ALU设计

一、设计概述

一种基于可编程逻辑器件FPGA和硬件描述语言的8位的ALU的设计方法。

该ALU采用层次设计方法,有寄存器模块、控制模块和显示模块组成,能实现8位无符号数的取值、加减和4种逻辑运算(与、或、异或、同或)。

该ALU在QuartusII软件环境下进行功能仿真,通过DE2验证。

二、设计功能

1、该处理器的数据宽度为8bit,可以实现算术加法、减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。

2、用选择端opcode [2:0] 选择8种运算,2个操作数分别是a_r [7:0]和b_r[7:0]

3、使用DE2板上的3个拨码开关设置当前ALU的运算功能,再由8个拨码开关给定数据A和数据B,由一个按键key手动提供脉冲。

三、设计方案

本设计共有5个模块。

1)脉冲输出器(key手动脉冲),计数依次产生4个脉冲到各个部件,第一个脉冲启动信号。

2)寄存器A,第二个脉冲来时锁存数据A,并在数码管上显示。

3)寄存器B,第三个脉冲来时锁存数据B,并在数码管上显示。

4)8位ALU,第四个脉冲来时进行运算,并锁存结果alu_out。

5)结果显示器,将结果显示通过DE2上的数码管显示。

8位嵌入式CPU的AMBA TM wrapper设计

关键 词 : o AMB r a p rI S C; A ”w p e ;P复 用 ; 入 式 C U 嵌 P

文章 编 号 :0 2 8 3 (0 6 3 — 0 30 文 献 标 识 码 : 中 图 分 类 号 :P 6 ;N 7 10 — 3 12 0 )4 0 7 — 3 A 3 8 T 4 r

维普资讯

嘲- 产品 、 研发 ห้องสมุดไป่ตู้ 测试 ・

带 F带 带 F 苷 {

8 位嵌入式 C U  ̄A A wrp e 设计 P MB a pr

顾 叶华 ,曾晓 洋 ,韩 军

( 复旦 大 学 专 用集成 电路 与 系统 国家重 点 实验 室, 海 2 1 0 ) 上 0 2 3

A A 总线 通 过 w ap r MB rp e 交互 通 信 。因 此 , 设 计 wap r首 要 p e,

先 需 了解 C U 和 AMB P A 总 线 。

C U有 8位 的 8 5 和 3 P 0l 2位 的 MIS A M7 A M P 、 R 、 R 9等 。 采 用 3 的 C U是 当前 没计 的 主流 , 成 本 比较高 , 易得 到广 泛 2位 P 但 不

6502汇编语言程序设计(2版)之程序设计part1

(一)

一. CPU 对命令的执行

6502是普通的8位CPU.它需要外接其他器件(如:SRAM、EPROM、定时/计数器、I/O接口器件等)才能工作,它地址线为16,直接寻址能力为64K($0000--$FFFF)之间. 数据线为8,一次只能完成8位数据(0--255)的处理. CPU通过地址线联系到要操作的内存单元,然后读取该单元的操作码,通过预设好了的操作码所代表的操作,CPU对其进行相应命令执行. 例如对命令 ASL 的执行,假设程序计数(PC)=$7000 , ($7000)=$0A .

[]中的内容为可选项

标号 标号标识了一条指令的位置,可以使用标号作为访问该指令的地址,标号的格式应遵循下面规则:

.必须从第一列开始或者以: 结束

. 不能用操作代码或伪指令的名字命名

. 标号长度为1~28个字符(视各汇编而定)

ror

jmp MULCH02

MULCH08:

rts

例3.

;无符号整型数除法

;($A2|$A1)/($A4|$A3)=$A2|$A1).........($A6|$A5)

;结果 , 商:($A2|$A1) 余数:($A6|$A5)

;说明: C=0有效, C=1 无效(除数为0)

3. $0200--$0700(cheapchange注:综合上下文,应为0200--07FF) 公共内存区 (1.5K字节)

4. $0800--$1FFF $0000 -- $0700的镜像. 连做了3次镜像(6K字节)

8位CPU设计与实现

计算机组成原理论文姓名:某某班级:计科一班学号:8位CPU的设计与实现论文CPU 的重要功效是履行指令,控制完成盘算机的各项操纵,包含运算操纵.传送操纵.输入/输出操纵等.作为模子盘算机设计,将重点放在存放器组,采纳较简略的构成模式,以尽量简练的设计帮忙读者控制CPU 的基起源基础理.此次设计CPU就是为了懂得CPU运行的道理,从而完成从指令体系到CPU的设计,并且经由过程仿真对CPU设计进行准确性评定.症结词:CPU,设计指标,电路道理图,运算部件,存放器组,模子机指令体系,微敕令序列,数据通路1. 设计的义务与请求1.1设计指标1. 能实现IN(输入).ADD(二进制加法).STA(存数).OUT(输出).JMP(无前提转移)这五种指令;2. 全部体系能正常稳固工作.1.2 设计请求1. 画出电路道理图;2.写出设计的全进程,附上有关材料和图纸(也可直接写在相干章节中),有心得领会.2. 计划论证与选择CPU的体系计划CPU 重要由算术逻辑单元ALU,数据暂存存放器DR1.DR2,数据存放器R0~R2,程序计数器PC,地址存放器AR,程序/数据存储器MEMORAY,指令存放器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所构成.图中虚线框内部分包含运算器.控制器.程序存储器.数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现.虚线框外部分主如果输入/输出装配,包含键盘.数码管.LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及不雅察CPU 内部工作情形及运算成果.1.运算部件运算部件的义务是对操纵数进行加工处理.重要由三部分构成:(1)输入逻辑.(2)算术/逻辑运算部件ALU.(3)输出逻辑2.存放器组盘算机工作时,CPU 须要处理大量的控制信息和数据信息.例如对指令信息进行译码,以便产生响应控制敕令对操纵数进行算术或逻辑运算加工,并且根据运算成果决议后续操纵等.是以,在CPU 中须要设置若干存放器,临时存放这些信息.在模子CPU中,存放器组由R0.R1.R2 所构成.3.指令存放器指令存放器(IR)指令存放器指令存放器(IR)用来存放当前正在履行的指令,它的输出包含操纵码信息.地址信息等,是产生微敕令的重要逻辑根据.4.程序计数器程序计数器(PC)程序计数器程序计数器也称指令指针,用来指导指令在存储器中的存放地位.当程序次序履行时,每次从主存掏出一条指令,PC 内容就增量计数,指向下一条指令的地址.增量值取决于现行指令所占的存储单元数.假如现行指令只占一个存储单元,则PC 内容加1;若现行指令占了两个存储单元,那么PC 内容就要加2.当程序须要转移时,将转移地址送入PC,使PC 指向新的指令地址.是以,当现行指令履行完,PC 中存放的老是后续指令的地址;将该地址送往主存的地址存放器AR,即可从存储器读取下一条指令.5.地址存放器CPU 拜访存储器,起首要找到须要拜访的存储单元,是以设置地址存放器(AR)来存放被访单元的地址.当须要读取指令时,CPU 先将PC 的内容送入AR,再由AR将指令地址送往存储器.当须要读取或存放数据时,也要先将该数据的有用地址送入AR,再对存储器进行读写操纵.6.标记存放器标记存放器F是用来记载现行程序的运行状况和指导程序的工作方法的,标记位则用来反应当前途序的履行状况.一条指令履行后,CPU 根据履行成果设置响应特点位,作为决议程序流向的断定根据.例如,当特点位的状况与转移前提相符时,程序就进行转移;假如不相符,则次序履行.在后面将要介绍的较庞杂模子盘算机设计中设置了两个标记位:进位Fc.零位Fz.实现信息传送要靠微敕令的控制,是以在CPU 中设置微敕令产生部件,根据控制信息产生微敕令序列,对指令功效所请求的数据传送进行控制,同时在数据传送至运算部件时控制完成运算处理.微敕令产生部件可由若干组合逻辑电路构成,也可以由专门的存储逻辑构成.产生微敕令的方法可分为组合逻辑控制方法和微程序控制方法两种.在本章所介绍的8 位模子CPU 设计中,采取微程序控制方法经由过程微程序控制器和微指令存储器产生微敕令,是以此CPU 属于庞杂指令CISC CPU.盘算机的工作经常是分步履行的,那么就须要有一种时光旌旗灯号作为分步履行的标记,如周期.节奏等.节奏是履行一个单步操纵所需的时光,一个周期可能包含几个节奏.如许,一条指令在履行进程中,根据不合的周期.节奏旌旗灯号,就能在不合的时光发出不合的微敕令完成不合的微操纵.周期.节奏.脉冲等旌旗灯号称为时序旌旗灯号,产生时序旌旗灯号的部件称为时序产生器或时序体系,它由一组触发器构成.由石英晶体振荡器输出频率稳固的脉冲旌旗灯号,也称时钟脉冲,为CPU 供给时钟基准.时钟脉冲经由一系列计数分频,产生所需的节奏(时钟周期)旌旗灯号.时钟脉冲与周期.节奏旌旗灯号和有关控制前提相联合,可以产生所需的各类工作脉冲.模子机指令体系一条指令必须包含下列信息:操纵码.操纵数的地址.操纵成果的存储地址.下一条指令的地址.指令的根本格局op-code 为操纵码,rs为源存放器,rd 为目标存放器存放器操纵数模子机指令体系,及其指令编码情势设模子机指令体系中包含有五条根本指令,分为算术运算指令.存取指令和控制转移指令等三种类型.五条机械指令分离是:IN(输入).ADD(二进制加法).STA(存数).OUT(输出).JMP(无前提转移).IN 为单字长(8 位二进制),其余为双字长指令,XX H 为addr对应的十六进制地址码.拟定指令流程和微敕令序列(盘算机设计中最症结步调)1.微程序控制概念(1)微敕令和微操纵一条机械指令可以分化成一个微操纵序列,这些微操纵是盘算机中最根本的,不成再分化的操纵.在微程序控制的盘算机中,将控制部件向履行部件发出的各类控制敕令叫做微敕令,它是构成控制序列的最小单位.是以,微敕令是控制盘算机各部件完成某个根本微操纵的敕令.微敕令和微操纵是一一对应的.微敕令是微操纵的控制旌旗灯号,微操纵是微敕令的操纵进程.微敕令有兼容性和互斥性之分.兼容性微敕令是指那些可以同时产生,配合完成某一些微操纵的微敕令;而互斥性微敕令是指在机械中不许可同时消失的微敕令.兼容和互斥都是相对的,一个微敕令可以和一些微敕令兼容,和另一些微敕令互斥.对于单独一个微敕令,就无所谓兼容性或互斥性了.(2)微指令.微地址微指令是指控制存储器中的一个单元的内容,即控制字,是若干个微敕令的聚集,存放控制字的控制存储器的单元地址就称为微地址.一条微指令平日至少包含两大部分信息:微操纵码字段,又称操纵控制字段,该字段指出微指令履行的微操纵;微地址码字段,又称次序控制字段,指出下一条要履行的微指令的地址.(3)微周期所谓微周期是指从控存中读掏出一条微指令并履行划定的响应操纵所需的时光.(4)微程序一系列微指令的有序聚集就是微程序.若干条有序的微指令构成了微程序.微程序可以控制实现一条机械指令的功效.或者说一条机械指令可以分化为特定的微指令序列.一旦机械的指令体系肯定今后,每条指令所对应的微程序被设计好并且存入控存后,控存老是处于只读的工作状况,所以控存一般采取只读存储器(ROM)存放.从新设计控存内容就能增长.删除.修正机械指令体系.在FPGA 中平日采取嵌入式阵列块构成的LPM_ROM 作为控存,存放微指令.(1)程度型微指令一次能界说并履行多个并行操纵微敕令的微指令.按照操纵控制字段的编码办法不合,程度型微敕令又分为三种:第一种是全程度型(不译码法)微指令,第二种是字段译码法程度型微指令,第三种是直接和字段译码相混杂的程度型微指令.(2)垂直型微指令垂直型微指令中设置操纵码字段,由微操纵码划定微指令的功效.垂直型微指令的构造相似于机械指令的构造.在一条微指令中只存一二个微敕令,每条微指令的功效比较简略.是以,实现一条机械指令的微程序要比程度型微指令编写的微程序长得多,它是采取较长的微程序构造去换取较短的微指令构造.3.模子机的微指令uA5~uA0:微程序控制器的微地址输出旌旗灯号,是下一条要履行的微指令的微地址.S3.S2.Sl.S0:由微程序控制器输出的ALU 操纵选择旌旗灯号,以控制履行16 种算术操纵或16 种逻辑操纵中的某一种操纵.M:微程序控制输出的ALU 操纵方法选择旌旗灯号.M=0 履行算术操纵;M=l履行逻辑操纵:微程序控制器输出的进位标记旌旗灯号,Cn=0 暗示ALU 运算时最低位有进位;Cn=1 则暗示无进位. WE:微程序控制器输出的RAM 控制旌旗灯号.当CE=0 时,如WE=0,为存储器读;如WE=1,为存储器写.A9.A8:译码后产生CS0.CS1.CS2 旌旗灯号,分离作为SW_B.RAM.LED 的选通控制旌旗灯号.A 字段(15.14.13):译码后产生与总线相衔接的各单元的输入选通讯号.B 字段(12.11.10):译码后产生与总线相衔接的各单元的输出选通讯号.C 字段(9.8.7):译码后产生分支断定测试旌旗灯号P(1)~P (4)和LDPC 旌旗灯号.履行一条微指令的进程相似于机械指令的履行进程.起首,将微指令从控存CM 中掏出,称为取微指令.对于垂直型微指令还应包含微操纵码的译码时光.然后,履行微指令所划定的各个微操纵.根据微指令的履行方法可分为串行履行和并行履行两种.5.时序安插因为CPU 的工作是分步进行的,并且须要严厉准时控制,是以设置时序旌旗灯号,以便在不合的时光发出不合的微敕令,控制完成不合的操纵.组合逻辑控制方法和微程序控制方法在时序安插上有差别,前者多采取三级时序划分,尔后者往往采取两级时序.这是设计中最症结的步调,这是因为须要根据这一步的设计成果形成最后的控制逻辑.拟定指令流程是将指令履行进程中的每步传送操纵(存放器之间的信息传送),用流程图的情势描写出来,拟定微敕令序列是用操纵时光表列出每步操纵所需的微敕令及其产生前提.7.形成控制逻辑设计的最后一步.采取组合逻辑控制方法或采取程序控制方法,有各自不合的设计办法.在组合逻辑控制方法中,将产生微敕令的前提进行分解.化简,形成逻辑式,从而构成控制器的焦点逻辑电路.在微程序控制方法中,则是根据微敕令来编写微指令,构成微程序,从而构成以控制存储器为焦点的控制逻辑.2.4 微程序设计1.IN指令为了履行输入指令,CPU 要做两件工作.起首,由INPUT 输入装配的数据开关SW输入数据送到数据总线上;其次,经由过程数据总线将输入的数据写入存放器R0 中.2.ADD指令 R0←R0+(MEM)存储单元的地址是存放在紧跟在操纵码后的字节中的,是以,起首要以该字节的内容为地址,即将该单元内容送地址存放器AR;然后,从AR 所指向的RAM 存储单元掏出操纵数送给DR2.因为在取指令操纵码时,PC 已经主动加1,指向下一字节,该地址就是存放操纵数的存储单元的地址.3.STA指令向存储器RAM 写数据操纵STA,以紧跟在操纵码后的字节作为存放操纵数地址,将R0 中的数据存入该地址单元.起首将紧跟在操纵码后的字节的内容送给地址存放器AR.4. OUT指令AR←PC,PC←PC+1;以PC的内容作为存数据的地址BUS←RAM,AR←BUS;AR指向存放操纵数的RAM单元BUS←RAM,DR1←BUSOUT←DR15.JMP指令AR←PC,PC←PC+1 ;以PC的内容作为取数据的地址BUS←RAM,PC←BUS ;将RAM内容送PC,实现程序转移3. CPU设计及微代码3.1 道理图模版取指令阶段完成的义务是将现行指令从主存中掏出来并送至指令存放器中.具体的操纵如下:(1)将程序计数器(PC)中的内容送至存储器地址存放器(AR),并送往地址总线(AB).(2)PC 的内容递增,为取下一条指令做好预备.(3)由控制单元(CU)经控制总线(CB)向存储器发读敕令.(4)从主存中掏出的指令经由过程数据总线(DB)送到指令存放器(IR)中.以上这些操纵对任何一条指令来说都是必须要履行的操纵,所以称为公共操纵.完成取指阶段义务的时光称为取指周期.掏出指令后,指令译码器ID 可辨认和区分出不合的指令类型.此时盘算机进入剖析取数阶段,以获取操纵数.因为各条指令功效不合,寻址方法也不合,所以剖析取数阶段的操纵是各不雷同的.(5)指令存放器(IR)中的内容送指令译码器(ID)进行指令译码.(6)指令译码器(ID)的内容送操纵控制器.(7)操纵控制器产生履行指令的微控制.2. 剖析取数阶段对于无操纵数指令,只要辨认出是哪条具体的指令,即可以直接转至履行阶段,所以不需进入剖析取数阶段.而对于带操纵数指令,为读取操纵数起首要盘算出操纵数的有用地址.假如操纵数在通用存放器内,则不须要再拜访主存;假如操纵数在主存中,则要到主存中去取数.对于不合的寻址方法,有用地址的盘算办法是不合的,有时要多次拜访主存才干掏出操纵数(间接寻址).对于无操纵数指令,只要辨认出是哪条具体的指令,即可以直接转至履行阶段,所以不需进入剖析取数阶段.而对于带操纵数指令,为读取操纵数起首要盘算出操纵数的有用地址.假如操纵数在通用存放器内,则不须要再拜访主存;假如操纵数在主存中,则要到主存中去取数.对于不合的寻址方法,有用地址的盘算办法是不合的,有时要多次拜访主存才干掏出操纵数(间接寻址).别的对于单操纵数指令和双操纵数指令,因为须要的操纵数的个数不合,剖析取数阶段的操纵也不合.3. 履行阶段履行指令阶段完成指令划定的各类操纵.履行阶段完成义务的时光称为履行周期.盘算机的根本操纵进程就是取指令.取操纵数.履行指令,然后再取下一条指令……如斯周而复始,直至碰到停机指令或外来的干涉为止.微程序流程图是根据每条指令的微操纵流程所绘制的,操纵框内给出的是该微操纵要履行的动作.当拟定“取指”微指令时,该微指令的判别测试字段为P(1)测试,根据P(1)的测试成果将消失多路分支.因为操纵码的位数已肯定为4 位,所以可直接将操纵码与微地址码的部分对应.本模子机用指令存放器(IR7~IR0)的高4 位(IR7~IR4)与微地址码的后4 位对应.模子机的微地址码共有六位,微地址码的高三位已固定为001,低三位从000~111 共有八种状况,现设计了五条指令,须要五个分支进口,是以,将低三位中的000B~100B 这五个地址分派给这五条指令,就得到五个分支进口微地址.这五个分支进口(以八进制暗示)分离是10.11.12.13 和14,占用五个固定的微地址单元.其余的微操纵单元的微地址设置,可以将还未应用的微地址按照从小到大的次序依次分派给这些微操纵单元,微地址的分派情形见图5-4.微地址标注在每个微操纵框的左上角,右上角标注的是微指令码.ALU 为运算器;DR0 和DR1 为其输入端的两个暂存存放器;R0 是数据存放器,用来保管数据和运算成果;PC 为程序计数器;IR 和ID分离为指令存放器和指令译码器;AR 和MOMERY 分离为存储地址存放器和存储数据存放器;INPUT 为输入装配;OUTPUT 为输出装配.各根本单元模块的输出端经由过程三态门控制与内部数据总线相衔接;微控制器按照时序产生器的节奏,对指令进行译码后产生同步的控制旌旗灯号.各部件旁边的C 是由微指令译码器输出的控制旌旗灯号,用于控制数据的输入和输出.与数据总线相连的旌旗灯号有些是单向的,有些则是双向的.如数据存放器.存储器.I/O 接口的数据旌旗灯号是双向的,而指令旌旗灯号.地址旌旗灯号.控制旌旗灯号是单向的.现实上在FPGA 中,双向端口元件的表述办法是:输入和输出端口采取两个不合的端口,这时各根本元件的输出端口不克不及直接与内部总线衔接在一路,而是须要经由过程三态门控制今后再衔接到总线上.在向总线输出数据时,不克不及同时有两路或两路以上数据一路输出,不然会产生数据冲突.是以在设计微程序.肯定微操纵时,应留意数据传输中控制旌旗灯号对时序的请求.3.5 微程序控制的基起源基础理3.6 在模子CPU中的软件履行微指令履行情形经由过程此次的设计,我受益匪浅.起首,我对CPU有了根本熟悉,熟悉它的道理,构造,运行;其次,我对微指令的熟悉也有了进一步进步,特殊是指令对应的功效以及对指令的懂得;再次,我对该部件的道理及功效运行有了必定层次的懂得;最后,我必须承认,不管碰到什么问题都要从底层抓起,然后去解决问题,当我对某些器械不懂时,要从书本的最根本概念看起,再到道理,运行层次,构造等去懂得才干真正懂,还有和他人的交换很重要,不懂的问题彼此交换看法可以受益匪浅.我很感激此次机遇让我有了一次锤炼.参考文献:[1] 潘松潘明. 现代盘算机构成道理. 科学出版社.[2] 王爱英.盘算机构成与构造(第四版).清华大学出版社.。

CPU设计

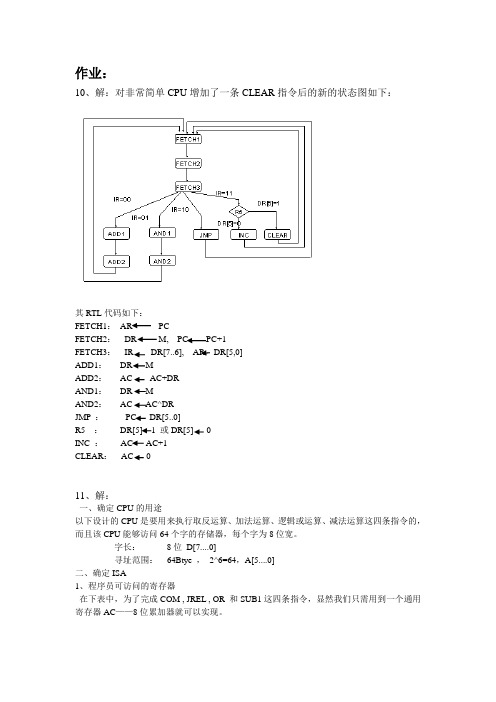

作业:10、解:对非常简单CPU增加了一条CLEAR指令后的新的状态图如下:其RTL代码如下:FETCH1:AR PCFETCH2:DR M, PC PC+1FETCH3:IR DR[7..6], AR DR[5,0]ADD1:DR MADD2:AC AC+DRAND1:DR MAND2:AC AC^DRJMP :PC DR[5..0]R5 :DR[5] 1 或DR[5] 0INC :AC AC+1CLEAR:AC 011、解:一、确定CPU的用途以下设计的CPU是要用来执行取反运算、加法运算、逻辑或运算、减法运算这四条指令的,而且该CPU能够访问64个字的存储器,每个字为8位宽。

字长:8位D[7....0]寻址范围:64Btye ,2^6=64,A[5....0]二、确定ISA1、程序员可访问的寄存器在下表中,为了完成COM , JREL , OR 和SUB1这四条指令,显然我们只需用到一个通用寄存器AC——8位累加器就可以实现。

指令操作码操作COM 00XX XXXX AC AC' (取反)JRET 01AA AAAA PC PC+00AA AAAAOR 10AA AAAA AC AC^M[00AA AAAA]SUB1 11AA AAAA AC AC—M[00AA AAAA]—12、CPU还需要一些其他的寄存器以便完成取指令(或数据)、译码和执行指令所必须的内部操作,最基本的寄存器有:AR(地址寄存器)——6位,由A[5.....0]向存贮提供地址PC (程序计数器)——6位,指出下一条指令的地址DR(数据寄存器)——8位,通过D[7....0]从存贮器接受指令和数据IR(指令寄存器)——2位,存放从存贮器中取回的指令的操作码部分。

三、为CPU设计状态图为了确定CPU的状态图,需对每条指令作如下分析:1、从存贮器取出指令(所有指令都相同)2、指令译码3、指令执行从存贮器中取出指令:1、原理:根据冯. 诺依曼型机的原理(指令在存贮器中按顺序存放.......), 在CPU能执行指令之前,它必须将这条指令从存贮中取出,CPU通过执行如下的操作序列完成这个任务的:【1】选择存贮单元由A[5... 0]确定【2】对A[5... 0]译码、延迟、并向存贮器发一个信号(如READ或R/W'=1),使存贮器将此指令输出到它的输出引脚。

基于VHDL的8位模型计算机的设计与实现

摘要随着计算机在人们生活中重要性和不可或缺性的提高,为了更方便的为大众使用,发展计算机性能成为IT行业的热点,但计算机的部结构极其复杂,为了便于研究便产生了模型计算机。

本文完成了基于VHDL的8位模型计算机的设计与实现。

文中首先阐述了8位模型计算机的原理,然后对其十个功能模块〔算术逻辑运算单元,累加器,控制器,地址寄存器,程序计数器,数据寄存器,存储器,节拍发生器,时钟信号源,指令寄存器和指令译码器进行了分析与设计。

最后在Quartus II 9.0环境下进行了仿真,完成了8位模型计算机的整体实现。

本文综合了计算机组成原理和数字逻辑与系统设计的知识,设计的8位模型计算机能更方便的了解计算机部构造和工作原理。

整个系统的开发体现了在Quartus II软件平台上用VHDL设计数字控制系统的实用性。

关键词:8位模型机; Quartus II ;VHDL语言AbstractWith the improvement of importance and indispensability in computer in people's life,in order to use more conveniently for public ,computer performance is becoming a hot in the IT industry development.but the internal structure of the computer is very complicate,Computer model simplifies the difficulty of the research.This article completed the design and implementation of eight model computer based on VHDL.First ,this article expounds the principle of eight model computer,then divides it into 10 modules<arithmetic logic unit, accumulator, controllers, address register, the program counter and data registers, memory, beat generator, a clock signal, instruction register and instruction decoder>and analyse and design each of them.Finally under the environment of the Quartus II 9.0 simulation, completed overall implementation of the 8 model computer. The analysis and design of the eight model computer integrated the knowledge of computer constitute principle and Digital logic and system design. The design of the eight model computer can be more convenient to understand internal structure and working principle.The whole system development manifests the practicability of designing the numerical control system on the Quartus II software platform with VHDL.Key words:eight model computer ; VHDL language; Quartus II目录1 绪论11.1 本课题研究的目的11.2 本课题研究的背景及意义12 基于VHDL编程的基础知识32.1 VHDL语言概述32.2 VHDL的设计流程 (4)2.3 有关Quartus II 的介绍52.4 本课题基于Quartus II的设计流程73 基于VHDL8位模型机的原理与设计73.1 模型计算机的原理73.2 模型机的总体设计要求83.3 模型机逻辑框图的设计83.3 模型机的指令系统设计83.4 模型机的指令执行流程设计83.5 基于VHDL8位模型机各模块的设计与实现 (10)3.5.1 算术逻辑单元ALU模块103.5.2 累加器模块113.5.3 控制器模块123.5.4 节拍发生器143.5.5 指令寄存器模块IR和指令译码器163.5.6 时钟产生器173.5.7 程序计数器模块183.5.8 地址寄存器MAR203.5.9 存储器RAM213.5.10 数据寄存器DR224 基于VHDL的8位模型计算机的实现234.1 基于VHDL的微程序执行流程图234.2 8位模型机的顶层原理图设计244.3 基于VHDL的8位模型机工作流程244.4 顶层VHDL源程序设计254.4.1 头文件cpu_defs的VHDL设计254.4.2 CPU的VHDL源程序设计264.5 8位模型机的整体实现34结论34致 35参考文献36附录A 英文原文.......................................... 错误!未定义书签。

8位CPU的设计

8位CPU的设计一、设计的任务与要求计算机的核心部件CPU通常包含运算器和控制器两大部分。

组成CPU的基本部件有运算部件,寄存器组,微命令产生部件和时序系统等。

这些部件通过CPU内部的总线连接起来,实现它们之间的信息交换。

1.设计目的(1).深入理解基本模型计算机的功能、组成知识;(2).深入学习计算机各类典型指令的执行流程;(3).学习微程序控制器的设计过程和相关技术,掌握LPM_ROM的配置方法。

(4).在掌握部件单元电路实验的基础上,进一步将单元电路组成系统,构造一台基本模型计算机。

(5).定义五条机器指令,并编写相应的微程序,上机调试,掌握计算机整机概念。

掌握微程序的设计方法,学会编写二进制微指令代码表。

(6).通过熟悉较完整的计算机的设计,全面了解并掌握微程序控制方式计算机的设计方法。

2.设计原理在部件实验过程中,各部件单元的控制信号是人为模拟产生的,而本实验将能在微过程控制下自动产生各部件单元控制信号,实现特定的功能。

实验中,计算机数据通路的控制将由微过程控制器来完成,CPU从内存中取出一条机器指令到指令执行结束的一个指令周期,全部由微指令组成的序列来完成,即一条机器指令对应一个微程序。

11该CPU 主要由算术逻辑单元ALU,数据暂存寄存器DR1、DR2,数据寄存器R0~R2,程序计数器PC,地址寄存器AR,程序/数据存储器MEMORAY,指令寄存器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所组成。

图中虚线框内部分包括运算器、控制器、程序存储器、数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现。

虚线框外部分主要是输入/输出装置,包括键盘、数码管、LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及观察CPU 内部工作情况及运算结果。

二、单元电路设计1、运算部件运算部件的任务是对操作数进行加工处理。

主要由三部分组成:(1) 输入逻辑。

ASIC实验报告(8位CPU的设计)

ASIC设计实验报告学院:电子工程学院学号:2014*******姓名:***指导老师:***2014年11月13日一、实验目的:通过对ASIC实验课的学习,应当学会以下几点:1.熟悉Linux操作系统的应用环境,基本命令行的应用,以及对vi编辑器熟练应用。

2.熟练掌握Verilog编程语言,包括基本组合逻辑电路的实现方法,基本时序逻辑电路的实现方法,怎样使用预定义的库文件,利用always块实现组合逻辑电路的方法已经着重了解assign与always 两种组合逻辑电路实现方法之间的区别,深入了解阻塞赋值与非阻塞赋值的概念以及应用的差别,有限状态机(FSM)实现复杂时序逻辑的方法,以及学会在Linux 系统环境当中应用Synopsys工具VCS进行仿真。

3.熟悉电路设计当中的层次化、结构化的设计方法。

4.熟悉CPU当中有哪些模块组成,模块之间的关系,以及其基本的工作原理。

5.学会利用汇编语言设计程序,注意代码规范性要求。

二、实验要求:按照实验指导书上的要求即:CPU各个模块的Verilog语言代码的编写、编译及仿真正确,并在规定的时间内完成。

要求对CPU进行语言级系统仿真结果正确之后,利用该实验当中采用的八个汇编关键字,编写一个能够实现某种功能的小程序。

然后对其中的控制器电路进行综合,并检查Timing 和Power,进行门级仿真。

三、实验内容:设计一个8位RISC_CPU 系统。

(RISC: Reduced Instruction Set Computer),它是一种八十年代才出现的CPU,与一般的CPU相比,不仅只是简化了指令系统,而且通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。

从实现的方法上,它的时序控制信号部件使用了硬布线逻辑,而不是采用微程序控制方式,故产生控制序列的速度要快的多,因为省去了读取微指令的时间。

此CPU所具有的功能有:(1)取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发出指令地址及控制信号。

基于VHDL语言的8位CPU的设计(quartus仿真)

假设指令地址为0、1、2、3…,为便于显示,设置地址指令和程序计数器输出为数制十进制, 仿真波形如下图:

图2.14 程序计数电路仿真波形

第二部分:RISC-CPU各模块设计与仿真

8. 状态控制器

是CPU的控制核心, 用于产生一系列的控 制信号,启动或停止 某些部件,由状态机 和状态机控制器组成, 如图。

图2.9 数据输出控制器

假设累加器输出值由00000000递增,验证当data_ena为1时,data输出alu_out的值,当 data_ena为0时,data输出"ZZZZZZZZ"。波形如下:

图2.10 数据输出控制器仿真波形

第二部分:RISC-CPU各模块设计与仿真

6. 地址多路器

用于选择输出的地址是PC地址还是数据/ 端口地址,如图2.11所示。每个指令周期的 前4个时钟周期用于从ROM中读取指令,输 出PC地址。后4个时钟周期用于对RAM或 端口的读写,输出数据或端口地址。

图2.7算术逻辑单元

在仿真过程中,假设操作码依次为上述8种操作码。数据值为5,累加器值为由3变0,以此来 验证zero作用。仿真波形下图所示:

图2.8 算术逻辑运算单元仿真波形

第二部分:RISC-CPU各模块设计与仿真

5.数据输出控制器

控制累加器数据输出,如图2.9由于数据总 线是各种操作时传送数据的公共通道,不同 的情况下传送不同的内容。有时要传输指令, 有时要传送RAM区或接口的数据。

图3.2 RISC-CPU各模块连接图

谢谢!!

WPS Office

Make Presentation much more fun

@WPS官方微博 @kingsoftwps

基于VHDL语言的8位 RISC-CPU的设计

8位逻辑计算机设计

4)内部寄存器的种类和数量

助记符

机器码1

机器码2

注释

_FETCH

00

00000

取指令

寄存器R?的值加到A上

图1.0 8位微型计算机开发设计过程

图1.1逻辑框图

表1.0功能设计

模块名称

模块功能

时钟发生器CLKGEN

产生一系列时钟信号,送往CPU其他部件

指令寄存器IR

寄存指令

累加器ACCUM

存放当前的运算结果

算术逻辑运算单元ALU

实现基本运算和操作

数据控制单元DATACTL

控制累加器数据输出

地址多路器ADDR

选择输出的地址是程序地址计数地址还是数据端口

程序计数器PC

提供指令地址

状态机MACHБайду номын сангаасNE

CPU控制核心,产生一系列控制信号,控制某些部件的启动或停止

对系统所需硬件做出初步的估计和选择

1.0对外围设备要求不高。只考虑现实、键盘、和串行口通信

2.0微处理器的考虑因素:

1)字长8位

2)寻址范围和寻址方式

VHDL实现简单的8位CPU

VHDL实现简单的8位CPU设计者:E-MAIL:CPU具有的功能:能完成一些简单的指令MOV AX,ADDRESS4 --将address4中的内容赋给AX寄存器(在8086/8088汇编语言中称这种寻址方式为直接寻址方式)ADD AX,ADDRESS4 -- 将address4中的内容加到AX寄存器中SUB AX,ADDRESS4 -- 用address4中的内容减去AX寄存器中的内容OUT -- 输出AX寄存器中的内容HLT -- CPU停止运行CPU工作的时序图:S0状态:程序计数器(PC)将值赋给MARS1状态:PC<=PC+1 注意:因为在设计状态机时引入了复位键(RST),为了避免一个信号有多个源,因而将时序进程(REG:PROCESS)和组合进程(COM:PROCESS)合二为一。

但是产生了一个比较麻烦的事情--------------即一个状态占用了两个时钟周期。

所以在设计PC<=PC+1时,引入了标志寄存器(FLAG),以确保在S1状态PC只加一次S2状态:从只读存储器(ROM)中读取汇编指令,并且将赋给指令寄存器(IR)IR<=DATABUS------------------------------------------------------------------------------------------------------------------------------------------------ 从S0-S2状态每条指令的执行都是相同的S3状态:取出指令寄存器的高4位(汇编的指令代码)进行译码if (temp="0000") or (temp="0001")or (temp="0010") thenmar<=ir(3 downto 0); --将数据存储的地址赋给MARelsif temp="1110" thenoutput_data<=ax; -- out overelsif temp="1111" thenrun<='0'; --Hlt overend if;有上面的程序可以看出,当指令是MOV、ADD、SUB中的一个时,取出地址当指令是OUT时将累加器中的值输出,该条指令做完当指令是HLT(1111)时,程序停止运行,该条指令做完S4状态:if temp="0000" then - -MOV AX,data overax<=dataBus;elsif temp="0001" then --ADD ax,databx<=databus;f1<='1';elsif temp="0010" then --SUB ax,bxbx<=databus;f1<='1';end if;读出RAM 中的内容(在此设计中,用ROM代替了RAM)在此状态MOV指令结束S5状态:为计算状态if temp="0001" and f1='1' thenax<=ax+bx;f1<='0';elsif temp="0010" and f1='1' thenax<=ax-bx;f1<='0';end if;当指令是ADD(0001)时,AX<=AX+BX当指令是SUB(0010)时,AX<=AX-BX此图为Modelsim se6.0的功能仿真图(结果为62 =(10+20+1)×2 注:×2用SHL指令实现因为其目的寄存器为Ax所以实现方法同OUT、HLT请读者自己实现)源程序:ROM16_4.VHD--//////////////////////////////////////////////////////////--16*8ROM--CE=0时允许读--huyugui--2005,1,28--//////////////////////////////////////////////////////////library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity rom16_8 isport( addr:in std_logic_vector(3 downto 0);ce:in std_logic;dataout:out std_logic_vector(7 downto 0));end entity rom16_8;architecture behave of rom16_8 isbegin--10+20+60-10=80hdataout<="00001001" when addr="0000" and ce='0' else --mov ax,9h"00011010" when addr="0001" and ce='0' else --add ax,ah"00011011" when addr="0010" and ce='0' else --add ax,bh"00101100" when addr="0011" and ce='0' else --sub ax,ch"" when addr="0100" and ce='0' else --out"" when addr="0101" and ce='0' else --hlt"00000000" when addr="0110" and ce='0' else"00000000" when addr="0111" and ce='0' else"00000000" when addr="1000" and ce='0' else"00010000" when addr="1001" and ce='0' else --10h"00100000" when addr="1010" and ce='0' else --20h"01100000" when addr="1011" and ce='0' else --60h"00010000" when addr="1100" and ce='0' else --10h"00000000" when addr="1101" and ce='0' else"00000000" when addr="1110" and ce='0' else"00000000" when addr="1111" and ce='0' else"";end architecture behave;CPU_CONTROL.VHD--/////////////////////////////////////////////////////////////////////////////--8_CPU--mov ax,address /add ax,address/sub ax,address/out /hlt--说明:address为4位的地址(9H-fH)--完善:每个状态为一个时钟周期,这样的话PC<=PC+1在S1状态将只做一次,时钟将--得到很大的改善--设计者:胡玉贵--时间:2005,1,29A--/////////////////////////////////////////////////////////////////////////////library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity cpu_control isport(clk:in std_logic;rst:in std_logic;output_data,databus_out:out std_logic_vector(7 downto 0));end entity cpu_control;architecture behave of cpu_control iscomponent rom16_8 isport( addr:in std_logic_vector(3 downto 0);ce:in std_logic;dataout:out std_logic_vector(7 downto 0));end component rom16_8;type states is (s0,s1,s2,s3,s4,s5);signal current_state,next_state:states;signal flag:std_logic;signal pc,addrbus:std_logic_vector(3 downto 0);signal ax,bx:std_logic_vector(7 downto 0);--Ax,Bxsignal cs:std_logic;signal databus:std_logic_vector(7 downto 0);signal run:std_logic;signal mar:std_logic_vector(3 downto 0);signal ir:std_logic_vector(7 downto 0);signal f1:std_logic;beginreg:processvariable temp:std_logic_vector(3 downto 0);beginif rst='1' then --系统复位pc<="0000";ax<="00000000";bx<="00000000";run<='1';flag<='1'; --PC可以加1f1<='1';current_state<=s0;--databus<="00000000";elsif rising_edge(clk) thenif run='1' thencase current_state iswhen s0=>next_state<=s1; --Address State&Fetchmar<=pc; --将PC的值赋给MAR,在S2状态时从ROM中读出指令(IR<=databus)when s1=>next_state<=s2;if flag='1' thenpc<=pc+1; --地址加1flag<='0';end if;when s2=>next_state<=s3;flag<='1' ;ir<=databus; --将ROM中的指令赋给IR(指令寄存器)when s3=>next_state<=s4;temp:=ir(7 downto 4); --取指令寄存器的高4位(指令代码MOV 0000,ADD 0001,SUB 0010)-- Mov Add Subif (temp="0000") or (temp="0001")or (temp="0010") thenmar<=ir(3 downto 0); --将数据存储的地址赋给MARelsif temp="1110" thenoutput_data<=ax; -- out overelsif temp="1111" thenrun<='0'; --Hlt overend if;when s4=>next_state<=s5; --在S4状态,将从数据总线上读取数据if temp="0000" then --MOV AX,data overax<=dataBus;elsif temp="0001" then --ADD ax,databx<=databus;f1<='1';elsif temp="0010" then --SUB ax,bxbx<=databus;f1<='1';end if;when s5=>next_state<=s0;if temp="0001" and f1='1' thenax<=ax+bx;f1<='0';elsif temp="0010" and f1='1' thenax<=ax-bx;f1<='0';end if;end case;current_state<=next_state; --此设计使每个状态为两个时钟周期(Attention) end if;end if;end process reg;u1:rom16_8 port map(addrbus,cs,databus);addrbus<=mar when (current_state=s2) or (current_state=s4) else"0000";cs<='0' when (current_state=s2) or (current_state=s4) else'1';databus_out<=databus;end architecture behave;参考书目:微机原理及应用第3章:清华大学出版社VHDL和数字电路设计:科学出版社VHDL实用教程:电子科技大出版社。

简单CPU系统设计及实现

简单CPU系统设计及实现首先,我们需要确定CPU系统的架构。

在本例中,我们将采用单周期处理器设计,该设计非常简单且易于实现。

在该架构中,每个指令在一个时钟周期内完成执行。

接下来,我们需要确定指令集的构成。

在本例中,我们将使用基本的指令集,包括算术操作指令(如加法、减法、乘法、除法)、逻辑操作指令(如与、或、异或)和数据传输指令(如存储、加载和移动数据)。

在开始设计CPU系统之前,我们需要确定CPU寄存器的数量和宽度。

在本例中,我们将使用8个寄存器,每个寄存器的宽度为8位。

这些寄存器将分别用于存储通用数据、存储器地址和指令。

现在我们可以开始设计CPU的数据路径。

数据路径是指数据在CPU内部通过的路径。

在单周期处理器中,数据路径包括指令存储器、程序计数器、寄存器文件、算术逻辑单元(ALU)和存储器。

指令存储器用于存储程序的指令,可以通过程序计数器(PC)来访问。

PC是一个寄存器,它存储下一条指令的地址。

每个时钟周期,PC增加1,以指向下一条指令。

寄存器文件用于存储CPU的寄存器,可以通过寄存器地址来访问。

寄存器文件包括8个通用寄存器。

ALU用于执行算术和逻辑运算。

它从寄存器文件中读取操作数,并将结果写回寄存器文件。

存储器用于存储数据,包括程序的指令和变量。

存储器有两个口,一个用于读取操作,一个用于写入操作。

设计数据路径后,我们需要设计控制单元。

控制单元控制数据路径中的信号流动。

在单周期处理器中,控制单元通常由指令解码器和控制逻辑组成。

指令解码器将二进制指令解码为对数据路径的控制信号。

控制逻辑基于解码的指令生成控制信号。

在实现CPU系统之前,我们需要设计指令的编码方式。

在本例中,我们将使用定长编码,每个指令都有相同的长度,例如8位。

现在我们可以开始实现CPU系统。

我们可以使用硬件描述语言(HDL)来描述和实现CPU系统的各个部分。

常用的HDL包括VHDL和Verilog。

我们可以使用仿真工具来验证CPU系统的功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程报告设计课题: 基本模型计算机设计与实现姓名:专业:学号:日期2011年4月24日——2011年5月日指导教师:国立华侨大学信息科学与工程学院目录1.设计的任务与要求 (1)2.方案论证与选择 (1)3.单元电路的设计和元器件的选择 (5)3.1 六进制电路的设计 (6)3.2 十进制计数电路的设计 (6)3.3 六十进制计数电路的设计 (6)3.4双六十进制计数电路的设计 (7)3.5时间计数电路的设计 (8)3.6 校正电路的设计 (8)3.7 时钟电路的设计 (8)3.8 整点报时电路的设计 (9)3.9 主要元器件的选择 (10)4.系统电路总图及原理 (10)5.经验体会 (10)参考文献 (11)附录A:系统电路原理图 (12)8位CPU的设计一、设计的任务与要求计算机的核心部件CPU通常包含运算器和控制器两大部分。

组成CPU的基本部件有运算部件,寄存器组,微命令产生部件和时序系统等。

这些部件通过CPU内部的总线连接起来,实现它们之间的信息交换。

1.设计目的(1).深入理解基本模型计算机的功能、组成知识;(2).深入学习计算机各类典型指令的执行流程;(3).学习微程序控制器的设计过程和相关技术,掌握LPM_ROM的配置方法。

(4).在掌握部件单元电路实验的基础上,进一步将单元电路组成系统,构造一台基本模型计算机。

(5).定义五条机器指令,并编写相应的微程序,上机调试,掌握计算机整机概念。

掌握微程序的设计方法,学会编写二进制微指令代码表。

(6).通过熟悉较完整的计算机的设计,全面了解并掌握微程序控制方式计算机的设计方法。

2.设计原理在部件实验过程中,各部件单元的控制信号是人为模拟产生的,而本实验将能在微过程控制下自动产生各部件单元控制信号,实现特定的功能。

实验中,计算机数据通路的控制将由微过程控制器来完成,CPU从内存中取出一条机器指令到指令执行结束的一个指令周期,全部由微指令组成的序列来完成,即一条机器指令对应一个微程序。

11该CPU 主要由算术逻辑单元ALU,数据暂存寄存器DR1、DR2,数据寄存器R0~R2,程序计数器PC,地址寄存器AR,程序/数据存储器MEMORAY,指令寄存器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所组成。

图中虚线框内部分包括运算器、控制器、程序存储器、数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现。

虚线框外部分主要是输入/输出装置,包括键盘、数码管、LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及观察CPU 内部工作情况及运算结果。

二、单元电路设计1、运算部件运算部件的任务是对操作数进行加工处理。

主要由三部分组成:(1) 输入逻辑。

(2) 算术/逻辑运算部件ALU。

(3) 输出逻辑。

2.寄存器组计算机工作时,CPU 需要处理大量的控制信息和数据信息。

例如对指令信息进行译码,以便产生相应控制命令对操作数进行算术或逻辑运算加工,并且根据运算结果决定后续操作等。

因此,在CPU 中需要设置若干寄存器,暂时存放这些信息。

在模型CPU中,寄存器组由R0、R1、R2所组成。

3.指令寄存器指令寄存器(IR)用来存放当前正在执行的指令,它的输出包括操作码信息、地址信息等,是产生微命令的主要逻辑依据。

4.程序计数器程序计数器(PC)也称指令指针,用来指示指令在存储器中的存放位置。

当程序顺序执行时,每次从主存取出一条指令,PC 内容就增量计数,指向下一条指令的地址。

增量值取决于现行指令所占的存储单元数。

如果现行指令只占一个存储单元,则PC 内容加1;若现行指令占了两个存储单元,那么PC 内容就要加2。

当程序需要转移时,将转移地址送入PC,使PC 指向新的指令地址。

因此,当现行指令执行完,PC 中存放的总是后续指令的地址;将该地址送往主存的地址寄存器AR,便可从存储器读取下一条指令。

5.地址寄存器CPU 访问存储器,首先要找到需要访问的存储单元,因此设置地址寄存器(AR)来存放被访单元的地址。

当需要读取指令时,CPU 先将PC 的内容送入AR,再由AR将指令地址送往存储器。

当需要读取或存放数据时,也要先将该数据的有效地址送入AR,再对存储器进行读写操作。

6.标志寄存器标志寄存器 F 是用来记录现行程序的运行状态和指示程序的工作方式的,标志位则用来反映当前程序的执行状态。

一条指令执行后,CPU 根据执行结果设置相应特征位,作为决定程序流向的判断依据。

例如,当特征位的状态与转移条件符合时,程序就进行转移;如果不符合,则顺序执行。

在后面将要介绍的较复杂模型计算机设计中设置了两个标志位:进位位Fc:运算后如果产生进位,将Fc 置为1;否则将Fc清为0。

零位Fz:运算结果为零,将Fz置为1,否则将Fz 清为0。

7.微命令产生部件实现信息传送要靠微命令的控制,因此在CPU 中设置微命令产生部件,根据控制信息产生微命令序列,对指令功能所要求的数据传送进行控制,同时在数据传送至运算部件时控制完成运算处理。

微命令产生部件可由若干组合逻辑电路组成,也可以由专门的存储逻辑组成。

产生微命令的方式可分为组合逻辑控制方式和微程序控制方式两种。

在本章所介绍的8 位模型CPU 设计中,采用微程序控制方式通过微程序控制器和微指令存储器产生微命令,因此此CPU 属于复杂指令CISC CPU。

8.时序系统计算机的工作常常是分步执行的,那么就需要有一种时间信号作为分步执行的标志,如周期、节拍等。

节拍是执行一个单步操作所需的时间,一个周期可能包含几个节拍。

这样,一条指令在执行过程中,根据不同的周期、节拍信号,就能在不同的时间发出不同的微命令完成不同的微操作。

周期、节拍、脉冲等信号称为时序信号,产生时序信号的部件称为时序发生器或时序系统,它由一组触发器组成。

由石英晶体振荡器输出频率稳定的脉冲信号,也称时钟脉冲,为CPU 提供时钟基准。

时钟脉冲经过一系列计数分频,产生所需的节拍(时钟周期)信号。

时钟脉冲与周期、节拍信号和有关控制条件相结合,可以产生所需的各种工作脉冲。

三、指令系统的结构及功能的确定1、指令是计算机执行某种操作的命令,而指令系统是一台计算机中所有机器指令的集合。

通常性能较好的计算机都设置有功能齐全、通用性强、指令丰富的指令系统,而指令功能的实现需要复杂的硬件结构来支持。

因此在设计CPU 时,首先要明确机器硬件应具有哪些功能,然后根据这些功能来设置相应指令,包括确定所采用的指令格式、所选择的寻址方式和所需要的指令类型。

设模型机指令系统中包含有五条基本指令,分为算术运算指令、存取指令和控制转移指令等三种类型。

五条机器指令分别是:IN(输入)、ADD(二进制加法)、STA(存数)、OUT(输出)、JMP(无条件转移)。

IN 为单字长(8 位二进制),其余为双字长指令,XX H 为addr对应的十六进制地址码。

(1)微命令和微操作微命令和微操作是一一对应的。

微命令是微操作的控制信号,微操作是微命令的操作过程。

微命令有兼容性和互斥性之分。

兼容性微命令是指那些可以同时产生,共同完成某一些微操作的微命令;而互斥性微命令是指在机器中不允许同时出现的微命令。

兼容和互斥都是相对的,一个微命令可以和一些微命令兼容,和另一些微命令互斥。

对于单独一个微命令,就无所谓兼容性或互斥性了。

(2)微指令、微地址微指令是指控制存储器中的一个单元的内容,即控制字,是若干个微命令的集合,存放控制字的控制存储器的单元地址就称为微地址。

一条微指令通常至少包含两大部分信息:微操作码字段,又称操作控制字段,该字段指出微指令执行的微操作;微地址码字段,又称顺序控制字段,指出下一条要执行的微指令的地址。

(3)微周期所谓微周期是指从控存中读取出一条微指令并执行规定的相应操作所需的时间。

(4)微程序一系列微指令的有序集合就是微程序。

若干条有序的微指令构成了微程序。

微程序可以控制实现一条机器指令的功能。

或者说一条机器指令可以分解为特定的微指令序列。

一旦机器的指令系统确定以后,每条指令所对应的微程序被设计好并且存入控存后,控存总是处于只读的工作状态,所以控存一般采用只读存储器(ROM)存放。

重新设计控存内容就能增加、删除、修改机器指令系统。

在FPGA 中通常采用嵌入式阵列块构成的LPM_ROM 作为控存,存放微指令。

uA5~uA0:微程序控制器的微地址输出信号,是下一条要执行的微指令的微地址。

S3、S2、Sl、S0:由微程序控制器输出的ALU 操作选择信号,以控制执行16 种算术操作或16 种逻辑操作中的某一种操作。

M:微程序控制输出的ALU 操作方式选择信号。

M=0 执行算术操作;M=l执行逻辑操作。

Cn:微程序控制器输出的进位标志信号,Cn=0 表示ALU 运算时最低位有进位;Cn=1 则表示无进位。

WE:微程序控制器输出的RAM 控制信号。

当CE=0 时,如WE=0,为存储器读;如WE=1,为存储器写A9、A8:译码后产生CS0、CS1、CS2 信号,分别作为SW_B、RAM、LED 的选通控制信号。

A 字段(15、14、13):译码后产生与总线相连接的各单元的输入选通信号。

B 字段(12、11、10):译码后产生与总线相连接的各单元的输出选通信号。

C 字段(9、8、7):译码后产生分支判断测试信号P(1)~P(4)和LDPC 信号。

2、微程序设计一个具有五条指令IN、ADD、STA、OUT和JMP 的微程序流程图。

其中方框代表基本的微操作,菱形框为分支判断框。

(1)IN指令为了执行输入指令,CPU 要做两件事情。

首先,由INPUT 输入装置的数据开关SW输入数据送到数据总线上;其次,通过数据总线将输入的数据写入寄存器R0 中。

BUS←SW ;R0←BUS由于输入到数据总线上的数据就是要写入寄存器的数据,因此可以将这两个操作合并成一个操作:R0←SW 3.(2)2.ADD指令R0←R0+(MEM)存储单元的地址是存放在紧跟在操作码后的字节中的,因此,首先要以该字节的内容为地址,即将该单元内容送地址寄存器AR;然后,从AR 所指向的RAM 存储单元取出操作数送给DR2。

由于在取指令操作码时,PC 已经自动加1,指向下一字节,该地址就是存放操作数的存储单元的地址。

通过执行以下三个步骤,可以从存储器中取出操作数送到DR2:AR←PC,PC←PC+1 ;以AR的内容作为取操作数的地址BUS←RAM,AR←BUS ;AR指向存放操作数的RAM单元BUS←RAM,DR2←BUS ;RAM中的数据通过BUS送DR2将R0 中的数据送DR1:DR1←R0在ALU 中进行加法运算,运算结果送R0:R0←(DR1)+(DR2)(3)STA指令向存储器RAM 写数据操作STA,以紧跟在操作码后的字节作为存放操作数地址,将R0 中的数据存入该地址单元。