VHDL点阵显示

LED点阵动画显示控制的VHDL程序实现

VHDL特点 特点

1.功能强大 功能强大 2.可移植性 可移植性 3.独立性 独立性 4.可操作性 可操作性 5.灵活性 灵活性

设计思路

1.数据文档读取 2.实现对数据文档的读取控制 3.数据在LED点阵板显示

LED板送数 板送数

LED点阵板电路图

数字“ 数字“0”

MIF文件格式 文件格式

WIDTH=8; DEPTH=8; ADDRESS_RADIX=BIN; DATA_RADIX=BIN; ADDRESS_RADIX:DATA_RADIX end

设计模块流程

各种信号的输入 CLK CLR GO

主模块:接收控制信号进行数据处理, 并且输出存储器输出数据行数控制以 及LED点阵板对应行号(ROW)

汉字显示

在LED点阵板上显示的“点”字

LED点阵动画显示控制 点阵动画显示控制 的VHDL程序实现 程序实现

学生:胡云龙 指导老师:张家波

VHDL语言 语言

VHDL的英文全称为very-high-speed integrated circuit hardware description language。1978年底,VHDL被美国电气和电 子工程师协会Institute of Electrical and Electronics Engineers (IEEE) 和美国国防部 确认为标准硬件描述语言。

设计程序

P1:process(go) begin if(go'event and go='1')then ----高电频“1”为触发态 if(cntdata<9)then cntdata<=cntdata+1; ----cntdata参数小于9,最大值为cntdata+1 else cntdata<=0; ----其他情况,输出显示“0”的数据 end if; end if; end process P1;

VHDL的实践(3)点阵显示系统的设计

第20、21讲 VHDL的实践(3)—点阵显示系统的设计【课前思考】数字逻辑中关于音乐芯片的设计的过程是怎样的?【学习目标】理解点阵显示系统的设计原理并分析清楚用VHDL实现一个点阵显示系统乐芯片的全部代码描述。

【重 难 点】重点:分析实现一个点阵显示系统的全部VHDL代码描述难点:点阵显示系统的设计原理【教学安排】学时:2 学时【知 识 点】8.3点阵显示系统的设计 (1)8.3点阵显示系统的设计1 系统结构与原理图1是系统的结构框图。

本系统选用的FPGA芯片是美国Altera公司的FLEX10K系列的EPF10K10LC84-4。

该芯片具有576个逻辑单元、84个引脚、72个逻辑阵列块、3个嵌入式阵列块,是一个高集成度的FPGA芯片。

系统由FPGA中的扫描控制模块、只读存储器ROM和FPGA外面的LED点阵显示模块、一个反相器和两个4-16译码器构成。

其中,DZ1、DZ2、DZ3、和DZ4是4个8×8的LED点阵显示模块,由这四个模块组合起来构成了本系统16×16的LED点阵显示模块。

两个4-16译码器(74LS154)和一个反相器配合FPGA中的行扫描控制模块共同完成了16×16点阵显示模块的32行的扫描控制。

FPGA中的只读存储器ROM中保存了要显示的多幅图像的数据,并以8位的数据宽度输出到LED阵显示模块的列端,配合行扫描控制共同完成多幅图像的显示。

图1 系统的结构框图2 扫描控制模块本系统的LED点阵模块如图2所示,共由16×16=256个LED发光二极管组成。

如何在该点阵模块上显示一幅图像是本设计的关键技术。

本设计是采用的一种32路动态分时扫描技术来实现的。

具体方法是,将如图1所示4个8×8阵列的显示模块DZ1、DZ2、DZ3、DZ4采用串行级联的方式构成为一个32行8列的扫描结构。

其列输入端与FPGA内的只读存储器ROM的8位数据输出端口相连;32个行控制端与两个4-16译码器A、B的输出相连;而译码器A、B的输入端和片选信号又与FPGA内的行扫描控制模块的输出端口scan4-scan0相连。

点阵实验设计报告

院系:物理与电子工程学院专业:电子信息工程班级: 2008级3班指导老师:谢小维姓名:刘进学号: 200807014321 实验时间: 2010年12月12日基于VHDL的汉字点阵动态显示系统的设计一、实验目的(1)在MAX+plus II软件平台上,熟练运用VHDL语言,完成16*16点阵的显示设计的软件编辑、编译、综合、仿真。

(2)使用EDA实验箱,实现16*16点阵显示的硬件功能。

(3)学习设计仿真工具的使用方法。

(4)学习层次化设计方法。

二、实验仪器16*16点阵(如图一)、EDA实验箱、MAX+plus II,导线若干图一、16*16点阵三、实验原理3.1 主要原理用动态时钟扫描技术使LED点阵模块显示出我们需要的汉字的列扫描的代码数据。

在有笔划下落处的小方格里填上“1”,无笔划处填上“0”,这样就形成了与这个汉字所对应的二进制数据在该矩形框上的分布。

最后用一个时钟扫描来控制让其输出。

3 .2汉字的显示第二步工作的步骤是:先在扫描模块的控制下,由地址线确定每次由ROM 送出某一列的16个LED所要显示的汉字的控制字节数据,同时由扫描模块输出的5位扫描码经两个4-16译码器解码后决定相应的某一列可以被点亮,而另外31列都不能被点亮。

该状态持续约0.4毫秒后,就接着进行下一行的扫描。

当完成了一次32行的扫描后,也就完成了一帧画面的显示。

重复上述过程不断修改ROM的地址区间的起始地址,转向下一幅画面的数据传送和显示。

如此进行,就可以在LED点阵模块上滚动显示ROM中存储的汉字。

四、VHDL语言程序设计4.1扫描频率控制的部分关键程序process(clk) --显示时序控制beginif clk'event and clk='1' then --上升沿dount<=dount+1;--计数累加if dount=255 thenif S=15 thenS<="0000";--S控制单个汉字扫描周期 elseS<=S+1;end if;S<=S+1;elseS<=S;end if;if cdount<15 then --控制列扫描频率cdount<=cdount+1;elsecdount<="0000";end if;end if;end process;4.2单个汉字扫描的部分关键程序process(cdount,s)begincase cdount iswhen "0000" => lie<="0000";when "0001" => lie<="0001";when "0010" => lie<="0010";when "0011" => lie<="0011";when "0100" => lie<="0100";when "0101" => lie<="0101";when "0110" => lie<="0110";when "0111" => lie<="0111";when "1000" => lie<="1000";when "1001" => lie<="1001";when "1010" => lie<="1010";when "1011" => lie<="1011";when "1100" => lie<="1100";when "1101" => lie<="1101";when "1110" => lie<="1110";when "1111" => lie<="1111";when others=>null;end case;if s="0000" thencase cdount isw h e n"0000"=>h a n g<="0100000000001000"; w h e n"0001"=>h a n g<="0010000000101000"; w h e n"0010"=>h a n g<="0001000001001001"; w h e n"0011"=>h a n g<="0000100110001010"; w h e n"0100"=>h a n g<="0000011010001110"; w h e n"0101"=>h a n g<="0000100001001000"; w h e n"0110"=>h a n g<="0011000000111000"; w h e n"0111"=>h a n g<="0110000000001100"; w h e n"1000"=>h a n g<="0000000000001000";w h e n"1001"=>h a n g<="0000000000000000"; w h e n"1010"=>h a n g<="0000111111111100"; w h e n"1011"=>h a n g<="0100000000000000"; w h e n"1100"=>h a n g<="1000000000000000"; w h e n"1101"=>h a n g<="0111111111111111"; w h e n"1110"=>h a n g<="0000000000000000"; w h e n"1111"=>h a n g<="0000000000000000"; when others =>null;end case;end if;if s="0001" thencase cdount isw h e n"0000"=>h a n g<="0000000000000000"; w h e n"0001"=>h a n g<="0100000001000000"; w h e n"0010"=>h a n g<="0010000001000010"; w h e n"0011"=>h a n g<="0001111111001100"; w h e n"0100"=>h a n g<="0010000000000000"; w h e n"0101"=>h a n g<="0100000100001000"; w h e n"0110"=>h a n g<="0100111111111111"; w h e n"0111"=>h a n g<="0100000100001000"; w h e n"1000"=>h a n g<="0100000100001000"; w h e n"1001"=>h a n g<="0100000100001000"; w h e n"1010"=>h a n g<="0111111111111111"; w h e n"1011"=>h a n g<="0100000100001000"; w h e n"1100"=>h a n g<="0100000110001100"; w h e n"1101"=>h a n g<="0110000100001000"; w h e n"1110"=>h a n g<="0010000000000000"; w h e n"1111"=>h a n g<="0000000000000000";when others => null;end case;end if;end process;--结束进程,各个进程之间是并发执行的4.3 整个程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity lcd1 isport (clk:in std_logic;hang:out std_logic_vector(15 downto 0);lie:out std_logic_vector(3 downto 0));end entity;architecture one of lcd1 issignal dount:std_logic_vector(7 downto 0);signal s,cdount:std_logic_vector(3 downto 0); beginprocess(clk)beginif clk'event and clk='1' thendount<=dount+1;if dount=255 thenif s=1 thens<="0000";elses<=s+1;end if;--s<=s+1;elses<=s;end if;if cdount<15 thencdount<=cdount+1;elsecdount<="0000";end if;end if;end process;process(cdount,s)begincase cdount iswhen "0000" => lie<="0000";when "0001" => lie<="0001";when "0010" => lie<="0010";when "0011" => lie<="0011";when "0100" => lie<="0100";when "0101" => lie<="0101";when "0110" => lie<="0110";when "0111" => lie<="0111";when "1000" => lie<="1000";when "1001" => lie<="1001";when "1010" => lie<="1010";when "1011" => lie<="1011";when "1100" => lie<="1100";when "1101" => lie<="1101";when "1110" => lie<="1110";when "1111" => lie<="1111";when others=>null;end case;if s="0000" thencase cdount isw h e n"0000"=>h a n g<="0100000000001000"; w h e n"0001"=>h a n g<="0010000000101000"; w h e n"0010"=>h a n g<="0001000001001001"; w h e n"0011"=>h a n g<="0000100110001010"; w h e n"0100"=>h a n g<="0000011010001110"; w h e n"0101"=>h a n g<="0000100001001000"; w h e n"0110"=>h a n g<="0011000000111000"; w h e n"0111"=>h a n g<="0110000000001100"; w h e n"1000"=>h a n g<="0000000000001000"; w h e n"1001"=>h a n g<="0000000000000000"; w h e n"1010"=>h a n g<="0000111111111100"; w h e n"1011"=>h a n g<="0100000000000000"; w h e n"1100"=>h a n g<="1000000000000000"; w h e n"1101"=>h a n g<="0111111111111111"; w h e n"1110"=>h a n g<="0000000000000000"; w h e n"1111"=>h a n g<="0000000000000000"; when others =>null;end case;end if;if s="0001" thencase cdount isw h e n"0000"=>h a n g<="0000000000000000"; w h e n"0001"=>h a n g<="0100000001000000"; w h e n"0010"=>h a n g<="0010000001000010"; w h e n"0011"=>h a n g<="0001111111001100"; w h e n"0100"=>h a n g<="0010000000000000"; w h e n"0101"=>h a n g<="0100000100001000"; w h e n"0110"=>h a n g<="0100111111111111"; w h e n"0111"=>h a n g<="0100000100001000"; w h e n"1000"=>h a n g<="0100000100001000"; w h e n"1001"=>h a n g<="0100000100001000"; w h e n"1010"=>h a n g<="0111111111111111"; w h e n"1011"=>h a n g<="0100000100001000"; w h e n"1100"=>h a n g<="0100000110001100"; w h e n"1101"=>h a n g<="0110000100001000"; w h e n"1110"=>h a n g<="0010000000000000"; w h e n"1111"=>h a n g<="0000000000000000";when others => null;end case;end if;end process;end architecture;五、系统调试与仿真5.1、输入完文本之后,对该文本进行功能仿真,然后在没有出现错误的情况下,对文本进行时序仿真,观察其波形如下:5.2、在对该文本进行编辑下载,在这之前,先要设置其器件,选择目标芯片。

点阵汉字显示VHDL语言设计

EDA技术实用教程实验报告实验名称:点阵汉字显示设计系别:XXX专业:电子信息工程姓名:X X X学号:XXXXXXXXX2010.12.216*16的点阵显示设计1、实验目的熟悉MAX+plu sⅡ的VHDL文本设计流程的全过程,学会用可编程逻辑器件设计制作一个16*16的点阵的显示设计。

16*16点阵显示是传统的点阵显示基本应用,它是很多复杂的显示的基础。

这种点阵的显示可以使用多种方法来实现,其中所用到的器件也不尽相同,但是很多基本算法和思想都是相同的,只是根据不同的硬件,具体的方法有所区别。

在此设计中,我所使用的点阵的列式有16个行信号组成的,每一行是由一个单独的位来控制,高电平有效,而列式由四个位矢量来控制的。

例如:“0000”表示第0行,“0000000000000001”表示第1行的点亮。

由于列式由一个矢量决定的,而每一时刻列只能有一个固定的值,因而只能是某一列的如干点亮,因此就决定了只能用逐列扫描的方法。

2、各模块及功能模块CHW控制每个字母显示时间Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity chw isPort (clk:in std_logic;Q:out std_logic_vector(1 downto 0));End chw;Architecture chw_arc of chw isBeginProcess(clk)Variable cnt:integer;Variable tmp:std_logic_vector(1 downto 0);beginIf clk'event and clk='1'thenif cnt<10000 thenCnt:=cnt+1;ElseCnt:=0;If tmp="11"thenTmp:="00";ElseTmp:=tmp+1;End if;End if;end if;Q<=tmp;End process;End chw_arc;模块CNTA产生列选择信号。

苗壮-数电实验-vhdl双色点阵设计

数字电路综合实验报告题目:双色点阵设计实验班级:2011211208姓名:苗壮学号:2011210889一实验要求1.固定红色显示一个汉子或图形,显示亮度4级可调,用一个btn按钮实现亮度调节,亮度变化视觉效果要尽量明显。

2.用从红到绿8级渐变色显示一个固定汉字或图形。

3.分别用单字循环显示,左右滚动显示,上下滚动显示三种显示方式单色显示四个汉字或图形,显示过程中,显示方式用一个btn按钮进行切换。

4.显示的图形或汉字要饱满美观。

提高要求:1.滚动显示过程中实现四种显示颜色的自动变换,颜色变化效果要尽量明显。

2.自拟其它功能。

二系统设计1.设计思路a.因为双色点阵要求几种状态同时发生,因此设置一个传输文字信息的形参sh1~sh8,和颜色控制的参量g1~g8,r1~r8,使文字能同时的发生所需状态,b.同时因亮度需要调节占空比,8种颜色也需要调节占空比。

因此亮度调节和8种颜色模块单独整合入显示模块中,用于最后刷新输入row变量和red,green变量。

c.文字滚动模块因为实验板的逻辑单元限制,每个动画改为10帧左右,包括跳动,左右滚动,上下滚动,和静态四种模块,需要设置一个count计数器,来实现帧的跳转。

d.最后,把按键防抖程序集合进程序内容里,进行仿真,下载测试。

2.总体框图输入button按键防抖btn1~btn4 按键模块(控制器)Clk_1(100hz) c_mode,b_mode,m_mode 输入clk 显示模块case 1:choose color分频模块clkout(5000hz) case 2:choose moveCase 3:choose bright3.模块设计A).Process clk:产生所需的时钟模块。

输出Clk_1,clkout;B).Process bu1~4:防止按键抖动模块。

输出bu1~bu4;C).Process c_mode,b_mode,m_mode:对应改变颜色,改变亮度和改变滚动方式的模块,输出g1~g8,r1~r8,sh1~sh8;D).Process show:刷新双色点阵模块,根据不同的mode输出不同的点阵信息以做到同时三模块完全独立,可以同时发生改变。

利用可编程器件实现点阵式LED显示

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

专题技术与工程应用

VHDL 主要用于描述数字系统的结构 、行为 、功 能和接口 。除了含有许多具有硬件特征语句外 ,语 言形式和描述风格与句法十分类似于一般的计算机 高级语言 。VHDL 的程序结构特点是将一项工程设 计 ,或者设计实体 (可以是一个元件 ,一个电路模块 或一个系统) 分成外部 (或称端口) 和内部 ,即实体的 内部功能和算法完成部分 。在对一个设计实体定义 了外部界面后 ,一旦其内部开发完成后 ,其他的设计 就可以直接调用这个实体 。

图 2 CPLD 内部设置方案

对于 CPLD 的设计分为 4 个模块 :分频器模块 、 扫描驱动控制模块 、读取存储器和移位寄存器模块 。

3 详细设计描述

(1) 读取存储器模块 读取存储器模块的主要功能是发出存储器的地 址码 ,给存储器地址并从相应存储器地址中取数据 。 这个模块主要由地址输出线 ,读取完毕信号端口 ,控 制输入和时钟输入端口组成 ,存储器中的数据是由 单片机来控制不断更新的 ,它的地址是一个连续的 空间 。因此 ,只需要把地址循环相加给出地址就可 以了 ,然后从相应的地址空间里读取数据 。当有的 地址访问过后数据就要更新 ,这时候读取完毕信号 端口给单片机一个回馈的信号 ,来让单片机控制存 储器更新数据 。另外还需要按照在读取数据的时候 要特别注意所选用存储器的时序 ,这样才能稳定可 靠地读出数据 。 (2) 分频器模块 分频器模块的主要的作用是给不同的内部逻辑 和外部电路提供不同频率的时钟信号 。比如给读取 存储器模块合适的频率时钟来满足存储器的时序 , 给移位寄存器模块提供不同的频率做数据的移位 等 。分频器的设计实际上就是一个计数器 ,在这个 模块中一共有 2 个输入端口 (中心时钟输入口和使 能口) 和多个输出的端口 (计数器的各个数组的端 口) ,采用二进制相加 ,2 个中心时钟后计数器的十 位变化 ,这样就达到了二分频的作用 ,4 个时钟过 后 ,计数器的百位开始变化 ,如此起到了四分频的作 用 ,依此类推 ,在条件允许的情况下可以多倍分频达 到分频的效果 。 (3) 移位寄存器模块 由于 595 是一个串入并出的器件 ,而从存储器 中读到的数据是 8 位的数据 ,而控制点阵式 LED 的 寄存器是串入并出的 ,如何把从存储器中读到的 8 位数据并行打入到点阵式 LED 的列上呢 ? 因此 ,在 CPLD 中设置了一个并串转换的移位寄存器 ,把八位 的数据一次打入到这个并串转换的寄存器上 ,然后 每过一个时钟送出一位的数据线串入到那个串入并 出的寄存器上 。并且要在下一个从存储器中读到的 数据打入之前把原来的数据串行串送完毕 ,此时串 出送给 595 的速度应当是从存储器中并行打入数据 的速度的 8 倍 。要满足这样的速度就需要不同的频 率的时钟 ,所以用一个上述的分频器来提供不同的 频率时钟信号 。

基于FPGA及VHDL的LED点阵汉字滚动显示设计方案【VIP专享】

基于FPGA及VHDL的LED点阵汉字滚动显示设计方案发布: 2011-8-31 | 作者: —— | 来源:wangliuguo| 查看: 555次| 用户关注:汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

况且,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如Qua汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

况且,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如QualtusⅡ软件,将硬件描述语言——VHDL程序固化于具有丰富I/O口、内部逻辑和连线资源的FPGA(现场可编程门阵列)中。

该技术具有系统设计效率高、集成度好、保密性强、易于修改、易于实现等优点,成为当今数字系统设计主流技术。

此方式所制作的LED点阵控制器,由于是纯硬件行为,具有速度快、可靠性高、抗干扰能力强、开发周期短等显著优点。

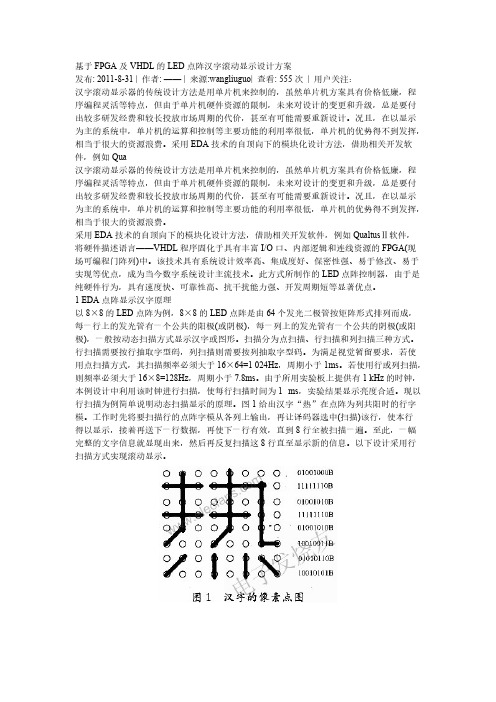

1 EDA点阵显示汉字原理以8×8的LED点阵为例,8×8的LED点阵是由64个发光二极管按矩阵形式排列而成,每一行上的发光管有一个公共的阳极(或阴极),每一列上的发光管有一个公共的阴极(或阳极),一般按动态扫描方式显示汉字或图形。

扫描分为点扫描、行扫描和列扫描三种方式。

行扫描需要按行抽取字型码,列扫描则需要按列抽取字型码。

汉字点阵显示“电子”两字

EDA实验报告汉字矩阵显示计科非师范20121105982余路生一、实验目的:用VHDL语言设计一程序,点阵法静态显示“电子”两个字,然后从左向右推出。

二、实验原理:以下为16×16点阵LED外观及引脚图及其等效电路,只要其对应的X、Y轴顺向偏压,即可使LED发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

应用时限流电阻可以放在X轴或Y轴。

图2.1 16×16点阵LED外观图图2.2 16×16点阵LED等效图本实验采用点扫描法,扫描频率必须大于16×64=1024Hz,周期小于1ms 即可。

若使用第二和第三种方式,则频率必须大于16×8=128Hz,周期小于7.8ms即可符合视觉暂留要求。

此外一次驱动一列或一行(8颗LED)时需外加驱动电路提高电流,否则LED亮度会不足。

汉字的存储:用动态分时扫描技术使LED点阵模块显示图像,需要进行两步工作。

第一步是获得数据并保存,即在存贮器中建立汉字数据库。

第二步是在扫描模块的控制下,配合行扫描的次序正确地输出这些数据。

获得图像数据的步骤是,先将要显示的每一幅图像画在一个如图3.3所示的被分成16×16共256个小方格的矩形框中,再在有笔划下落处的小方格里填上“1”,无笔划处填上“0”,这样就形成了与这个汉字所对应的二进制数据在该矩形框上的分布,再将此分布关系以32×16的数据结构组成64个字节的数据,并保存在只读存贮器ROM中。

以这种方式将若干个汉字的数据贮存在存贮器内,就完成了图像数据库的建立工作。

4图3.3 16×16LED点阵模块然后,依次对多汉字抽取像素信息,并按序排队存放起来,便可得到一个待显示数据序列。

将这个序列存到ROM中进一步通过寻址的方法来控制该数据序列的释放过程,就可实现在LED 发光二极管点阵上滚动显示多汉字信息的目的。

图2.3 滚动显示多汉字信息的原理示意图汉字的显示:第二步工作的步骤是:先在扫描模块的控制下,由地址线确定每次由ROM送出某一列的16个LED所要显示的汉字的控制字节数据,同时由扫描模块输出的5位扫描码经两个4-16译码器解码后决定相应的某一列可以被点亮,而另外31列都不能被点亮。

vhdl实验报告_16乘16点阵_列选_显示

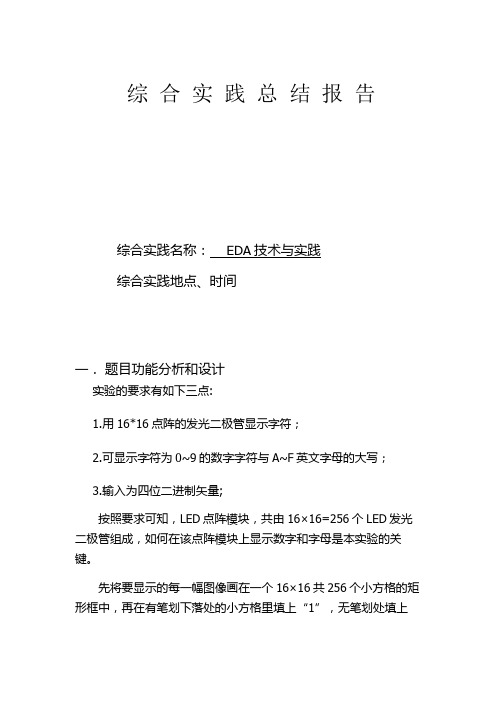

综合实践总结报告综合实践名称: EDA技术与实践综合实践地点、时间一.题目功能分析和设计实验的要求有如下三点:1.用16*16点阵的发光二极管显示字符;2.可显示字符为0~9的数字字符与A~F英文字母的大写;3.输入为四位二进制矢量;按照要求可知,LED点阵模块,共由16×16=256个LED发光二极管组成,如何在该点阵模块上显示数字和字母是本实验的关键。

先将要显示的每一幅图像画在一个16×16共256个小方格的矩形框中,再在有笔划下落处的小方格里填上“1”,无笔划处填上“0”,这样就形成了与这个汉字所对应的二进制数据在该矩形框上的分布以数字8为例,点阵分布为:0000000000000000000000000000000000011111111110000001111111111000000110000001100000011000000110000001100000011000000111111111100000011111111110000001100000011000000110000001100000011000000110000001111111111000000111111111100000000000000000000000000000000000考虑到实际物理实验平台上点阵发光二极管的原理,以下为16×16点阵LED外观图,只要其对应的X、Y轴顺向偏压,即可使LED 发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

所以我采用行列扫描的方法,用四位二进制数做列选信号(总共16列),如选中第一列,则扫描第一列之中哪些行是高电平(1),哪些行是低电平(0);为高电平的则点亮,为低电平的不亮。

(列信号都接地)。

如此,列选信号由“0000”变到“1111”时,16列扫描完毕,一个字也就出来了,列选信号重新由“0000”开始扫描。

注意扫描频率必须要足够快,才能保证显示一个数字或字母时所有灯在肉眼看来是同时在闪烁的。

汉字点阵显示VHDL源程序

汉字点阵显示VHDL源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity hzxs isport(clk1,clk2:in std_logic;rd:out std_logic;we: out std_logic;ledw:out std_logic_vector(2 downto 0); d:out std_logic_vector(0 downto 7));end hzxs;architecture hav of hzxs issignal count:std_logic_vector(0 to 2);signal a: std_logic_vector(3 downto 0);beginprocess(clk2)beginif clk2'event and clk2='1' thencount<=count+1;end if;ledw<=count;a(2 downto 0)<=count;end process;process(clk1)beginif clk1'event and clk1='1' thena(3)<=not a(3);end if;end process;process(a)begincase a iswhen"0000"=>d<="10110100";--数when"0001"=>d<="11111111"; when"0010"=>d<="01001010"; when"0011"=>d<="11011010"; when"0100"=>d<="11110110"; when"0101"=>d<="11100110"; when"0110"=>d<="01110110"; when"0111"=>d<="11011011"; when"1000"=>d<="00010000";--字when"1001"=>d<="11111111";when"1010"=>d<="11111101"; when"1011"=>d<="00001100"; when"1100"=>d<="11111111"; when"1101"=>d<="00010000"; when"1110"=>d<="00010000"; when"1111"=>d<="00001100";when others=>d<="00000000";end case;end process;rd<='1';we<='0';end hav;数字抢答器VHDL源程序1)抢答器QDQlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity qdq isport(clr:in std_logic;a,b,c,d:in std_logic;an,bn,cn,dn:out std_logic);end qdq;architecture hav of qdq issignal ss:std_logic_vector(0 to 3);beginss<=a&b&c&d;process(clr,a,b,c,d)beginif clr='1' thencase ss iswhen "1000"=>an<='1';bn<='0';cn<='0';dn<='0'; when "0100"=>an<='0';bn<='1';cn<='0';dn<='0'; when "0010"=>an<='0';bn<='0';cn<='1';dn<='0'; when "0001"=>an<='0';bn<='0';cn<='0';dn<='1'; when others=>an<='0';bn<='0';cn<='0';dn<='0'; end case;elsif clr='0' thenan<='0';bn<='0';cn<='0';dn<='0';end if;end process;end hav;2)计分器JFQlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity jfq isport(en1:in std_logic;clk3:in std_logic;bs:out std_logic_vector(3 downto 0);ss:out std_logic_vector(3 downto 0);gs:out std_logic_vector(3 downto 0);add:in std_logic;dec:in std_logic);end jfq;architecture hav of jfq isbeginprocess(clk3,en1,add,dec)variable ssw:std_logic_vector(3 downto 0); variable bsw:std_logic_vector(3 downto 0); beginbsw:="0001";if clk3='1' and clk3'event thenif en1='1' thenif add='1' thenif ssw="1001" thenbsw:=bsw+1;ssw:="0000";elsessw:=ssw+1;end if;elsif dec='1' thenif ssw="1111" thenbsw:=bsw-1;ssw:="1001";elsessw:=ssw-1;end if;end if;end if;end if;ss<=ssw;bs<=bsw;gs<="0000";end process;end hav;3) 选择器XZQlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity xzq isport( a1,b1:in std_logic;abw:in std_logic_vector(0 to 3);asw:in std_logic_vector(0 to 3);agw:in std_logic_vector(0 to 3);bbw:in std_logic_vector(0 to 3);bsw:in std_logic_vector(0 to 3);bgw:in std_logic_vector(0 to 3);obw:out std_logic_vector(0 to 3);osw:out std_logic_vector(0 to 3);ogw:out std_logic_vector(0 to 3)); end xzq;architecture hav of xzq isbeginprocess(a1,b1)beginif a1='1' and b1='0' thenobw<=abw;osw<=asw;ogw<=agw;elsif a1='0' and b1='1' thenobw<=bbw;osw<=bsw;ogw<=bgw;end if;end process;end hav;4)译码器YMQlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity ymq isport( clk2:in std_logic;bw:in std_logic_vector(3 downto 0);sw:in std_logic_vector(3 downto 0);gw:in std_logic_vector(3 downto 0);y:out std_logic_vector(7 downto 0);ledw:out std_logic_vector(2 downto 0)); end ymq;architecture hav of ymq issignal knum:std_logic_vector(3 downto 0); signal count:std_logic_vector(2 downto 0); beginprocess(clk2)beginif clk2'event and clk2='1' thenif count<2 thencount<=count+1;elsecount<="000";end if;end if;end process;ledw<=count;knum<=gw when count=0 elsesw when count=1 elsebw when count=2 ;y<="00111111" when knum="0000" else "00000110" when knum="0001" else"01011011" when knum="0010" else"01001111" when knum="0011" else"01100110" when knum="0100" else"01101101" when knum="0101" else"01111101" when knum="0110" else"00000111" when knum="0111" else"01111111" when knum="1000" else"01101111" when knum="1001" else"00000000" ;end hav;。

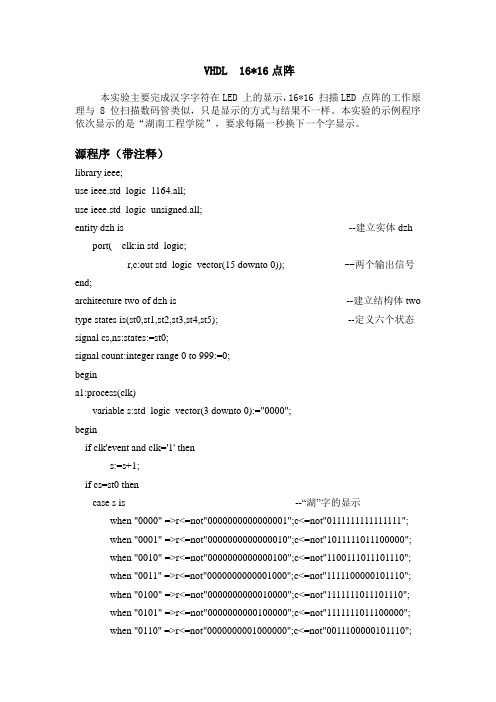

VHDL 16

VHDL 16*16点阵本实验主要完成汉字字符在LED 上的显示,16*16 扫描LED 点阵的工作原理与8 位扫描数码管类似,只是显示的方式与结果不一样。

本实验的示例程序依次显示的是“湖南工程学院”,要求每隔一秒换下一个字显示。

源程序(带注释)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dzh is --建立实体dzh port( clk:in std_logic;r,c:out std_logic_vector(15 downto 0)); --两个输出信号end;architecture two of dzh is --建立结构体two type states is(st0,st1,st2,st3,st4,st5); --定义六个状态signal cs,ns:states:=st0;signal count:integer range 0 to 999:=0;begina1:process(clk)variable s:std_logic_vector(3 downto 0):="0000";beginif clk'event and clk='1' thens:=s+1;if cs=st0 thencase s is --“湖”字的显示when "0000" =>r<=not"0000000000000001";c<=not"0111111111111111";when "0001" =>r<=not"0000000000000010";c<=not"1011111011100000";when "0010" =>r<=not"0000000000000100";c<=not"1100111011101110";when "0011" =>r<=not"0000000000001000";c<=not"1111100000101110";when "0100" =>r<=not"0000000000010000";c<=not"1111111011101110";when "0101" =>r<=not"0000000000100000";c<=not"1111111011100000";when "0110" =>r<=not"0000000001000000";c<=not"0011100000101110";when "0111" =>r<=not"0000000010000000";c<=not"1100101110101110";when "1000" =>r<=not"0000000100000000";c<=not"1111101110100000";when "1001" =>r<=not"0000001000000000";c<=not"1111101110101110";when "1010" =>r<=not"0000010000000000";c<=not"1111101110101110";when "1011" =>r<=not"0000100000000000";c<=not"1110101110101110";when "1100" =>r<=not"0001000000000000";c<=not"1101100000101110";when "1101" =>r<=not"0010000000000000";c<=not"1011111111101110";when "1110" =>r<=not"0100000000000000";c<=not"0111111111011100";when "1111" =>r<=not"1000000000000000";c<=not"1111111111111111";when others =>null;end case;elsif cs=st1 thencase s is --“南”字的显示when "0000" =>r<=not"0000000000000001";c<=not"1111111111111111";when "0001" =>r<=not"0000000000000010";c<=not"1111111110111111";when "0010" =>r<=not"0000000000000100";c<=not"1111111101111111";when "0011" =>r<=not"0000000000001000";c<=not"1100000000000111";when "0100" =>r<=not"0000000000010000";c<=not"1111111011111111";when "0101" =>r<=not"0000000000100000";c<=not"1111110111111111";when "0110" =>r<=not"0000000001000000";c<=not"1100000000000111";when "0111" =>r<=not"0000000010000000";c<=not"1101101110110111";when "1000" =>r<=not"0000000100000000";c<=not"1101110101110111";when "1001" =>r<=not"0000001000000000";c<=not"1101100000110111";when "1010" =>r<=not"0000010000000000";c<=not"1101111011110111";when "1011" =>r<=not"0000100000000000";c<=not"1101000000010111";when "1100" =>r<=not"0001000000000000";c<=not"1101111011110111";when "1101" =>r<=not"0010000000000000";c<=not"1101111011100111";when "1110" =>r<=not"0100000000000000";c<=not"1111111111111111";when "1111" =>r<=not"1000000000000000";c<=not"1111111111111111";when others =>null;end case;elsif cs=st2 thencase s is --“工”字的显示when "0000" =>r<=not"0000000000000001";c<=not"1111111111111111";when "0001" =>r<=not"0000000000000010";c<=not"1111111111111111";when "0010" =>r<=not"0000000000000100";c<=not"1111111111111111";when "0011" =>r<=not"0000000000001000";c<=not"1100000000000111";when "0100" =>r<=not"0000000000010000";c<=not"1111111011111111";when "0101" =>r<=not"0000000000100000";c<=not"1111111011111111";when "0110" =>r<=not"0000000001000000";c<=not"1111111011111111";when "0111" =>r<=not"0000000010000000";c<=not"1111111011111111";when "1000" =>r<=not"0000000100000000";c<=not"1111111011111111";when "1001" =>r<=not"0000001000000000";c<=not"1111111011111111";when "1010" =>r<=not"0000010000000000";c<=not"1111111011111111";when "1011" =>r<=not"0000100000000000";c<=not"1111111011111111";when "1100" =>r<=not"0001000000000000";c<=not"1100000000000111";when "1101" =>r<=not"0010000000000000";c<=not"1111111111111111";when "1110" =>r<=not"0100000000000000";c<=not"1111111111111111";when "1111" =>r<=not"1000000000000000";c<=not"1111111111111111";end case;elsif cs=st3 thencase s is --“程”字的显示when "0000" =>r<=not"0000000000000001";c<=not"1111111111111111";when "0001" =>r<=not"0000000000000010";c<=not"1111111111111111";when "0010" =>r<=not"0000000000000100";c<=not"1111110110000011";when "0011" =>r<=not"0000000000001000";c<=not"1100001110111011";when "0100" =>r<=not"0000000000010000";c<=not"1111011110000011";when "0101" =>r<=not"0000000000100000";c<=not"1111011111111111";when "0110" =>r<=not"0000000001000000";c<=not"1000000100000001";when "0111" =>r<=not"0000000010000000";c<=not"1110001111101111";when "1000" =>r<=not"0000000100000000";c<=not"1101010111101111";when "1001" =>r<=not"0000001000000000";c<=not"1101011010000011";when "1011" =>r<=not"0000100000000000";c<=not"1111011111101111";when "1100" =>r<=not"0001000000000000";c<=not"1111011111101111";when "1101" =>r<=not"0010000000000000";c<=not"1111011100000001";when "1110" =>r<=not"0100000000000000";c<=not"1111111111111111";when "1111" =>r<=not"1000000000000000";c<=not"1111111111111111";when others =>null;end case;elsif cs=st4 thencase s is --“学”字的显示when "0000" =>r<=not"0000000000000001";c<=not"1111111111111111";when "0001" =>r<=not"0000000000000010";c<=not"1111011011110111";when "0010" =>r<=not"0000000000000100";c<=not"1111101101101111";when "0011" =>r<=not"0000000000001000";c<=not"1111111111111111";when "0100" =>r<=not"0000000000010000";c<=not"1110000000000011";when "0101" =>r<=not"0000000000100000";c<=not"1110111111111011";when "0110" =>r<=not"0000000001000000";c<=not"1101110000010111";when "0111" =>r<=not"0000000010000000";c<=not"1111111111011111";when "1000" =>r<=not"0000000100000000";c<=not"1111111100111111";when "1001" =>r<=not"0000001000000000";c<=not"1111111101111111";when "1010" =>r<=not"0000010000000000";c<=not"1111100000001111";when "1011" =>r<=not"0000100000000000";c<=not"1111111101111111";when "1100" =>r<=not"0001000000000000";c<=not"1111111101111111";when "1101" =>r<=not"0010000000000000";c<=not"1111111001111111";when "1110" =>r<=not"0100000000000000";c<=not"1111111111111111";when "1111" =>r<=not"1000000000000000";c<=not"1111111111111111";when others =>null;end case;elsif cs=st5 thencase s is --“院”字的显示when "0000" =>r<=not"0000000000000001";c<=not"1111111110111111";when "0010" =>r<=not"0000000000000100";c<=not"1011010000000001";when "0011" =>r<=not"0000000000001000";c<=not"1011010111111101";when "0100" =>r<=not"0000000000010000";c<=not"1010101111111011";when "0101" =>r<=not"0000000000100000";c<=not"1001111100001111";when "0110" =>r<=not"0000000001000000";c<=not"1010011111111111";when "0111" =>r<=not"0000000010000000";c<=not"1011010000000011";when "1000" =>r<=not"0000000100000000";c<=not"1011011101101111";when "1001" =>r<=not"0000001000000000";c<=not"1000111101101111";when "1010" =>r<=not"0000010000000000";c<=not"1011111101101111";when "1011" =>r<=not"0000100000000000";c<=not"1011111011101101";when "1100" =>r<=not"0001000000000000";c<=not"1011110111100001";when "1101" =>r<=not"0010000000000000";c<=not"1011111111111111";when "1110" =>r<=not"0100000000000000";c<=not"1111111111111111";when "1111" =>r<=not"1000000000000000";c<=not"1111111111111111";when others =>null;end case;else null;end if;end if;end process a1;a2:process(clk) --下一状态的转换beginif clk'event and clk='1' thenif count<999 thencount<=count+1;else count<=0;case cs iswhen st0=>ns<=st1;when st1=>ns<=st2;when st2=>ns<=st3;when st3=>ns<=st4;when st4=>ns<=st5;when st5=>ns<=st0;when others=>ns<=st0;end case;end if;end if;end process a2;a3:process(clk) --当前状态的转换beginif clk'event and clk='1' thencs<=ns;end if;end process a3;end architecture;。

硬件描述语言 VHDL AD DA 点阵 矩阵键盘 液晶显示知识讲解

Input Data

0 1 0 1 0 1 X X

CE

CS DAC data Latch

Condition

0

0

0

“Transparent”

0

0

1

“Transparent”

0

0

Latching

0

1

Latching

0

0

Latching

0

• begin

•

if clk'event and clk='1' then

•

if cnt<8 then

•

cnt:=cnt+1;

•

q<='0';

•

else if cnt>7 then

•

cnt:=cnt+;

• end if;

•

end if;

•

end if;

• end process;

• end rtl;

第三章第四节

利用可编程逻辑器件进行 D/A和A/D控制接口的设计

1 D/A和A/D的应用

A/D和D/A转换器是把微型计算机的 应用领域扩展到检测和过程控制的必要 装置,是把计算机和生产过程、科学实 验过程联系起来的重要桥梁。下图给出 了A/D、D/A转换器在微机检测和控制系 统中的应用实例框图。

2 在可编程逻辑器件中的D/A接口设计

分频仿真时序图

2. 模块SANJIAO如下图所示。它是三角波产

生模块。

sjb

clk reset

q[7..0]

inst5

VHDL点阵显示

VHDL点阵显示数字电路课程设计报告课程:基于FPGA的点阵显示控制器的设计学院:电气信息工程学院专业:测控技术与仪器班级:姓名:学号:合姓名:日期:一、引言随着我国经济的高速发展,对公共场合发布信息的需求日益增长,利用LED 点阵滚动显示汉字的出现正好适应了这一市场需求,已经成为信息传播的一种重要手段。

采用传统方法设计的汉字滚动显示器,通常需要使用单片机、存储器和制约逻辑电路来进行PCB板级的系统集成。

尽管这种方案有单片机软件的支持较为灵活,但是由于受硬件资源的限制,未来对设计的变更和升级,总是难以避免要付出较多研发经费和较长投放市场周期的代价。

随着电子设计自动化(EDA)技术的进展,基于可编程FPGA器件进行系统芯片集成的新设计方法,也正在快速地到代基于PCB板的传统设计方式。

因此,基于FPGA 和VHDL语言实现在8*8点阵上的汉字静态或一屏显示问题。

二、课题要求(1)技术要求1根据电路特点,用层次设计概念。

将此设计任务分成若干模块,规定每一模块的功能和各模块之间的借口,透视加深层次化设计概念;2软件的原件管理深层含义,以及模块元件之间的连接概念,对于不同目录下的同一设计,如何熔合;3适配划分前后的仿真内容有何不同概念,仿真信号对象有何不同,有更深一步了解。

熟悉了FPGA设计的调试过程中手段的多样化;4按适配划分后的管脚定位,同相关功能块硬件电路接口连线;(2)功能要求1在8*8点阵上显示汉字2可以静态显示或一屏显示3利用拨码开关来实现静态显示与一屏显示切换(3)本人的工作三、设计方案(1)工作原理8*8点阵原理:按照要求可知,点阵模块,共由8*8=64个发光二极管组成,如何在该点阵模块上显示汉字是本实验的关键。

先将要显示的每幅图像画在8*8共64个小方格的矩形框中,再在有笔划下落处的小方格里填上“1”,五笔划处填上“0”,这样就形成了与这个汉字所对应的二进制数据在该矩形矿上的分布以“正”为例,点阵分布为:1000000010000001111100011000000111111111100010011000100110000000(2)原理框图四、单元电路设计,仿真结果与分析(1)静态显示“正”library ieee;ENTITY peng isport(clk,en:in std_logic;lie:out std_logic_vector(7 downto 0); --列com:out std_logic_vector(7 downto 0));--行End peng;Architecture a of peng issignal st1:std_logic_vector(7 downto 0);signal osc:std_logic;signal osd:std_logic;signal d_ff:std_logic_vector(27 downto 0);signal data:std_logic_vector(7 downto 0);signal d0,d1,d2,d3,d4,d5,d6,d7:std_logic_vector(7 downto 0);signal lie0,lie1,lie2,lie3,lie4,lie5,lie6,lie7:std_logic_vector(7 downto 0);Begincom<=data;lie<=st1;d0<="10000000";d1<="10000001";d2<="11110001";d3<="10000001";d4<="11111111";d5<="10001001";d6<="10001001";d7<="10000000";--字库正First:processbeginwait until clk='1';if(d_ff(27 downto 0)>=2e8)thend_ff(27 downto 0)<="0000000000000000000000000000";elsed_ff(27 downto 0)<=d_ff+1;end if;osc<=not d_ff(10);end process first;second:process(osc)beginif(osc='1' and osc'event and en='0')thenif st1(7 downto 0)="00000000"or st1(7 downto 0)="01111111"thenst1(7 downto 0)<="11111110";data<=d0;elsif st1(7 downto 0)="11111110"thenst1(7 downto 0)<="11111101";data<=d1;elsif st1(7 downto 0)="11111101"thenst1(7 downto 0)<="11111011";data<=d2;elsif st1(7 downto 0)="11111011"thenst1(7 downto 0)<="11110111";data<=d3;elsif st1(7 downto 0)="11110111"thenst1(7 downto 0)<="11101111";data<=d4;elsif st1(7 downto 0)="11101111"thenst1(7 downto 0)<="11011111";data<=d5;elsif st1(7 downto 0)="11011111"thenst1(7 downto 0)<="10111111";data<=d6;elsif st1(7 downto 0)="10111111"thenst1(7 downto 0)<="01111111";data<=d7;end if;end if;end process second;end a;(2)一屏显示“上下五千年”Library ieee;Entity weng isPort(Clk,en:in std_logic;lie:out std_logic_vector(7 downto 0);--列Com:out std_logic_vector(7 downto 0));--行End weng;Architecture a of weng issignal st1:std_logic_vector(7 downto 0);signal osc:std_logic;signal osd:std_logic;signal d_ff:std_logic_vector(27 downto 0);signal data:std_logic_vector(7 downto 0);signal d0,d1,d2,d3,d4,d5,d6,d7:std_logic_vector(7 downto 0);signal lie0,lie1,lie2,lie3,lie4,lie5,lie6,lie7:std_logic_vector(6 downto 0);begincom<=data;lie<=st1;D0<="10000000"when lie0(6 downto 0)="0000000"else"00000001"when lie0(6 downto 0)="0000001"else"10000000"when lie0(6 downto 0)="0000010"else"00010000"when lie0(6 downto 0)="0000011"else"00100100"when lie0(6 downto 0)="0000100"else"00000000";D1<="10000000"when lie0(6 downto 0)="0000000"else "00000001"when lie0(6 downto 0)="0000001"else "10001001"when lie0(6 downto 0)="0000010"else "00010100"when lie0(6 downto 0)="0000011"else "00111011"when lie0(6 downto 0)="0000100"else "00000000";D2<="10000000"when lie0(6 downto 0)="0000000"else "00000001"when lie0(6 downto 0)="0000001"else "10001001"when lie0(6 downto 0)="0000010"else "00010100"when lie0(6 downto 0)="0000011"else "00101010"when lie0(6 downto 0)="0000100"else "00000000";D3<="11111111"when lie0(6 downto 0)="0000000"else "11111111"when lie0(6 downto 0)="0000001"else "11111111"when lie0(6 downto 0)="0000010"else "11111100"when lie0(6 downto 0)="0000011"else "00101010"when lie0(6 downto 0)="0000100"else "00000000";D4<="10010000"when lie0(6 downto 0)="0000000"else "00001001"when lie0(6 downto 0)="0000001"else "10001001"when lie0(6 downto 0)="0000010"else "00010010"when lie0(6 downto 0)="0000011"else "11111110"when lie0(6 downto 0)="0000100"else "00000000";D5<="10010000"when lie0(6 downto 0)="0000000"else "00010001"when lie0(6 downto 0)="0000001"else "10001001"when lie0(6 downto 0)="0000010"else "00010001"when lie0(6 downto 0)="0000011"else "00101010"when lie0(6 downto 0)="0000100"else "00000000";D6<="10010000"when lie0(6 downto 0)="0000000"else "00100001"when lie0(6 downto 0)="0000001"else "11111000"when lie0(6 downto 0)="0000010"else "00010000"when lie0(6 downto 0)="0000011"else "00101010"when lie0(6 downto 0)="0000100"else "00000000";D7<="10000000"when lie0(6 downto 0)="0000000"else"00000001"when lie0(6 downto 0)="0000001"else"10000000"when lie0(6 downto 0)="0000010"else"00010000"when lie0(6 downto 0)="0000011"else"00100000"when lie0(6 downto 0)="0000100"else"00000000";first:processbeginwait until clk='1';if(d_ff(27 downto 0)>=2e8)thend_ff(27 downto 0)<="0000000000000000000000000000";elsed_ff(27 downto 0)<=d_ff+1;end if;osc<=not d_ff(10);osd<=not d_ff(26);end process first;second:process(osc)beginif(osc='1' and osc'event and en='0')thenif st1(7 downto 0)="00000000"or st1(7 downto 0)="01111111"then st1(7 downto 0)<="11111110";data<=d0;elsif st1(7 downto 0)="11111110"thenst1(7 downto 0)<="11111101";data<=d1;elsif st1(7 downto 0)="11111101"thenst1(7 downto 0)<="11111011";data<=d2;elsif st1(7 downto 0)="11111011"thenst1(7 downto 0)<="11110111";data<=d3;elsif st1(7 downto 0)="11110111"thenst1(7 downto 0)<="11101111";data<=d4;elsif st1(7 downto 0)="11101111"thenst1(7 downto 0)<="11011111";data<=d5;elsif st1(7 downto 0)="11011111"thenst1(7 downto 0)<="10111111";data<=d6;elsif st1(7 downto 0)="10111111"thenst1(7 downto 0)<="01111111";data<=d7;end if;end if;end process second;third:process(osd)beginif(osd='1' and osd'event and en='0')thenif lie0(6 downto 0)="0000100"thenlie0(6 downto 0)<="0000000";else lie0(6 downto 0)<=lie0+1;end if;end if;end process third;end a;五.顶层文件电路设计,仿真结果与分析顶层文件library ieee;entity zong isport( a:in std_logic_vector(1 downto 0);clk:in std_logic;hang:out std_logic_vector(7 downto 0); lie:out std_logic_vector(7 downto 0)); end entity zong;architecture one of zong iscomponent peng isport(clk,en:in std_logic;lie:out std_logic_vector(7 downto 0); --列 com:out std_logic_vector(7 downto 0)); end component;component weng isPort(Clk,en:in std_logic;lie:out std_logic_vector(7 downto 0);--列 Com:out std_logic_vector(7 downto 0));--行end component;signal h1,h2:std_logic_vector(7 downto 0); signal l1,l2:std_logic_vector(7 downto 0);beginu1:peng port map(clk=>clk,en=>a(1),com=>h1,lie=>l1);u2:weng port map(clk=>clk,en=>a(0),com=>h2,lie=>l2);hang<=h1 or h2;lie<=l1 or l2;end architecture one;六、调试结果创建工程在Quartus II 中新建一个VHDL File文件,将vhdl代码输入这个文件,并保存到工作目录,名为zong.vhd。

点阵显示实验

点阵显示实验16*16点阵显示实验引言当今,数字系统的设计可以直接面向用户的需求,根据系统功能的要求,从上到下逐层完成相应的描述、综合、优化、仿真与验证,直到生成器件。

而FPGA(Field Programmable Gate Array,现场可编程门镇列)以设计灵活及速度快的特点,在数字专用集成电路的设计中得到了广泛应用。

本文介绍的汉字显示系统,将16*16点阵与FPGA巧妙结合,采用VHDL(VHSIC Hardware Description Language,硬件描述语言)进行功能描述一、点阵显示原理1点阵模块说明此设计采用4块8*8的点阵块组成16*16的点阵显示模块1.18*8点阵块工作原理如图1所示。

8*8点阵块工作方式:Q端加正电压,COM端接地时发光二管点亮。

例如,当COM8接地且Q1~Q8分别接高电平时,第一行亮。

同理,当COM7接地,Q1~Q8分别接高电平时,第二行亮。

依此类推。

当Q5端加高电平时,分别让COM1~COM8接地,第一12列亮。

其它列依此类推。

1.2 16*16点阵模块用4块8*8的点阵块组成16*16的点阵模块显示汉字,连接关系如图2所示。

Q0~Q15成为点阵块的行线,COM0~COM15形成点阵块的列线。

1.3 行列驱动由循环计数器输出经放大后的驱动点阵,形成动态扫描,分别控制一列中的每个灯,当列线发出信号后,行线同时发出数据,这样就将一个汉字由左到右分成16列。

在完成各列的同时,行线发出行数据,一个循环就可以将一个汉字完整的重现在16*16的点阵模块上。

本实验主要完成汉字字符在LED 上的显示,16*16扫描LED 点阵的工作原理与8位扫描数码管类似,只是显示的方式与结果不一样而已。

下面就本实验系统的16*16点阵的工件原理做一些简单的说明。

16*16点阵由此256个LED通过排列组合而形成16行*16列的一个矩阵式的LED 阵列,俗称16*16点阵。

LED点阵显示的VHDL程序代码

附录带有注释的VHDL程序代码:-------------------------------------------------------- Design unit: dot_led(display) (Entity and Architectures)-- File name : dot_led.vhd-- Description: Matrix dot leds display-- Limitations: None-- System : VHDL'93-- Author : Fan Bishuang-- Email : fbshfj@-- Revision : Version 1.0 16/5/05------------------------------------------------------library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;use IEEE.std_logic_arith.all;entity dot_led_fanye isport(clk :in std_logic; --system clk(250kHz)set:in bit;R:out std_logic_vector(3 downto 0); --Matrix dot leds row input,for R="0000", the first line is enabled.L:out std_logic_vector(15 downto 0)); --Matrix dot leds line inputend dot_led_fanye;architecture display of dot_led_fanye issignal clk1:std_logic;signal R_val:std_logic_vector(3 downto 0);signal cnt:integer range 0 to 250000;signald0,d1,d2,d3,d4,d5,d6,d7,d8,d9,d10,d11,d12,d13,d14,d15:std_logic_vector(15 downto 0);signal sel:integer range 0 to 8;begind0<=X"0200"when sel=0 else ------------“电”字第1行X"0000"when sel=1 else ------------“子”字第1行X"0000"when sel=2 else ------------“一”字第1行X"0100"when sel=3 else ------------“班”字第1行X"0000"when sel=4 else ------------“05”字第1行X"0010"when sel=5 else ------------“号”字第1行X"0100"when sel=6 else ------------“韦”字第1行X"0200"when sel=7 else ------------“文”字第1行X"0000"when sel=8 else ------------“写”字第1行X"0000"; -------否则熄灭第1行所有LEDd1<=X"0200"when sel=0 else ------------“电”字第2行X"3FF0"when sel=1 else ------------“子”字第2行X"0000"when sel=2 else ------------“一”字第2行X"0904"when sel=3 else ------------“班”字第2行X"0000"when sel=4 else ------------“05”字第2行X"1FF8"when sel=5 else ------------“号”字第2行X"0100"when sel=6 else ------------“韦”字第2行X"0100"when sel=7 else ------------“文”字第2行X"7FFE"when sel=8 else ------------“写”字第2行X"0000"; -------否则熄灭第2行所有LEDd2<=X"0010"when sel=1 else ------------“子”字第3行X"0000"when sel=2 else ------------“一”字第3行X"7DFE"when sel=3 else ------------“班”字第3行X"3CFE"when sel=4 else ------------“05”字第3行X"1010"when sel=5 else ------------“号”字第3行X"0104"when sel=6 else ------------“韦”字第3行X"0104"when sel=7 else ------------“文”字第3行X"4002"when sel=8 else ------------“写”字第3行X"0000"; -------否则熄灭第3行所有LEDd3<=X"7FF8"when sel=0 else ------------“电”字第4行X"0020"when sel=1 else ------------“子”字第4行X"0000"when sel=2 else ------------“一”字第4行X"2110"when sel=3 else ------------“班”字第4行X"4240"when sel=4 else ------------“05”字第4行X"1010"when sel=5 else ------------“号”字第4行X"FFFE"when sel=6 else ------------“韦”字第4行X"FFFE"when sel=7 else ------------“文”字第4行X"8804"when sel=8 else ------------“写”字第4行X"0000"; -------否则熄灭第4行所有LEDd4<=X"4210"when sel=0 else ------------“电”字第5行X"0040"when sel=1 else ------------“子”字第5行X"0000"when sel=2 else ------------“一”字第5行X"2510"when sel=3 else ------------“班”字第5行X"4240"when sel=4 else ------------“05”字第5行X"0100"when sel=6 else ------------“韦”字第5行X"1010"when sel=7 else ------------“文”字第5行X"0820"when sel=8 else ------------“写”字第5行X"0000"; -------否则熄灭第5行所有LEDd5<=X"4210"when sel=0 else ------------“电”字第6行X"0180"when sel=1 else ------------“子”字第6行X"0000"when sel=2 else ------------“一”字第6行X"2510"when sel=3 else ------------“班”字第6行X"4240"when sel=4 else ------------“05”字第6行X"1FF0"when sel=5 else ------------“号”字第6行X"0110"when sel=6 else ------------“韦”字第6行X"0810"when sel=7 else ------------“文”字第6行X"0FF0"when sel=8 else ------------“写”字第6行X"0000"; -------否则熄灭第6行所有LEDd6<=X"7FF0"when sel=0 else ------------“电”字第7行X"0104"when sel=1 else ------------“子”字第7行X"0004"when sel=2 else ------------“一”字第7行X"2510"when sel=3 else ------------“班”字第7行X"427C"when sel=4 else ------------“05”字第7行X"0004"when sel=5 else ------------“号”字第7行X"3FF8"when sel=6 else ------------“韦”字第7行X"0820"when sel=7 else ------------“文”字第7行X"0800"when sel=8 else ------------“写”字第7行X"0000"; -------否则熄灭第7行所有LEDd7<=X"4210"when sel=0 else ------------“电”字第8行X"FFFE"when sel=1 else ------------“子”字第8行X"FFFE"when sel=2 else ------------“一”字第8行X"F57C"when sel=3 else ------------“班”字第8行X"4202"when sel=4 else ------------“05”字第8行X"FFFE"when sel=5 else ------------“号”字第8行X"0100"when sel=6 else ------------“韦”字第8行X"0420"when sel=7 else ------------“文”字第8行X"0808"when sel=8 else ------------“写”字第8行X"0000"; -------否则熄灭第8行所有LEDd8<=X"4210"when sel=0 else ------------“电”字第9行X"0100"when sel=1 else ------------“子”字第9行X"0000"when sel=2 else ------------“一”字第9行X"2510"when sel=3 else ------------“班”字第9行X"4202"when sel=4 else ------------“05”字第9行X"0400"when sel=5 else ------------“号”字第9行X"0104"when sel=6 else ------------“韦”字第9行X"0440"when sel=7 else ------------“文”字第9行X"0FFC"when sel=8 else -----------“写”字第9行X"0000"; -------否则熄灭第9行所有LEDd9<=X"7FF0"when sel=0 else ------------“电”字第10行X"0100"when sel=1 else ------------“子”字第10行X"0000"when sel=2 else ------------“一”字第10行X"2910"when sel=3 else ------------“班”字第10行X"4202"when sel=4 else ------------“05”字第10行X"0810"when sel=5 else ------------“号”字第10行X"7FFE"when sel=6 else -----------“韦”字第10行X"0280"when sel=7 else ------------“文”字第10行X"0008"when sel=8 else ------------“写”字第10行X"0000"; -------否则熄灭第10行所有LEDd10<=X"4210"when sel=0 else ------------“电”字第11行X"0100"when sel=1 else ------------“子”字第11行X"0000"when sel=2 else ------------“一”字第11行X"2110"when sel=3 else ------------“班”字第11行X"4202"when sel=4 else ------------“05”字第11行X"1FF8"when sel=5 else ------------“号”字第11行X"0104"when sel=6 else ------------“韦”字第11行X"0100"when sel=7 else ------------“文”字第11行X"0048"when sel=8 else ------------“写”字第11行X"0000"; -------否则熄灭第11行所有LEDd11<=X"0200"when sel=0 else ------------“电”字第12行X"0100"when sel=1 else ------------“子”字第12行X"0000"when sel=2 else ------------“一”字第12行X"2210"when sel=3 else ------------“班”字第12行X"4202"when sel=4 else ------------“05”字第12行X"0010"when sel=5 else ------------“号”字第12行X"0104"when sel=6 else ------------“韦”字第12行X"0280"when sel=7 else ------------“文”字第12行X"7FE8"when sel=8 else ------------“写”字第12行X"0000"; -------否则熄灭第12行所有LEDd12<=X"0204"when sel=0 else ------------“电”字第13行X"0100"when sel=1 else ------------“子”字第13行X"0000"when sel=2 else ------------“一”字第13行X"3A10"when sel=3 else -----------“班”字第13行X"4242"when sel=4 else ------------“05”字第13行X"0010"when sel=5 else ------------“号”字第13行X"0104"when sel=6 else ------------“韦”字第13行X"0460"when sel=7 else ------------“文”字第13行X"0008"when sel=8 else ------------“写”字第13行X"0000"; -------否则熄灭第13行所有LEDd13<=X"0204"when sel=0 else ------------“电”字第14行X"0100"when sel=1 else ------------“子”字第14行X"0000"when sel=2 else ------------“一”字第14行X"E214"when sel=3 else ------------“班”字第14行X"3C3C"when sel=4 else ------------“05”字第14行X"0010"when sel=5 else ------------“号”字第14行X"0128"when sel=6 else ------------“韦”字第14行X"0810"when sel=7 else ------------“文”字第14行X"0008"when sel=8 else ------------“写”字第14行X"0000"; -------否则熄灭第14行所有LEDd14<=X"01FC"when sel=0 else -----------“电”字第15行X"0500"when sel=1 else ------------“子”字第15行X"0000"when sel=2 else ------------“一”字第15行X"44FE"when sel=3 else ------------“班”字第15行X"0000"when sel=4 else ------------“05”字第15行X"00A0"when sel=5 else ------------“号”字第15行X"0110"when sel=6 else ------------“韦”字第15行X"300E"when sel=7 else ------------“文”字第15行X"0050"when sel=8 else ------------“写”字第15行X"0000"; -------否则熄灭第15行所有LEDd15<=X"0000"when sel=0 else ------------“电”字第16行X"0200"when sel=1 else ------------“子”字第16行X"0000"when sel=2 else ------------“一”字第16行X"0800"when sel=3 else ------------“班”字第16行X"0000"when sel=4 else ------------“05”字第16行X"0040"when sel=5 else ------------“号”字第16行X"0100"when sel=6 else ------------“韦”字第16行X"C004"when sel=7 else ------------“文”字第16行X"0020"when sel=8 else ------------“写”字第16行X"0000"; -------否则熄灭第16行所有LEDprocess(clk,set)beginif(set='0')then -------如果功能键没按下,则所有LED全灭L<=X"0000";R_val<="0000";elsif(clk'event and clk='1')then ------每0.004ms扫描一次if( R_val="1111")thenR_val<="0000"; ------当扫描完一遍,再从头扫描elseR_val<=R_val+'1'; ------扫完一行,再扫下一行end if;if(cnt=250000)then ------1s的时间到时,计数器清零cnt<=0;if(sel=8)then ------当显示完9个字,再从第一个字开始显示sel<=0;elsesel<=sel+1; ------显示完一个字,再显示下一个字end if;elsecnt<=cnt+1; ------还没到达1s时,继续计数end if;case R_val iswhen "0000"=>L<=d0; ------当扫描第1列时,送字模的第1行像素信息when "0001"=>L<=d1; ------当扫描第2列时,送字模的第2行像素信息when "0010"=>L<=d2; ------当扫描第3列时,送字模的第3行像素信息when "0011"=>L<=d3; ------当扫描第4列时,送字模的第4行像素信息when "0100"=>L<=d4; ------当扫描第5列时,送字模的第5行像素信息when "0101"=>L<=d5; ------当扫描第6列时,送字模的第6行像素信息when "0110"=>L<=d6; ------当扫描第7列时,送字模的第7行像素信息when "0111"=>L<=d7; ------当扫描第8列时,送字模的第8行像素信息when "1000"=>L<=d8; ------当扫描第9列时,送字模的第9行像素信息when "1001"=>L<=d9; -----当扫描第10列时,送字模的第10行像素信息when "1010"=>L<=d10; ----当扫描第11列时,送字模的第11行像素信息when "1011"=>L<=d11; ----当扫描第12列时,送字模的第12行像素信息when "1100"=>L<=d12; ----当扫描第13列时,送字模的第13行像素信息when "1101"=>L<=d13; ----当扫描第14列时,送字模的第14行像素信息when "1110"=>L<=d14; ----当扫描第15列时,送字模的第15行像素信息when "1111"=>L<=d15; ----当扫描第16列时,送字模的第16行像素信息when others=>null;end case;R<=R_val; end if;end process; end display;。

EDA技术综合设计课程设计-基于VHDL的16×16汉字 点阵动态显示系统的设计

《EDA技术综合设计》课程设计报告报告题目:基于VHDL的16×16汉字点阵动态显示系统的设计作者所在系部:电子工程系作者所在专业:电子信息工程摘要随着电子技术的不断革新,以二极管为基础的LED点阵随之获得了广泛的应用。

在日常生活中,点阵随处可见。

通过多种控制手段,点阵还可以实现各种文字和图案的动态显示。

而在不同的应用场合,点阵的设计要求是不同的。

传统的思路一般是应用单片机实现点阵控制,但这种方法会受到一定的硬件资源限制。

随着电子设计自动化技术的进展,基于可编程逻辑器件进行系统芯片集成的点阵控制不失为一种新的设计思路。

本设计以电子设计自动化(EDA)技术为核心,运用硬件描述语言(VHDL),在MAX+plus Ⅱ环境下进行编程并下载到可编程逻辑器件中实现LED点阵的控制电路。

主要程序除了常用的译码器、计数器之外,还包括了自定义功能的控制模块。

通过编程、调试、仿真、下载完成了汉字的动态显示。

彰显了EDA技术在当今电子领域中的重要地位。

关键词:EDA、可编程逻辑器件、计数器、点阵、动态目录一、概述 (5)二、方案设计与论证 (5)1、点亮点阵中一个点的原理 (5)2、点亮一个字的原理 (5)3、动态显示不同汉字的原理 (5)三、底层文件与程序设计 (6)1.十六进制计数器 (6)2.八进制计数器 (7)3.字显示控制模块 (8)四、系统调试与仿真 (12)1、开发环境介绍 (12)2、新建项目 (12)3、输入程序 (12)4、编译 (13)5、时序仿真 (13)6、设计顶层文件 (14)7、选择器件 (14)8、设置管脚 (14)9、下载 (14)五、硬件调试 (15)六、心得体会 (15)七、参考文献 (15)八、指导教师及评语 (16)课程设计任务书课题名称基于VHDL的16×16点阵汉字动态显示系统的设计完成时间指导教师职称学生姓名班级总体设计要求和技术要点1.在时钟信号的控制下,使点阵动态点亮,点亮方式自行设计,其中位选信号为16-4编码器编码输出。

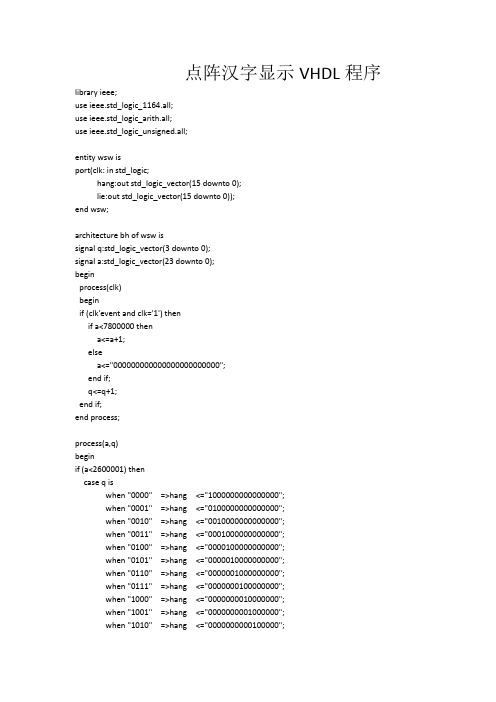

点阵汉字显示VHDL程序

点阵汉字显示VHDL程序libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;entitywsw isport(clk: in std_logic;hang:outstd_logic_vector(15 downto 0);lie:outstd_logic_vector(15 downto 0));endwsw;architecturebh of wsw issignal q:std_logic_vector(3 downto 0);signal a:std_logic_vector(23 downto 0);beginprocess(clk)beginif (clk'event and clk='1') thenif a<7800000 thena<=a+1;elsea<="000000000000000000000000";end if;q<=q+1;end if;end process;process(a,q)beginif (a<2600001) thencase q iswhen "0000" =>hang <="1000000000000000"; when "0001" =>hang <="0100000000000000"; when "0010" =>hang <="0010000000000000"; when "0011" =>hang <="0001000000000000"; when "0100" =>hang <="0000100000000000"; when "0101" =>hang <="0000010000000000"; when "0110" =>hang <="0000001000000000"; when "0111" =>hang <="0000000100000000"; when "1000" =>hang <="0000000010000000"; when "1001" =>hang <="0000000001000000"; when "1010" =>hang <="0000000000100000";when "1011" =>hang <="0000000000010000"; when "1100" =>hang <="0000000000001000"; when "1101" =>hang <="0000000000000100"; when "1110" =>hang <="0000000000000100"; when "1111" =>hang <="0000000000000001"; end case;case q iswhen "0000" =>lie <="1111111111111111"; when "0001" =>lie <="1000000000000011"; when "0010" =>lie <="1111111011111111"; when "0011" =>lie <="1111111011111111"; when "0100" =>lie <="1111111011111111"; when "0101" =>lie <="1111111011111111"; when "0110" =>lie <="1111111011111111"; when "0111" =>lie <="1100000000000011"; when "1000" =>lie <="1111111011111111"; when "1001" =>lie <="1111111011111111"; when "1010" =>lie <="1111111011111111"; when "1011" =>lie <="1111111011111111"; when "1100" =>lie <="1111111011111111"; when "1101" =>lie <="0000000000000000"; when "1110" =>lie <="1111111111111111"; when "1111" =>lie <="1111111111111111";end case;elsif (a<5200000) thencase q iswhen "0000" =>hang<="1000000000000000"; when "0001" =>hang<="0100000000000000"; when "0010" =>hang<="0010000000000000"; when "0011" =>hang<="0001000000000000"; when "0100" =>hang<="0000100000000000"; when "0101" =>hang<="0000010000000000"; when "0110" =>hang<="0000001000000000"; when "0111" =>hang<="0000000100000000"; when "1000" =>hang<="0000000010000000"; when "1001" =>hang<="0000000001000000"; when "1010" =>hang<="0000000000100000"; when "1011" =>hang<="0000000000010000"; when "1100" =>hang<="0000000000001000"; when "1101" =>hang<="0000000000000100"; when "1110" =>hang<="0000000000000100"; when "1111" =>hang<="0000000000000001";end case;case q iswhen "0000" =>lie<="1111111111111111"; when "0001" =>lie<="1000000100000001"; when "0010" =>lie<="1111110111111101"; when "0011" =>lie<="1111110111111101"; when "0100" =>lie<="1011110110111101"; when "0101" =>lie<="1101101111011011"; when "0110" =>lie<="1110101111101011"; when "0111" =>lie<="1111011111110111"; when "1000" =>lie<="1111001111110011"; when "1001" =>lie<="1110110111101101"; when "1010" =>lie<="1110111011011110"; when "1011" =>lie<="1101111110111111"; when "1100" =>lie<="1011111101111111"; when "1101" =>lie<="0111111011111111"; when "1110" =>lie<="1111111111111111"; when "1111" =>lie<="1111111111111111";end case;elsecase q iswhen "0000" =>hang <="1000000000000000"; when "0001" =>hang <="0100000000000000"; when "0010" =>hang <="0010000000000000"; when "0011" =>hang <="0001000000000000"; when "0100" =>hang <="0000100000000000"; when "0101" =>hang <="0000010000000000"; when "0110" =>hang <="0000001000000000"; when "0111" =>hang <="0000000100000000"; when "1000" =>hang <="0000000010000000"; when "1001" =>hang <="0000000001000000"; when "1010" =>hang <="0000000000100000"; when "1011" =>hang <="0000000000010000"; when "1100" =>hang <="0000000000001000"; when "1101" =>hang <="0000000000000100"; when "1110" =>hang <="0000000000000100"; when "1111" =>hang <="0000000000000001"; end case;case q iswhen "0000" =>lie <="1111011110111111";when "0001" =>lie <="1111011110111111"; when "0010" =>lie <="1110011110111111"; when "0011" =>lie <="1110100000000011"; when "0100" =>lie <="1110111110111111"; when "0101" =>lie <="1100110000000011"; when "0110" =>lie <="1100111110111111"; when "0111" =>lie <="1010111110111111"; when "1000" =>lie <="0110100000000011"; when "1001" =>lie <="1110111110111011"; when "1010" =>lie <="1110111110111011"; when "1011" =>lie <="1110111110111011"; when "1100" =>lie <="1110111110101011"; when "1101" =>lie <="1110111110110011"; when "1110" =>lie <="1110111110111111"; when "1111" =>lie <="1110111110111111"; end case;end if;end process;endbh;。

VHDL8x8点阵的显示

8*8点阵的显示一、实验目的通过用VHDL语言设计8*8点阵的显示,掌握时序电路的设计,熟悉汉字字符显示的原理。

二、实验原理利用多个数字LED显示器可以显示多位数字.三、实验内容用VHDL语言设计8*8点阵的显示,并进行编译、波形仿真及器件编程.仿真图如下,代码见附录图表 1 8*8点阵的显示功能仿真图附录代码一、library ieee;use ieee.std_logic_1164。

all;use ieee.std_logic_arith。

all;entity dianzhen8 isport (clk:in std_logic;reset:in std_logic;hang:out std_logic_vector(7 downto 0);lie:out std_logic_vector(7 downto 0));end dianzhen8;architecture zhang of dianzhen8 issignal clk8:std_logic;beginprocess(clk,reset)variable cnt:integer range 0 to 3;variable lie8:std_logic_vector (7 downto 0);beginif reset=’1’thenlie8:=”10000000”;elsif clk'event and clk='1’thenif cnt=3 thenclk8〈=not clk8;cnt:=0;elsecnt:=cnt+1;end if;lie8:=lie8(0)&lie8(7 downto 1);end if;lie〈=lie8;end process;process(clk8,reset)variable hang8:std_logic_vector(7 downto 0);beginif reset=’1’thenhang8:=”11111110";elsif clk8’event and clk8='1'thenhang8:=hang8(0)&hang8(7 downto 1);end if;hang<=hang8;end process;end zhang;代码二、--汉字滚动—-**************库定义、包定义********************library IEEE;use IEEE。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电路课程设计报告课程:基于FPGA的点阵显示控制器的设计学院:电气信息工程学院专业:测控技术与仪器班级:姓名:学号:合作者姓名:日期:一、引言随着我国经济的高速发展,对公共场合发布信息的需求日益增长,利用LED 点阵滚动显示汉字的出现正好适应了这一市场需求,已经成为信息传播的一种重要手段。

采用传统方法设计的汉字滚动显示器,通常需要使用单片机、存储器和制约逻辑电路来进行PCB板级的系统集成。

尽管这种方案有单片机软件的支持较为灵活,但是由于受硬件资源的限制,未来对设计的变更和升级,总是难以避免要付出较多研发经费和较长投放市场周期的代价。

随着电子设计自动化(EDA)技术的进展,基于可编程FPGA器件进行系统芯片集成的新设计方法,也正在快速地到代基于PCB板的传统设计方式。

因此,基于FPGA和VHDL语言实现在8*8点阵上的汉字静态或一屏显示问题。

二、课题要求(1)技术要求1根据电路特点,用层次设计概念。

将此设计任务分成若干模块,规定每一模块的功能和各模块之间的借口,透视加深层次化设计概念;2软件的原件管理深层含义,以及模块元件之间的连接概念,对于不同目录下的同一设计,如何熔合;3适配划分前后的仿真内容有何不同概念,仿真信号对象有何不同,有更深一步了解。

熟悉了FPGA设计的调试过程中手段的多样化;4按适配划分后的管脚定位,同相关功能块硬件电路接口连线;(2)功能要求1在8*8点阵上显示汉字2可以静态显示或一屏显示3利用拨码开关来实现静态显示与一屏显示切换(3)本人的工作三、设计方案(1)工作原理8*8点阵原理:按照要求可知,点阵模块,共由8*8=64个发光二极管组成,如何在该点阵模块上显示汉字是本实验的关键。

先将要显示的每幅图像画在8*8共64个小方格的矩形框中,再在有笔划下落处的小方格里填上“1”,五笔划处填上“0”,这样就形成了与这个汉字所对应的二进制数据在该矩形矿上的分布以“正”为例,点阵分布为:1000000010000001111100011000000111111111100010011000100110000000(2)原理框图四、单元电路设计,仿真结果与分析(1)静态显示“正”library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_Unsigned.all;use ieee.std_logic_ARITH.all;ENTITY peng isport(clk,en:in std_logic;lie:out std_logic_vector(7 downto 0); --列com:out std_logic_vector(7 downto 0));--行End peng;Architecture a of peng issignal st1:std_logic_vector(7 downto 0);signal osc:std_logic;signal osd:std_logic;signal d_ff:std_logic_vector(27 downto 0);signal data:std_logic_vector(7 downto 0);signal d0,d1,d2,d3,d4,d5,d6,d7:std_logic_vector(7 downto 0);signal lie0,lie1,lie2,lie3,lie4,lie5,lie6,lie7:std_logic_vector(7 downto 0);Begincom<=data;lie<=st1;d0<="10000000";d1<="10000001";d2<="11110001";d3<="10000001";d4<="11111111";d5<="10001001";d6<="10001001";d7<="10000000";--字库正First:processbeginwait until clk='1';if(d_ff(27 downto 0)>=2e8)thend_ff(27 downto 0)<="0000000000000000000000000000";elsed_ff(27 downto 0)<=d_ff+1;end if;osc<=not d_ff(10);end process first;second:process(osc)beginif(osc='1' and osc'event and en='0')thenif st1(7 downto 0)="00000000"or st1(7 downto 0)="01111111"then st1(7 downto 0)<="11111110";data<=d0;elsif st1(7 downto 0)="11111110"thenst1(7 downto 0)<="11111101";data<=d1;elsif st1(7 downto 0)="11111101"thenst1(7 downto 0)<="11111011";data<=d2;elsif st1(7 downto 0)="11111011"thenst1(7 downto 0)<="11110111";data<=d3;elsif st1(7 downto 0)="11110111"thenst1(7 downto 0)<="11101111";data<=d4;elsif st1(7 downto 0)="11101111"thenst1(7 downto 0)<="11011111";data<=d5;elsif st1(7 downto 0)="11011111"thenst1(7 downto 0)<="10111111";data<=d6;elsif st1(7 downto 0)="10111111"thenst1(7 downto 0)<="01111111";data<=d7;end if;end if;end process second;end a;(2)一屏显示“上下五千年”Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity weng isPort(Clk,en:in std_logic;lie:out std_logic_vector(7 downto 0);--列Com:out std_logic_vector(7 downto 0));--行End weng;Architecture a of weng issignal st1:std_logic_vector(7 downto 0);signal osc:std_logic;signal osd:std_logic;signal d_ff:std_logic_vector(27 downto 0);signal data:std_logic_vector(7 downto 0);signal d0,d1,d2,d3,d4,d5,d6,d7:std_logic_vector(7 downto 0);signal lie0,lie1,lie2,lie3,lie4,lie5,lie6,lie7:std_logic_vector(6 downto 0);begincom<=data;lie<=st1;D0<="10000000"when lie0(6 downto 0)="0000000"else"00000001"when lie0(6 downto 0)="0000001"else"10000000"when lie0(6 downto 0)="0000010"else"00010000"when lie0(6 downto 0)="0000011"else"00100100"when lie0(6 downto 0)="0000100"else"00000000";D1<="10000000"when lie0(6 downto 0)="0000000"else"00000001"when lie0(6 downto 0)="0000001"else"10001001"when lie0(6 downto 0)="0000010"else"00010100"when lie0(6 downto 0)="0000011"else"00111011"when lie0(6 downto 0)="0000100"else"00000000";D2<="10000000"when lie0(6 downto 0)="0000000"else"00000001"when lie0(6 downto 0)="0000001"else"10001001"when lie0(6 downto 0)="0000010"else"00010100"when lie0(6 downto 0)="0000011"else"00101010"when lie0(6 downto 0)="0000100"else"00000000";D3<="11111111"when lie0(6 downto 0)="0000000"else "11111111"when lie0(6 downto 0)="0000001"else "11111111"when lie0(6 downto 0)="0000010"else "11111100"when lie0(6 downto 0)="0000011"else "00101010"when lie0(6 downto 0)="0000100"else "00000000";D4<="10010000"when lie0(6 downto 0)="0000000"else "00001001"when lie0(6 downto 0)="0000001"else "10001001"when lie0(6 downto 0)="0000010"else "00010010"when lie0(6 downto 0)="0000011"else "11111110"when lie0(6 downto 0)="0000100"else "00000000";D5<="10010000"when lie0(6 downto 0)="0000000"else "00010001"when lie0(6 downto 0)="0000001"else "10001001"when lie0(6 downto 0)="0000010"else "00010001"when lie0(6 downto 0)="0000011"else "00101010"when lie0(6 downto 0)="0000100"else "00000000";D6<="10010000"when lie0(6 downto 0)="0000000"else "00100001"when lie0(6 downto 0)="0000001"else "11111000"when lie0(6 downto 0)="0000010"else "00010000"when lie0(6 downto 0)="0000011"else "00101010"when lie0(6 downto 0)="0000100"else "00000000";D7<="10000000"when lie0(6 downto 0)="0000000"else "00000001"when lie0(6 downto 0)="0000001"else "10000000"when lie0(6 downto 0)="0000010"else "00010000"when lie0(6 downto 0)="0000011"else "00100000"when lie0(6 downto 0)="0000100"else "00000000";first:processbeginwait until clk='1';if(d_ff(27 downto 0)>=2e8)thend_ff(27 downto 0)<="0000000000000000000000000000"; elsed_ff(27 downto 0)<=d_ff+1;end if;osc<=not d_ff(10);osd<=not d_ff(26);end process first;second:process(osc)beginif(osc='1' and osc'event and en='0')thenif st1(7 downto 0)="00000000"or st1(7 downto 0)="01111111"then st1(7 downto 0)<="11111110";data<=d0;elsif st1(7 downto 0)="11111110"thenst1(7 downto 0)<="11111101";data<=d1;elsif st1(7 downto 0)="11111101"thenst1(7 downto 0)<="11111011";data<=d2;elsif st1(7 downto 0)="11111011"thenst1(7 downto 0)<="11110111";data<=d3;elsif st1(7 downto 0)="11110111"thenst1(7 downto 0)<="11101111";data<=d4;elsif st1(7 downto 0)="11101111"thenst1(7 downto 0)<="11011111";data<=d5;elsif st1(7 downto 0)="11011111"thenst1(7 downto 0)<="10111111";data<=d6;elsif st1(7 downto 0)="10111111"thenst1(7 downto 0)<="01111111";data<=d7;end if;end if;end process second;third:process(osd)beginif(osd='1' and osd'event and en='0')thenif lie0(6 downto 0)="0000100"thenlie0(6 downto 0)<="0000000";else lie0(6 downto 0)<=lie0+1;end if;end if;end process third;end a;五.顶层文件电路设计,仿真结果与分析顶层文件library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_Unsigned.all;use ieee.std_logic_ARITH.all;entity zong isport( a:in std_logic_vector(1 downto 0);clk:in std_logic;hang:out std_logic_vector(7 downto 0);lie:out std_logic_vector(7 downto 0));end entity zong;architecture one of zong iscomponent peng isport(clk,en:in std_logic;lie:out std_logic_vector(7 downto 0); --列com:out std_logic_vector(7 downto 0));end component;component weng isPort(Clk,en:in std_logic;lie:out std_logic_vector(7 downto 0);--列Com:out std_logic_vector(7 downto 0));--行end component;signal h1,h2:std_logic_vector(7 downto 0);signal l1,l2:std_logic_vector(7 downto 0);beginu1:peng port map(clk=>clk,en=>a(1),com=>h1,lie=>l1); u2:weng port map(clk=>clk,en=>a(0),com=>h2,lie=>l2); hang<=h1 or h2;lie<=l1 or l2;end architecture one;六、调试结果创建工程在Quartus II 中新建一个VHDL File文件,将vhdl代码输入这个文件,并保存到工作目录,名为zong.vhd。