Quartus+ModelSim-Altera 联合仿真(Verilog版)

QuartusII9.0与Modelsim-Altera6.4a无缝连接

end

assign fm = (cnt <= 6'd24) ? 1'b1 : 1'b0;

endmodule

2、编写TestBench测试平台,选择QuartusII9.0菜单栏Processing—>start—>start TsetBench Template Writer,QuartusII9.0会自动生成TestBench模板。

clk,rst_n,

fm

);

input clk;

input rst_n;

output fm;

reg[5:0] cnt;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) cnt <= 6'd0;

else if(cnt < 6'd49) cnt <= cnt + 1'b1;

// port map - connection between master ports and signals/registers

.clk(clk),

.fm(fm),

.rst_n(rst_n)

);

initial//时钟信号产生

begin

clk = 0;

forever

#20 clk = ~clk;

3、然后打开TestBench模板编写测试代码,代码如下:

`timescale 1ns/1ps

module fp_verilog_vlg_tst();

reg clk;

reg rst_n;

// wires

wire fm;

在quartusII中用modelsim-altera仿真

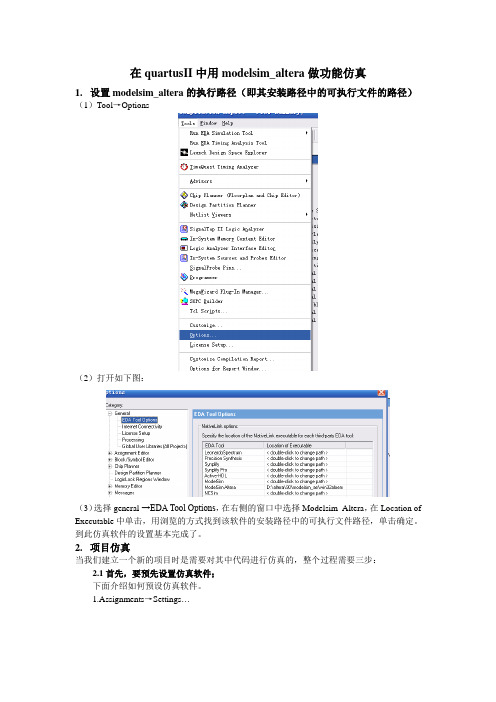

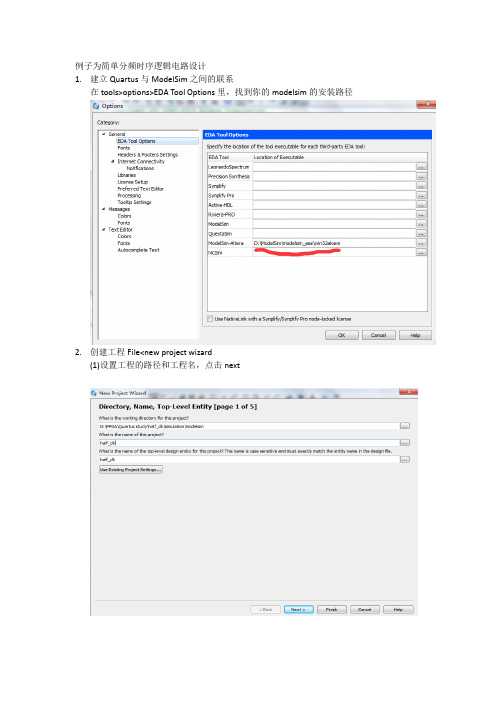

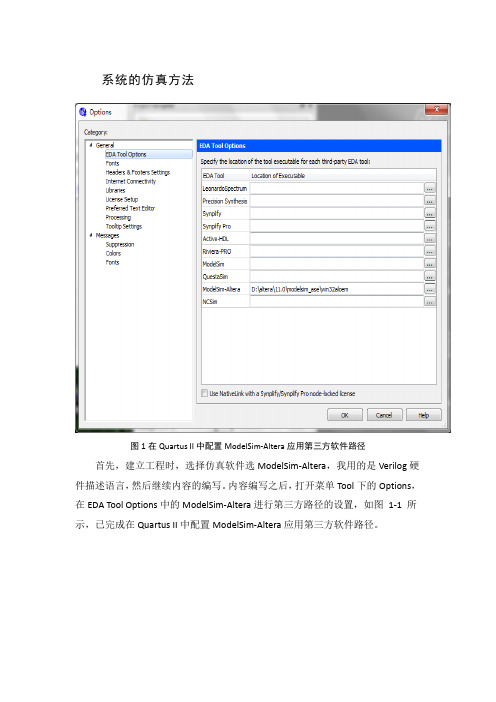

在quartusII中用modelsim_altera做功能仿真1.设置modelsim_altera的执行路径(即其安装路径中的可执行文件的路径)(1)Tool→Options(2)打开如下图:(3)选择general →EDA Tool Options,在右侧的窗口中选择Modelsim_Altera,在Location of Executable中单击,用浏览的方式找到该软件的安装路径中的可执行文件路径,单击确定。

到此仿真软件的设置基本完成了。

2.项目仿真当我们建立一个新的项目时是需要对其中代码进行仿真的,整个过程需要三步:2.1首先,要预先设置仿真软件;下面介绍如何预设仿真软件。

1.Assignments→Settings…2.打开如下界面3选择“Simulation”,右侧设置按上图设置。

2.2其次,仿真之前需要编写测试平台,测试平台有两种的方法:●直接建立XX.v文件●在quartusII中自动生成测试平台模板文件,文件为XX.vt文件下面介绍如何自动生成测试平台模板文件。

1.Processing→Start→Start Test Bench Template Writer注意:要生成testbench模板的前提条件是为项目选择预用的仿真软件,然后模块必须编译成功。

Testbench模板生成后的默认路径为:项目目录\simulation\modelsim\项目名.vt(因为刚才在预设置仿真软件时的“Output Directory”选择的是默认的值simulation\modelsim)。

2.对于自动生成的测试平台模版需要打开修改测试激励信号,这里不做介绍,很简单的。

2.3改写完后要在项目里添加测试平台文件到项目里。

1.Assignments→Settings…2.在打开界面做如下操作:(1)选择“Compile test bench”,然后单击“Test Benches…”(2)打开下面的窗口(3)单击“New”打开下面的窗口,且按图中填写相关信息这个窗口是用来输入testbench的资料和选择testbench的路径的。

Quartus II 13.1 +ModelSim-Altera 10.1d (Quartus

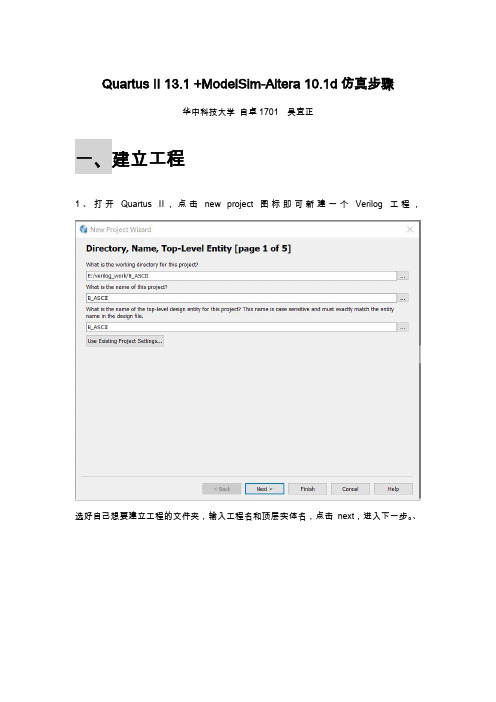

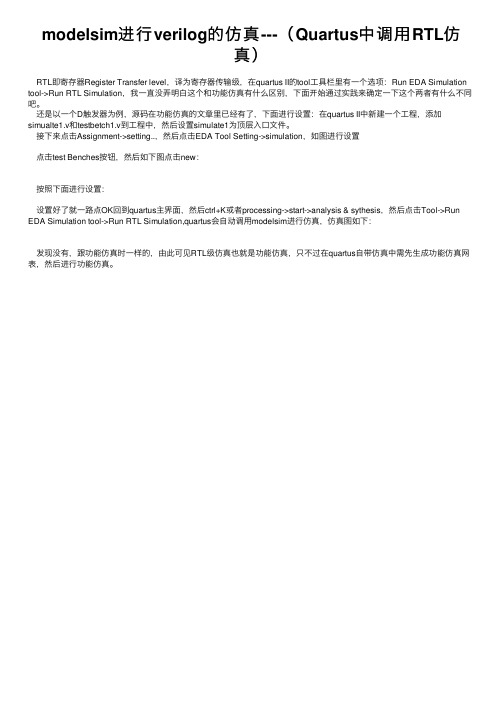

Quartus II 13.1 +ModelSim-Altera 10.1d仿真步骤华中科技大学自卓1701 吴宜正一、建立工程1、打开Quartus Ⅱ,点击new project图标即可新建一个Verilog工程,选好自己想要建立工程的文件夹,输入工程名和顶层实体名,点击next,进入下一步。

、2、可以向工程中加入已经存在的文件,如果没有点击next即可。

3、选取自己想要的器件,点击next即可。

4、在实验中最好在方框中选取Verilog HDL,以便之后编写Testbench文件。

点击next按钮。

之后finish即可。

5、添加Verilog文件在file菜单中选择new,之后输入自己的代码保存即可添加到工程中。

二、编译代码以二进制-ASCII码转化器为例输入代码后进行编译,编译可以按照以下步骤进行1、分析与综合。

点击菜单项Processing->start->Start Analysis &Synthesis也可以直接在工具栏找到。

如果编译成功,左下角窗口有如下显示。

2、全编译文件。

点击菜单项Processing->start compilation,或使用CTRL+L执行全编译。

执行后,如果程序没有问题左下角窗口有如下显示:三、电路仿真1、设定仿真工具此版本Quartus不提供仿真功能,需要调用Modelsim进行仿真,而如果要使用Modelsim 进行仿真首先要编写Testbench文件,在Quartus中,首先要设定仿真工具assignments-setting -EDA tool setting -simulation选择你需要的工具。

这里如果你使用的是下载Quartus时自动下载的ModelSim-Altera那么就选择这个,而如果使用的是单独下载的ModelSim那么就要选择ModelSim。

2. 自动产生测试激励文件模板:在菜单项中选择processing - start - Start test bench template writer3、添加testbench这时Quartus已经自动为你生成一个.vt文件,但是没有自动添加到你的工程内,需要自己去工程目录内寻找。

在Modelsim中加入altera的仿真库

虽然这是个老话题了,但总会有刚入门的朋友不知道的。我在这里还是讲讲吧!问什么要这样做?

1、Quartus不支持Testbench

2、调用了megafunction或者lpm库之类的Altera的函数

3、时序仿真要在Modelsim下做仿真,

总会遇到上面这几个问题,因为需要在Modelsim中加入Quartus的仿真库。 Altera公司推荐的具体的做法是: 1、在Modelsim中,File->Change Directory,将工作目录改变到想要存放仿真库的地方,然后点击OK。将来产生的一大堆仿真库要用的文件就存放在这里。 2、Design->Create a New Library,建立一个新的库:Altera,点击OK。 3、Compile ..quartusedasim_lib下面的两个文件,220model.v和altera_mf.v,记得编译的时候上面的library一定是Altera。这样三步以后,就完成了在Modelsim中添加Altera的库!实际中,这样做不方便。我是这样做的。把220model.v和altera_mf.v拷贝到你要编译的文件所在的文件夹里。先编译这两个文件,等于是把Altera的器件加到了work这个library里。然后再在library下编译你要用的文件就可以了。这样方便些。

4 start compilation... ARTUS中调用Modelsim,verilog下,步骤如下,并作一说明。

1 将modelsim启动路径(如:c:modelsimmodeltechwin32;)加入到环境变量path中。

2 在quartus中建立project,并产生所用的testbench

quartus与modelsim联合仿真步骤总结自己

1.首先安装好quartus和modelsim2.复制altera quartus eda sim_lib 中对应芯片的.v文件到modelsim文件夹内3.打开quartus新建工程在第四步eda tool setting 中simulation选项中选择modelsim 语言默认为veillog 后面不打勾4.assignments settings eda stimulation工具选择modelsim 路径选择modelsim安装的路径写到win32这一步点击确定至此准备工作全部完成5.写veillog 程序然后保存编译编译后会在我们的工程目录下生成simulation文件夹,里面又有一个modelsim文件夹。

6.创建或者是编写testbench引导文件简单的可以创建复杂的需要自己编写quartus自己创建不了这是一个端口引导文件目的是建立modelsim和quartus之间的桥梁能够让modelsim创建出我们需要的与quartus中相匹配的端口并且执行相同的功能这些功能执行信息都存放在了testbench引导文件当中7.创建testbench文件过程:Processing->Start->Start Test Bench Template Write这时创建的testbench文件存放在4中所说的modelsim文件夹中以.vt为后缀名以工程名命名8.添加该文件:Assignments->EDA Tool Settings选择Simulation设置仿真环境在NativeLink settings中选择Compile test bench并点击后面的Test Benches 在Test Benches中点击New设置Test Bench属性在Test bench entity栏一定要填写刚刚我们创建的testbench文件的实体名即module top_vlg_tst();中的top_vlg_tst。

VHDLQuartusII调用Modelsim进行仿真

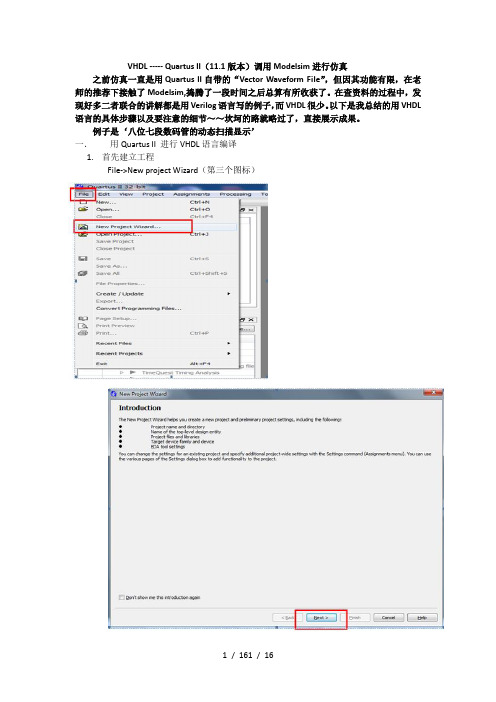

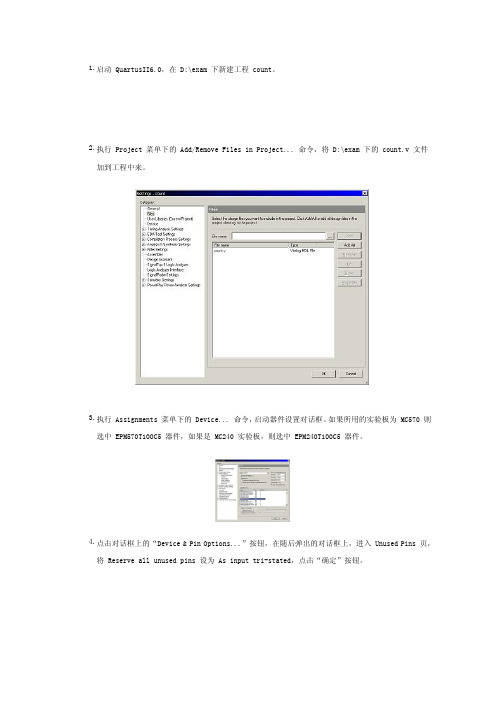

VHDL ----- Quartus II(11.1版本)调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“Vector Waveform File”,但因其功能有限,在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL 语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是‘八位七段数码管的动态扫描显示’一.用Quartus II 进行VHDL语言编译1.首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

3.编译快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置具体的实验器件根据提供的实验板设定Assignment->Device4.引脚分配Assignment->Pin Planner在Location下的方格中填入对应的硬件引脚,也是根据实验板而定6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim1、设置仿真工具为Modelsim-alteraTool->Options->EDA Tool Options,在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用Quartus II生成的模板Processing->start->Start TestBench Template Writer,显示成功后关闭生成报告。

Quartus与modelsim联合仿真

例子为简单分频时序逻辑电路设计

1.建立Quartus与ModelSim之间的联系

在tools>options>EDA Tool Options里,找到你的modelsim的安装路径

2.创建工程File<new project wizard

(1)设置工程的路径和工程名,点击next

(2)第二个界面中会有会有add的选项,对于新手来说暂时用不上,直接点next

(3)选择芯片类型(芯片类型以后深入学习会有区别选择的),如图所示为我的选择

(4)选择联合仿真工具和语言

(5)工程建立完成

3.建立综合模块程序,file<new<verilog HDL File

4.输入程序,点击保存,之后点击start compilation

在processing<start<start test bench template writer,会在你的工程中生成一个half_clk.vt 的文件(simulation文件夹中)。

5.打开half_clk.vt文件,修改test bench程序,点击保存之后编译

6.设置联合仿真,assignment<setting<EDA Tool Setting<simulation,按图所示配置

点击test bench<new,输入按图所示,file name找到之前生成的half_clk.vt文件,点击add 添加

7.进行联合仿真

8.自动启动modelsim进行仿真,得到波形图(tips:通过Ctrl+鼠标的滑轮控制改变波形大

小)

如有不足之处望改进!!!。

modelsim进行verilog的仿真---(Quartus中调用RTL仿真)

modelsim进⾏verilog的仿真---(Quartus中调⽤RTL仿

真)

RTL即寄存器Register Transfer level,译为寄存器传输级,在quartus II的tool⼯具栏⾥有⼀个选项:Run EDA Simulation tool->Run RTL Simulation,我⼀直没弄明⽩这个和功能仿真有什么区别,下⾯开始通过实践来确定⼀下这个两者有什么不同吧。

还是以⼀个D触发器为例,源码在功能仿真的⽂章⾥已经有了,下⾯进⾏设置:在quartus II中新建⼀个⼯程,添加simualte1.v和testbetch1.v到⼯程中,然后设置simulate1为顶层⼊⼝⽂件。

接下来点击Assignment->setting..,然后点击EDA Tool Setting->simulation,如图进⾏设置

点击test Benches按钮,然后如下图点击new:

按照下⾯进⾏设置:

设置好了就⼀路点OK回到quartus主界⾯,然后ctrl+K或者processing->start->analysis & sythesis,然后点击Tool->Run EDA Simulation tool->Run RTL Simulation,quartus会⾃动调⽤modelsim进⾏仿真,仿真图如下:

发现没有,跟功能仿真时⼀样的,由此可见RTL级仿真也就是功能仿真,只不过在quartus⾃带仿真中需先⽣成功能仿真⽹表,然后进⾏功能仿真。

VHDL--QuartusII调用Modelsim进行仿真..doc

VHDL —— Quartus 11(11.1版本调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“ Vector Waveform File但因其功能有限, 在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是八位七段数码管的动态扫描显示’一.用Quartus II进行VHDL语言编译1. 首先建立工程File->New project Wizard(第三个图标IntroductionT»w WUartf hctw OMt* ■ new preyed preAwurr prwfM rdj^rvg the <oi> i —Cf New Pt eel WLurdDirectory, Nd ok?, f op I eve! t fit Hy [ 1 ol 5JWwt • fw B^grtany »«ClDr 簞 2 *W prqgKl?U r'^Ww FMhag 厚叫<™« 电「申mjrdjQ口»**#1 4 ** e* tw >a^4r-*l *rtir r g W p轉W TIM « *» «*"*«** *B«C*r ・W enfliv*M»W ** 華«*h^ru填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish撚后单击yes。

新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法电|脚弧{} ts ts e 代%处处 » n 创1鑼a l =*二二imlibrary ieee;use ieee .std_logic_1164.all;use ieee.std_logic_unsigned.all; □ entity hexx is日 port (clk:xn std_logic;―时神信号输入key:in std_logic_vector (3 downto 0) ;■-四位信号若入 ag : out std^logic^vector (6 downto 0);―7段值号辕出 • sei:out std_logic_vector (2 downto 0)) ;-■数码管送择 end;22 sel<«ql; end if;1C 11 12□ architecture a of hexx is 曰begnn□process (elk)variable ql :std logic vector (2 downto 0):■R 000R ; 1€ n19 2C 21 曰曰卜beginif elk*event and clk«thenif ql-w lll H then ql:"000”; else qls-ql*1!*; end if ; 24电i nend process; 细(} tFS / ® 口创圖2 I r = we 789 10library ieee;use ieee.std IoqIc 1164.all;use ieee.5td_logic_unaignedeall: Bentity hexx is曰 port (clk:in std_logic;一时神(8号辐入key: m std logic tor (3 downto 0) ;一Qfifll 号输入sg:ouc std_logic_vector (6 downs 0); -」段(B 号•出 sellout scd_logxc_vector (2 downto 0));■■数冯苣送择 end; 11 Barchitectuxe a of hexx is 12 Qtegin三曰卜曰□process (cllc)variable ql:std_lo^ic —vector (2 downto 0): beginif elk 'event and clJc**!* then If ql —ill- then ql : —000": else •000- end if ; sel<*ql; end if; end process;-HD —曰 6 7 8 2 2 2 ••X•■“ ■八1 2 3 q注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

ModelSim的前后仿真(Quartus)

利用Quartus5.0实现功能仿真1)打开一个工程文件。

2)打开Settings设置栏,选择Fitting Settings下的Simulator栏。

在右边出现的设置栏中将“Simulation Mode”的下拉菜单选择“Functional”,即可以实现软件下的功能仿真。

(下拉菜单中有“Functional”、“Timing”和“Timing using Fast Timing Model”,分别代表可以在Quartus软件下实现功能仿真,时序仿真和快速时序仿真。

最后一项一般不选,如果在Settings->Timing Requirement->More Settings下“Report Combined Fast/Slow Timing”选项设为“On”,就可以选择最后一项。

编译的报告里也会分别列出最快和最慢的时序报告。

)3)选择“Processing”菜单下的“Generate Functional Simulation Netlist”命令,否则将无法启动仿真。

4)新建一个波形仿真文件,文件后缀名为.vwf。

选择File菜单下的New->Other Files->VectorWaveform File。

如下图所示,左边空白栏处是节点名的列表区,右边空白栏处是仿真波形的显示区。

波形编辑窗口默认时间为1us,如果想改变仿真时间,可以选择Edit菜单下End Time,在弹出的对话框中选择需要的时间。

将新建的波形仿真文件保存下来。

5)将需要仿真的信号加入波形编辑窗口。

在列表区任一位置双击或者点击右键选择“InsertNode or Bus…”,弹出的对话框点击“Node Finder”按钮。

在“Node Finder”界面中点击“List”按钮,有关信号的列表会出现在界面的左边,双击需要观察的信号加入至界面右边。

如果工程中用到了很多信号,在左边列表中也会显示很多(Named编辑框默认的是*通配符),可以在Named编辑框中添加需要的信号名称实现模糊查找。

QuartusII+ModelsimAltera仿真

调试

增加仿真时间, 如:VISM 2> run 20ns 仿真其他功能

要素:输入激励、测试基准、输出比较 模拟方式:simulator和emulator

Quartus II与 ModelSim结合仿真

功能仿真:又称前仿真,不考虑时延,检查功 能的正确性。

综合后仿真:把综合生成的标准延时反标注到 综合仿真模型去,可估计门延时带来的影响, 但是只能估计门延时,不能估计线延时。(不 十分准确,不做)

数字设计验证

对一个成功的数字设计项目而言,设计工程 师和范转换为规范实现 的过程。

验证过程:确认是现方案是否满足设计规范 的过程。

验证方法:基于模拟的验证和基于形式化的 验证。

基于模拟的验证

设计被置于一个测试基准下,把输入激 励施加于测试基准,从设计获得输出并 将它与参考输出进行比较。

测试基准自动生成

自动在simulation目录下生成*.vt文件,自己再修改,添加激励。

测试基准设置

Project Navigator下右键选择Settings下的NativeLink Settings

执行功能仿真

功能仿真结果

时序仿真

执行时序仿真

PVT: P---Process V---Voltage T--Temperature

布局布线后生成的仿真延时文件最全不仅包括门延时还包括布线延时所以最为准确能较好的反映芯片的实际工作情况一般来说布局布线必须进行以此确保设计的可靠性和稳定性发现时序违规thankyouwwwhuaweicom功能仿真仿真工具设置

QuartusII+ModelsimAlt era仿真

本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢!

Quartus II接合ModelSim做仿真

1.启动 QuartusII6.0,在 D:\exam 下新建工程 count。

2.执行 Project 菜单下的 Add/Remove Files in Project... 命令,将 D:\exam 下的 count.v 文件加到工程中来。

3.执行 Assignments 菜单下的 Device... 命令,启动器件设置对话框。

如果所用的实验板为 MC570 则选中 EPM570T100C5 器件,如果是 MC240 实验板,则选中 EPM240T100C5 器件。

4.点击对话框上的“Device & Pin Options...”按钮,在随后弹出的对话框上,进入 Unused Pins 页,将 Reserve all unused pins 设为 As input tri-stated,点击“确定”按钮。

5.在左侧的 Category 窗口里,展开 EDA Tool Setings 组,选中 Simulation 项,对话框的左侧将弹出有关于 Simulation 的设置项。

在 Tool name 一栏,选择 ModelSim;Format for output netlist 一栏,选择 Verilog;Time scale 一栏,选择 1ns。

点击“OK”按钮。

6.在 Assignments 菜单下,点击 Pins 命令。

在 Pin Planner 中,按下图所示,分配管脚。

7.在 Project Navigator 窗口中,将页面切换到文件管理页(中间的),选中 Device Design Files 组中的 count.v 文件,点击右键,在弹出菜单中点击 Set as Top-level Entity 命令,将该文件设为顶层设计文件。

在 Processing 菜单下,点击 Start Compilation 命令,待编译完成后,退出 QuartusII6.0。

将 D:\exam\simulation\modelsim 下的 count_v.sdo 文件复制到 D:\exam 下。

Quartus II调用ModelSim仿真方法

系统的仿真方法图1在Quartus II中配置ModelSim-Altera应用第三方软件路径首先,建立工程时,选择仿真软件选ModelSim-Altera,我用的是Verilog硬件描述语言,然后继续内容的编写。

内容编写之后,打开菜单Tool下的Options,在EDA Tool Options中的ModelSim-Altera进行第三方路径的设置,如图1-1 所示,已完成在Quartus II中配置ModelSim-Altera应用第三方软件路径。

如图2 NativeLink settings然后,选择Assignments下的EDA Tool Settings下的Simulation中的NativeLink settings,选择Compile test bench,设置其中的Test Benches,New,然后编辑里头内容,然后具体内容如图 2 所示,然后,Test bench name填入的是设计的顶层文件、Top level module in test bench和Design instance name in test bench是填入仿真的文件的名字,Test bench files填入仿真的文件路径。

最后生成测试文件,选择在Quartus II开发界面菜单栏下Processing下的Start 下面的Start Test Bench Template Writer,提示生成成功。

生成测试仿真文件的大框,里头一些内容还需自己添加。

以下告诉你如何添加内容,在仿真目录下找到为“.vt”的文件,然后打开这个文件,根据需要给以激励和时钟进行编辑。

具体的Test Bench的编写正在附录四中,写完Test Bench之后就可以进行在菜单栏Tools 下的Run EDA Simulation下的EDA RTL Simulation仿真。

Quartus与ModelSim联合仿真流程文档

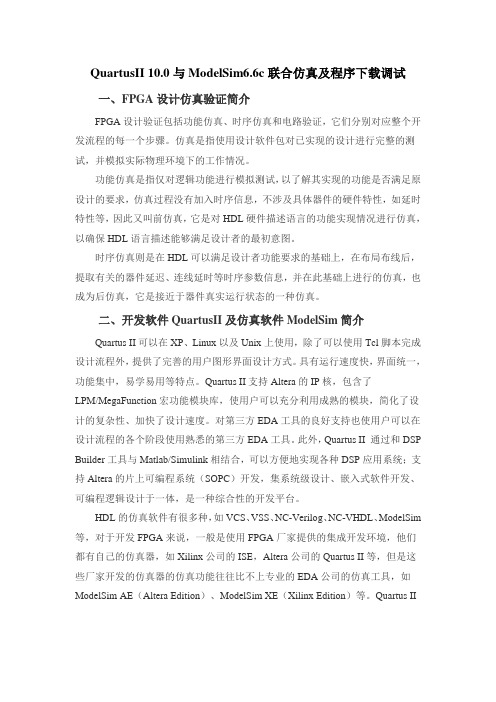

QuartusII 10.0与ModelSim6.6c联合仿真及程序下载调试一、FPGA设计仿真验证简介FPGA设计验证包括功能仿真、时序仿真和电路验证,它们分别对应整个开发流程的每一个步骤。

仿真是指使用设计软件包对已实现的设计进行完整的测试,并模拟实际物理环境下的工作情况。

功能仿真是指仅对逻辑功能进行模拟测试,以了解其实现的功能是否满足原设计的要求,仿真过程没有加入时序信息,不涉及具体器件的硬件特性,如延时特性等,因此又叫前仿真,它是对HDL硬件描述语言的功能实现情况进行仿真,以确保HDL语言描述能够满足设计者的最初意图。

时序仿真则是在HDL可以满足设计者功能要求的基础上,在布局布线后,提取有关的器件延迟、连线延时等时序参数信息,并在此基础上进行的仿真,也成为后仿真,它是接近于器件真实运行状态的一种仿真。

二、开发软件QuartusII及仿真软件ModelSim简介Quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式。

具有运行速度快,界面统一,功能集中,易学易用等特点。

Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。

对第三方EDA工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统(SOPC)开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台。

HDL的仿真软件有很多种,如VCS、VSS、NC-Verilog、NC-VHDL、ModelSim 等,对于开发FPGA来说,一般是使用FPGA厂家提供的集成开发环境,他们都有自己的仿真器,如Xilinx公司的ISE,Altera公司的Quartus II等,但是这些厂家开发的仿真器的仿真功能往往比不上专业的EDA公司的仿真工具,如ModelSim AE(Altera Edition)、ModelSim XE(Xilinx Edition)等。

Quartus II 13.1与自带modelsim_Altera 10.0d仿真软件的联调

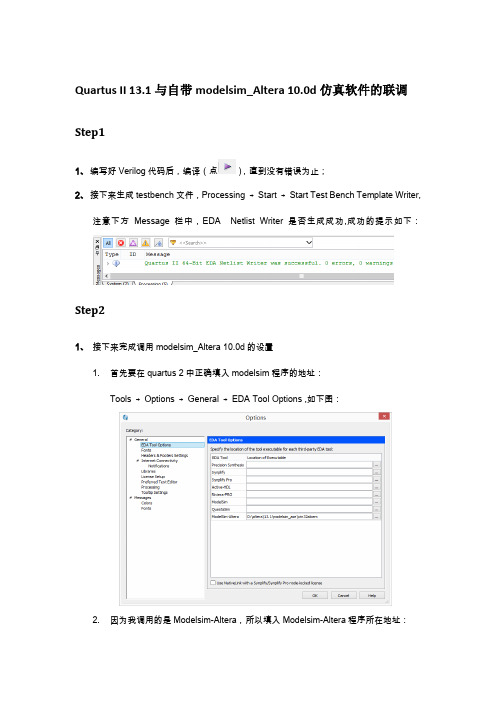

Quartus II 13.1与自带modelsim_Altera 10.0d仿真软件的联调Step11、编写好Verilog代码后,编译(点),直到没有错误为止;2、接下来生成testbench文件,Processing →Start →Start Test Bench Template Writer,注意下方Message栏中,EDA Netlist Writer是否生成成功,成功的提示如下:Step21、接下来完成调用modelsim_Altera 10.0d的设置1.首先要在quartus 2中正确填入modelsim程序的地址:Tools →Options →General →EDA Tool Options ,如下图:2.因为我调用的是Modelsim-Altera,所以填入Modelsim-Altera程序所在地址:D:\altera\13.1\modelsim_ase\win32aloem(注:一般只是盘符不一样,我装在D 盘,如果你装在C盘,那地址就是C:\altera\13.1\modelsim_ase\win32aloem)3.接下来,就是正确载入测试文件了,载入前,先要修改testbench:(测试文件只是模板,要自己加入时钟信号,输入信号,即添加激励,否则无法出现仿真波形)Assignments →Settings 出现如下界面:i.勾选下图的小方格,当在Quartus中编译快完成时,自带调出Modelsim_Altera;ii.如果你的代码是用Verilog写的,则此处要选Verilog HDL;iii.下面这个选项是仿真时间单位:`timescale 仿真时间单位/时间精度(eg: `timescale 100ns/10ns)仿真时间单位和时间精度,就比如常见的刻度尺,仿真时间单位以cm为单位,时间精度以mm为单位,所以仿真时间单位是大于或等于时间精度的。

iv.选择Compile test bench ,点Test Benches…v.出现下图,点New…vi.出现下图:vii.先填写下图,点File name 空格旁的,添加生成的Testbench文件,格式是 .vt ,点Add 完成添加。

使用Quartus-Modelsim联合仿真

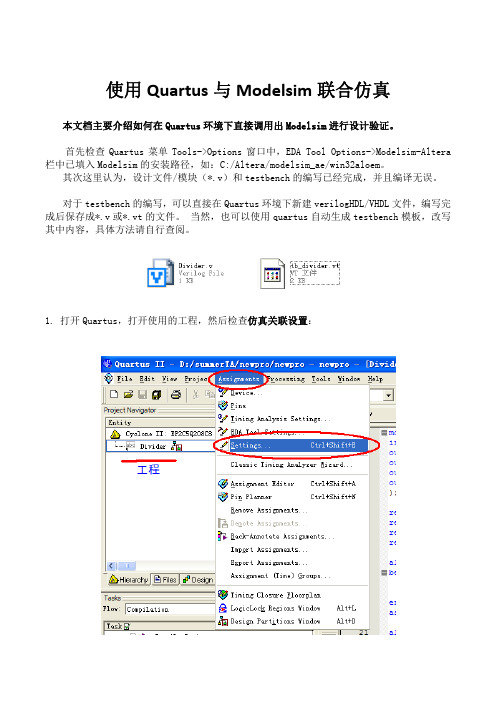

使用Quartus与Modelsim联合仿真 本文档主要介绍如何在Quartus环境下直接调用出Modelsim进行设计验证。

首先检查Quartus菜单Tools->Options窗口中,EDA Tool Options->Modelsim-Altera 栏中已填入Modelsim的安装路径,如:C:/Altera/modelsim_ae/win32aloem。

其次这里认为,设计文件/模块(*.v)和testbench的编写已经完成,并且编译无误。

对于testbench的编写,可以直接在Quartus环境下新建verilogHDL/VHDL文件,编写完成后保存成*.v或*.vt的文件。

当然,也可以使用quartus自动生成testbench模板,改写其中内容,具体方法请自行查阅。

1.打开Quartus,打开使用的工程,然后检查仿真关联设置:

然后你会看到:

2.testbench的设置

设置完成后,全编译。

编译完成后,点击:

自动启动modelsim,你将看到:

你还可以查看Modelsim控制台:

编译完成后,点击:

自动启动modelsim,你将看到:

你还可以查看Modelsim控制台:

仔细观察,时序仿真和功能仿真还是有很大差别的哦~~。

用quartusII再带的modelsim进行后仿真(时序仿真)的操作步骤

⽤quartusII再带的modelsim进⾏后仿真(时序仿真)的操作步

骤

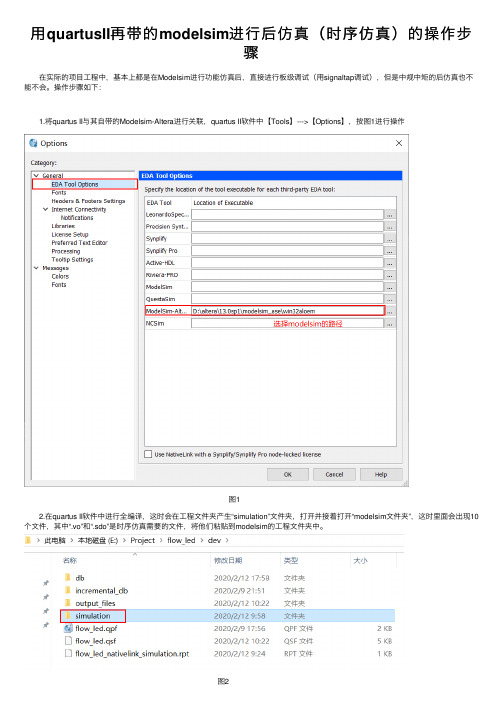

在实际的项⽬⼯程中,基本上都是在Modelsim进⾏功能仿真后,直接进⾏板级调试(⽤signaltap调试),但是中规中矩的后仿真也不能不会。

操作步骤如下:

1.将quartus II与其⾃带的Modelsim-Altera进⾏关联,quartus II软件中【Tools】--->【Options】,按图1进⾏操作

图1

2.在quartus II软件中进⾏全编译,这时会在⼯程⽂件夹产⽣“simulation”⽂件夹,打开并接着打开“modelsim⽂件夹”,这时⾥⾯会出现10个⽂件,其中“.vo”和“.sdo”是时序仿真需要的⽂件,将他们粘贴到modelsim的⼯程⽂件夹中。

图2

图3

3.接下来还需要Altera的器件库

其中Altera的器件库⽂件在:D:\altera\13.0sp1\modelsim_ase\altera\verilog\altera

D:\altera\13.0sp1\modelsim_ase\altera\verilog\cycloneive

图4

4.将testbench⽂件和“.vo”⽂件加到⼯程上,然后编译,然后右键选择【Add to project】-->【Simulation Configuration】,选择【Work】中的"xxx_tb"⽂件,然后选择【Libraries】中加载刚在粘贴的2个Altera器件库,然后在【SDF】中加载刚才粘贴的“xx.sdo”⽂件,然后点【Save】,最后点击“Simulation”即可进⾏时序仿真。

如图5 、6、7所⽰:

图5

图6

图7 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Quartus+ModelSim-Altera联合仿真(Verilog版)

作者:L.xiang (注:默认Next/OK/Finish)

Step1:新建工程New Project Wizard...设置路径+工程名+entity名(project、entity必须同名);

Step2:选择器件:Cyclone II EP2C5F26C8(例如);

Step3:Simulation设置:ModelSim-Altera+Verilog HDL;

Step4:新建文件,选Verilog HDL File;

Step5:输入代码,并保存为led(.v文件);

Step6:调试,修改直到没有Error为止(工程目录下同时自动生成了simulation文件);

Step7:生成Test Bench文件(.vt):Processing->Start->Start Test Bench Template Writer;

Step8:工程目录下C:\altera\text\led1\simulation\modelsim打开led.vt文件,并复制“led_vlg_tst”;

Step9:设置Simulation:Assignments+Settings;

Step10:Simulation->仿真扫描时间Time scale:100ps(或其它值),Comple test bench-> Tset Benchse...;

Step11:点击New...;

Step12:粘贴Test bench name:led_vlg_tst(Step8中已复制),Top level module in test bench:led_vlg_tst(必须和.vt文件里的module名一致);

Step13:添加Test bench files:simulation/modelsim/led.vt,并点击Add;

Step14:点击,即启动ModelSim进入仿真;

Step14:工作区中双击打开i1文件,并将所需要的信号添加到仿真波形图中:Add->To Wave;

Step15:点击,便可看到完整的波形图了。

完成仿真。

——2013.04.02杭州。