计算机组成原理与系统结构课后作业答案(包健_冯建文 章复嘉版)

计算机组成与系统结构课后答案全

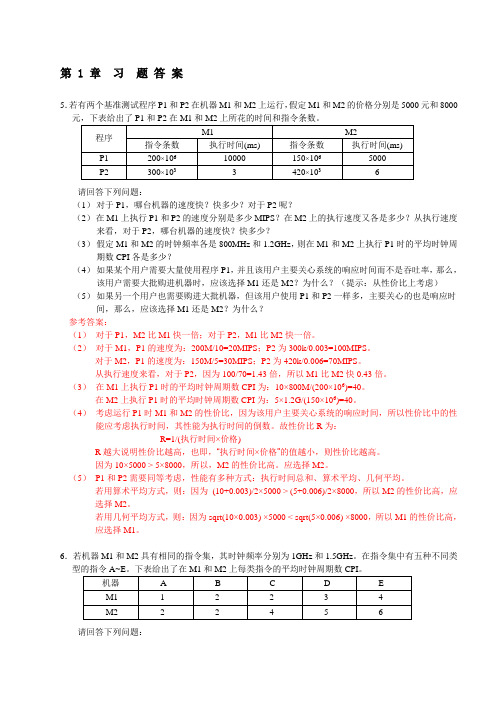

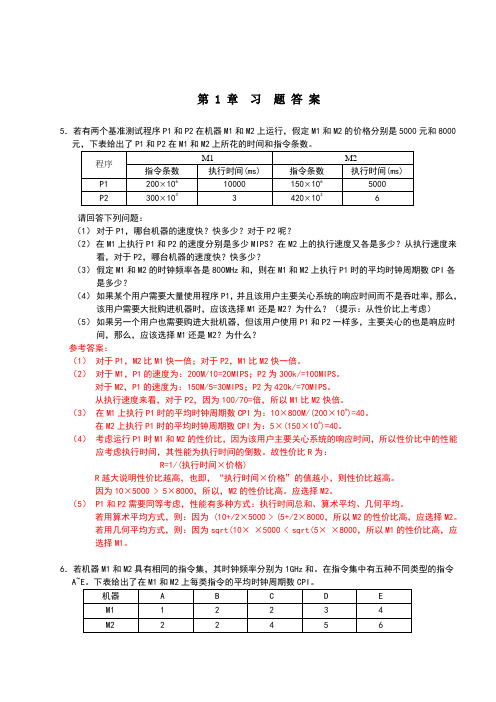

第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

因为10×5000 > 5×8000,所以,M2的性价比高。

计算机组成与系统结构课后答案版全

第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/=70MIPS。

从执行速度来看,对于P2,因为100/70=倍,所以M1比M2快倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

因为10×5000 > 5×8000,所以,M2的性价比高。

应选择M2。

计算机组成原理课后习题-参考答案

习题参考答案

5-2:计算机为什么要设置时序部件? 周期、节拍、脉冲三级时序关系如何 表示?

一条指令运行的各种操作控制信号在时间上有严格 的定时关系, 的定时关系,时序部件用以控制时序以保证指令 的正确执行。 的正确执行。 将指令周期划分为几个不同的阶段, 将指令周期划分为几个不同的阶段,每个阶段称为 一个机器周期。 一个机器周期。 一个机器周期又分为若干个相等的时间段, 一个机器周期又分为若干个相等的时间段,每个时 时间段称为一个时钟周期(节拍)。 时间段称为一个时钟周期(节拍)。 在一个时钟周期(节拍)内可设置几个工作脉冲, 在一个时钟周期(节拍)内可设置几个工作脉冲, 用于寄存器的清除、接收数据等工作。 用于寄存器的清除、接收数据等工作。

9

习题什么特点?

依据控制器中的时序控制部件和微操作控制信号形 成部件的具体组成与运行原理不同,通常把控制 成部件的具体组成与运行原理不同, 器区分为微程序控制器和硬布线控制器两大类。 器区分为微程序控制器和硬布线控制器两大类。 微程序控制方式是用一个ROM做为控制信号产生 微程序控制方式是用一个 做为控制信号产生 的载体, 中存储着一系列的微程序, 的载体,ROM中存储着一系列的微程序,组成微 中存储着一系列的微程序 程序的微指令代码产生相应的操作控制信号, 程序的微指令代码产生相应的操作控制信号,这 是一种存储逻辑型的控制器。方便修改和扩充, 是一种存储逻辑型的控制器。方便修改和扩充, 但指令执行速度较慢。 但指令执行速度较慢。 硬布线控制方式采用组合逻辑电路实现各种控制功 在制造完成后, 能,在制造完成后,其逻辑电路之间的连接关系 就固定下来,不易改动。其运行速度快, 就固定下来,不易改动。其运行速度快,但构成 复杂。 复杂。

13

习题参考答案

计算机组成原理课后习题及答案(完整版)

精选2021版课件

7

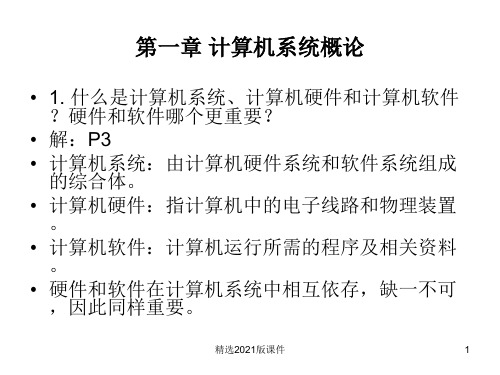

• 3. 什么是摩尔定律?该定律是否永远生效 ?为什么?

• 答:P23,否,P36

精选2021版课件

8

系统总线

第三章

精选2021版课件

9

1. 什么是总线?总线传输有何特点? 为了减轻总线的负载,总线上的部件都应 具备什么特点?

解:总线是多个部件共享的传输部件; 总线传输的特点是:某一时刻只能有 一路信息在总线上传输,即分时使用; 为了减轻总线负载,总线上的部件应 通过三态驱动缓冲电路与总线连通。

解: 总线标准——可理解为系统与模块、 模块与模块之间的互连的标准界面。 总线标准的设置主要解决不同厂家各 类模块化产品的兼容问题; 目前流行的总线标准有:ISA、EISA、 PCI等; 即插即用——指任何扩展卡插入系统 便可工作。EISA、PCI等具有此功能。

精选2021版课件

16

11. 画一个具有双向传输功能的总线逻

12

总线的主设备(主模块)——指一次总

线传输期间,拥有总线控制权的设备(模块); 总线的从设备(从模块)——指一次总

线传输期间,配合主设备完成传输的设备(模 块),它只能被动接受主设备发来的命令;

总线的传输周期——总线完成一次完整 而可靠的传输所需时间;

总线的通信控制——指总线传送过程中 双方的时间配合方式。

精选2021版课件

10

4. 为什么要设置总线判优控制?常见的集 中式总线控制有几种?各有何特点?哪种方式响 应时间最快?哪种方式对电路故障最敏感?

解:总线判优控制解决多个部件同时申请总 线时的使用权分配问题;

常见的集中式总线控制有三种: 链式查询、计数器查询、独立请求;

特点:链式查询方式连线简单,易于扩充,

计算机组成与系统结构课后答案全

关系表达式

运算类型

结果

说明

0 == 0U

–1 < 0

–1 < 0U

47 > –47 – 1

47U > –47 – 1

47 > (int) 48U

参考答案:

(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/=70MIPS。

从执行速度来看,对于P2,因为100/70=倍,所以M1比M2快倍。

(3)[x]补=x = +

(4)[x]补=x =–101101B =–45

7.假定一台32位字长的机器中带符号整数用补码表示,浮点数用IEEE 754标准表示,寄存器R1和R2的内容分别为R1:0000108BH,R2:8080108BH。不同指令对寄存器进行不同的操作,因而,不同指令执行时寄存器内容对应的真值不同。假定执行下列运算指令时,操作数为寄存器R1和R2的内容,则R1和R2中操作数的真值分别为多少?

(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)

(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?

+,–,+,–,+,–,+0,–0

计算机组成与系统结构课后答案全

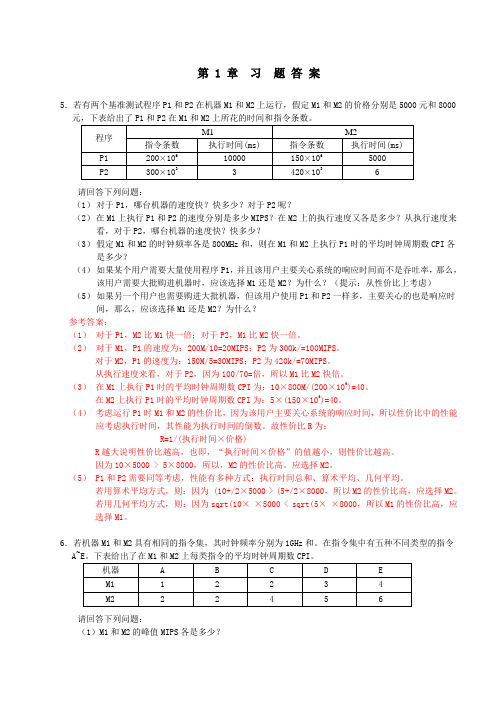

第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000元,下表给出了P1和P2在M1和M2上所花的时间和指令条数。

请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/=70MIPS。

从执行速度来看,对于P2,因为100/70=倍,所以M1比M2快倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

因为10×5000 > 5×8000,所以,M2的性价比高。

计算机组成原理包健版答案解析

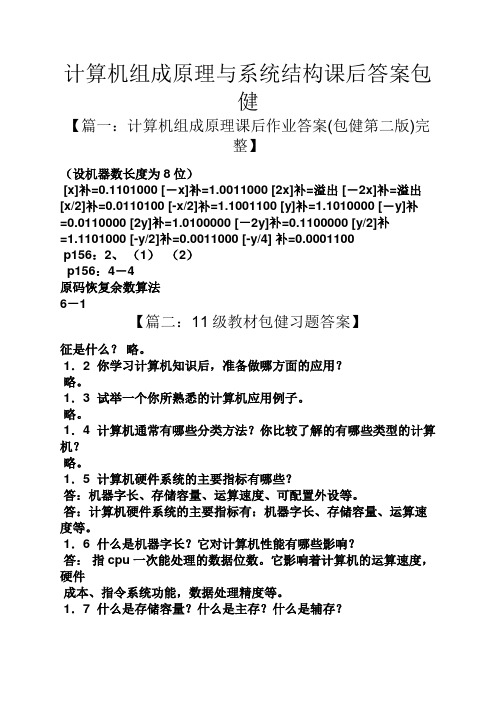

1.1 概述数字计算机的发展经过了哪几个代?各代的基本特征是什么?略。

1.2 你学习计算机知识后,准备做哪方面的应用?略。

1.3 试举一个你所熟悉的计算机应用例子。

略。

1.4 计算机通常有哪些分类方法?你比较了解的有哪些类型的计算机?` 。

1.5 计算机硬件系统的主要指标有哪些?答:机器字长、存储容量、运算速度、可配置外设等。

答:计算机硬件系统的主要指标有:机器字长、存储容量、运算速度等。

1.6 什么是机器字长?它对计算机性能有哪些影响?答:指CPU一次能处理的数据位数。

它影响着计算机的运算速度,硬件成本、指令系统功能,数据处理精度等。

1.7 什么是存储容量?什么是主存?什么是辅存?答:存储容量指的是存储器可以存放数据的数量(如字节数)。

它包括主存容量和辅存容量。

主存指的是CPU能够通过地址线直接访问的存储器。

如内存等。

辅存指的是CPU不能直接访问,必须通过I/O接口和地址变换等方法才能访问的存储器,如硬盘,u盘等。

1.8 根据下列题目的描述,找出最匹配的词或短语,每个词或短语只能使用一次。

(1)为个人使用而设计的计算机,通常有图形显示器、键盘和鼠标。

(2)计算机中的核心部件,它执行程序中的指令。

它具有加法、测试和控制其他部件的功能。

(3)计算机的一个组成部分,运行态的程序和相关数据置于其中。

(4)处理器中根据程序的指令指示运算器、存储器和I/O设备做什么的部件。

(5)嵌入在其他设备中的计算机,运行设计好的应用程序实现相应功能。

(6)在一个芯片中集成几十万到上百万个晶体管的工艺。

(7)管理计算机中的资源以便程序在其中运行的程序。

(8)将高级语言翻译成机器语言的程序。

(9)将指令从助记符号的形式翻译成二进制码的程序。

(10)计算机硬件与其底层软件的特定连接纽带。

供选择的词或短语:1、汇编器2、嵌入式系统3、中央处理器(CPU)4、编译器5、操作系统6、控制器7、机器指令8、台式机或个人计算机9、主存储器 10、VLSI答:(1)8,(2)3,(3)9,(4)6,(5)2,(6)10,(7)5,(8)4,(9)1,(10)7计算机系统有哪些部分组成?硬件由哪些构成?答:计算机系统硬件系统和软件系统组成。

杭电_计算机组成原理_包建_课后作业答案

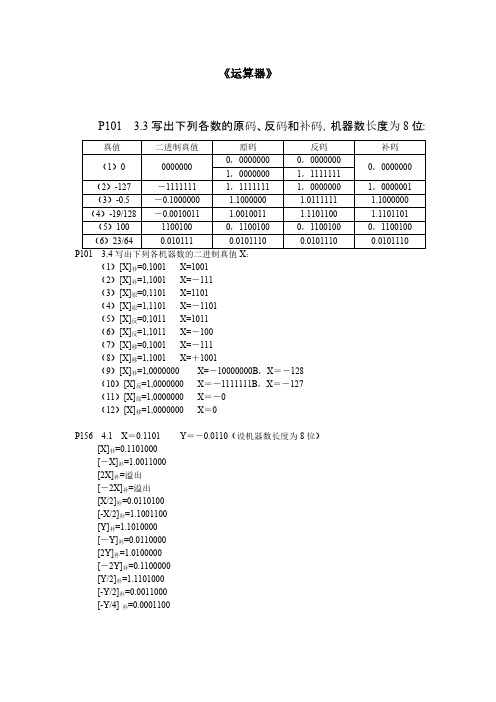

《运算器》P61 3.4写出下列各机器数的二进制真值X:(1)[X]补=0,1001 X=1001(2)[X]补=1,1001 X=-111(3)[X]原=0,1101 X=1101(4)[X]原=1,1101 X=-1101(5)[X]反=0,1011 X=1011(6)[X]反=1,1011 X=-100(7)[X]移=0,1001 X=-111(8)[X]移=1,1001 X=+1001(9)[X]补=1,0000000 X=-10000000B,X=-128(10)[X]反=1,0000000 X=-1111111B,X=-127(11)[X]原=1,0000000 X=-0(12)[X]移=1,0000000 X=0P107 4.1X=0.1101 Y=-0.0110(设机器数长度为8位)[X]补=0.1101000[-X]补=1.0011000[2X]补=溢出[-2X]补=溢出[X/2]补=0.0110100[-X/2]补=1.1001100[Y]补=1.1010000[-Y]补=0.0110000[2Y]补=1.0100000[-2Y]补=0.1100000[Y/2]补=1.1101000[-Y/2]补=0.0011000[-Y/4]补=0.0001100P61:5、(1) X=-25/64=-0.011001B ,Y=2.875=10.111B[X]浮=0,11111 1.11001=7F9H [Y]浮=1,00010 0.10111=897H (2) [Z]浮=9F4H=1,00111 1.10100=-80P61:6、机器数字长16位 (1) 无符号整数:12~016-(2) 原码表示的定点整数:1,111…11~0,111…11即12~)12(1515--- (3) 补码表示的定点整数:1,00…000~0,111…11即12~21515--(4) 补码表示的定点小数:1.00…000~0.111…11即1521~1---(5) 非规格化浮点数:ER M N ⨯=最大数=12772)21(--⨯-最小数=12721-⨯-最大负数=72722--⨯-最小正数=72722--⨯(6) 最大数=12772)21(--⨯-最小数=12721-⨯-最大负数=72712)22(---⨯+-最小正数=72122--⨯P107:2、(1)(2)P108:4-14-2P108:55-1补码BOOTH算法5-2补码BOOTH算法P108:6、6-1原码恢复余数算法6-2原码加减交替算法P108 7-1补码加减交替算法7-2补码加减交替算法P108:8-1(1)X=-1.625=-1.101B Y=5.25=101.01B X+YX-Y:1、对阶同上2、尾数相减:11.1100110+ 11.01011[E X-Y]补= 11.00100103、结果不需规格化4、舍入处理:[E X-Y]补=1.00101[X-Y] = 0,0011 1,00101X=0.2344 = 0.00111 Y= -0.1133=-0.00011X-Y:1、对阶同上2、尾数相减:00.11100+ 00.01100[E X-Y]补= 01.01000 发生正溢尾数右移,阶码加1[E X-Y]补= 0.10100[M x-y] = 1.11113、结果不需规格化4、舍入处理:[E X-Y]补=0.10100[X-Y] = 1,1111 0,10100(1)X=5.25=101.01B Y=-1.625=-1.101B X*Y9-1 X/Y:9-2 X*Y9-2 X/Y《存储体系》P225:2、 (1) 片641641161664=⨯=⨯⨯K K(2) s msμ625.151282=(3) s ns μ64500128=⨯ P225:3、(1) 最大主存容量=bit 16218⨯(2) 共需片6416416416218=⨯=⨯⨯bitK bit芯片;若采用异步刷新,则刷新信号的周期为s msμ625.151282= (3) 每块8字节,则Cache 容量为行925128162==⨯BytebitK ,即c=9,Cache 采用2路组相联映射,则r=1。

(完整版)计算机组成原理课后作业答案(包健第二版)完整

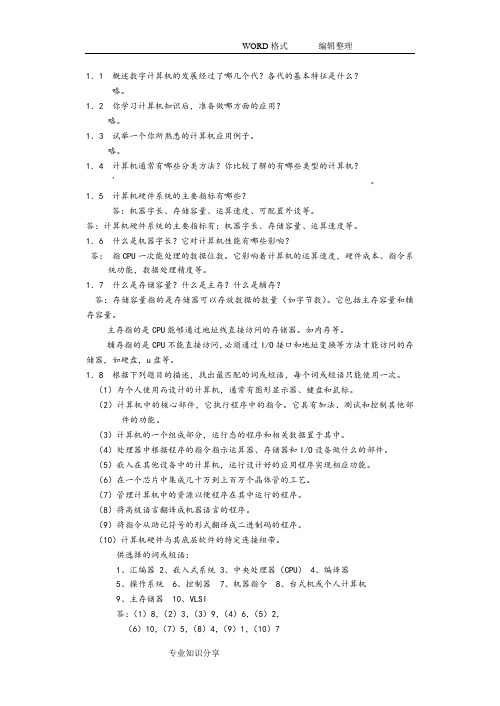

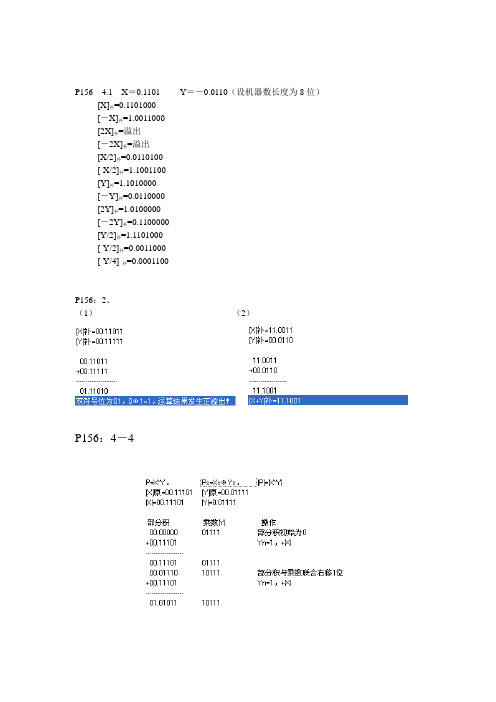

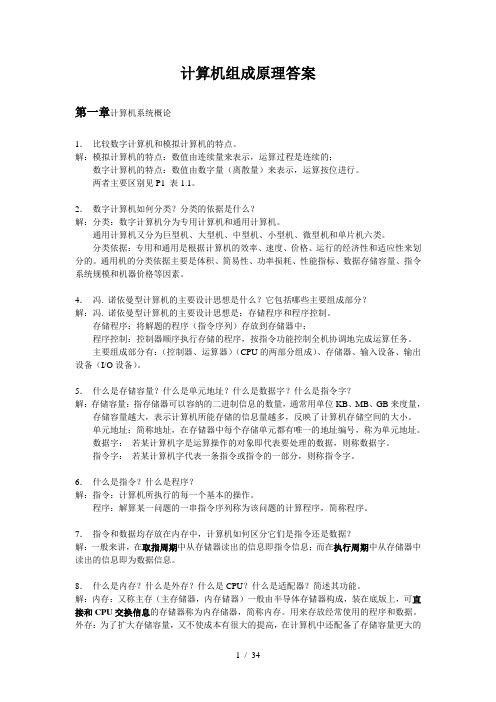

P156 4.1X=0.1101 Y=-0.0110(设机器数长度为8位)[X]补=0.1101000[-X]补=1.0011000[2X]补=溢出[-2X]补=溢出[X/2]补=0.0110100[-X/2]补=1.1001100[Y]补=1.1010000[-Y]补=0.0110000[2Y]补=1.0100000[-2Y]补=0.1100000[Y/2]补=1.1101000[-Y/2]补=0.0011000[-Y/4]补=0.0001100P156:2、(1)(2)P156:4-46-1原码恢复余数算法6-2原码加减交替算法P156:4.8阶码(5位补码)尾数(6位补码)(1)X=-1.625=-1.101B Y=5.25=101.01B X+YX-Y:1、对阶同上2、尾数相减:11.1100110+ 11.01011[E X-Y]补= 11.00100103、结果不需规格化4、舍入处理:[E X-Y]补=1.00101[X-Y] = 0,0011 1,00101P108:9-1阶码(5位移码)尾数(6位补码)(1)X=5.25=101.01B Y=-1.625=-1.101B X*Y9-1 X/Y:9-2 X*Y9-2 X/Y《存储体系》P225:2、 (1) 片641641161664=⨯=⨯⨯K K(2) s msμ625.151282=(3) s ns μ64500128=⨯ P225:3、(1) 最大主存容量=bit 16218⨯(2) 共需片6416416416218=⨯=⨯⨯bitK bit芯片;若采用异步刷新,则刷新信号的周期为s msμ625.151282= (3) 每块8字节,则Cache 容量为行925128162==⨯BytebitK ,即c=9,Cache 采用2路组相联映射,则r=1。

主存容量为块161828162=⨯Bytebit,即m=16。

每块包含4个字,每字包含2个字节。

计算机组成原理课后习题参考答案

计算机组成原理答案第一章计算机系统概论1.比较数字计算机和模拟计算机的特点。

解:模拟计算机的特点:数值由连续量来表示,运算过程是连续的;数字计算机的特点:数值由数字量(离散量)来表示,运算按位进行。

两者主要区别见P1 表1.1。

2.数字计算机如何分类?分类的依据是什么?解:分类:数字计算机分为专用计算机和通用计算机。

通用计算机又分为巨型机、大型机、中型机、小型机、微型机和单片机六类。

分类依据:专用和通用是根据计算机的效率、速度、价格、运行的经济性和适应性来划分的。

通用机的分类依据主要是体积、简易性、功率损耗、性能指标、数据存储容量、指令系统规模和机器价格等因素。

4.冯. 诺依曼型计算机的主要设计思想是什么?它包括哪些主要组成部分?解:冯. 诺依曼型计算机的主要设计思想是:存储程序和程序控制。

存储程序:将解题的程序(指令序列)存放到存储器中;程序控制:控制器顺序执行存储的程序,按指令功能控制全机协调地完成运算任务。

主要组成部分有:(控制器、运算器)(CPU的两部分组成)、存储器、输入设备、输出设备(I/O设备)。

5.什么是存储容量?什么是单元地址?什么是数据字?什么是指令字?解:存储容量:指存储器可以容纳的二进制信息的数量,通常用单位KB、MB、GB来度量,存储容量越大,表示计算机所能存储的信息量越多,反映了计算机存储空间的大小。

单元地址:简称地址,在存储器中每个存储单元都有唯一的地址编号,称为单元地址。

数据字:若某计算机字是运算操作的对象即代表要处理的数据,则称数据字。

指令字:若某计算机字代表一条指令或指令的一部分,则称指令字。

6.什么是指令?什么是程序?解:指令:计算机所执行的每一个基本的操作。

程序:解算某一问题的一串指令序列称为该问题的计算程序,简称程序。

7.指令和数据均存放在内存中,计算机如何区分它们是指令还是数据?解:一般来讲,在取指周期中从存储器读出的信息即指令信息;而在执行周期中从存储器中读出的信息即为数据信息。

计算机组成原理与系统结构习题解答共93页

计算机组成原理与系统结构习题很 少遇到 抵抗。 ——塞 ·约翰 逊 2、权力会使人渐渐失去温厚善良的美 德。— —伯克

3、最大限度地行使权力总是令人反感 ;权力 不易确 定之处 始终存 在着危 险。— —塞·约翰逊 4、权力会奴化一切。——塔西佗

5、虽然权力是一头固执的熊,可是金 子可以 拉着它 的鼻子 走。— —莎士 比

31、只有永远躺在泥坑里的人,才不会再掉进坑里。——黑格尔 32、希望的灯一旦熄灭,生活刹那间变成了一片黑暗。——普列姆昌德 33、希望是人生的乳母。——科策布 34、形成天才的决定因素应该是勤奋。——郭沫若 35、学到很多东西的诀窍,就是一下子不要学很多。——洛克

计算机组成原理与系统结构课后答案包健

计算机组成原理与系统结构课后答案包健【篇一:计算机组成原理课后作业答案(包健第二版)完整】(设机器数长度为8位)[x]补=0.1101000 [-x]补=1.0011000 [2x]补=溢出 [-2x]补=溢出[x/2]补=0.0110100 [-x/2]补=1.1001100 [y]补=1.1010000 [-y]补=0.0110000 [2y]补=1.0100000 [-2y]补=0.1100000 [y/2]补=1.1101000 [-y/2]补=0.0011000 [-y/4] 补=0.0001100p156:2、(1)(2)p156:4-4原码恢复余数算法6-1【篇二:11级教材包健习题答案】征是什么?略。

1.2 你学习计算机知识后,准备做哪方面的应用?略。

1.3 试举一个你所熟悉的计算机应用例子。

略。

1.4 计算机通常有哪些分类方法?你比较了解的有哪些类型的计算机?略。

1.5 计算机硬件系统的主要指标有哪些?答:机器字长、存储容量、运算速度、可配置外设等。

答:计算机硬件系统的主要指标有:机器字长、存储容量、运算速度等。

1.6 什么是机器字长?它对计算机性能有哪些影响?答:指cpu一次能处理的数据位数。

它影响着计算机的运算速度,硬件成本、指令系统功能,数据处理精度等。

1.7 什么是存储容量?什么是主存?什么是辅存?答:存储容量指的是存储器可以存放数据的数量(如字节数)。

它包括主存容量和辅存容量。

主存指的是cpu能够通过地址线直接访问的存储器。

如内存等。

辅存指的是cpu不能直接访问,必须通过i/o接口和地址变换等方法才能访问的存储器,如硬盘,u盘等。

用一次。

(1)为个人使用而设计的计算机,通常有图形显示器、键盘和鼠标。

(2)计算机中的核心部件,它执行程序中的指令。

它具有加法、测试和控制其他部件的功能。

(3)计算机的一个组成部分,运行态的程序和相关数据置于其中。

(4)处理器中根据程序的指令指示运算器、存储器和i/o设备做什么的部件。

计算机组成原理与系统结构课后作业答案(包健-冯建文-章复嘉版)

《运算器》P101 3.3写出下列各数的原码、反码和补码,机器数长度为8位:真值二进制真值原码反码补码0,00000000,00000000,0000000(1)000000001,00000001,1111111(2)-127-11111111,11111111,00000001,0000001(3)-0.5-0.1000000 1.1000000 1.0111111 1.1000000(4)-19/128-0.0010011 1.0010011 1.1101100 1.1101101(5)10011001000,11001000,11001000,1100100(6)23/640.0101110.01011100.01011100.0101110P101 3.4写出下列各机器数的二进制真值X:(1)[X]补=0,1001X=1001(2)[X]补=1,1001X=-111(3)[X]原=0,1101X=1101(4)[X]原=1,1101X=-1101(5)[X]反=0,1011X=1011(6)[X]反=1,1011X=-100(7)[X]移=0,1001X=-111(8)[X]移=1,1001X=+1001(9)[X]补=1,0000000X=-10000000B,X=-128(10)[X]反=1,0000000X=-1111111B,X=-127(11)[X]原=1,0000000X=-0(12)[X]移=1,0000000X=0P156 4.1 X=0.1101Y=-0.0110(设机器数长度为8位)[X]补=0.1101000[-X]补=1.0011000[2X]补=溢出[-2X]补=溢出[X/2]补=0.0110100[-X/2]补=1.1001100[Y]补=1.1010000[-Y]补=0.0110000[2Y]补=1.0100000[-2Y]补=0.1100000[Y/2]补=1.1101000[-Y/2]补=0.0011000[-Y/4]补=0.0001100P102:3.8、阶码(6位移码)尾数(6位原码)(1)X=-25/64=-0.011001B ,Y=2.875=10.111B [X]浮=0,11111 1.11001=7F9H [Y]浮=1,00010 0.10111=897H (2)[Z]浮=9F4H=1,00111 1.10100=-80P102:9、机器数字长16位(1)无符号整数:12~016-(2)原码表示的定点整数:1,111…11~0,111…11即12~)12(1515---(3)补码表示的定点整数:1,00…000~0,111…11即12~21515--(4)补码表示的定点小数:1.00…000~0.111…11即1521~1---(5)非规格化浮点数:ERM N ⨯=阶码(8位移码)尾数(8位补码)最大数=12772)21(--⨯-阶码=1,1111111尾数=0.1111111最小数=12721-⨯-阶码=1,1111111尾数=1.0000000最大负数=72722--⨯-阶码=0,0000000尾数=1.1111111最小正数=72722--⨯阶码=0,0000000尾数=0.0000001(6)规格化浮点数:最大数=12772)21(--⨯-阶码=1,1111111尾数=0.1111111最小数=12721-⨯-阶码=1,1111111尾数=1.0000000最大负数=72712)22(---⨯+-阶码=0,0000000尾数=1.0111111最小正数=72122--⨯阶码=0,0000000尾数=0.10000004-2P156:55-1补码BOOTH算法5-2补码BOOTH算法P156:6、6-1原码恢复余数算法6-2原码加减交替算法P156 7-1补码加减交替算法7-2补码加减交替算法X=0.2344 = 0.00111 Y= -0.1133=-0.00011X-Y:1、对阶同上2、尾数相减:00.11100+ 00.01100[E X-Y]补= 01.01000 发生正溢尾数右移,阶码加1[E X-Y]补= 0.10100[M x-y] = 1.11113、结果不需规格化4、舍入处理:[E X-Y]补=0.10100[X-Y] = 1,1111 0,101009-1 X/Y:9-2 X*Y9-2 X/Y《存储体系》P225:2、(1)片641641161664=⨯=⨯⨯K K (2)s msμ625.151282=(3)s ns μ64500128=⨯P225:3、(1)最大主存容量=bit16218⨯(2)共需芯片;若采用异步刷新,则刷新信号的周期为片6416416416218=⨯=⨯⨯bitK bits msμ625.151282=(3)每块8字节,则Cache 容量为,即c=9,Cache 采用2路行925128162==⨯BytebitK 组相联映射,则r=1。

计算机组成与系统结构习题参考答案

计算机组成与系统结构习题答案第1章计算机系统概述1-1 见教材1.1.2。

1-2 见教材1.2.1。

1-3 见教材1.2.1。

1-4 见教材1.2.3。

1-5 见教材1.3.1。

1-6 各需KN ns 、KN 2 ns 、KN 3 ns 的时间。

1-7 需要K M N s 、K 22M N s 和K 33MN s 的时间。

1-8 透明的有:指令缓冲器、时序发生器、乘法器、主存地址寄存器、先行进位链、移位器。

1-9 见教材1.4.2。

1-1053.01910==F1-11 CPI=1.55, 运算速度≈25.81MIPS程序执行时间=3.875×10-3s 1-12 (1)平均CPI=2.28。

(2)MIPS 速率≈43.86MIPS 。

1-13 第二种方法效果就好。

第2章数据的机器层次表示2-1 (725.6875)10=(1325.54)8=(2D5.B)16=(1011010101.1011)22-2 (111010.011)2=(72.3)8=(3A.6)16。

(1000101.1001)2=(105.44)8=(45.9)16。

2-3 真值 原码 补码 反码 0 -0 0.1000 -0.1000 0.1111 -0.1111 1101 -110100000000 10000000 0.1000000 1.1000000 0.1111000 1.1111000 00001101 1000110100000000 00000000 0.1000000 1.1000000 0.1111000 1.0001000 00001101 1111001100000000 11111111 0.1000000 1.0111111 0.1111000 1.0000111 00001101 111100102-4真值原码补码反码1670.0111 0.0111 0.01111640.0100 0.0100 0.01001610.0001 0.0001 0.00010 0.0000 0.0000 0.0000-0 1.0000 0.0000 1.1111-161 1.0001 1.1111 1.1110-164 1.0100 1.1100 1.1011-167 1.0111 1.1001 1.10002-5[X1]补=0.10100,[X2]补=1.01001。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《运算器》P101 3.4写出下列各机器数的二进制真值X:(1)[X]补=0,1001 X=1001(2)[X]补=1,1001 X=-111(3)[X]原=0,1101 X=1101(4)[X]原=1,1101 X=-1101(5)[X]反=0,1011 X=1011(6)[X]反=1,1011 X=-100(7)[X]移=0,1001 X=-111(8)[X]移=1,1001 X=+1001(9)[X]补=1,0000000 X=-10000000B,X=-128(10)[X]反=1,0000000 X=-1111111B,X=-127(11)[X]原=1,0000000 X=-0(12)[X]移=1,0000000 X=0P156 4.1X=0.1101 Y=-0.0110(设机器数长度为8位)[X]补=0.1101000[-X]补=1.0011000[2X]补=溢出[-2X]补=溢出[X/2]补=0.0110100[-X/2]补=1.1001100[Y]补=1.1010000[-Y]补=0.0110000[2Y]补=1.0100000[-2Y]补=0.1100000[Y/2]补=1.1101000[-Y/2]补=0.0011000[-Y/4]补=0.0001100(1) X=-25/64=-0.011001B ,Y=2.875=10.111B[X]浮=0,11111 1.11001=7F9H [Y]浮=1,00010 0.10111=897H (2) [Z]浮=9F4H=1,00111 1.10100=-80P102:9、机器数字长16位 (1) 无符号整数:12~016-(2) 原码表示的定点整数:1,111…11~0,111…11即12~)12(1515---(3) 补码表示的定点整数:1,00…000~0,111…11即12~21515-- (4) 补码表示的定点小数:1.00…000~0.111…11即1521~1--- (5) 非规格化浮点数:ER M N ⨯=最大数=12772)21(--⨯-最小数=12721-⨯-最大负数=72722--⨯-最小正数=72722--⨯(6) 最大数=12772)21(--⨯-最小数=12721-⨯-最大负数=72712)22(---⨯+-最小正数=72122--⨯(1)(2)P156:4-14-2P156:55-1补码BOOTH算法5-2补码BOOTH算法P156:6、6-1原码恢复余数算法6-2原码加减交替算法P156 7-1补码加减交替算法7-2补码加减交替算法P156:4.8阶码(5位补码)尾数(6位补码)(1)X=-1.625=-1.101B Y=5.25=101.01B X+YX-Y:1、对阶同上2、尾数相减:11.1100110+ 11.01011[E X-Y]补= 11.00100103、结果不需规格化4、舍入处理:[E X-Y]补=1.00101[X-Y] = 0,0011 1,00101X=0.2344 = 0.00111 Y= -0.1133=-0.00011X-Y:1、对阶同上2、尾数相减:00.11100+ 00.01100[E X-Y]补= 01.01000 发生正溢尾数右移,阶码加1[E X-Y]补= 0.10100[M x-y] = 1.11113、结果不需规格化4、舍入处理:[E X-Y]补=0.10100[X-Y] = 1,1111 0,10100阶码(5位移码)尾数(6位补码)(1)X=5.25=101.01B Y=-1.625=-1.101B X*Y9-1 X/Y:9-2 X*Y9-2 X/Y《存储体系》P225:2、 (1) 片641641161664=⨯=⨯⨯K K(2) s msμ625.151282=(3) s ns μ64500128=⨯ P225:3、(1) 最大主存容量=bit 16218⨯(2) 共需片6416416416218=⨯=⨯⨯bitK bit芯片;若采用异步刷新,则刷新信号的周期为s msμ625.151282= (3) 每块8字节,则Cache 容量为行925128162==⨯BytebitK ,即c=9,Cache 采用2路组相联映射,则r=1。

主存容量为块161828162=⨯Bytebit,即m=16。

每块包含4个字,每字包含2个字节。

标记行0标记行11标记行21标记行3…28-1标记行29-2标记行29 -1Cache Cache主存01 (2)8主存字块标记组地址块内字地址882主存字地址16主存字块标记组地址块内字地址882主存字节地址16字内字节地址1主存字地址=462EH=00 0100 01,10 0010 11,10;因此该字映射到Cache 的第139组。

(4) 分析地址:A 15A 14A 13A 12A 11A 10A 9A 8A 7A 6A 5A 4A 3A2A 1A 0最小128K RAM0000000000000000111111111111111111111111111111110000000000000… …… …… …A 17A 1600最高端8K ROM11111111保留区128K 的RAM 区由片162881616128=⨯=⨯⨯bitK bitK SRAM 芯片构成;分为8组,组与组之间进行字扩展;每个组内有2片进行位扩展。

P225:5、平均访问时间)()1()1()()1(p c m m c c m m c c c a t t t h h t t h h t h t ++⨯-⨯-++⨯⨯-+⨯= 其中:t a —— 平均访问时间;t c —— Cache 的存储周期;t m —— 主存的存储周期;t p —— 磁盘的存储周期;h c —— Cache 的命中率;h m —— 主存的命中率。

所以,nsns ns ns ns t ns ns ns ns t a a 74482.38.418)120080(%40%1080%60%1020%90=+++=+⨯⨯+⨯⨯+⨯=P168:6、 命中率%5.97%10010039003900=⨯+=h平均访问时间nsns ns ns ns t t h t h t a mc a 45639240%5.240%5.97)1(=+=⨯+⨯=⨯-+⨯=e = t c /t a =40/45=8/9P168:7、4路组相联映射,所以r=2 每块4字,所以b=2; 每字32位,所以每字包含4字节。

Cache 容量为行行字节字节92512448==⨯K ,故c=9主存容量为块块字节字节20214416==⨯M M ,故m=20标记行0标记行31标记行4标记行7…27-1标记行29-4标记行29 -1Cache Cache主存01 (213)…………(1) Cache 共分为:2c-r = 29-2 = 128组。

(2)主存字块标记组地址块内字地址1372主存字节地址20字内字节地址2P226:8、4路组相联映射,所以r=2 每块64字,所以b=6; Cache 容量为行字字72648=K ,故c=7 主存容量为块字字12264256=K ,故m=12标记行0标记行31标记行4标记行7…25-1标记行27-4标记行27 -1Cache Cache主存01 (2)7…………主存字地址0~8447,位于主存的哪几块内呢?132648448=字字,即主存的第0~8447字位于连续的132块内。

4421325余商块块=,因此这132块连续分布在第0~4大组内,其中在第4大组中只有4块。

CPU 第1次依次访问主存的0~8447字时不命中132次。

Cache 的变化如图所示CPU 从第2次开始直到第21次访问主存的0~8447字时,每轮不命中20次(从第0~4大组的前4块都不命中,其余都命中),Cache 的变化如图所示Cache第0大组第1大组第2大组第3大组第4大组主存Cache Cache Cache Cache Cache Cache因为10mc t t =, 命中率%7.99%100177408176876%1002184482020132218448=⨯=⨯⨯⨯--⨯=h设使用Cache 比不使用Cache 在速度上提高x 倍,则倍7.91011)1(10)()1(=⨯⨯-+⨯=+⨯-+⨯=mm mc m c mt h t h t t t h t h t x《指令系统》12、地址0019H001AH第一条转移指令:0019H001AH(PC)=001AH,执行该JMP指令后(PC)=001AH+0006H=0020H第二条转移指令:0019H001AH(PC)=001AH,执行该13、寄存器-存储器型指令是指一个操作数来自寄存器,另一个操作数来自存储器。

间接寻址时EA=(ADDR),因此操作数地址存放在主存地址为0~219-1的单元内,假设存储器按字编址,则EA应该是32位的地址,则主存最大存储空间为232字。

(2)其实用32位通用寄存器做基址寄存器,类似于80X86机器上存储器分段管理。

EA=32位基地址+偏移地址,所以EA是32位,则主存最大存储空间为232字。

16、设某机寄存器字长16位,用16进制表示,已知:变址寄存器内容为0004H,PC 的内容为0003H,内存中部分单元内容如下:地址:内容地址:内容0002H:000AH 0007H:000AH0003H:0002H 0008H:0002H0004H:0007H 0009H:0003H0005H:0004H 000AH:0009H0006H:0005H 000BH:0008H若某机器字长16位,采用单字长指令,每个地址码6位。

试采用操作码扩展技术,设计14条二地址指令,80条一地址指令,60条零地址指令。

请给出指令编码示意图。

设某8位计算机,除HALT 指令外,指令均为双字长,格式如下:其中,问:CPU 启动执行指令到停机,期间执行了哪几条指令?写出每条指令的功能、寻址方式、操作数及执行结果。

解:由于(PC )=22H ,即程序的第一条指令地址为22H ,从22H 开始,执行到2DH (HALT 指令)为止,共五条指令。

经分析,所有指令的目的操作数的寻址方式均为寄存器寻址方式,为R1。

下面列出每条指令的功能、源操作数的寻址方式、源操作数及执行结果。

《控制器》6、设某机平均执行一条指令需要两次访问内存,平均需要三个机器周期,每个机器 周期包含4个节拍周期。

若机器主频为25MHz ,试回答:1)若访问主存不需要插入等待周期,则平均执行一条指令的时间为多少? 2)若每次访问内存需要插入2个等待节拍周期,则平均执行一条指令的时间是又多少?解:(1)MHz2511==主频时钟周期 s μ48.043=⨯⨯=时钟周期平均指令周期(2)s μ64.02243=⨯⨯+⨯⨯=时钟周期时钟周期平均指令周期7、设某机主频为8MHz ,每个机器周期包含4个节拍周期,该机平均指令执行速度为1MIPS 。