本科优秀毕业论文(时钟数据恢复)

一种新型的高速时钟数据恢复电路的设计和验证

一种新型的高速时钟数据恢复电路的设计和验证摘要:1.背景和动机2.电路设计原理3.具体设计方案4.验证和测试5.结果和分析6.结论和展望正文:一、背景和动机随着现代通信技术的快速发展,高速数据传输已经成为通信系统中的关键技术。

在高速数据传输过程中,时钟数据恢复电路(CDR)作为核心模块,对于确保数据传输的准确性和稳定性具有至关重要的作用。

本文针对一种新型的高速时钟数据恢复电路进行设计和验证,以满足不断提高的通信速率需求。

二、电路设计原理本文提出的高速时钟数据恢复电路主要基于数字信号处理技术,通过捕获和恢复发送端时钟信号的相位信息,实现接收端时钟与发送端时钟的同步。

电路设计的关键部分包括:高速锁相环电路、复用CDR环路、滤波器和相位插值控制电路。

三、具体设计方案1.高速锁相环电路:采用1.25GHz的参考时钟,通过16相频锁相环技术,提供数据恢复所需的等相位间隔参考时钟。

2.复用CDR环路:采用电流逻辑模式前端电路,构成复用CDR环路,以实现对高速数据信号的恢复。

3.滤波器和相位插值控制电路:设计滤除亚稳态时钟的采样超前、滞后鉴相器,以及选择时钟与相位插值的控制时钟电路。

四、验证和测试通过对所设计的高速时钟数据恢复电路进行数模混合仿真检测,验证电路在实际应用环境中的性能。

测试结果表明,该电路具有较高的恢复准确性和稳定性。

五、结果和分析本文提出的高速时钟数据恢复电路在仿真测试中表现出良好的性能,为实现高速数据传输提供了有效的同步解决方案。

相比传统电路设计,该方案具有更高的恢复速度和更低的功耗,有助于提高通信系统的整体性能。

六、结论和展望本文针对一种新型的高速时钟数据恢复电路进行了详细的设计和验证。

通过采用数字信号处理技术,实现了高精度、高速度的时钟信号恢复。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种数字通信领域中常用的技术,用于从接收到的信号中恢复出时钟信息,并将其用于数据采样和解码。

本文将介绍时钟数据恢复的工作原理以及其在通信系统中的应用。

一、时钟数据恢复的原理1.1 时钟信号的重要性时钟信号在数字通信系统中起着至关重要的作用,它用于同步发送和接收端的数据采样和解码过程。

时钟信号的准确性和稳定性直接影响到通信系统的性能。

1.2 时钟数据恢复的需求在数字通信中,接收到的信号可能会受到传输介质、噪声等因素的影响,导致时钟信号的失真和抖动。

因此,需要一种方法来从接收到的信号中恢复出准确的时钟信息。

1.3 时钟数据恢复的原理时钟数据恢复的原理是基于接收到的信号中的边缘信息来恢复时钟信号。

通过比较信号的上升沿和下降沿的时间间隔,可以推测出时钟信号的频率和相位,从而实现时钟数据的恢复。

二、时钟数据恢复的应用2.1 数字通信系统时钟数据恢复在数字通信系统中广泛应用,用于恢复接收端的时钟信号,以确保数据的准确采样和解码。

它可以应对传输介质的噪声和失真,提高通信系统的可靠性和性能。

2.2 光纤通信在光纤通信中,时钟数据恢复被用于恢复接收端的光信号的时钟信息。

光信号在传输过程中可能会受到光纤的色散和衰减等影响,导致时钟信号的失真。

时钟数据恢复技术可以有效地恢复出准确的时钟信号,提高光纤通信系统的性能。

2.3 高速串行通信在高速串行通信中,时钟数据恢复被用于恢复接收端的时钟信号。

高速串行通信中的时钟信号往往由数据信号中的边缘信息推测而来,因此时钟数据恢复技术对于保证数据的准确采样和解码至关重要。

三、时钟数据恢复的算法3.1 相位锁定环路(Phase Locked Loop, PLL)相位锁定环路是一种常用的时钟数据恢复算法。

它通过不断调整本地时钟的相位和频率,使其与接收到的信号的相位和频率保持同步,从而实现时钟数据的恢复。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种重要的数字信号处理技术,用于恢复由于传输过程中引起的时钟偏移或者颤动而导致的数据失真。

本文将介绍时钟数据恢复的原理、应用、算法、性能和发展趋势。

一、时钟数据恢复的原理1.1 时钟数据恢复的基本概念时钟数据恢复是指通过对接收到的数字信号进行时钟提取和重构,以确保数据在接收端正确解调和处理的过程。

1.2 时钟信号的重要性时钟信号是数字通信系统中的关键信号,它决定了数据信号的采样时刻和速率,直接影响系统的性能和稳定性。

1.3 时钟数据恢复的原理时钟数据恢复通过采用PLL(锁相环)或者其他算法对接收到的信号进行时钟提取和重构,使得接收端的时钟与发送端的时钟保持同步。

二、时钟数据恢复的应用2.1 数字通信系统中的应用时钟数据恢复广泛应用于数字通信系统中,如光纤通信、无线通信、卫星通信等领域。

2.2 数据存储系统中的应用时钟数据恢复也被应用于数据存储系统中,如硬盘驱动器、固态硬盘等设备,以确保数据的读取和写入的准确性和稳定性。

2.3 其他领域的应用时钟数据恢复还被广泛应用于音频处理、视频处理、雷达系统等领域,以提高系统的性能和可靠性。

三、时钟数据恢复的算法3.1 PLL算法PLL算法是时钟数据恢复中常用的算法之一,通过不断调整本地时钟的频率和相位,使其与接收到的信号保持同步。

3.2 时域插值算法时域插值算法通过对信号进行插值处理,补偿传输过程中的时钟偏移和颤动,以恢复原始数据信号。

3.3 频域分析算法频域分析算法通过对信号进行频谱分析,提取信号的频率信息,从而实现时钟数据恢复。

四、时钟数据恢复的性能4.1 误码率时钟数据恢复的性能可以通过误码率来评估,误码率越低,说明时钟数据恢复的效果越好。

4.2 颤动抑制能力时钟数据恢复的性能还可以通过颤动抑制能力来评估,颤动抑制能力越强,说明时钟数据恢复对传输过程中的颤动影响越小。

4.3 鲁棒性时钟数据恢复的性能还可以通过其对噪声和干扰的反抗能力来评估,鲁棒性越强,说明时钟数据恢复对环境变化的适应能力越强。

《面向400G的光通信的时钟与数据恢复电路设计》

《面向400G的光通信的时钟与数据恢复电路设计》面向400G光通信的时钟与数据恢复电路设计一、引言随着互联网的迅猛发展,对高速、大容量的光通信技术需求日益增长。

其中,400G光通信技术以其高速率和高效能的优势,成为了现代通信网络的关键技术之一。

在400G光通信系统中,时钟与数据恢复电路的设计显得尤为重要。

本文将探讨面向400G 光通信的时钟与数据恢复电路设计,以提高系统性能和可靠性。

二、时钟与数据恢复电路的重要性在光通信系统中,时钟与数据恢复电路是关键组成部分。

它负责从接收到的光信号中提取时钟信号和数据信息,以保证信号传输的同步性和准确性。

时钟与数据恢复电路的性能直接影响整个系统的传输速率、误码率和可靠性。

因此,优化设计时钟与数据恢复电路是提高400G光通信系统性能的关键。

三、设计要求与挑战在面向400G光通信的时钟与数据恢复电路设计中,需要满足以下要求:1. 高速度:电路必须能够处理高达400Gbps的数据速率,以满足高速传输的需求。

2. 低抖动:时钟信号的抖动必须尽可能小,以保证信号传输的稳定性和准确性。

3. 抗干扰能力强:电路应具备较好的抗电磁干扰和光噪声干扰能力,以保证在复杂电磁环境下的性能稳定性。

4. 低功耗:在保证性能的前提下,应尽量降低电路功耗,以延长设备使用寿命和降低运营成本。

然而,在实际设计中,面临诸多挑战。

例如,如何在高速传输中保持低抖动、如何提高电路的抗干扰能力以及如何在保证性能的同时降低功耗等。

这些挑战要求设计者具备深厚的电子工程知识和丰富的实践经验。

四、设计思路与方法为了满足上述设计要求,可以采取以下设计思路与方法:1. 采用先进的电路技术:如采用高速、低抖动的时钟恢复电路和高速、高灵敏度的数据恢复电路,以提高电路的性能和稳定性。

2. 优化电路结构:通过优化电路布局和参数设计,降低电路功耗,提高抗干扰能力。

3. 引入先进算法:如采用锁相环、自适应滤波等算法,实现时钟与数据的同步恢复和优化处理。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种用于恢复数字信号中时钟信息的技术,它在数字通信系统中起着至关重要的作用。

本文将从时钟数据恢复的定义、原理、应用、发展和未来趋势等方面进行探讨。

一、时钟数据恢复的定义1.1 时钟数据恢复是指在数字通信系统中从接收到的信号中提取出时钟信息的过程。

1.2 时钟数据恢复技术通过对接收到的信号进行处理,从中提取出时钟信号,以确保信号的正确接收和处理。

1.3 时钟数据恢复技术可以应用于各种数字通信系统中,如光纤通信、无线通信等。

二、时钟数据恢复的原理2.1 时钟数据恢复的原理是通过对接收到的信号进行采样和重构,从中提取出时钟信息。

2.2 时钟数据恢复技术通常包括时钟信号提取、时钟信号重构和时钟信号同步等过程。

2.3 时钟数据恢复的原理是基于数字信号处理和时钟同步技术,通过对信号进行分析和处理实现时钟信息的提取和恢复。

三、时钟数据恢复的应用3.1 时钟数据恢复技术广泛应用于数字通信系统中,如光纤通信、无线通信等。

3.2 时钟数据恢复技术可以提高系统的稳定性和可靠性,确保信号的正确接收和处理。

3.3 时钟数据恢复技术还可以用于信号的重构和同步,以确保系统的正常运行和数据的准确传输。

四、时钟数据恢复的发展4.1 随着数字通信技术的不断发展,时钟数据恢复技术也在不断完善和提升。

4.2 新的时钟数据恢复算法和技术不断涌现,为数字通信系统的性能提升提供了有力支持。

4.3 时钟数据恢复技术的发展趋势是向着更高的精度、更低的功耗和更广泛的应用领域发展。

五、时钟数据恢复的未来趋势5.1 未来时钟数据恢复技术将更加注重对复杂信号环境下的时钟信息提取和恢复。

5.2 时钟数据恢复技术将不断融合新的技术手段,如人工智能、深度学习等,以提高系统的性能和稳定性。

5.3 时钟数据恢复技术的未来趋势是向着更智能、更高效和更可靠的方向发展。

总结:时钟数据恢复技术在数字通信系统中具有重要作用,通过对接收到的信号进行处理,提取出时钟信息,确保信号的正确接收和处理。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种重要的通信技术,用于在数字通信系统中恢复时钟信号。

在数字通信系统中,时钟信号是非常关键的,它用于同步发送和接收数据,确保数据的准确传输。

本文将介绍时钟数据恢复的原理、应用、技术和发展趋势。

一、时钟数据恢复的原理1.1 时钟信号的重要性:时钟信号用于同步发送和接收数据,确保数据的准确传输。

1.2 时钟信号的失真:在数字通信系统中,时钟信号可能因为传输距离、噪声等原于是失真。

1.3 CDR的作用:CDR可以通过对接收到的数据进行分析和处理,恢复出准确的时钟信号。

二、时钟数据恢复的应用2.1 光通信系统:在光通信系统中,CDR可以用于恢复光信号的时钟信号。

2.2 高速数据传输:在高速数据传输系统中,CDR可以用于恢复数据的时钟信号,确保数据传输的准确性。

2.3 无线通信系统:在无线通信系统中,CDR可以用于恢复无线信号的时钟信号,提高数据传输的稳定性。

三、时钟数据恢复的技术3.1 相位锁定环(PLL):PLL是一种常用的时钟数据恢复技术,通过反馈控制相位差,使得输出的时钟信号与输入的时钟信号同步。

3.2 等化器:等化器可以对接收到的信号进行处理,去除噪声和失真,从而恢复出准确的时钟信号。

3.3 自适应滤波器:自适应滤波器可以根据接收到的信号的特点自动调整滤波器的参数,提高时钟数据恢复的准确性。

四、时钟数据恢复的发展趋势4.1 高速化:随着通信技术的发展,时钟数据恢复技术也在不断提高传输速度。

4.2 高精度:时钟数据恢复技术将会越来越精确,以应对复杂的通信环境。

4.3 低功耗:未来的时钟数据恢复技术将会越来越注重低功耗,以满足节能环保的需求。

五、结论时钟数据恢复是数字通信系统中非常重要的技术,它可以确保数据的准确传输。

随着通信技术的不断发展,时钟数据恢复技术也在不断提高,未来将会在高速化、高精度和低功耗方面取得更大的突破。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种用于恢复时钟信号的技术,它在现代通信和数据传输领域中起着重要的作用。

CDR技术可以有效地提取出传输信号中的时钟信息,使得接收端能够正确地解读数据。

本文将介绍CDR的基本原理、应用场景、性能指标、实现方式和未来发展方向。

一、CDR的基本原理1.1 时钟信号的重要性:时钟信号在数据传输中起着同步和定时的作用,是确保数据准确传输的关键。

1.2 时钟偏移和颤动:在数据传输中,时钟信号可能会受到噪声、失真等因素的影响,导致时钟偏移和颤动。

1.3 时钟恢复技术:CDR技术通过采样、滤波、锁相环等方法,对接收到的信号进行处理,恢复出准确的时钟信息。

二、CDR的应用场景2.1 光纤通信:在光纤通信中,CDR技术可以解决光纤传输中的时钟漂移和颤动问题,提高传输质量和稳定性。

2.2 高速串行链路:在高速串行链路中,CDR技术可以对传输信号进行时钟恢复,保证数据的准确性和可靠性。

2.3 无线通信:在无线通信中,CDR技术可以对接收到的信号进行时钟恢复,提高信号解调的效果,提升通信质量。

三、CDR的性能指标3.1 颤动容限:CDR技术的性能可以通过颤动容限来评估,即在不同信号条件下,CDR能够恢复出稳定的时钟信号的最大颤动范围。

3.2 时钟恢复时间:CDR技术的性能还可以通过时钟恢复时间来评估,即从接收到信号到恢复出稳定的时钟信号所需的时间。

3.3 误码率:CDR技术的性能还可以通过误码率来评估,即在时钟恢复后,数据传输中浮现的错误比特率。

四、CDR的实现方式4.1 采样和保持:CDR技术中的采样和保持电路可以对传输信号进行采样,以获取时钟信息。

4.2 相位锁定环:CDR技术中的相位锁定环可以通过调整相位来实现时钟恢复,保证接收到的信号与本地时钟同步。

4.3 时钟恢复算法:CDR技术中的时钟恢复算法可以通过对采样数据进行处理,恢复出准确的时钟信号。

五、CDR的未来发展方向5.1 高速率:随着通信和数据传输领域的发展,对高速率的需求越来越大,CDR技术需要不断提高性能,以适应高速率传输的要求。

本科优秀毕业论文(时钟数据恢复)

摘要摘要本论文主要提供了一种实用的方式从数据流中恢复时钟,并以此时钟来恢复出原始数据,并且设计产生系统自检所需的信号。

本设计基于如今已经非常成熟的FPGA技术,采用一种非常新颖的方法成功实现了从数据流中同步恢复出时钟,并且采用纯数字电路的方法,利用EDA平台设计出了恢复原始数据的译码电路,此外,本设计还实现了系统自检;设计从实际应用的角度出发,旨在解决现实生活中的车载电子设备的通信问题,切合实际,同时,对现有的时钟同步数据恢复的方法进行学习与改进。

论文涵盖了模拟电路设计,数字电路设计,硬件编程,调试,软件仿真,逻辑综合各个方面,具有很大的现实意义。

关键词:时钟数据恢复,FPGA,锁相环,状态机IABSTRACTABSTRACTThis paper aims at providing a practical method to recovery the clock transformed by the data stream, through which it can decode the original data stream and it can create the self-checking signal needed by the system.My design succeeds to recovery the clock through the data stream based on the technology of mature FPGA and I achieve to design the decoding circuit by digital circuit on the platform of EDA. The research is from the practical point of view, aiming to solve communication problems in real life in-vehicle electronic devices. Also, we learn and improve on existing methods of clock and data recovery. The design contains analogy circuit design, digital circuit design, hardware programming, debug, simulation and logical synthesis and so on.Key Words: Clock and Data Recovery, FPGA, PLL, State MachineII目录第1章引言 (1)1.1数据恢复的同步设计和系统自检的概况和发展现状 (1)1.1.1时钟数据同步恢复电路的简介 (1)1.1.2系统自检的简介 (2)1.1.3时钟数据恢复电路的发展趋势 (2)1.2时钟数据恢复电路以及系统自检的必要性和挑战 (3)1.3本课题的研究目的和研究内容 (4)1.3.1研究目的 (4)1.3.2研究内容 (5)1.3.3论文的结构安排 (6)第2章传统的时钟数据恢复电路 (7)2.1概述 (7)2.2传统的时钟数据恢复电路的方法 (8)2.2.1前馈相位跟踪型CDR (8)2.2.2反馈相位跟踪型CDR (11)第3章基于FPGA的时钟数据恢复电路 (16)3.1设计任务概述 (16)3.2各模块电路设计 (16)3.2.1毛刺消除电路的设计 (16)3.2.2时钟恢复电路的设计 (18)3.2.3译码电路的设计 (24)3.2.3.1有限状态机的介绍 (25)3.2.3.2序列检测器的设计 (26)3.2.3.3时钟数据恢复电路 (29)第4章系统自检的设计以及电路中各个时钟的设计 (31)III4.1系统自检的设计 (31)4.1.1自检信号序列发生器的设计 (31)4.2时钟数据恢复电路中的时钟 (34)4.2.1时钟数据恢复电路系统的总体电路图 (34)4.3锁相环技术 (35)4.3.1锁相环简介 (35)4.3.1.1鉴相器 (36)4.3.1.2环路滤波器 (36)4.3.1.3压控振荡器 (37)4.3.2锁相环倍频获得所需时钟信号 (37)第5章结束语 (40)参考文献 (41)致谢 (42)外文资料原文 (43)外文资料翻译 (53)IV第1章引言第1章引言在高速串行数据通信中,为了节省开销,一般只传送数据信号而不传送与数据信号同步的时钟信号。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种用于恢复传输信号中的时钟信息的技术。

在数字通信中,信号传输过程中可能会受到噪声、失真等干扰,导致时钟信息的丢失或者不稳定。

CDR技术通过对传输信号进行采样和重构,恢复出准确的时钟信号,确保数据的可靠传输。

本文将从原理、应用、算法、性能和未来发展等五个方面详细介绍时钟数据恢复技术。

一、原理:1.1 时钟信号的重要性:时钟信号在数字通信中起到同步和定时的作用,确保数据的准确传输。

1.2 时钟信号的丢失和不稳定性原因:传输信号受到噪声、失真、衰减等干扰因素影响,导致时钟信息的丢失或者不稳定。

1.3 CDR的作用:CDR技术通过采样和重构传输信号,恢复出准确的时钟信号,保证数据的可靠传输。

二、应用:2.1 光纤通信中的CDR:光纤通信中,光信号在传输过程中容易受到衰减、色散等影响,导致时钟信息的丢失。

CDR技术可以恢复出准确的时钟信号,提高光纤通信的性能。

2.2 高速串行通信中的CDR:高速串行通信中,时钟信号的恢复对于数据的传输速率和稳定性至关重要。

CDR技术可以在高速串行通信中实时恢复时钟信号,确保数据的可靠传输。

2.3 高频信号处理中的CDR:在高频信号处理中,时钟信号的准确性对于信号处理算法的性能有着重要影响。

CDR技术可以提供准确的时钟信号,提高高频信号处理的精度和效果。

三、算法:3.1 时钟恢复算法的分类:时钟恢复算法可以分为基于锁相环(PLL)的算法和基于非锁相环的算法两类。

3.2 基于PLL的时钟恢复算法:基于PLL的时钟恢复算法通过不断调整反馈环路的相位和频率,使得恢复的时钟信号与原始时钟信号同步。

3.3 基于非锁相环的时钟恢复算法:基于非锁相环的时钟恢复算法通过统计和估计传输信号的特征,恢复出准确的时钟信号。

四、性能:4.1 时钟恢复的误差和抖动:时钟恢复算法的性能可以通过误差和抖动来评估,误差指恢复的时钟信号与原始时钟信号之间的差距,抖动指时钟信号的不稳定性。

高速数字信号传输设计中的时钟数据恢复技术

高速数字信号传输设计中的时钟数据恢复技术在高速数字信号传输设计中,时钟数据恢复技术起着至关重要的作用。

当信号传输速度达到一定水平时,准确、稳定的时钟信号是保证数据传输质量的关键。

在本文中,我们将深入探讨高速数字信号传输设计中的时钟数据恢复技术。

首先,让我们了解时钟数据恢复技术的基本原理。

在数字通信中,发送端和接收端的时钟频率可能会产生偏差,导致数据传输时钟信号不同步,从而影响到数据的准确性和稳定性。

时钟数据恢复技术的主要目的就是通过在接收端重新生成一个稳定的时钟信号,以确保正确采样数据。

这种技术在高速传输中尤为重要,因为在高速传输中时钟偏差会更加明显。

时钟数据恢复技术主要有两种方法:一种是基于信号的恢复,另一种是基于时钟的恢复。

基于信号的恢复方法通过分析接收到的数据信号来提取时钟信息,然后根据这些信息生成本地时钟信号。

这种方法适用于信号质量较好的情况下,但在高噪声环境下可能会受到影响。

而基于时钟的恢复方法则是通过在数据中嵌入时钟信息,然后在接收端利用这些信息来恢复时钟信号。

这种方法对信号质量要求不高,但可能会增加数据传输的复杂性。

在实际应用中,常用的时钟数据恢复技术包括Costas环、PLL(锁相环)和CDR(时钟数据恢复器)。

Costas环是一种经典的时钟数据恢复技术,通过对接收信号的相位进行解调,提取出时钟信息并进行时钟恢复。

PLL则是一种常用的时钟同步技术,通过对输入信号进行频率和相位的比较,使得输出时钟信号与输入信号同步。

而CDR则是一种更加先进的技术,通过对接收到的数据进行采样和比较,自动调整时钟频率和相位来实现时钟数据恢复。

在设计高速数字信号传输系统时,选择合适的时钟数据恢复技术至关重要。

不同的应用场景可能需要不同的技术方案,例如对于长距离传输和高噪声环境下,CDR技术可能更适合;而对于简单的短距禁止传输,PLL可能就足够了。

在选择时钟数据恢复技术时,还需要考虑到系统的复杂度、成本和功耗等因素,以寻求最佳的平衡点。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种用于恢复数字信号中的时钟信息的技术。

在数字通信中,时钟信号的准确性对于数据的传输和解析至关重要。

CDR技术可以通过对接收到的数字信号进行采样和重构,从而恢复出准确的时钟信息,保证数据的稳定传输和正确解析。

本文将介绍CDR的原理和应用,并详细阐述其在时钟恢复、数据传输和通信系统中的重要性。

一、CDR的原理和工作方式:1.1 采样和重构:CDR通过对接收到的数字信号进行采样,即在固定的时间间隔内对信号进行取样。

采样的目的是获取信号的瞬时状态,并将其转换为离散的数字值。

接着,CDR使用这些采样值来重构时钟信号,即通过插值和滤波等技术将离散的采样值转换为连续的时钟信号。

1.2 相位锁定环路(Phase Locked Loop, PLL):PLL是CDR的核心组成部分,用于将重构的时钟信号与接收到的信号进行比较和调整,以保持两者的相位同步。

PLL通过不断调整重构时钟信号的相位,使其与接收到的信号相位保持一致,从而实现时钟数据的恢复。

1.3 时钟频率调整:CDR还可以根据接收到的信号的频率特性来调整时钟的频率。

通过对信号进行频率分析和比较,CDR可以自动调整时钟频率,以适应信号的变化,确保数据的稳定传输和正确解析。

二、CDR在时钟恢复中的应用:2.1 光纤通信系统:在光纤通信系统中,光信号在传输过程中会受到光纤的衰减和色散等影响,导致信号的失真和时钟信息的丢失。

CDR技术可以通过恢复时钟信息,减小信号失真,提高数据传输的可靠性和稳定性。

2.2 高速串行通信接口:在高速串行通信接口中,时钟信号的准确性对于数据的传输速率和可靠性至关重要。

CDR技术可以通过恢复时钟信号,使接收端能够正确解析数据并保持与发送端的同步,实现高速数据传输。

2.3 数字存储系统:在数字存储系统中,时钟信号的准确性对于数据的读取和写入至关重要。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种重要的数字通信技术,用于在高速数据传输中恢复时钟信号。

本文将介绍时钟数据恢复的基本概念、工作原理、应用领域、优势以及发展趋势。

一、基本概念1.1 时钟数据恢复是指在数字通信系统中,通过采样和重构技术,从接收到的数据流中提取出时钟信号。

1.2 时钟数据恢复通常用于高速串行通信系统,以确保数据传输的稳定性和准确性。

1.3 时钟数据恢复可以根据不同的传输标准和速率进行调整和优化,以适应不同的应用场景。

二、工作原理2.1 时钟数据恢复的工作原理主要包括信号采样、时钟提取和时钟重构三个步骤。

2.2 信号采样是通过对接收到的数据流进行采样,获取数据的波形信息。

2.3 时钟提取是从采样的数据中提取出时钟信号,以确定数据的传输速率和时序关系。

2.4 时钟重构是根据提取出的时钟信号,对接收到的数据进行重新定时,以恢复原始的时钟信号。

三、应用领域3.1 时钟数据恢复广泛应用于高速数字通信系统,如光纤通信、高速总线、数据存储等领域。

3.2 在光纤通信系统中,时钟数据恢复可以提高数据传输的稳定性和可靠性,减少误码率。

3.3 在数据存储系统中,时钟数据恢复可以确保数据的读写速度和准确性,提高系统性能和可靠性。

四、优势4.1 时钟数据恢复可以有效解决高速数据传输中时钟漂移和时钟颤动等问题,提高系统的稳定性和可靠性。

4.2 时钟数据恢复可以适应不同的传输标准和速率,具有较强的通用性和灵便性。

4.3 时钟数据恢复技术不断发展和优化,可以满足不断增长的数据传输需求和挑战。

五、发展趋势5.1 随着数字通信技术的不断发展,时钟数据恢复技术将继续向更高速、更稳定、更智能的方向发展。

5.2 时钟数据恢复技术将与其他数字通信技术相结合,实现更高效的数据传输和处理。

5.3 时钟数据恢复技术将在5G通信、物联网、人工智能等领域发挥越来越重要的作用,推动数字化社会的发展和进步。

总结:时钟数据恢复是一种重要的数字通信技术,通过采样和重构技术,可以提取出时钟信号,确保高速数据传输的稳定性和准确性。

TDM数据在IP分组网传输中的时钟恢复精灵论文

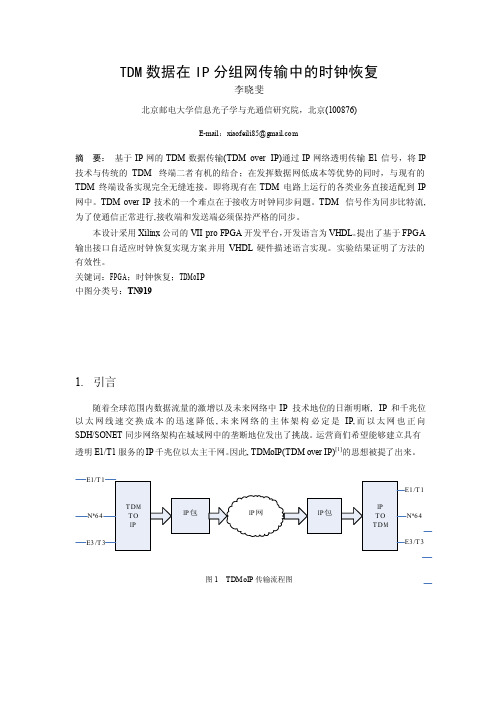

TDM 数据在IP 分组网传输中的时钟恢复李晓斐北京邮电大学信息光子学与光通信研究院,北京(100876)E-mail:*********************摘要:基于IP 网的TDM 数据传输(TDM over IP)通过IP 网络透明传输E1 信号,将IP 技术与传统的TDM 终端二者有机的结合;在发挥数据网低成本等优势的同时,与现有的TDM 终端设备实现完全无缝连接。

即将现有在TDM 电路上运行的各类业务直接适配到IP 网中。

TDM over IP 技术的一个难点在于接收方时钟同步问题。

TDM 信号作为同步比特流, 为了使通信正常进行,接收端和发送端必须保持严格的同步。

本设计采用Xilinx 公司的VII pro FPGA 开发平台,开发语言为VHDL。

提出了基于FPGA 输出接口自适应时钟恢复实现方案并用VHDL 硬件描述语言实现。

实验结果证明了方法的有效性。

关键词:FPGA;时钟恢复;TDMo IP中图分类号:TN9191. 引言随着全球范围内数据流量的激增以及未来网络中IP 技术地位的日渐明晰, IP 和千兆位以太网线速交换成本的迅速降低, 未来网络的主体架构必定是IP, 而以太网也正向SDH/SONET 同步网络架构在城域网中的垄断地位发出了挑战。

运营商们希望能够建立具有透明E1/T1 服务的IP 千兆位以太主干网。

因此, TDMoIP(TDM over IP)[1]的思想被提了出来。

N*6*64 E3/T3图1 TDMoIP 传输流程图TDMoIP 技术可以采用A TM 论坛定义的电路仿真类似的方式来封装IP 数据包中的数据单元,从而实现TDM 信号的透明传输。

加之RTP 和RTCP 实时协议的使用,保证了数据传输的质量。

利用该技术传输T1/E1 信号,不但可以提供极佳的话音质量,还可以以各种速率支持Modem、传真和视频,并保留现有的PBX 系统易于安装维护、价格低廉等特征。

54 Mb-s NRZ时钟数据恢复电路的设计与实现

2 电路系统设计

本文设计的时钟恢复电路,由锁频环路和锁相环路组成,其中还包括一个辅助的频率检测器。锁频环路和锁相环路共用一个低通滤波器和压控振荡器,其中锁频环路的性能决定了频率捕捉范围,锁相环路性能的优劣决定了恢复时钟质量。为了降低时钟的抖动影响及增强系统的稳定性,各组成模块都需要特别的设计。

3 时钟恢复电路仿真结果

对于本文设计的时钟提取电路,采用0.18 μm标准CMOS工艺实现,电源电压为1.8 V,使用Cadence软件的Spectre仿真工具仿真。时钟数据恢复电路最终的仿真波形图,图中上方波形为输入的54 Mb/s的NRZ数据信息,中间为电路提取的时钟波形,下方波形为由提取的时1”的状态下,也能够从数据中准确无误地提取出数据时钟。

图3中M17~M24组成电荷泵电路的电流源电路,M21~M24为启动电路。电流源晶体管PMOS管M8、M9和电流沉晶体管NMOS管M10、M11采用大尺寸晶体管,有效地减小了晶体管阈值电压不匹配并降低了沟道长度调制效应。同时采用了一种等效电容的电位跟踪输出电位的方法来降低电荷泵电路的电容效应对输出的影响,从而降低输出时钟的jitter效应[2],[4];在电荷泵的输出端和两个电流源之间引入由运算放大器组成的电压跟随器(由M12~M16组成)。由于B点总是跟踪A点电位,当充电放电开关M0、M1关断,M2、M3打开时,B点电位通过M2、M3将C、D点钳位,使得C、D点电位保持不变,从而保证M2、M3下次打开时不会出现瞬间大电流。C、D两点电位的稳定同时减小了M0、M1的栅极电容,缩短了M0、 M1的开启时间。由于C、D点始终受到A点电位的控制,当M0或M1开启时A点电位起伏减小,同理可以分析出E,F点也受到A点电位的控制,当M4或M5开启时A点电位起伏减小。电荷泵输出“vctrl”将变得更加平滑,压控振荡器的输出频率更加稳定,输出时钟的抖动减小。在锁定时,电荷泵各节点的电压保持恒定,而不会发生周期性充放电的情况,有效解决了电荷共享问题。图4所示为本文设计的鉴相环路电荷泵在输出电压“vctrl”变化下的充放电电流。

时钟数据恢复(CDR)

时钟数据恢复(CDR)引言概述:时钟数据恢复(CDR)是一种电子设备中常见的技术,它的主要作用是将传输过程中的时钟信号从输入数据中恢复出来。

CDR技术在通信、计算机和数据存储等领域中起着重要的作用。

本文将从四个方面详细介绍CDR技术的原理、应用、优势和未来发展。

一、CDR技术的原理1.1 时钟信号的重要性:时钟信号在数字系统中起着同步和定时的作用,是数据传输的基础。

没有准确的时钟信号,数据传输可能会出现错误。

1.2 时钟数据恢复的需求:在长距离传输、高速传输和复杂信道环境中,时钟信号可能会受到噪声、失真和抖动等干扰,导致时钟信号的丢失或变形。

1.3 CDR技术的原理:CDR技术通过采样、检测和锁定的方式,从输入数据中恢复出准确的时钟信号。

具体而言,CDR技术会对输入数据进行采样,检测采样点的时钟相位误差,并通过反馈机制调整本地时钟信号,最终实现时钟数据的恢复。

二、CDR技术的应用2.1 通信领域:CDR技术在光纤通信和高速数据传输中广泛应用。

它可以恢复出光纤通信中的时钟信号,保证数据的传输质量和可靠性。

2.2 计算机领域:CDR技术在计算机内部的总线、接口和芯片中使用。

它可以恢复出高速总线和接口中的时钟信号,确保数据的同步和稳定传输。

2.3 数据存储领域:CDR技术在硬盘驱动器和固态硬盘中起着重要的作用。

它可以恢复出存储介质中的时钟信号,确保数据的读取和写入的准确性和稳定性。

三、CDR技术的优势3.1 自适应性:CDR技术具有自适应性,可以根据输入数据的特性和环境条件自动调整时钟恢复的参数,适应不同的传输场景。

3.2 高精度:CDR技术能够实现高精度的时钟恢复,可以达到纳秒级的时钟相位误差,确保数据传输的准确性和稳定性。

3.3 抗干扰能力:CDR技术具有较强的抗干扰能力,可以有效抑制噪声、失真和抖动等干扰信号,提高数据传输的可靠性和鲁棒性。

四、CDR技术的未来发展4.1 高速传输:随着数据传输速率的不断提高,CDR技术将面临更高的挑战。

时钟数据恢复原理

时钟数据恢复原理

时钟数据恢复是一种数据恢复技术,用于恢复因时钟信号中断而丢失的数据。

在数据传输过程中,时钟信号是控制数据传输速率和同步的关键。

然而,如果时钟信号中断或不稳定,数据传输就会变得不可靠,从而导致数据丢失。

为了恢复时钟信号中断导致的数据丢失,一种常用的方法是通过插值技术来重建丢失的数据。

插值是从已知数据点中推断和填补缺失点的过程。

首先,我们需要确定时钟信号中断的时间点。

通常,我们可以通过检测数据传输速率的突然变化或数据错误来确定这些时间点。

然后,我们需要找到丢失数据之前和之后的已知数据点。

接下来,我们可以使用线性插值或其他插值算法来估计丢失数据点。

线性插值是一种简单的插值技术,它假设数据点之间的变化是线性的,并根据已知数据点的位置和值来计算丢失数据点的值。

其他插值算法,如样条插值和拉格朗日插值,可以提供更精确的估计。

一旦我们估计出丢失数据点的值,我们就可以将其填充到原始数据中,从而恢复数据的完整性。

然后,我们可以继续使用恢复后的数据进行后续分析和处理。

需要注意的是,时钟数据恢复仅能修复由时钟信号中断导致的数据丢失问题。

对于其他类型的数据丢失,例如硬盘损坏或文件删除,需要使用其他数据恢复技术进行修复。

此外,时钟数

据恢复并不能保证恢复的数据完全准确,因为插值算法本身可能存在一定的误差。

总的来说,时钟数据恢复是一种通过插值技术来恢复因时钟信号中断导致的数据丢失的过程。

它可以帮助我们恢复丢失的数据,并继续进行后续的数据处理和分析。

集成电路设计中的时钟和数据恢复技术

集成电路设计中的时钟和数据恢复技术时钟和数据恢复技术在集成电路设计中起着重要的作用。

时钟信号是控制电路各个部件协同工作的关键,而数据恢复技术则保证了在复杂电路系统中数据传输的可靠性和稳定性。

本文将详细介绍时钟和数据恢复技术在集成电路设计中的原理、应用和挑战。

一、时钟的作用和原理时钟信号在集成电路中充当一个定时器,控制电路各个部件按照特定时序进行操作。

时钟信号的频率和相位准确性对整个电路的性能和功耗都有着重要影响。

时钟信号的频率决定了电路处理能力的上限,而时钟信号的相位决定了电路操作的时序。

高频率时钟可以加快电路的运行速度,但也会增加功耗和散热。

相反,低频率时钟可以降低功耗,但会限制电路的最高工作频率。

因此,时钟的频率选择在平衡功耗和性能上是一个关键的设计考虑因素。

时钟信号通常由时钟发生器产生,发生器可以采用振荡器、频率锁定环或多级分频器等技术来保证时钟信号的质量。

在时钟设计中,需要考虑时钟稳定性、噪声、抖动和时钟切割等问题,以确保时钟信号的准确性和可靠性。

二、时钟与数据恢复技术的应用时钟和数据恢复技术在各个领域的集成电路设计中都有广泛的应用,例如通信、计算机、嵌入式系统等。

在通信领域,时钟和数据恢复技术常用于高速串行接口的设计中,例如以太网、USB、PCI Express等。

这些接口在传输数据时需要复杂的时钟沿和时序控制,时钟和数据恢复技术能够确保数据的传输稳定性和可靠性。

在计算机领域,时钟和数据恢复技术被广泛运用于处理器和内存控制器等核心器件的设计中。

时钟信号的频率和时钟相位对于处理器的性能至关重要,而数据恢复技术则用于解决高速存储器访问时的数据读取和写入问题。

在嵌入式系统中,时钟和数据恢复技术用于控制外设和内核之间的数据传输。

例如,时钟和数据恢复技术可以确保音频输出的时序和质量,同时也可以确保传感器数据的准确性和实时性。

三、时钟和数据恢复技术的挑战时钟和数据恢复技术在集成电路设计中面临着一些挑战。

时钟数据恢复电路英文文献

Clock and Data Recovery CircuitAt the output of the limiting amplifier, the amplified data signal with sharpened data edges is available for further processing, but unique interpretation of the received signal requires timing information. Serial communication links do not provide a synchronization signal on a separate channel and therefore the receiver must rely on the extraction of the timing information from the data stream. This clock and data recovery process can be performed in a similar manner in optical communication, electrical serial links, hard drive read-out channels, as well as in some memory interfaces. In the latter field, advocates and opponents of the clock forwarding scheme still debate about the advantages and drawbacks of per-channel clock recovery circuits.Proper denomination of the whole synchronization process would be clock recovery and data retiming, better describing the behaviorally independent operations. Indeed the recovered clock is used to re-sample the incoming (or sometimes delayed) data to provide proper timing information, i.e. synchronicity, for the following blocks (Figure 8.1). However, in many implementations, the retiming operation is embedded in the clock recovery part to achieve improved circuit performance .FIGURE 8.1. Clock recovery and data retiming principleThe major challenges of multichannel clock recovery circuit design have already been presented, namely, the achievement of low-power and low-area overhead with minimum impact on the circuit performance. First, an introduction to the important concepts in the design of clock recovery circuits is presented. Then, an overview of a variety of clock recovery topologies with their respective advantages and drawbacks allows the reader to fully understand the design choices operated later in this chapter. After discussion ofappropriate topologies for multichannel clock recovery, a top-down design approach is presented which validates the jitter performance of the selected topology at the concept level, at the behavioral level and at the transistor level. Finally, the transistor-level design of the CDR is briefly discussed and characterization techniques are introduced.1.Clock Recovery PrinciplesHistorically, clock recovery was performed using resonant filter-based structures, either using discrete passive elements or resonant elements like surface acoustic wave (SAW) devices. In the era of systems-on-chip, requirements for small system form factors and minimum bill of material, the use of such off-chip components is strongly discouraged. In the long-haul market, where fiber-optic communications made their breakthrough first, phase-locked loop (PLL) topologies have become the mainstream solution, thanks to their capability of monolithic integration with a minimum number of external components, typically only one loop filter capacitor.Beyond the fact that the PLL currently still dominates the field and is the most well-known clock recovery topology, we would like to use this CDR structure as a basis to the explanation of some concepts to the novice reader. A more detailed discussion of PLL-based clock recovery circuits can be found in [83]. For simplification, let us first consider a phase-locked loop with a periodic input signal (Figure 8.2). The three main building blocks are the phase detector (PD), the loop filter (LF) and the voltage-controlled oscillator (VCO). The phase detector compares the phase error between the input signal and the generated signal at the VCO output. The phase error is integrated in the low-pass loop filter and the resulting control signal tunes the VCO frequency, which in turn reduces the phase error.FIGURE 8.2. PLL with periodic input signalThe periodic input signal f(t) can be written as the sum of sine and cosine functions,namely, its Fourier series:In most high data rate applications, we can neglect the higher order harmonics and focus on the fundamental signal, which can be written as:The instantaneous value f(t) of a sine wave is defined by its peak amplitude A and its instantaneous phase (t), which can again be decomposed into a constant angular frequency w0=2πf0 and a time-varyin phase angleθ(t). In phase and frequency modulation schemes used in wireless data transmission, this time-varying phase angle contains the information to be transmitted. In fiber optic links, it does not contain any useful information, but represents the phase noise due to channel and circuit imperfections like noise and limited bandwidth.In both types of applications, the phase-locked loop technique allows to extract the time-dependent phase information and track the input signal. The in-phase output signal vout, locked to the input signal, guarantees a very small phase error φe(t) between the input phase φi(t) and the output phase φo(t)。

英语作文-揭秘集成电路设计中的时钟与数据恢复技术与应用

英语作文-揭秘集成电路设计中的时钟与数据恢复技术与应用In the realm of integrated circuit (IC) design, the interplay between clocking and data recovery techniques is pivotal. These elements form the backbone of synchronous digital systems, ensuring that data is transmitted and processed reliably and efficiently.Clocking in IC design refers to the use of a clock signal to coordinate the timing of circuit operations. This clock signal, typically generated by an oscillator, serves as a heartbeat for the system, synchronizing the activities of various components. The precision of this clock signal is crucial, as it determines the system's maximum operating speed and influences its susceptibility to timing-related errors.Data recovery, on the other hand, is the process of accurately extracting data from a noisy or distorted signal. In high-speed communication systems, data recovery circuits, often referred to as Clock and Data Recovery (CDR) circuits, are essential. They recover the timing information (clock) from the incoming data stream and use it to regenerate a clean version of the data, free from transmission-induced imperfections.The integration of clocking and data recovery technologies is especially significant in serial communication protocols such as PCI Express, USB, and SATA. These protocols rely on high-speed serial links, where data is sent one bit at a time over a single channel. The absence of a separate clock line necessitates the use of sophisticated CDR circuits to extract timing information from the serial data itself.One of the key challenges in designing CDR circuits is dealing with jitter, which is the deviation from true periodicity of a presumed periodic signal. Jitter can be introduced by a variety of sources, including thermal noise, power supply variations, and electromagnetic interference. Effective CDR circuits must be able to tolerate a certain amount of jitter while still recovering the original data accurately.Another aspect of clocking in IC design is the distribution of the clock signal throughout the chip. As ICs become more complex and operate at higher speeds, the challenge of delivering a consistent clock signal to all parts of the chip increases. Techniques such as clock tree synthesis and the use of phase-locked loops (PLLs) are employed to mitigate issues like clock skew, which is the difference in timing of the clock signal's arrival at different parts of the circuit.In conclusion, the synergy between clocking and data recovery techniques is a cornerstone of modern IC design. It enables the creation of systems that are not only fast and powerful but also resilient to the imperfections inherent in electronic communication. As technology marches forward, the evolution of these techniques will continue to be a critical area of research and development, pushing the boundaries of what is possible in the world of electronics. 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要摘要本论文主要提供了一种实用的方式从数据流中恢复时钟,并以此时钟来恢复出原始数据,并且设计产生系统自检所需的信号。

本设计基于如今已经非常成熟的FPGA技术,采用一种非常新颖的方法成功实现了从数据流中同步恢复出时钟,并且采用纯数字电路的方法,利用EDA平台设计出了恢复原始数据的译码电路,此外,本设计还实现了系统自检;设计从实际应用的角度出发,旨在解决现实生活中的车载电子设备的通信问题,切合实际,同时,对现有的时钟同步数据恢复的方法进行学习与改进。

论文涵盖了模拟电路设计,数字电路设计,硬件编程,调试,软件仿真,逻辑综合各个方面,具有很大的现实意义。

关键词:时钟数据恢复,FPGA,锁相环,状态机IABSTRACTABSTRACTThis paper aims at providing a practical method to recovery the clock transformed by the data stream, through which it can decode the original data stream and it can create the self-checking signal needed by the system.My design succeeds to recovery the clock through the data stream based on the technology of mature FPGA and I achieve to design the decoding circuit by digital circuit on the platform of EDA. The research is from the practical point of view, aiming to solve communication problems in real life in-vehicle electronic devices. Also, we learn and improve on existing methods of clock and data recovery. The design contains analogy circuit design, digital circuit design, hardware programming, debug, simulation and logical synthesis and so on.Key Words: Clock and Data Recovery, FPGA, PLL, State MachineII目录第1章引言 (1)1.1数据恢复的同步设计和系统自检的概况和发展现状 (1)1.1.1时钟数据同步恢复电路的简介 (1)1.1.2系统自检的简介 (2)1.1.3时钟数据恢复电路的发展趋势 (2)1.2时钟数据恢复电路以及系统自检的必要性和挑战 (3)1.3本课题的研究目的和研究内容 (4)1.3.1研究目的 (4)1.3.2研究内容 (5)1.3.3论文的结构安排 (6)第2章传统的时钟数据恢复电路 (7)2.1概述 (7)2.2传统的时钟数据恢复电路的方法 (8)2.2.1前馈相位跟踪型CDR (8)2.2.2反馈相位跟踪型CDR (11)第3章基于FPGA的时钟数据恢复电路 (16)3.1设计任务概述 (16)3.2各模块电路设计 (16)3.2.1毛刺消除电路的设计 (16)3.2.2时钟恢复电路的设计 (18)3.2.3译码电路的设计 (24)3.2.3.1有限状态机的介绍 (25)3.2.3.2序列检测器的设计 (26)3.2.3.3时钟数据恢复电路 (29)第4章系统自检的设计以及电路中各个时钟的设计 (31)III4.1系统自检的设计 (31)4.1.1自检信号序列发生器的设计 (31)4.2时钟数据恢复电路中的时钟 (34)4.2.1时钟数据恢复电路系统的总体电路图 (34)4.3锁相环技术 (35)4.3.1锁相环简介 (35)4.3.1.1鉴相器 (36)4.3.1.2环路滤波器 (36)4.3.1.3压控振荡器 (37)4.3.2锁相环倍频获得所需时钟信号 (37)第5章结束语 (40)参考文献 (41)致谢 (42)外文资料原文 (43)外文资料翻译 (53)IV第1章引言第1章引言在高速串行数据通信中,为了节省开销,一般只传送数据信号而不传送与数据信号同步的时钟信号。

这样,在接收端为了保证数据处理的同步,时钟等时序信息必须从数据中提取出来,继而利用该时钟对数据进行“重定时”来消除传输过程中积累的抖动,这一时钟提取和数据重定时的过程一般称为“时钟数据恢复”(CDR, Clock and Data Recovery)。

高速CDR电路是高速数字通信中一个不可或缺的关键模块,种类繁多。

传统的CDR电路包括时钟恢复(CR,Clock Recovery)电路和数据恢复(DR,Data Recovery)电路两部分,而数据恢复又可以细分为时钟数据相位调整(相位对准,phase alignment)电路[1]和数据采样判决电路。

根据数据恢复(或数据采样)时,本地时钟与数据之间的相位关系及其实现方式的不同,CDR的结构大体可以被分为三类:前馈(feed forward)相位跟踪型,反馈(feedback)相位跟踪型,以及(无相位跟踪)盲过采样(blind—oversampling)型[2]。

为了保证电路正常工作和及时发现系统故障,电路设计中大多数要设计自检电路,自检电路包括对器件工作状态,环境补偿,保护元件是否失效,修正参数等等,单片机电路还包括程序是正常执行,初始参数的自动设置,有LED显示的还要检测是否断笔,以及配合人工通过显示确定系统状态等。

系统运行过程中,各模块、各通信链路等都需要定时或根据主控制器要求进行自检。

1.1数据恢复的同步设计和系统自检的概况和发展现状1.1.1时钟数据同步恢复电路的简介数据时钟恢复电路的用途变得越来越广泛。

从无线通信到有线通信,从光接收机到硬盘的读写,都需要数据时钟恢复电路才能进行正常的数据传输和通信。

尤其是串行通信,由于数据时钟恢复电路具有节约连线资源、对信号的幅度要求小、信号之间的串扰小和传输速率高等优点,在诸如以太网、光通信和硬盘数据传输等系统中得到广泛的应用。

随着现代通信的飞速发展,用来衡量通信系统的重要1电子科技大学学士学位论文指标——传输速率,已经迈向数十吉(G)的数量级[2]。

传输速率的不断提高给终端设计带来更大的挑战,尤其使接收机终端中的关键单元——数据时钟恢复电路的设计变得越来越具有挑战性。

数据通信系统中,由于发射端电子器件的噪声、传输路径中的衰减和干扰等因素,接收端接收到的数据包含大量噪声,必须设法从这些带噪数据中提取有用的数据。

数据时钟恢复电路就是一种从带噪声数据中提取时钟信号、进而恢复出有用数据的电路。

因此,数据时钟恢复电路的性能直接影响到整个系统的质量。

超高速时钟数据恢复电路也有报道。

数据率的提高,意味着每一位数据的持续时间的降低,1Gbps的数据率相当于每一位数据的持续时间只有一个纳秒(ns),这对电路的性能以及对时钟的抖动的优化提出了更高的要求。

时钟恢复电路的结构主要针对的是2.5Gbps以上的串行信号[3],在长距离通信中,由于数据的位宽时间很短,码间干扰显著,抖动相对可观,电路主要以锁相环结构为主;而在许多短距离接口电路中,要求锁定时间很短,抖动容忍范围宽,开环结构依然有着广泛的应用。

1.1.2系统自检的简介对于完整的系统电路来说,都应该具有自检电路,随着时间的推移,系统在运行过程中难免会出现一些问题,比如在实际应用中,主机发出信号从机负责接受并且提取数据和时钟,为了保证电路正常工作和及时发现系统故障,必须要有系统自检电路的设计,包括对器件工作状态,环境保护,修正参数等。

对计算机而言,系统自检也称为POST(Power On Self Test),打开电脑,主板加电开始从BIOS引导硬件自检到BIOS选择启动项硬盘还是光驱,寻找引导文件,包括关键部位测试和非关键部位测试,加电,cpu、rom、BIOS,system clock、DMA、64k RAM、显卡。

如果有问题称为核心故障。

同理,对于任和硬件电路,都应该具有自检电路,保证其工作在正常环境中,一旦系统出现状况,就会发出故障信号,通知维修。

1.1.3时钟数据恢复电路的发展趋势时钟数据恢复电路从出现至今已经经历了多次变革,其改进的主要方面是CDR 电路结构的优化,促使CDR电路结构变化的因素主要包括工艺的变化,以及由于2第1章引言工艺水平的影响导致的电路速度和电源电压的变化,面积和功耗的影响等。

从上世纪九十年代至今,CMOS工艺水平经历了0.9um、0.6um、0.35um、0.25um、0.18um 直到90nm、65nm甚至45nm[5],可谓突飞猛进。

CDR的发展趋势:(1)各种基本CDR相互借鉴融合。

(2)多速率及连续速率变化。

一方面可以增加CDR的通用性,另一方面,可以适应有多速率或宽范围连续速率要求的场合。

(3)数字化。

对越来越多的CDR模块的数字化,可以增加电路的可靠性,可移植型,以及减小芯片面积,提高电路的集成度(如LF,CP的数字化)。

(4)亚速率化。

通过工作在亚速率,PFD/VCO等都可以工作在较低速率,功耗可以降低,最高CDR数据率可以得到提升,PFD也往往具有分接功能。

当然亚速率往往是以增加对VCO多相位的需求为代价的,这也将大大增加电路设计的复杂度,比如较严格的时钟相位差要求等。

(5)微波化。

主要在工作速率很高的场合,如采用分布式VCO产生多相位时钟,采用微带线作为延时单元等。

(6)并行化。

满足越来越多的短距离并行I/O的需求。

1.2时钟数据恢复电路以及系统自检的必要性和挑战如果接收端不进行时钟同步,而是使用自己本地的时钟,则足够长的时间后接收到的数据总会出现不可预知的重复或丢失,导致接收错误。

因此发端必须将与数据速率相关的时钟信号传输给接收端,时钟信号可以走单独的信号线,也可以用一定的方式隐含在数据信号中。

接收端对此时钟信号进行同步,从而能够“不多也不少”地从接收的数据波形中恢复数据。

另外传输过程中,数据信号多少会发生一定的畸变,时钟同步的另外一个作用是保证接收端在波形畸变最少的时刻恢复数据,减少出错概率。

随着集成电路性能不断提高和网络技术的日益发展,数据处理量和交换量越来越大,人们要求数据传输的速率越来越快,对通信带宽的要求也越来越高,数据带宽已经成为限制电路整体性能的瓶颈。