(Multisim数电仿真)半加器和全加器

实验二--组合逻辑电路实验(半加器、全加器)

掌握 验证 学会

实验目的

组合逻辑电路的功能测试

数 法半字加电器路和实全验加箱器及的示逻波辑器功的能使用方 二进制数的运算规律

实验设备

序号 名称

型号与规格 数量

1 数字电路实验箱

THD-1

1

2 二输入四与非门

74LS00

3

3 二输入四异或门

74LS86

1

4 二输入端四或非门 74LS02

1

实验内容与步骤

1. 组合逻辑电路功能测试 2.用异或门(74LS86)和与非门组成的半加

器电路 3.全加器组合电路的逻辑功能测试 4. 用与非门实现逻辑函数 F AB AC BC *5.用异或门、或非门、与非门组成的全加器

电路的逻辑功能测试(选做)

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

输出

Y1

Y2

(1)按上图接线(注意数字编号与芯片管脚编号对应) (2)写出Y2的逻辑表达式并化简。 (3)图中A、B、C接实验箱下方的逻辑开关,Y1,Y2接实验箱上方的电平显示发光管。 (4)按表格要求,拨动开关,改变A、B、C输入的状态,填表写出Y1,Y2的输出状态。 (5)将运算结果与实验结果进行比较 。

5、记录实验结果(二)

2.用异或门(74LS86)和与非门(74LS00)组成的半加器电路

输入

A

B

0

0

0

1

1

0

1

1

输出

Y

Z

(1)在数字电路实验箱上插入异或门和与非门芯片。输入端A、B接逻辑开 关,Y,Z接电平显示发光管。 (2)按表格要求,拨动开关,改变A、B输入的状态,填表写出y、z的输出 状态,并根据真值表写出y、z逻辑表达式。

数电实验报告半加全加器

数电实验报告半加全加器实验目的:掌握半加器和全加器的原理和应用,了解半加器和全加器的构造和工作原理。

实验器材:逻辑电路实验箱、7400四与非门、7402四与非门、7408四与门、7432四或门、7447数码显示器、开关、电源、跳线等。

实验原理:半加器和全加器是数字电路中常用的基本逻辑电路,用于对二进制进行加法运算,主要用于数字电路中的算术逻辑单元(ALU)。

1.半加器实验原理:半加器是一种能够对两个二进制位进行加法运算的电路。

半加器有两个输入端和两个输出端,输入端分别为A和B,输出端分别为S和C。

其中,A和B分别为要加的两个二进制数位,S为运算结果的个位,并且用S=A⊕B表示;C为运算结果的十位(进位),C=A·B表示。

半加器的真值表和逻辑符号表达式如下:```A,B,S,C0,0,0,00,1,1,01,0,1,01,1,0,1```2.全加器实验原理:全加器是一种能够对两个二进制位和一个进位信号进行加法运算的电路。

全加器有三个输入端和两个输出端,输入端分别为A、B和Cin,输出端分别为S和Cout。

其中,A和B分别为要加的两个二进制数位,Cin 为上一位的进位信号,S为运算结果的个位,并且用S=A ⊕ B ⊕ Cin表示;Cout为运算结果的十位(进位),Cout=(A·B) + (A·Cin) + (B·Cin)表示。

全加器的真值表和逻辑符号表达式如下:```A ,B , Cin , S , Cout0,0,0,0,00,0,1,1,00,1,0,1,00,1,1,0,11,0,0,1,01,0,1,0,11,1,0,0,11,1,1,1,1```实验步骤:1.首先,按照实验原理连接逻辑门实验箱中的电路。

将7400四与非门的1、2号引脚分别连接到开关1、2上,将开关3连接到7400的3号引脚,将开关4连接到7400的5号引脚,将7400的6号引脚连接到LED1上,表示半加器的进位输出。

实验二--组合逻辑电路实验(半加器、全加器)

掌握 验证 学会

实验目的

组合逻辑电路的功能测试

数 法半字加电器路和实全验加箱器及的示逻波辑器功的能使用方 二进制数的运算规律

实验设备

序号 名称

型号与规格 数量

1 数字电路实验箱

THD-1

1

2 二输入四与非门

74LS00

3

3 二输入四异或门

74LS86

5、记录实验结果(三)

3.全加器组合电路的逻辑功能测试

Ai

Bi

Ci-1

Y

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Z

X1

X2

X3

Si

Ci

5、记录实验结果(四)

F AB AC BC

自己设计实现逻辑函数,给出逻辑电路连接图,并连接调ቤተ መጻሕፍቲ ባይዱ。

5、记录实验结果(选做)

(1)画出用异或门、或非门和与非门实现全加器的逻辑电路图,写出逻辑表达式。 (2)找出异或门、或非门和与非门器件,按自己设计画出的电路图接线,注意:接 线时,或非门中不用的输入端应该接地。与非门中不用的输入端应该接VCC。 (3)当输入端Ai Bi Ci-1为下列情况时,测量Si和Ci的逻辑状态并填入表格中

实验步骤

1、检查芯片完好

每个小组在数字电路试验箱上找到本次实验所需要的芯片 ,并查看芯片形状是否完好,芯片管脚有没有插牢。

2、查看数字电路实验箱

74LS86

74LS00

3、了解芯片

实验二 组合逻辑电路实验(半加器、全加器) PPT

5、记录实验结果(三)

3.全加器组合电路的逻辑功能测试

5、记录实验结果(四)

FABACBC

自己设计实现逻辑函数,给出逻辑电路连接图,并连接调试。

5、记录实验结果(选做)

(1)画出用异或门、或非门和与非门实现全加器的逻辑电路图,写出逻辑表达式。 (2)找出异或门、或非门和与非门器件,按自己设计画出的电路图接线,注意:接 线时,或非门中不用的输入端应该接地。与非门中不用的输入端应该接VCC。 (3)当输入端Ai Bi Ci-1为下列情况时,测量Si和Ci的逻辑状态并填入表格中

电路的逻辑功能测试(选做)

实验步骤

1、检查芯片完好

每个小组在数字电路试验箱上找到本次实验所需要的芯片 ,并查看芯片形状是否完好,芯片管脚有没有插牢。

2、查看数字电路实验箱

74LS86

74LS00

3、了解芯片

芯片管脚示意图

4、实验内容与结果(一)

1.组合逻辑电路功能测试 (选用芯片74LS00)

(1)按上图接线(注意数字编号与芯片管脚编号对应) (2)写出Y2的逻辑表达式并化简。 (3)图中A、B、C接实验箱下方的逻辑开关,Y1,Y2接实验箱上方的电平显示发光管。 (4)按表格要求,拨动开关,改变A、B、C输入的状态,填表写出Y1,Y2的输出状态。 (5)将运算结果与实验结果进行比较 。

5、记录实验结果(二)

2.用异或门(74LS86)和与非门(74LS00)组成的半加器电路

(1)在数字电路实验箱上插入异或门和与非门芯片。输入端A、B接逻辑开 关,Y,Z接电平显示发光管。 (2)按表格要求,拨动开关,改变A、B输入的状态,填表写出y、z的输出 状态,并根据真值表写出y、z逻辑表达式。

实验一 半加器全加器的设计

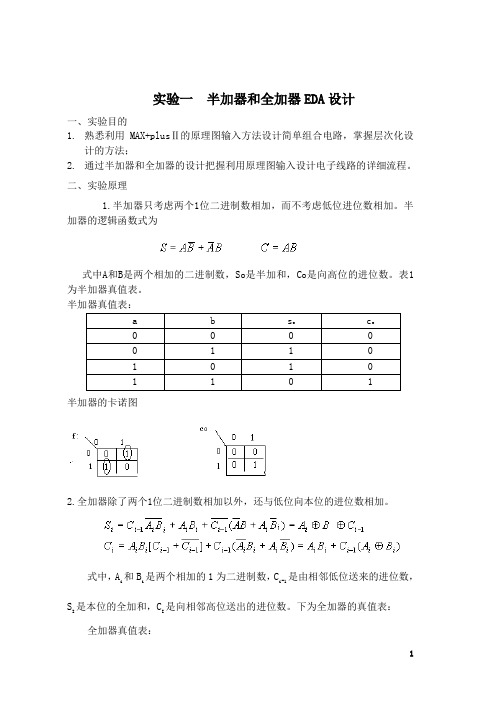

实验一半加器和全加器EDA设计一、实验目的1.熟悉利用MAX+plusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法;2.通过半加器和全加器的设计把握利用原理图输入设计电子线路的详细流程。

二、实验原理1.半加器只考虑两个1位二进制数相加,而不考虑低位进位数相加。

半加器的逻辑函数式为式中A和B是两个相加的二进制数,So是半加和,Co是向高位的进位数。

表1为半加器真值表。

半加器真值表:a b so c o0 0 0 00 1 1 01 0 1 01 1 0 1半加器的卡诺图2.全加器除了两个1位二进制数相加以外,还与低位向本位的进位数相加。

式中,Ai 和Bi是两个相加的1为二进制数,Ci-1是由相邻低位送来的进位数,S I 是本位的全加和,CI是向相邻高位送出的进位数。

下为全加器的真值表:全加器真值表:a b Cf co10 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1全加器的卡诺图四、实验内容和步骤1.(1)打开MUXPLUS错误!未找到引用源。

,选择”File”→”New”,在弹出的”New”对话框中选择”File Type”中为原理图编辑输入项”Graghic Editor file”,按”OK”后将打开原理图输入编辑窗。

(2)在原理图编辑窗中的任何一个位置右击鼠标,将快捷菜单,选择其中的输入元件项”Enter Symbol”。

(3)用鼠标双击元件库”Libraries”中的c:\muxplus2\max2lib\prim项(假设Muxplus2安装在C盘)。

在”Symbol Files”窗口即可看到基本逻辑元件库prim中的所有元件。

为了设计半加器,分别调入元件and2,not,xnor,input和output并连接好。

如图8-3,8-4所示。

然后分别在input和output的PINNAME 上双击使其变黑色,再用键盘分别输入各引脚名:a,b,co,so。

数字电子技术 实验7 半加器、全加器、数据选择器、分配器及其应用

教学时间:年月日第周星期节授课班级:本次课课时: 2 总第70节教学内容(课题):实验7 半加器、全加器、数据选择器、分配器及其应用教学目标:1.掌握中规模集成电路数据选择器的工作原理及逻辑功能。

2.熟悉利用译码器或者数据选择器构成任意逻辑函数的方法。

3.验证加法器的功能。

4.验证分配器的功能。

教学重点:数据选择器的应用。

教学难点:加法器和分配器的验证。

教学方法:课堂讲授教具及其他教学材料:多媒体课件、TAFE教材教学过程设计:复习并导入新课:问题:1.用译码器实现逻辑函数的方法是什么?2.用数据选择器实现逻辑函数的方法是什么?3.半加器和全加器的原理是什么?● 事先给学生的预习材料:实验课题:实验七 半加器、全加器、数据选择器、分配器及其应用一、实验目的:1、掌握中规模集成电路数据选择器的工作原理及逻辑功能。

2、熟悉利用译码器或者数据选择器构成任意逻辑函数的方法。

3、熟悉加法器、分配器的特点和应用。

二、实验原理电路:同学预习实验时自己画出。

三、实验设备及器件:数字逻辑电路实验箱1个。

74LS138 3-8线译码器1片,74LS151 8选1数据选择器1片。

74LS20 7-1所示。

(a )(c )74LS138 图7-1 集成电路引脚图四、实验测试电路由集成电路引脚图结合原理图,由同学自己画出。

五、实验内容与步骤1、用译码器实现函数F=AB+BC 。

参照原理图和测试电路图搭接电路,并观察电路的功能。

2、用数据选择器实现函数F=AB+C 。

参照原理图和测试电路图搭接电路,并观察电路的功能。

3、选做:用译码器74LS138实现全加器。

4、选做:用8选1数据选择器实现函数 F=ABC+D 。

六、实验注意事项:1、注意集成电路输入控制端和输出控制端的信号;2、74LS138集成块搭接中注意输出信号的处理;3、74LS20使用时注意NC 端的处理。

七、实验结论:● 新课讲解:1、用译码器实现函数F=AB+B C 。

(Multisim数电仿真)半加器和全加器教学总结

(M u l t i s i m数电仿真)半加器和全加器实验3.5 半加器和全加器一、实验目的:1.学会用电子仿真软件Multisim7进行半加器和全加器仿真实验。

2.学会用逻辑分析仪观察全加器波形:3.分析二进制数的运算规律。

4. 掌握组合电路的分析和设计方法。

5.验证全加器的逻辑功能。

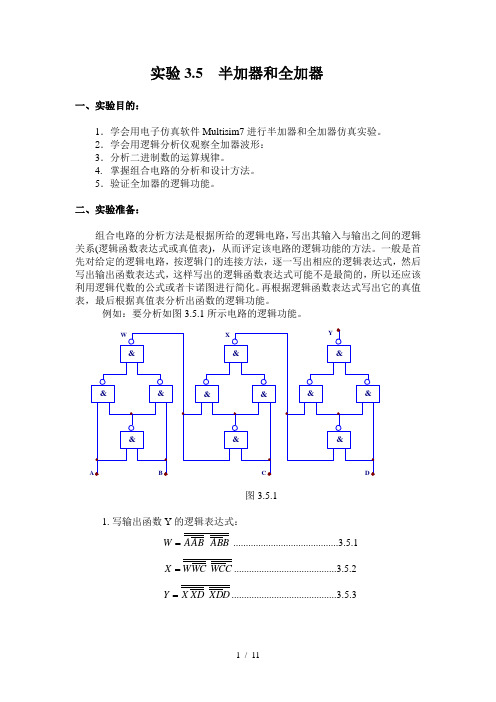

二、实验准备:组合电路的分析方法是根据所给的逻辑电路,写出其输入与输出之间的逻辑关系(逻辑函数表达式或真值表),从而评定该电路的逻辑功能的方法。

一般是首先对给定的逻辑电路,按逻辑门的连接方法,逐一写出相应的逻辑表达式,然后写出输出函数表达式,这样写出的逻辑函数表达式可能不是最简的,所以还应该利用逻辑代数的公式或者卡诺图进行简化。

再根据逻辑函数表达式例Array如:要分析如图3.5.1所示电路的逻辑功能。

图3.5.11.写输出函数Y的逻辑表达式:W=..........................................3.5.1AABBABWWCX=.........................................3.5.2WCCXXDY=..........................................3.5.3DXD2.进行化简:W+=A=....................................................3.5.4 AB+BABBABAWCWC+=....................…..3.5.5=++X+ACABCACBBCABDCCBBYXDDXDAA+=++A++=DBCDABCCDB+...........................…...3.5.6A+A+CABDBCDCDBA3. 列真值表:表3.5.1:4.功能说明:逻辑图是一个检奇电路。

输入变量的取值中,有奇数个1 则有输出,否则无输出。

组合电路的设计目的就是根据实际的逻辑问题,通过写出它的真值表和逻辑函数表达式,最终找到实现这个逻辑电路的器件,将它们组成最简单的逻辑电路。

运算电路(半加器、全加器)实验

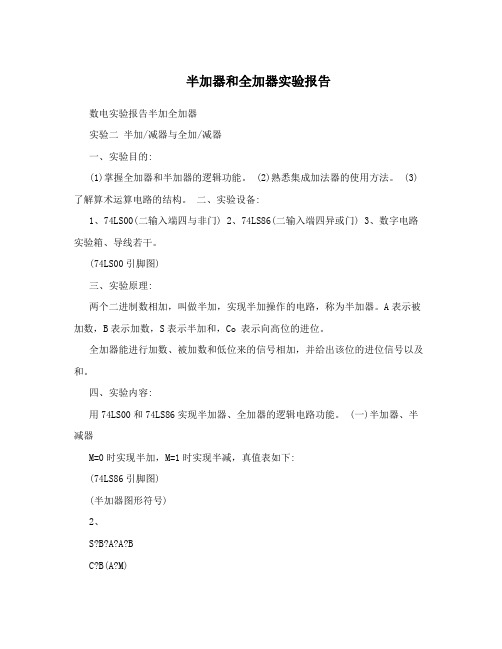

实验三运算电路(半加器、全加器及逻辑运算)一、实验目的1、掌握组合逻辑电路的功能测试。

2、验证半加器全加器的逻辑功能。

3、学会二进制的运算规律。

二、实验仪器及器件1、元器件:74LS00 二输入端四与非门 3 片74LS86 二输入端四异或门 1 片三、预习要求1、预习组合逻辑电路的分析方法;2、预习用与非门和异或门构成的半加器、全加器的工作原理;3、预习二进制数的运算。

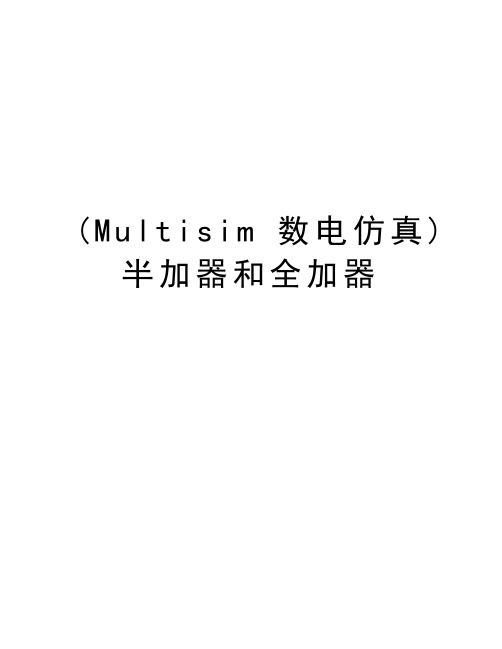

四、实验内容1、组合逻辑电路功能测试⑴用2 片74LS00 组成图3.1 所示逻辑电路。

为了便于接线和检查,按图中注明的芯片编号及引脚对应的标号接线。

⑵图中A、B、C 接电平开关,Y1、Y2 接发光管电平显示。

⑶按表3.1 要求,改变A、B、C 的状态填表并写出Y1、Y2 的逻辑表达式。

⑷比较逻辑表达式运算结果与实验是否一致。

2、测试用异或门(74LS86)和与非门组成的半加器的逻辑功能根据半加器的逻辑表达式可知,半加器Y 是A、B 的异或,而进位Z 是A、B 相与,故半加器可用一个集成异或门和二个与非门组成如图3.2。

⑴在实验箱上用异或门和与非门接成以上电路。

A、B 接电平开关、Y、Z 接电平显示。

⑵按表3.2 要求改变A、B 状态,将实验结果填表。

3、测试全加器的逻辑功能。

⑴写出图3.3 电路的逻辑表达式;⑵根据逻辑表达式列出真值表;⑶根据真值表画出函数Si、Ci 的卡诺图。

Y = A’B+AB’Z =C X1 =A’B+C’+ABX2 =A’B’+AB+C X3 =A’B+AB’+C’S i =A’B’C+A’BC’+AB’C+ABCC i =AC+AB+BC⑷填写表3.3 各点状态。

⑸按照原理图选择与非门,接线进行测试。

将结果记录在表3.4 中,并与表3.3 数据进行比较,看逻辑功能是否一致。

4、测试用异或、与或和非门组成的全加器的逻辑功能⑴画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出逻辑表达式。

⑵用上述三块逻辑电路器件按自己画出接线图。

数字电路实验Multisim仿真完整版

数字电路实验M u l t i s i m仿真HEN system office room 【HEN16H-HENS2AHENS8Q8-HENH1688】实验一逻辑门电路一、与非门逻辑功能的测试74LS20(双四输入与非门)仿真结果二、门)三、与或非门逻辑功能的测试四、现路;一、分析半加器的逻辑功能二.74LS138接成四线-十六线译码器 00000001011110001111(2)用一片74LS153接成两位四选一数据选择器; (3)用一片74LS153一片74LS00和接成一位全加器(1)设计一个有A 、B 、C 三位代码输入的密码锁(假设密码是011),当输入密码正确时,锁被打开(Y 1=1),如果密码不符,电路发出报警信号(Y 2=1)。

以上四个小设计任做一个,多做不限。

还可以用门电路搭建实验三 触发器及触发器之间的转换1. D 触发器逻辑功能的测试(上升沿)2. JK 触发器功能测试(下降沿)Q=0Q=0略3. 思考题:(1)(2)(3)略实验四寄存器与计数器1.右移寄存器(74ls74 为上升沿有效)位异步二进制加法,减法计数器(74LS112 下降沿有效)也可以不加数码显示管3.设计性试验(1)74LS160设计7进制计数器(74LS160 是上升沿有效,且异步清零,同步置数)若采用异步清零:若采用同步置数:(2)74LS160设计7进制计数器略(3)24进制83进制注意:用74LS160与74LS197、74LS191是完全不一样的实验五 555定时器及其应用1.施密特触发器输入电压从零开始增加:输入电压从5V开始减小:2.单稳态触发器3.多谢振荡。

实验名称:组合逻辑电路(半加器全加器及逻辑运算)

实验名称:组合逻辑电路(半加器全加器及逻辑运算) 一、 实验目的1. 掌握组合逻辑电路的功能测试2. 验证半加器和全加器的逻辑功能3. 学会二进制数的运算规律二、 实验仪器及材料器件 74LS00 二输入端四与非门 3片 74LS86 二输入端四异或门 1片74LS54 四组输入与或非门 1片 三、实验内容1. 组合逻辑电路功能测试(1) 用2片74LS00组成如图逻辑电路。

为便于接线和检查,需要标明芯片及各引脚编号。

(2) 图中A 、B 、C 接电平开关,Y 1、Y 2接发光管电平显示。

(3) 按表要求,改变电平开关填表并写出Y 1、Y 2逻辑表达式。

1Y A AB =+ 2Y A B B C=+(4)将运算结果与实验比较经检验,结果一致2.测试用异或门和与非门组成的半加器的逻辑功能根据半加器的逻辑表达式可知,半加器是A、B异或,而进位是A、B相与。

故半加器电路图可如图所示(1)在数字电路模拟实验箱上连接如图电路,A、B接电平开关,Y、Z 接电平显示。

(2)按表要求改变电平状态,填表3. 测试全加器的逻辑功能(1) 写出如图电路的逻辑表达式Y A B =⊕ i 1Z C -= 1i -1X C =⋅⊕(A B )2X A B =⊕ 3()X C C A B =+⊕i i 11()i S A B C A B C --=⊕⋅+⊕1()i i C AB C A B -=+⊕(2) 根据逻辑表达式列真值表(3) 根据真值表画逻辑函数的Si 、Ci 卡诺图(4) 填写表各点状态(5) 按原理图选择与非门进行接线测试,将结果填入下表,与上表比较看逻辑功能是否一致。

4. 测试用异或门、与或门和非门组成的全加器逻辑功能全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或非门和一个与非门实现。

(1) 画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出逻辑表达式。

i S A B C =⊕⊕ ()i i C AB A B C =+⊕⋅(2)找出异或门、与或非门和与门器件按自己画出的图接线,接线时注意与或非门中不用的与门输入端接地。

组合半加器、全加器及乘法器电路的设计

组合半加器、全加器及乘法器电路的设计一、实验目的(1)熟悉组合逻辑电路的特点及一般分析方法。

(2)学习组合半加器电路的功能及测试。

(3)学习组合全加器电路的功能及测试。

(4)学习两位组合乘法器电路的功能及测试。

(5)学习反相器、与门、或非门等集成电路的检测。

(6)提高学生实际动手操作能力。

(7)提高学生检查及排除电路故障的能力。

(8)增强学生组合逻辑电路的综合设计和分析能力。

二、实验器材虚拟实验设备操作系统为Windows XP的计算机 1台Electronics Workbench Multisim 8.x〜9.x 电子线路仿真软件 1 套直流电源V CC 1个逻辑探头4个逻辑开关4个逻辑分析仪1个逻辑转换器1个字信号发生器1个电阻(1K Q, 1/4W) 4 个六反相器2个二输入端四与门3个二输入端四或门2个二输入端四异或门1个实际工程实验设备数字系统综合实验箱1台数字万用表1台六反相器2个二输入端四与门3个二输入端四或门2个二输入端四异或门1个三、实验原理及实验电路组合逻辑电路的一般设计步骤:根据设计任务和要求列出该电路的真值表,利用卡诺图等方法从真值表中得到电路输入与输出的逻辑函数(即电路输入与输出的逻辑表达式)。

根据给定实验的元器件,从而得出组合逻辑电路。

二输入端异或门XOR2的逻辑函数为Y=A B + A B,其特点是“相同输出0,相反输出1”。

二输入端或门OR的逻辑函数为Y=A+B,即两个输入端只要有一个输入端为“1”,输出即为“1”,只有两个输入端同时输入为“0”,输出才为“0”。

半加器有两个输入端,即被加数A和加数B;两个输出端,即A、B 之和数S以及进位C。

这里用二输入端四异或门74LS86 一块以及二输入端四与门74LS08 一块组成半加器。

表9-1为组合半加器的真值表。

表9-1组合半加器电路真值表组合全加器电路有三个输入端,即被加数A,加数B,低位向本位的进位数C0;两个输出端即A、B、C0之和数S以及进位C。

半加器和全加器实验报告

半加器和全加器实验报告数电实验报告半加全加器实验二半加/减器与全加/减器一、实验目的:(1)掌握全加器和半加器的逻辑功能。

(2)熟悉集成加法器的使用方法。

(3)了解算术运算电路的结构。

二、实验设备:1、74LS00(二输入端四与非门)2、74LS86(二输入端四异或门)3、数字电路实验箱、导线若干。

(74LS00引脚图)三、实验原理:两个二进制数相加,叫做半加,实现半加操作的电路,称为半加器。

A表示被加数,B表示加数,S表示半加和,Co 表示向高位的进位。

全加器能进行加数、被加数和低位来的信号相加,并给出该位的进位信号以及和。

四、实验内容:用74LS00和74LS86实现半加器、全加器的逻辑电路功能。

(一)半加器、半减器M=0时实现半加,M=1时实现半减,真值表如下:(74LS86引脚图)(半加器图形符号)2、S?B?A?A?BC?B(A?M)(二)全加器、全减器S?A?B?Ci-1Ci?BCi-1?(M?A)(B?C)五、实验结果半加器:S?B?A?A?B C?B(A?M)全加器:S?A?B?Ci-1Ci?C1M?C2M其中C1?(A?B)Ci?1?AB,C2?(AB)Ci?1?AB为了方便,以下Ci?1用C表示CI?(AB?AB)CM?(AB?AB)CM?ABM?ABM?ABCM?ABCM?ABCM?ABCM?ABM?ABM?ABCM?ABCM?ABCM?ABCM?(ABCM?ABCM?ABCM?ABCM ?BC?ABCM?ABCM?ABCM?ABCM?(M?A)(B?C)(BC)则Ci?BCi-1?(M?A)(B?C)六、心得体会本次实验做的是半加/减器和全加/减器两个电路,比上次实验复杂很多,因此充满了挑战性。

实验过程中,我认识到了在利用给定的电子元件进行实验设计来实现某一种或多种功能时,对电路的化简非常重要,而且要符合给定元件的限定条件,只有将电路化简成为能够与给定元件相符的情况下才能达到实验目的。

(Multisim数电仿真)半加器和全加器

实验3.5 半加器和全加器一、实验目的:1.学会用电子仿真软件Multisim7进行半加器和全加器仿真实验。

2.学会用逻辑分析仪观察全加器波形:3.分析二进制数的运算规律。

4. 掌握组合电路的分析和设计方法。

5.验证全加器的逻辑功能。

二、实验准备:组合电路的分析方法是根据所给的逻辑电路,写出其输入与输出之间的逻辑关系(逻辑函数表达式或真值表),从而评定该电路的逻辑功能的方法。

一般是首先对给定的逻辑电路,按逻辑门的连接方法,逐一写出相应的逻辑表达式,然后写出输出函数表达式,这样写出的逻辑函数表达式可能不是最简的,所以还应该利用逻辑代数的公式或者卡诺图进行简化。

再根据逻辑函数表达式写出它的真值W=..........................................3.5.1ABABABWCX=.........................................3.5.2WWCCXY=..........................................3.5.3XDDXD2.进行化简:AW+=....................................................3.5.4AB=+BABBAABX+WCW+=....................…..3.5.5C+=+ABCABCCABBCACDBBAXCYDXDAD+=++D++=DBCAABCCDB+...........................…...3.5.6A+A+BCDCDAABCDB3. 列真值表:4.功能说明:逻辑图是一个检奇电路。

输入变量的取值中,有奇数个 1 则有输出,否则无输出。

组合电路的设计目的就是根据实际的逻辑问题,通过写出它的真值表和逻辑函数表达式,最终找到实现这个逻辑电路的器件,将它们组成最简单的逻辑电路。

例如:设计半加器逻辑电路。

1. 进行逻辑抽象:如果不考虑的来自低位的进位将两个1位二进制数相加,称为半加。

实验二组合逻辑电路实验(半加器、全加器)

2、查看数字电路实验箱

74LS86

74LS00

3、了解芯片

芯片管脚示意图

4、实验内容与结果(一)

1.组合逻辑电路功能测试 (选用芯片74LS00)

No Image

输入

A

B

C

0

0

0

0

0

1

0

1

0

0

1

1

1

输入

Ai

Bi

Ci-1

0

0

0

输出

Si

Ci

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

认真复习,加强练习, 巩固成果,学以致用!

Goodbye!

5、记录实验结果(二)

2.用异或门(74LS86)和与非门(74LS00)组成的半加器电路

输入

A

B

0

0

0

1

1

0

1

1

输出

Y

Z

(1)在数字电路实验箱上插入异或门和与非门芯片。输入端A、B接逻辑开 关,Y,Z接电平显示发光管。 (2)按表格要求,拨动开关,改变A、B输入的状态,填表写出y、z的输出 状态,并根据真值表写出y、z逻辑表达式。

1 实验目的 2 实验设备 3 实验内容与步骤

掌握 验证 学会

实验目的

组合逻辑电路的功能测试

数 法半字加电器路和实全验加箱器及的示逻波辑器功的能使用方 二进制数的运算规律

实验二半加器全加器

进位输出。

全加器的实现方式

01

全加器可以通过逻辑门电路实现,如与门、或门和 非门等。

02

具体实现方式可以根据实际需求选择不同的逻辑门 组合,以实现全加器的功能。

03

全加器在计算机中广泛应用于二进制数的加法运算 和进位处理。

04

实验步骤

设计半加器和全加器

确定输入和输出

半加器有2个输入和3个输出,全加器有3个输入和2个输 出。

结果分析

半加器分析

半加器的原理是通过异或门和与门实现两个 一位二进制数的加法运算,不考虑进位的情 况。通过实验结果可以看出,半加器能够正 确地实现两个一位二进制数的加法运算,并 输出正确的和以及进位。

全加器分析

全加器的原理是通过异或门、与门和一位全 加器实现两个一位二进制数的加法运算,同 时考虑进位的情况。通过实验结果可以看出, 全加器能够正确地实现两个一位二进制数的 加法运算,并输出正确的和、进位以及溢出。

将进位传递给下一位。

如果被加数的某一位与加数 的对应位相加结果为1,且低 位进位输入也为1,则相应的 低位进位输出端会输出1,表 示需要将进位传递给下一位。

全加器的实现方式

全加器可以通过逻辑门电路 实现,如AND门、OR门和 NOT门。

OR门用于处理被加数和加数 的对应位相加结果为1的情况。

AND门用于处理被加数和加 数的对应位相加结果为0的情 况。

检查电路功能

通过输入不同的二进制数,检查电路是否能够正确实现半加器和全加器的功能。

进行二进制数的加法运算

选择要加的二进制数

选择两个一位或两位的二进制 数进行加法运算。

输入二进制数

将选择的二进制数输入到半加 器或全加器中。

观察输出结果

实验二--组合逻辑电路实验(半加器、全加器)

5、记录实验结果(三)

3.全加器组合电路的逻辑功能测试

Ai

Bi

Ci-1

Y

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Z

X1

X2

X3

Si

Ci

5、记录实验结果(四)

F AB AC BC

自己设计实现逻辑函数,给出逻辑电路连接图,并连接调试。

5、记录实验结果(选做)

(1)画出用异或门、或非门和与非门实现全加器的逻辑电路图,写出逻辑表达式。 (2)找出异或门、或非门和与非门器件,按自己设计画出的电路图接线,注意:接 线时,或非门中不用的输入端应该接地。与非门中不用的输入端应该接VCC。 (3)当输入端Ai Bi Ci-1为下列情况时,测量Si和Ci的逻辑状态并填入表格中

输入

Ai

Bi

Ci-1

0

0

0

输出

Si

Ci

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

认真复习,加强练习, 巩固成果,学以致用!

Goodbye!

以上有不当之处,请大家给与批评指正, 谢谢大家!

实验步骤

1、检查芯片完好

每个小组在数字电路试验箱上找到本次实验所需要的芯片 ,并查看芯片形状是否完好,芯片管脚有没有插牢。

2、查看数字电路实验箱

74LS86

数电实验报告二组合逻辑电路(半加器`全加器及逻辑运算)

一、实验目的

1、掌握组合逻辑电路的功能测试。

2、验证半加器和全加器的逻辑功能。

3、学会二进制数的运算规律。

二、实验元器件

数电实验箱、集成芯片(74LS00、74LS10、74LS54、74LS86)、导线。

三、实验内容

1、组合逻辑功能路功能测试。

用两片74LS00组成图2-3

A

A

B

A

A

B

A

Y+

=

⋅

=

1C

B

B

A

C

B

B

A

Y+

=

⋅

=

2

2、测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

用一片(74LS86)和(74LS00)组成半加器。

数电实验报告二

组合逻辑电路(半加器、全加器及逻辑运算)

Vcc

A B

3、

S

CO

CO

A B

C

4、设计性实验

设计一个“一致电路”。

电路有三个输入端,一个输出端。

当三个输入端变量A、B、C状态一致时,输出F为“1”;当三个变量状态不一致时,输出F为“0”。

(要求:用与非门组成电路。

)

步骤:

i.列真值表:(右图)

ii.写出逻辑表达式:

()()

ABC

C

B

A

F⋅

=

iii.画逻辑电路图:(下图)

A

B

C

F

iv.按下图连接实验电路。

(下图)

A B。

数电实验报告-半加半减器,全加全减器

S A B Ci

Co 的卡诺图

-3-

Co BCi (Ci B)(M A) 四、实验结果

半加器半减器的电路实现如图所示:

-4-

(74LS00 引脚图)

(74LS86LS86 实现半加器、全加器的逻辑电路功能。

(一)半加器、半减器 M=0 时为半加,M=1 时为半减,真值表如下:

-1-

2、半加器、半减器卡诺图:

-2-

(二)全加器、全减器 M=0 表示全加,M=1 表示全减

数字电子技术实验报告

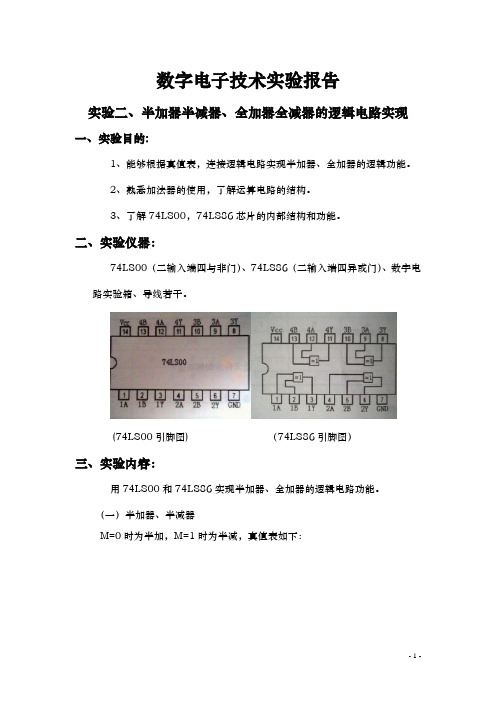

实验二、半加器半减器、全加器全减器的逻辑电路实现

一、实验目的:

1、能够根据真值表,连接逻辑电路实现半加器、全加器的逻辑功能。 2、熟悉加法器的使用,了解运算电路的结构。 3、了解 74LS00,74LS86 芯片的内部结构和功能。

二、实验仪器:

74LS00(二输入端四与非门)、74LS86(二输入端四异或门)、数字电 路实验箱、导线若干。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验3.5半加器和全加器、实验目的:1. 学会用电子仿真软件Multisim7进行半加器和全加器仿真实验。

2 •学会用逻辑分析仪观察全加器波形:3. 分析二进制数的运算规律。

4. 掌握组合电路的分析和设计方法。

5. 验证全加器的逻辑功能。

、实验准备:组合电路的分析方法是根据所给的逻辑电路,写出其输入与输出之间的逻辑关系(逻辑函数表达式或真值表),从而评定该电路的逻辑功能的方法。

一般是首先对给定的逻辑电路,按逻辑门的连接方法,逐一写出相应的逻辑表达式,然后写出输出函数表达式,这样写出的逻辑函数表达式可能不是最简的,所以还应该利用逻辑代数的公式或者卡诺图进行简化。

再根据逻辑函数表达式写出它的真值表,最后根据真值表分析出函数的逻辑功能。

例如:要分析如图3.5.1所示电路的逻辑功能。

图3.5.11. 写输出函数丫的逻辑表达式:W 二AAB ABB ......................................... 3.5.1X =WWC WCC ....................................... 3.5.2丫= XXD XDD ........................................ 3.5.32. 进行化简:W = AAB ABB 二AB AB ................................................................... 3.5.4X =WC Wc 二 ABC ABC ABC ABC ............................................... 5.5 …..3.Y =XD X D 二A BCD ABCD ABCD ABCD逻辑图是一个检奇电路。

输入变量的取值中,有奇数个 1则有输出,否则 无输出。

组合电路的设计目的就是根据实际的逻辑问题,通过写出它的真值表和逻辑 函数表达式,最终找到实现这个逻辑电路的器件,将它们组成最简单的逻辑电路。

例如:设计半加器逻辑电路。

1.进行逻辑抽象:如果不考虑的来自低位的进位将两个 1位二进制数相加,称为半加。

设 A 、 B 是两个加数,S 是它们的和,Ci 是向高位的进位。

贝肪艮据二进制数相加的规 律,可以写出它们的真值表如表 3.5.2所示。

3.列真值表:表 3.5.1: AB C D Y 0 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 1 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 0 1 1111..3.5.6ABCD A BCD ABCD ABCD ................................4.功能说明:表3.5.2:2.写出逻辑函数式:S = A B + AB = A ㊉B _丿 .............................................. 3.5.7。

=AB3. 选定器件的类型:可选异或门来实现半加和;可选两片与非门(或一片与门)实现向高位的进位。

如图3.5.2所示。

图 3.5.2、计算机仿真实验内容:1.测试用异或门、与门组成的半加器的逻辑功能:(1).按照图3.5.3所示,从电子仿真软件Multisim7基本界面左侧左列真实元件工具条中调出所需元件:其中,异或门74LS86N从“TTL”库中调出;与门4081BD_5V从“CMOS ”库中调出。

指示灯从电子仿真软件Multisim7基本界面左侧右列虚拟元件库中调出,X1选红灯;X2选蓝灯。

图 3.5.3(2) .打开仿真开关,根据表3.5.3改变输入数据进行实验,并将结果填入表 内。

表 3.5.3:输入 输 出 A B SCi0 00 11112. 测试全加器的逻辑功能:(1).从电子仿真软件Multisim7基本界面左侧左列真实元件工具条中 CMOS ”库中调出或门4071BD_5V 、与门4081BD_5V ;从“TTL ”库中调出zz异或门74LS86D ,组成仿真电路如图3.5.4所示图 3.5.4(2).打开仿真开关,根据表3.5.4输入情况实验,并将结果填入表内 表 3.5.4:输入 输 出A B C i 4SC i0 0 00 0 10 1 00 1 11 0 01 0 111 01113. 用逻辑分析仪观察全加器波形:(1) .先关闭仿真开关,在图3.5.4中删除除集成电路以外的其它元件。

(2) .点击电仿真软件 Multisim7基本界面右侧虚拟仪器工具条中的“ Word Generato ”按钮,如图3.5.5(左图)所示,调出字信号发生器图标(右图)“XWG1 ”, 将它放置在电子平台上。

图 3.5.5(3) .再点击虚拟仪器工具条中的“ Logic Analyzer ”按钮,如图3.5.6(左图) 所示,调出逻辑分析仪图标(右图)“XLA1 ”,将它放置在电子平台上。

o o O XXX三三二三三a三=T三三图 3.5.6(5) .双击字信号发生器图标“XWG1”,将打开它的放大面板如图3.5.8所示。

它是一台能产生32位(路)同步逻辑信号的仪表。

按下放大面板的“ Controls ”栏 的“ Cycle ”按钮,表示字信号发生器在设置好的初始值和终止值之间周而复始 地输出信号;单选“ Display ”栏下的“ Hex ”表示信号以十六进制显示;“Trigger ” 栏用于选择触发的方式;“ Freque nc?栏用于设置信号的频率。

--■rrra *+1*彎c t+f+ raILogic Analyzer |■ r r '・-rr•・「r|o o O XXX三三三三二二(4).连好仿真电路如图3.5.7所示..U1A ..,U1B ・.74L 汨已D'74LS06D:「ijZA :::::::4CT81ED 刘…I -_I | J ' . 4071BD 砂图 3.5.7图 3.5.8(6) .按下“ Controls”栏的“ Set…”按钮,将弹出对话框如图 3.5.9所示。

单选“Display Type”栏下的16进制“Hex”,再在设置缓冲区大小“ Buffer Size” 输入“ 000B”即十六进制的“11”,如图中鼠标手指所示,然后点击对话框右上角“ Accept”回到放大面板。

图 3.5.9(7) .点击放大面板右边8位字信号编辑区进行逐行编辑,从上至下在栏中输入十六进制的00000000~0000000A共11条8位字信号,编辑好的11条8位字信号如图3.5.10所示,最后关闭放大面板。

&OOOOOOCOOOOOOOOOOOOOOOOOOOOOO&图 3.5.10(8) .打开仿真开关,双击逻辑分析仪图标“XLA1 ”,将出现逻辑分析仪放大面板如图3.5.11所示。

将面板上“ Clock”框下“ Clock/Div ”栏输入12,再点击面板左下角” Reverse按钮使屏幕变白,稍等扫描片刻,然后关闭仿真开关。

将逻辑分析仪面板屏幕下方的滚动条拉到最左边,见图中鼠标手指所示。

图 3.5.11Ready '~Triepw 厂00000000OOQCOOOl000000020000000300003004ooaoooos0000000600000007ooocooos00000009±OOOOOQOATime (S)2.400m 4.£00m 7.200m P ,600m 12.000m10e1314Tma右Tam 了Ttrai®TfmlOTmallT皿12Teml3Tam 14TemlJTmal£1—1 _ 厂1 "L_1 ___ : __ : __ :__ : __:1 - -1 厂1_rn r~~LD J OOOS12 000 msDDDDDDDaTriggerClockC locks/Dhr |Sa…Bttemal Qualifier Qumlifiyr r rControls DisplayFreqiuernty|1(• HexC Dec厂BinaryC ASCII匠11T1 "T2创岂(9) .拉出屏幕上的读数指针可以观察到一位全加器各输入、 输出端波形,例 如:图3.5.12中读数指针所在位置表示输入信号 A=0、B=1、C j 」=1; S=0、G=1。

(注:屏幕左侧标有“ 9”的波形表示A ;标有“ 10”的波形表示B ;标有“ 8” 的波形表示G 」;标有“ 13”的波形表示S ;标有“ 14”的波形表示C i o ) (10) .按表3.5.5要求,用读数指针读出4个观察点的状态,并将它们的逻辑 状态和逻辑分析波形填入表3.5.5中。

Time (S)2.400^4.800m7.200mP.600m12.000mrrrrrrrri1O r 1.1.i.9,N 1 11 __________ 1 ■Lfc _____________ i ____ 1f 1 一―10_r i_ ~i r i ! : r~81 1 ___ 1:j ----- L : :1 : : ! : is:1 I 1; ; 1 : r14 f —-―1. I —丨 S 1 |1__ 1 a s Tan<5 niuumiuinnIl 1 18” 1 1 1 1 1 1 (1 | 讯 | i| p >1 4 1 1 4 1< II 1 !| 1 III II i i i i i i t| 1 \ 1< |< 1 1 1 1 >1< 1< tl 1 d d ill h i i i i i i 1 1 4 1 |i l> 1 1 1 1 4 l> d 1 1 i ill h i i i i i i 1 1 可 1 1 1" 1 1 >1 1 >1: l< 1 1 1 ll l|l II 1 1 l| 1 1 1 \ 1 4 1 l< I' 1 1 1 1 >l! |i i il il d i h iiiiiiTenn?Tam 9Toi 10 Tom 11込冲 Tom 13Tam 14TfflalS Tom 16nnnnnnnnnniinnnn1 1 || 1 1 1 \ 1 4 1 1 I' 1111«l>Clc (it Qua Tiigg_Qu4Clock T1 ♦芈12 T2-T14 417 mj12.000 ru 7.583 msDOISUocks/DivTrigger Set... S«.,PErtemal Qualifierr cQualifierC表 3.5.5:图 3.5.127八、7广1 23 4 状 态 波 形 状 态 波 形 状 态 波 形 状态 波 形输 A111B 011入 Ci 斗1输 出 S C i四、实验室操作实验内容:设计两个一位二进制数相加的全加器:1. 进行逻辑抽象分析:考虑的来自低位的进位将两个1位二进制数相加,称为全加。