小数分频

小数分频器的设计及其应用

第24卷 增刊2005年9月国 外 电 子 测 量 技 术Foreign Elect ronic Measurement TechnologyVol.24,Suppl.Sep.,2005作者简介: 尹佳喜(1981-),华中科技大学电气与电子工程学院04级研究生,研究方向电力电子与电力传动。

研究与设计小数分频器的设计及其应用尹佳喜(华中科技大学电气与电子工程学院 湖北武汉430074)摘要:分频器是数字系统设计中最常见的电路之一,在数字系统设计中,经常需要对时钟进行小数倍分频。

本文给出了三种用于实现小数分频的方案,并将三种方案进行了比较。

在此基础上,介绍了小数分频器在直接数字频率合成技术和步进电机驱动速度控制中的两种常见应用。

关键词:小数分频器 直接数字频率合成 步进电机 频率The Design and Application of Decim al Fraction Frequency DividerY in Jiaxi(College of Elect ricit y and Elect ronic Engeneering ,H uaz hong Universit y of S cience and Techlonog y ,W uhan 430074,China )Abstract :Frequency division is one of t he mo st common circuit s in t he design of digital system.Generally ,decimal f raction f requency division is needed.In t his paper ,t hree met hods to realize deci 2mal f raction frequency division are given ,and t he comparison among t he t hree met hods is presented.Applications of decimal Fraction Frequency divider in t he area such as direct digital f requency syn 2t hesis technology and stepper motor drive speed controller are int roduced.K eyw ords :decimal f raction frequency divider ,direct digital frequency synt hesis (DDS ),stepper mo 2tor ,frequency.0 引言 现代电子系统设计中,数字电子系统所占的比例越来越大,现代电子系统发展的趋势是数字化和集成化。

小数分频器的verilog-hdl设计

频率合成技术是现代通讯系统的重要组成部分,他将一个高稳定和高准确度的基准频率,经过四则运算,产生同样稳定度和基准度的频率。

分频器是集成电路中最基础也是最常用的电路。

整数分频器的实现比较简单,可采用标准的计数器或可编程逻辑器件设计实现。

但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

本文利用veriloghdl硬件描述语言的设计方式,通过modelsimse开发软件进行仿真,设计基于fpga的双模前置小数分频器。

随着超大规模集成电路的发展,利用fpga小数分频合成技术解决了单环数字频率合成器中高鉴相频率与小频间隔之间的矛盾。

1双模前置小数分频原理小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为k的小数分频,k可表示为:式中:n,n,x均为正整数;n为到x的位数,即k有n位小数。

另一方面,分频比又可以写成:式中:m为分频器输入脉冲数;p为输出脉冲数。

令p=10n,则:以上是小数分频器的一种实现方法,即在进行10n次n分频时,设法多输入x个脉冲。

2电路组成每个周期分频n+10-n.x,其电路双模前置小数分频器电路由÷n/n+1双模分频器、控制计数器和控制逻辑3部分组成。

当a点电平为1时,进行÷n分频;当a点电平为0时进行÷n+1分频。

适当设计控制逻辑,使在10n个分频周期中分频器有x次进行÷n+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了x.(n+1)+(10n-x).n个脉冲,也就是10n.n+x个脉冲,其原理如图1所示。

3小数分频器的verilog-hdl设计现通?过设计一个分频系数为8.7的分频器来给出使用veriloghdl语言设计数字逻辑电路的一般设计方法。

这里使用÷8/9双模前置分频器,按照前面的分析,可以通过计数器计数先做3次8分频,后做7次9分频,即可得到平均分频系数8.7。

基于FPGA的小数分频器设计

第1章 本课题内容1 课题目的频率合成技术是现代通信系统的重要组成部份,是对一个高精度和高稳固度的基准频率进行加、减、乘、除四那么运算,产生具有一样稳固度和基准度的频率。

分频器是数字逻辑电路设计中常常利用的一个大体电路。

通常,整数分频能够很容易地用计数器或状态机来实现。

但在某些场合下,时钟源与所需要的频率并非成整数关系,现在便需要采纳小数分频器进行分频。

一样来讲,小数分频电路能够分为半整数分频电路和非半整数分频电路两类。

关于小数分频的FPGA 设计,目前普遍采纳的方式是双模前置小数分频,和一种由双模前置小数分频改良而取得的小数分频——用一个半整数分频器和一个整数分频器代替双模前置小数分频中的两个整数分频器。

尽管这两种方案输出时钟的占空比误差和抖动性能方面有所不同,但其工作原理却是一致的。

双模前置小数分频器在理论上能够实现任意小数分频。

但在实际的电路设计中,不可能真正实现任意小数分频。

小数分频器的精度受操纵计数器的阻碍,而操纵计数器的设计会受硬件资源的限制,尽管FPGA 有相当丰硕的硬件资源。

另外,基于FPGA 实现的双模前置小数分频器在两个整数分频时钟之间的切换点上,有时候会显现毛刺,而时钟是不该该有毛刺存在的。

现在,就要结合脉冲删除技术,设计出一种能够进行任意小数分频且可不能显现毛刺的小数分频方案,并通过编程实现。

本文利用VHDL 硬件描述语言的设计方式,通过MAXPLUS II 开发平台,利用Altera 公司的FPGA 器件,设计并实现了一种不同占空比的任意小数分频器。

2 小数分频的大体原理假设时钟源的频率为f 0 ,期望取得的频率为f 1 ,那么其分频比X 为: X=10f f (式1-1) 其中,X>1。

假设M<X<M+1,M 为整数,那么有 X=M+212N N N +=2121)1(N N N M N M +⨯++⨯ (式1-2)其中,N 1和N 2均为整数。

当N 1和N 2取不同的正整数时,从)(212N N N +能够取得任意一个小数,就能够够从理论上实现任意小数分频比的分频。

简述小数分频技术原理及其电路机理解析

简述小数分频技术原理及其电路机理解析摘要:本文主要介绍了小数分频技术的理论和故障机理分析关键字:小数分频;小数环;锁相环1引言1964年第一台全晶体管信号发生器的诞生,从此信号发生器便进入了飞速发展阶段。

伴随着电子技术的发展,电子测试测量方向对信号发生器的要求也日益提高,传统的整数锁相技术已经无法满足更高的技术要求。

2小数分频技术的背景及意义整数N分频锁相技术具有锁定频率的特性,可以把整机信号的频率锁定在参考时钟信号频率的整数倍上。

但同时,它在技术层面存在很多瑕疵,整机输出信号的频率只能以参考时钟信号频率的整数倍变化。

当我们需要更高的锁相环频率分辨率时,就只能降低参考时钟频率的大小,而这必然会影响信号发生器中的锁相环性能,导致信号的相位噪声指标变差,降低信号的频谱纯度。

因此,就必须利用其它方法来加强它的频谱纯度。

小数分频运用一种平均的思想来获得小数的分频比。

通过改变分频比的某位小数,就可以在不改变参考频率的情况下来获得较高的频率分辨率。

从而解决了传统整数N分频锁相环路鉴相频率和分辨率相互影响、相互冲突的矛盾。

采用小数分频技术,来提高鉴相频率既可增加环路带宽范围,加强反馈环路增益效果,提高频率转换效率,又可以降低因为大分频比N导致的相位噪声增大现象,从而可获得比整数N分频锁相环路更好的噪声性能,降低环路的相位噪声,提高频谱纯度。

小数分频锁相技术可以使分频比变为小数,对频率进行细分,获得任意小的频率步进,实现了极高分辨率的分频比,它具有频率分辨率高、锁相时间短、相位噪声低的优势。

3小数分频技术的原理小数分频顾名思义,即输出频率可以按参数输入频率的分数倍变化而变化。

其实现原理为:在多个分频周期中,使其某几个周期抽掉一个波形或者加入一个波形,从而在整个的平均计数周期中,得到一个小数分频比。

锁相频率合成器的基本特性是,每当可编程分频器的分频比改变 1 时,得到输出频率增量为参考频率 fr。

假设可编程分频器能提供小数的分频比,每次改变某位小数,就能在不降低参考频率的情况下提高参考频率分频比了。

电子教材-小数分频锁相环的工作原理

4

小数分频锁相环的优点

– 无线对讲机必须以 1Hz 为频率步进

整数分频 锁相环: • 鉴相频率 (PDF) = 1 Hz !!! 小数分频 锁相环: • 鉴相频率 (PDF) = 10 KHz (若 Nfractional = 0.0001)

小数分频锁相环的工作原理

下一代无线基站的成功设计技巧

议程

-PLL 介绍及小数分频锁相环的优点 -小数分频锁相环的错误使用 -小数分频锁相环详解 -参考杂散及如何减少杂散 -总结

2

锁相环基础

R 计数器

fref

无噪声及稳定的 参考信源

÷R

鉴相器 及 电荷泵

环路 滤波器 压控振荡器 N 计数器 ÷N

900 900 900 900 901 900.2 第 1 次 第 2 次 第 3 次 第 4 次 第 5 次 平均值

– 瞬时相位错误会产生大量的小数杂散,并出现在偏移中心频率 Nfractional x PDF 之处

12

Delta sigma 小数分频 锁相环

R 计数器

fref

无噪声及稳定的 参考信源

• N 值越低,增加的噪声便越少

6

小数分频锁相环的优点

-80 Phase noise /dBc/Hz

-120 N=40000 N=400 -160

-200 0.1 1 10 Offset /KHz 100 1000

• N 计数器会令频综的噪声增加 20 log(N) – 整数分频 锁相环: 噪声增幅 = 92 dB – 小数分频 锁相环: 噪声增幅 = 52 dB • N 值越低,增加的噪声便越少

小数分频器原理

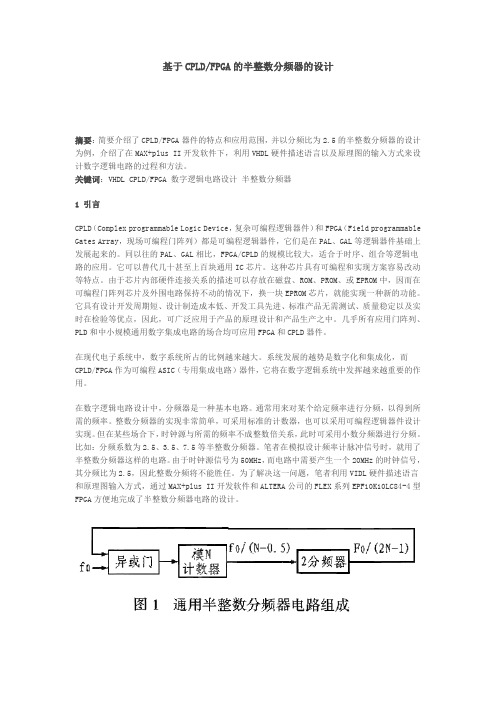

基于CPLD/FPGA的半整数分频器的设计摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。

关键词:VHDL CPLD/FPGA 数字逻辑电路设计半整数分频器1 引言CPLD(Complex programmable Logic Device,复杂可编程逻辑器件)和FPGA(Field programmable Gates Array,现场可编程门阵列)都是可编程逻辑器件,它们是在PAL、GAL等逻辑器件基础上发展起来的。

同以往的PAL、GAL相比,FPGA/CPLD的规模比较大,适合于时序、组合等逻辑电路的应用。

它可以替代几十甚至上百块通用IC芯片。

这种芯片具有可编程和实现方案容易改动等特点。

由于芯片内部硬件连接关系的描述可以存放在磁盘、ROM、PROM、或EPROM中,因而在可编程门阵列芯片及外围电路保持不动的情况下,换一块EPROM芯片,就能实现一种新的功能。

它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及实时在检验等优点,因此,可广泛应用于产品的原理设计和产品生产之中。

几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。

在现代电子系统中,数字系统所占的比例越来越大。

系统发展的越势是数字化和集成化,而CPLD/FPGA作为可编程ASIC(专用集成电路)器件,它将在数字逻辑系统中发挥越来越重要的作用。

在数字逻辑电路设计中,分频器是一种基本电路。

通常用来对某个给定频率进行分频,以得到所需的频率。

整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编程逻辑器件设计实现。

但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

比如:分频系数为2.5、3.5、7.5等半整数分频器。

小数分频频率合成器的理论基础(翻译)

小数分频频率合成器的理论基础A. Marques _, M. Steyaert and W. SansenESAT-MICAS, K.U. Leuven, Kard. Mercierlaan 94, B-3001 Heverlee, Belgium本文提出了一种基于锁相回路(PLL)频率合成器的演变概述。

数字PLL的主要限制的描述,以及随之而来的小数N技术使用的必要性是有道理的。

合成频率的旁瓣典型的杂散噪声线的起源进行了解释。

它通过使用数字∆∑调制器来控制分频值展示了如何消除这些杂散噪声线。

最后,数字∆∑调制器的使用同分数N PLL的输出相位噪声的影响一起进行了分析。

1.介绍无线通信领域,在过去十年中有了很大的发展。

这种快速发展,主要是通过引进强大的数字信号处理技术。

这些技术允许执行复杂的调制解调方案,以及先进的数字校正技术,最终产生非常高性能的系统,可以完全或几乎完全集成在一个标准的低成本技术。

典型的接收器/发射器无线系统RF部分如图1所示。

可以看出,在无线系统中,一个或多个频率合成器几乎都是必要的,同时在接收和发射部分。

此频率合成器必须不仅能够产生感兴趣的频带内的所有频率,以及产生具有高纯度的,由于不断下降的频道间距。

图1 典型的射频部分,一个无线接收器/发射器系统在无线系统领域,在过去几年中主要重点一直是在一个完整的系统的全面整合,包括发射器/接收器和频率合成器,使用短沟道CMOS或BiCMOS工艺(见[1,13]其引用)。

因此,频率合成精度高,稳定的需求令人难以置信的增长,特别是对需要的操作频率非常高(在千兆赫兹的范围内)的应用,小频率决议(典型的信道间隔几百万赫兹数100千赫),和低相位噪声数字(100dBc的订单数100千赫载波)。

此外,同时,在过去几十年,数字可编程的频率合成器的需求也增加了。

本文提供了一个数字可编程频率合成器相位锁定回路(PLL)为基础的演变概述。

由于相位噪声实际上是为无线通信系统所要求的规格是非常艰难的,主要的重点将在相位噪声的分析和如何在不削弱系统的其他特征的同时减少它。

deltasigma小数分频dither原理

deltasigma小数分频dither原理Delta Sigma 小数分频是一种将高频信号降频为低频信号的数字信号处理技术。

Dither(抖动)则是在数字信号处理过程中加入一定的噪音,以改善信号的量化误差。

本文将详细介绍Delta Sigma 小数分频和dither 的原理和应用。

一、Delta Sigma 小数分频的原理Delta Sigma(ΔΣ)调制是一种高效的数字信号处理技术,通过将高频信号采样、量化和编码,然后再将编码结果通过可变的数字序列进行调制,最终转换为低频信号。

其主要原理可以简单概括为以下几个步骤:1.采样:将待分频的高频信号进行采样,并将采样结果通过一个低通滤波器进行滤波,以去除高频成分形成基带信号。

2.量化:通过一个高分辨率的ADC(模数转换器)将基带信号进行量化,得到一个比特序列。

量化的目标是尽量减小误差,并保持足够的动态范围。

3.利用反馈和比较器:通过一个比较器将量化的结果与反馈信号进行比较,得到一个差值。

4.可变的数字序列:这个差值将作为一个可变的数字序列,控制下一个采样周期中采样的时刻和幅度。

5.重复以上过程:重复以上过程直到最新的差值足够小,或者达到设定的停止条件。

Delta Sigma 小数分频的主要特点是需要较高的过采样率,即采样频率要远高于分频后的输出频率。

这样可以利用高采样率降低量化误差,并通过反馈调制得到准确的分频结果。

二、Dither 的原理Dither 是一种在数字信号处理过程中引入一定程度的噪音的技术,主要用于解决量化误差带来的问题。

在数字信号处理中,由于信号是以离散的方式进行采样和量化,因此可能会出现量化误差。

量化误差是指将连续的模拟信号转换为离散的数字信号时所引入的误差。

这种误差会导致信号失真和动态范围的减小。

Dither 的作用是通过引入一定程度的噪音,将量化误差转化为随机的噪音,从而改善信号的质量。

具体原理如下:1.加入噪音:在量化过程中,将一个随机的、均匀分布的噪音序列加到待量化信号上。

任意数(整数、小数)分频器

任意数(整数、小数)分频器一、分频原理1.1偶数倍分频偶数倍分频通过计数器计数是很容易实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2—1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数.以此循环下去.这种方法可以实现任意的偶数分频。

1.2奇数倍分频奇数倍分频通过计数器也是比较容易实现的,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转.这样实现的三分频占空比为1/3或者2/3。

要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

与此同时进行下降沿触发的模N计数,到和上升沿触发输出时钟翻转选定值相同值时,进行输出时钟时钟翻转,同样经过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。

两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

如图1-1所示,是一个3分频器的仿真时序图。

图1—1 3分频器时序图1.3小数分频1。

3。

1原理小数分频有很多方法,基本原理都是一样,在若干分频周期中,使某几个周期多计或少计一个数,从而在整个周期的总体平均意义上获得一个小数分频比。

设:K为分频系数;N为分频系数的整数部分;X为分频系数的小数部分;M为输入脉冲个数;P为输入脉冲个数;n为小数部分的位数。

小数分频锁相环_小数杂散定性分析

锁相环小数杂散定性分析牟俊全²成都²2020-09最近想系统性的把锁相环小数杂散梳理一下,在网上查了查资料,无奈发现,要嘛是对几种特定频点的小数杂散泛泛而谈,定理式的描述几种杂散情况;要嘛就是从时差到相差、从相差到频域,通过各种级数、微积分变换对各阶小数杂散进行精确的定量分析,实在没有工程实践意义。

无奈,这里我从工程实践的角度,将几种典型的小数杂散分布情况进行梳理、总结,希望可以对小伙伴们起到一定的帮助。

情况1、当VCO输出频率正好在鉴相频率整数倍的频点时:此时VCO频率经过N分频器(由于是整数倍,此时N+1模分频器未参与,相当于整数N分频器)分频后,恰好等于鉴相频率。

这种情况下,参考频率与N分频器输出的反馈频率无频差,鉴相器锁定后不会进行相位矫正,因此理论上不会产生量化相差。

因此此时VCO输出频率中无小数杂散。

(实际中N分频器也会产生一些分频杂散频率,主要是鉴相频率,称谓鉴相泄露。

但是频率一般较高,可以被环路滤波器滤除。

因此一般不予考虑)情况2、当VCO输出频率正好在鉴相频率的N*(1±1/2) 倍频点时:此时N分频器有一半时间进行N分频,一半时间进行N+1分频。

(N、N+1分频交替进行)这种情况下,鉴相器每进行一次N分频,参考频率超前(360/N)°,当下次N+1分频时,又滞后( 360/N)°(大概值,实际有细微偏差,总之第一次超前的相位等于第二次滞后的相位。

),如此往复进行。

整体看来,参考频率与N分频器输出频率之间无平均相差。

这种情况下,鉴相器每2个鉴相频率周期就会完成一次相位矫正(先超前,后滞后)。

相当于在VCO输出频率之上,调制了一个等于0.5倍鉴相频率的信号(实际上是该信号及其丰富的各次谐波,此即为小数杂散)。

由于鉴相频率一般都在环路滤波器的带外,因此0.5倍鉴相频率,一般也都可以被环路滤波器滤除掉。

所以实际工程中,在二分之一鉴相频点,不存在小数杂散。

小数分频

7.3 、7.32

1.2 分频选择

• 以7.3分频为例: 要实现7.3分频,只要在10次分频中,做10-3=7次除7,3 次初8就可以得到:N=(7*7+3*8)/10=7.3。 • 以7.32分频为例: • 要实现7.32分频,只要在每100次分频中做100-32=68次除 7,32次除8,即可得到:N=(68*7+32*8)/100=7.32 • 所以,对于任何M.F分频: 都可以做(10-F)次除M,F次除(M+1),即可得到 N=[(10-F)*M+F(M+1)]/10=[10*M-F*M+F*M+F]/10 =[10*M+F]/10=M.F

每进行一次分频,计数值为小数部分累计相加,如果大于10, 则进行N+1次分频,累计值再减去10;若小于10则进行 N次分频。

• 以方法对输入频率进行2.7次分频,分频器选择:

序列 累加 值 1 7 2 14 3 11 4 8 5 15 6 12 7 9 8 16 9 13 10 10 3

分频 系数

2

3

3

2

3

3

2

3

3

可见,在10次分频中进行了7次3分频和3次2分频

1.3 任意整数分频

(1)偶数分频

偶数分频是易于实现的。当计数器输出为0到N/2-1 时。时钟输出0或1,计数器输出为N/2时到N-1时,时 钟输出1或0,当计数器数到N-1时,复位计数器,如 此循环下去,就可以实现对输入频率的偶数分频。 这种方案可以有限度的调整占空比。 以4分频为例:

•可见,实现N.F的小数分频,只需要对输入信号做不同次数的 N分频和N+1分频,就要设方法将两种分频混合均匀。 •这种“均匀”工作是通过计数器来完成的。

小数分频pll 带宽

小数分频pll 带宽

小数分频PLL(Phase-Locked Loop)是一种常见的时钟生成电路,它可以将输入的参考时钟信号分频成为所需的输出时钟信号。

PLL的带宽是指其锁相环的频率响应特性,即在输入时钟信号发生变化时,输出时钟信号的变化速度。

带宽的大小直接影响PLL的稳定性和锁定时间。

从理论角度来看,小数分频PLL的带宽取决于其环路滤波器的设计和参数设置。

一般来说,带宽的选择需要在满足系统稳定性的前提下尽可能大,以确保快速的锁定时间和良好的动态性能。

从实际设计角度来看,小数分频PLL的带宽需要考虑到系统的要求和特性。

较窄的带宽可以提供更好的抗噪声和抗干扰能力,但可能导致锁定时间较长,动态性能较差;而较宽的带宽可以提供更快的锁定时间和更好的动态性能,但也可能增加系统的噪声和干扰敏感度。

此外,小数分频PLL的带宽还受到环路滤波器的阶数、零极点配置、增益等参数的影响。

在实际设计中,工程师需要综合考虑系统的稳定性、锁定时间、动态性能以及抗干扰能力等因素,进行适

当的带宽选择和环路滤波器设计,以满足特定应用的要求。

总的来说,小数分频PLL的带宽是一个复杂而重要的设计参数,需要在理论和实际需求之间进行权衡和优化,以确保PLL系统能够

在特定应用环境下稳定可靠地工作。

sdc 小数分频约束

sdc 小数分频约束SDC小数分频约束是指在数字系统设计中,对于使用小数分频器的时钟信号,需要进行约束以确保系统的正常工作和准确性。

小数分频是一种常用的技术,可用于控制时钟频率,以满足特定的设计需求。

二、小数分频的原理小数分频器是一种将输入时钟信号按照指定的分频比例进行缩减的电路。

其基本原理是通过计数器和逻辑单元实现对时钟信号的分频控制。

具体而言,当计数器达到设定值时,逻辑单元将输出一个时钟脉冲,然后重新开始计数,形成了分频后的时钟信号。

三、SDC小数分频约束的重要性在数字系统设计中,时钟信号是整个系统的重要组成部分,对系统的性能和稳定性有着重要影响。

而小数分频作为一种常用的技术手段,用于生成特定频率的时钟信号,因此其约束十分关键。

只有明确了SDC小数分频的约束,才能确保时钟信号的准确性、稳定性和可靠性。

1. 分频比例:确定所需的分频比例,即输入时钟信号与输出时钟信号的频率之比。

在约束中明确指定分频比例,可以根据设计要求和系统性能进行合理选择。

2. 精度要求:对于一些对时钟信号精度要求较高的应用场景,需要设定适当的分频精度。

通常情况下,要求分频后的时钟信号频率与给定频率之间的误差应在一定范围内。

3. 时钟延迟:分频操作会引入一定的时钟延迟,因此需要对时钟信号的延迟进行合理的约束。

确保延迟在接受范围内,以避免对系统的正常运行产生不良影响。

4. 时序关系:在时钟信号的分频过程中,有可能会涉及到其他时序逻辑的处理,因此需要明确时序关系。

确保逻辑运算的正确性和时序的合理性。

通过对SDC小数分频约束的准确理解和合理应用,可以有效保证数字系统的正常运行和性能优化。

在实际的系统设计中,要特别注意分频比例、精度要求、时钟延迟和时序关系等关键要点,以确保时钟信号的稳定性和可靠性。

只有在满足约束要求的前提下,小数分频技术才能发挥其最大的作用。

六、参考资料[1] "Clock Divider" - Wikipedia, the free encyclopedia[2] "SDC Constraints" - Doulos[3] "Introduction to SDC" - Xilinx User Guides。

小数分频原理

小数分频原理小数分频是一种常见的数字电路设计技术,可以将一个时钟信号按照一定的比例分频,得到所需的频率。

本文将详细介绍小数分频原理及其应用。

一、小数分频原理小数分频是指将一个时钟信号按照非整数比例进行分频。

在数字电路中,常用的分频器是锁相环(PLL)和分数分频器。

其中,锁相环是一种基于反馈的控制系统,它可以通过调整反馈路径上的计数器的值来实现分频比的精确控制。

而分数分频器是一种通过将时钟信号输入到分频器中的两个计数器之一,然后将另一个计数器的输出作为输出时钟信号的方式来实现分频的。

在分数分频器中,两个计数器的初始值是固定的,它们的差值就是分频比的小数部分。

当第一个计数器计数到初始值时,它将发出一个脉冲信号,触发第二个计数器计数一次,然后输出一个脉冲信号作为输出时钟信号。

通过不断重复这个过程,就可以实现小数分频。

二、小数分频的应用小数分频广泛应用于数字通信系统、音频处理、图像处理等领域。

下面将分别介绍一些典型的应用。

1. 数字通信系统中的小数分频在数字通信系统中,时钟信号的频率往往需要精确控制。

小数分频可以用来实现通信系统中的时钟同步、数据解调等功能。

例如,GSM 系统中的时钟同步就是通过小数分频来实现的。

2. 音频处理中的小数分频在音频处理中,时钟信号的频率决定了音频的采样率和播放速度。

小数分频可以用来控制音频的采样率,从而实现音频的倍速播放、变速播放等功能。

此外,小数分频还可以用于音频合成、混音等处理。

3. 图像处理中的小数分频在图像处理中,小数分频可以用来控制图像的帧率,实现图像的快速播放、慢动作播放等效果。

此外,小数分频还可以用于图像的缩放、旋转等处理。

三、小数分频的优势和局限性小数分频具有以下优势:1. 分频精度高:小数分频可以实现非整数的分频比,分频精度较高。

2. 灵活性强:小数分频可以根据实际需求来调整分频比,具有较大的灵活性。

3. 节省资源:小数分频器通常只需要一个时钟信号和几个计数器,占用的资源较少。

小数分频锁相环的工作原理

小数分频锁相环的优点

• 鉴相频率 (PDF) 有更多选择

– 例如: 最小频率步进 = 30 KHz – 整数 分频锁相环:

• fvco = (N)PDF, (N+1)PDF, (N+2)PDF, ..... • 最小鉴相频率 (PDF) = 30 KHz

– 小数分频 锁相环:

• fvco = (Nint)PDF, (Nint+Nfractional)PDF, (Nint+2xNfractional)PDF, ….. • 最小鉴相频率 (PDF) =

• 添加随机性

– 为小数分频 平均序列添 加随机性

9dB down Gone

LMX2531

18

抑制小数杂散的方法

• 只要采用以下序列,便可确保 N = 99.5:

– 98, 99, 100, 101, … (模式重复出现) – 周期性序列可能会产生较多小数杂散

• 添加随机性

– 将序列随机化 – 99, 100, 98, 101, 98, 99, 100, 101, 98, 101, 99, … (模式重复出现) – – – – 降低其周期性可以将小数杂散推高至高频区 对亚小数杂散产生最大影响 对小数杂散产生较少影响 若 FNUM 等于 “0”,可能会恶化杂散

PDF = 10MHz Nfractional = 0.22 LBW = 10KHz 2nd order modulator 4th order loop filer 2nd order loop filter 7dB down

– 稍高的相位噪声若可 接受

• 电阻会增添噪声

LMX2531

– 采用可配置的局部内 置式环路滤波器锁相 环可以简化设计

小数分频锁相环原理

小数分频锁相环原理今天来聊聊小数分频锁相环原理。

你知道吗?生活中有很多跟频率相关的东西,就像我们听广播,每个电台都有自己固定的频率,收音机得精准地调到那个频率才能清楚听到节目。

锁相环就有点像这个收音机的调谐装置,不过小数分频锁相环又有它特殊的地方。

我一开始接触这个小数分频锁相环的时候,真的是一头雾水。

啥是小数分频呢?简单来说,如果把分频比喻成分蛋糕的话,整数分频就像把一个蛋糕分成几块一样,只能是整数,比如说分成2块、3块。

但是小数分频就厉害了,它可以把这个蛋糕分成块这种带小数的部分。

这就要说到小数分频锁相环的特别之处了。

普通的整数分频锁相环可能在满足某些特定的频率转换上不太灵活。

比如说,我们希望从输入频率得到一个很精确但又不是整数倍数关系的输出频率的时候,整数分频锁相环就有点捉襟见肘了。

而小数分频锁相环就可以用它小数分频的能力来搞定这个问题。

有意思的是,小数分频锁相环实现小数分频是通过一些巧妙的方式。

它其实是在多个整数分频比例之间快速切换,让整体看起来好像是在进行小数分频操作。

就好比是你想要一个刻度的长度,你没有这么精确的尺子,那你可以交替使用1刻度的尺子和2刻度的尺子,快速切换,最后量出来平均效果就是刻度这么个意思。

从理论上讲,它依据的是平均的概念。

举例来说,在通信系统里,如果我们想要把10MHz的频率通过小数分频锁相环转变成。

传统的整数分频就是5分频啦,那就是直接把10MHz变成2MHz,这就不够精确。

但是小数分频锁相环可能会是按照类似3分频、2分频交替这样来做,平均下来就是分频,这样就能得到我们想要的输出频率。

不过老实说,我在学习这个过程中也有困惑。

比如说在这个交替分频过程中怎么保证切换的时候不会有跳跃或者紊乱呢?这就涉及到小数分频锁相环的控制机制了,它得有很复杂的反馈控制电路。

这个反馈控制电路就像一个非常有经验的舵手,看着各种情况随时调整这艘分频的“船”的方向,让整个分频过程平稳准确地进行。

eda课程设计-航空通信中小数分频器的设计[管理资料]

![eda课程设计-航空通信中小数分频器的设计[管理资料]](https://img.taocdn.com/s3/m/512e992958f5f61fb63666b7.png)

航空通信中小数分频器的设计摘要:FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

本次项目是小数分频。

小数分频是为解决人们想要小数频率的愿望,而不局限于整数频率。

高速发展的的当今社会是数字化的时代,各种各样的数字化产品进入了市场。

而用VHDL语言实现的数字产品也在一定范围内满足市场上不同的需求。

用FPGA设计的产品不但降低的生产成本,还在一定程度上缩短了生产周期。

同时所需的人力又不是特别多。

小数分频的基本原理小数分频的基本原理是采用脉冲吞吐计数器和锁相环技术先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。

,可以将分频器设计成9次10分频,1次11分频,这样总的分频值为:F=(9×10+1×11)/(9+1)=,由于分频器的分频值不断改变,因此分频后得到的信号抖动较大。

(N为整数)时,可控制扣除脉冲的时间,以使输出成为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。

本次设计用VHDL设计了小数分频器,在QuartusⅡ,仿真结果证明本次实验正确,最后用FPGA器件实现了小数分频器。

关键字:FPGA 小数分频器 VHDL 频率计目录1 FPGA及VHDL简介什么是FPGA (3)FPGA由什么构成 (4)FPGA设计步骤 (5)硬件描述语言VHDL (9)2 小数分频分析及设计整数分频与半整数分频 (11)分频的程序 (11)顶层原理图 (14)3 外围及显示电路设计频率计 (15)4位十进制频率计的设计 (15)4位十进制频率计系统仿真及结果 (16)TESTCL模块的设计 (16)TESTCL模块系统仿真及结果 (19)4 实验总结 (20)致谢 (21)参考文献 (21)引言随着各种先进雷达、制导、定位系统、数字通信设备及专用测试仪性能的不断提高,对其频率源的要求越来越高。

verilog 实现小数分频(小数分频器)代码

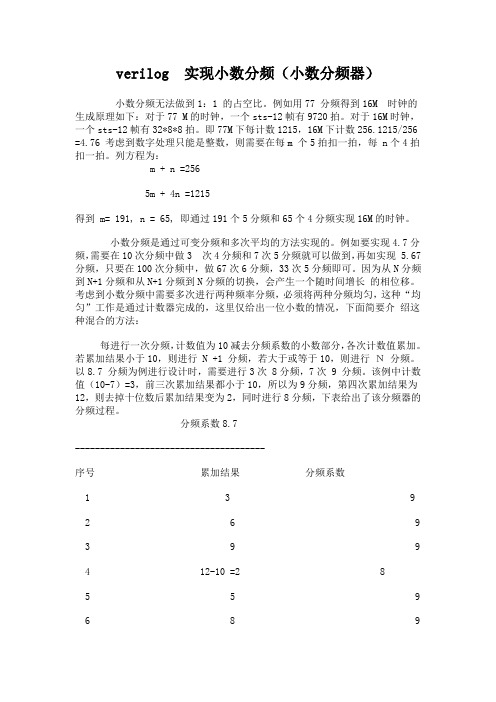

verilog 实现小数分频(小数分频器)小数分频无法做到1:1 的占空比。

例如用77 分频得到16M 时钟的生成原理如下:对于77 M的时钟,一个sts-12帧有9720拍。

对于16M时钟,一个sts-12帧有32*8*8拍。

即77M下每计数1215,16M下计数256.1215/256 =4.76 考虑到数字处理只能是整数,则需要在每m 个5拍扣一拍,每 n个4拍扣一拍。

列方程为:m + n =2565m + 4n =1215得到 m= 191, n = 65, 即通过191个5分频和65个4分频实现16M的时钟。

小数分频是通过可变分频和多次平均的方法实现的。

例如要实现4.7分频,需要在10次分频中做3 次4分频和7次5分频就可以做到,再如实现 5.67分频,只要在100次分频中,做67次6分频,33次5分频即可。

因为从N分频到N+1分频和从N+1分频到N分频的切换,会产生一个随时间增长的相位移。

考虑到小数分频中需要多次进行两种频率分频,必须将两种分频均匀,这种“均匀”工作是通过计数器完成的,这里仅给出一位小数的情况,下面简要介绍这种混合的方法:每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。

若累加结果小于10,则进行 N +1 分频,若大于或等于10,则进行N分频。

以8.7 分频为例进行设计时,需要进行3次 8分频,7次 9 分频。

该例中计数值(10-7)=3,前三次累加结果都小于10,所以为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,下表给出了该分频器的分频过程。

分频系数8.7--------------------------------------序号累加结果分频系数1 3 92 6 93 9 94 12-10 =2 85 5 96 8 97 11-10 =1 88 4 99 7 910 10 8 以下是代码模块://top modulemodule fd89bits( clkin,reset,a,clkout);input clkin;input reset;input a;output reg clkout;wire clkout1,clkout2;fd8bits dut1(clkin,reset,clkout1);fd9bits dut2(clkin,reset,clkout2);always@(posedge clkin) beginif(a)clkout <= clkout1;elseclkout <= clkout2;endendmodule`timescale 1ns / 1psmodule fd8bits(clk_in,reset,clk_out );input clk_in;input reset;output reg clk_out;reg[3:0] count;always@(posedge clk_in) beginif(!reset)count <= 0;else beginif(count < 7)count <= count + 1;elsecount <= 0;endclk_out <= count[2];endendmodule// 9 分频module fd9bits(clk_in,reset,clk_out );input clk_in;input reset;output reg clk_out;reg[3:0] count;always@(posedge clk_in) beginif(!reset)count <= 0;else beginif(count < 8)count <= count + 1;elsecount <= 0;endclk_out <= count[2];endendmodule// testbenchmodule testbench();reg clk_in;reg reset;reg a;wire clk_out;fd89bits dut(clk_in,reset,a,clk_out);initial beginclk_in= 0;reset = 0;#11;reset = 1;forever begina = 1;#60;a = 0;#20;a = 1;#40;a = 0;#20;a = 1;#40;a = 0;#20;endendalways #10 clk_in = ~clk_in; endmodule//result。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

component sel port( clock_in : in std_logic; Xnumber : in std_logic_vector(3 downto 0); sel_out : out std_logic); end component; ---------------------------------------------component mux_21 port( a : in std_logic; b : in std_logic; s : in std_logic; y : out std_logic); end component; -----------------------------------------------signal selt : std_logic; 信号定义 signal selt_not : std_logic;

7.3 、7.32

1.2 分频选择

• 以7.3分频为例: 要实现7.3分频,只要在10次分频中,做10-3=7次除7,3 次初8就可以得到:N=(7*7+3*8)/10=7.3。 • 以7.32分频为例: • 要实现7.32分频,只要在每100次分频中做100-32=68次除 7,32次除8,即可得到:N=(68*7+32*8)/100=7.32 • 所以,对于任何M.F分频: 都可以做(10-F)次除M,F次除(M+1),即可得到 N=[(10-F)*M+F(M+1)]/10=[10*M-F*M+F*M+F]/10 =[10*M+F]/10=M.F

signal clock_1 : std_logic; signal clock_2 : std_logic; signal clock_sel: std_logic; signal n_fd : std_logic_vector(3 downto 0); signal n1_fd : std_logic_vector(3 downto 0); ------------------------------------------------------------begin number0 : number port map (n, n_fd, n1_fd); fdn0 : fdn port map (clock, selt_not, n_fd, clock_1); fdn1 : fdn port map (clock, selt, n1_fd, clock_2); mux_210 : mux_21 port map (clock_2, clock_1, selt, clock_sel); sel0 : sel port map (clock_sel, x, selt); selt_not <= not selt;clock_out <= clock_sel; end arch; 顶层文件描述结束

architecture arch of NdotXfd is

结构体

component number port( n : in std_logic_vector(3 downto 0); number0 : out std_logic_vector(3 downto 0); number1 : out std_logic_vector(3 downto 0) ); end component; --------------------------------------------------元件例化 component fdn port( clock_in : in std_logic; enable : in std_logic; n_of_fd : in std_logic_vector(3 downto 0); clock_out : out std_logic); end component;

2

3

3

2

3

3

2

3

3

可见,在10次分频中进行了7次3分频和3次2分频

1.3 任意整数分频

(1)偶数分频

偶数分频是易于实现的。当计数器输出为0到N/2-1 时。时钟输出0或1,计数器输出为N/2时到N-1时,时 钟输出1或0,当计数器数到N-1时,复位计数器,如 此循环下去,就可以实现对输入频率的偶数分频。 这种方案可以有限度的调整占空比。 以4分频为例:

每进行一次分频,计数值为小数部分累计相加,如果大于10, 则进行N+1次分频,累计值再减去10;若小于10则进行 N次分频。

• 以方法对输入频率进行2.7次分频,分频器选择:

序列 累加 值 1 7 2 14 3 11 4 8 5 15 6 12 7 9 8 16 9 13 10 10 3

分频 系数

•可见,实现N.F的小数分频,只需要对输入信号做不同次数的 N分频和N+1分频,就要设方法将两种分频混合均匀。 •这种“均匀”工作是通过计数器来完成的。

两种方法: 每进行一次分频,计数值为10减去分频系数的小数部分,各 次的计数值累加;若累加值小于10,进行N+1分频,若大于或 等于10,进行N分频。

基于VHDL的小数分频设计

• 1. 小数分频的基本原理 • 2. 各个模块功能的实现

1.基本原理分析

1.1小数分频的基本原理

• 小数分频的基本原理:即在若干个分频周期中采取某种方 法使某几个周期多计和少计一个数,从而在整个计数周期 的总体平均意义上获取一个分频比。 • 分频比:K=M/P。 M代表分频器输入的脉冲数; K代表分频器输出的脉冲数; 10 n X)P M=K*P=(N+ 实质:设定一个分频比使得:输出频率=输入频率/分频比。

• 2. 各个模块功能的实现

2.1 顶层文件

1:NdotXfd,顶层文件 library ieee; use ieee.std_logic_1164.all; 库、程序包 use ieee.std_logic_unsigned.all; -------------------------------------------------------entity NdotXfd is port ( clock : in std_logic; n : in std_logic_vector(3 downto 0); x : in std_logic_vector(3 downto 0); 实体 clock_out : out std_logic ); end entity;

------------------------------------------------------------

小数分频是由两个不一样的整数:1 的比例混合而成的。

假设:每5个脉冲为一组,当计数器记到2两个脉冲时, 产生一个输出脉冲,当计数器记后3个脉冲时, 产生一个输出脉冲。

那么,这5个输入脉冲就产生了2个输出脉冲。 从而,得到分频比为 k=5/2=2.5。

(2)奇数分频

若进行非50%的奇数分频,则按照偶数分频的方法来 进行分频。 要实现占空比为50%的2N+1分配器,则需要对待分频 时钟上升沿和下降沿分别进行N/(2N+1)分频,然后将 两个分频所得的时钟信号相或,即可得到占空比为 50%的2N+1分频器。 以5分频为例: 要实现占空比为50%的5分频,要对上升沿进行2分频, 对下降沿进行2分频,再将得到的信号进行或运算, 即可得到。