modelsim仿真详细过程

ModelSim后仿真详细流程介绍PPT课件

延时信息

2021/3/9

8

目录

仿真的基本概念 ➢后仿真前的基本准备工作

后仿真的基本操作步骤

2021/3/9

9

后仿真前的基本准备工作

▪ ModelSim库

库文件,是指已经编译通过的设计文件的总体。

ModelSim中有两种库类型:

工作库

资源库

1.库的内容会随着使用者 更新设计文件和重新编译 而变化; ▪2D.e存sc放ript当ion前of设th计e b文usi件nes编s 译 后产生的设计单元; 3.编译前必须先创建好工 作库; 4.每次编译只允许有一个 工作库; 5.默认的工作库名是work

2021/3/9

14

后仿真前的基本准备工作

▪ Altera仿真库建立步骤

2.启动ModelSim SE。建立两个新库,从主菜单选择File->New-> Library,选中“a new library and a logical mapping to it”,在“Library Name”填写“altera_base_v”,Library Physical Name填写文件夹绝 对路径,如图所示。

2021/3/9

13

后仿真前的基本准备工作

▪ Altera仿真库建立步骤

1.在ModelSim安装目录中建立两个文件夹,一个是用于存放公用的 库给它取名altera_base_v;另一个是用于存放您要用到的特定的器件 库,取名为altera_device。

比如,F:\Modelsim 6.5\altera\altera_base_v F:\Modelsim6.5\altera\altera_device

注意:要把 Enable optimization 前 面的勾去掉,即不进行自动优化。

ModelSim仿真流程

ModelSim仿真流程关于ModelSim仿真流程EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

下面店铺准备了关于ModelSim仿真流程,欢迎大家参考!1、运行ModelSim,如果上一次使用ModelSim建立过工程,这时候会自动打开上一次所建立的工程;2、点击File->New->Project,在Project Name中我们输入建立的工程名,在Project Location中输入工程保存的路径,注意ModelSim不能为一个工程自动建立一个目录,这里我们最好是自己在Project Location中输入路径来为工程建立目录,在Default Library Name中为我们的设计编译到哪一个库中,这里我们使用默认值,这样,在我们编译设计文件后,在Workspace窗口的Library中就会出现work库。

这里我们输入完以后,点击OK;3、如果提示我们给定的工程路径不存在,是否建立该路径,我们的目的就是为工程建立一个新目录,因此,点击确定;4、点击Create New File可以为工程添加新建的文件,点击Add Existing File为工程添加已经存在的文件,点击Create Simulation为工程添加仿真,点击Create New Folder可以为工程添加新的目录。

这里我们点击Create New File;5、我们在File Name中输入文件名称,Add file as type为输入文件的.类型为VHDL、Verilog、TCL或text,这里我们使用默认设置VHDL,Folder为新建的文件所在的路径,Top Level为在我们刚才所设定的工程路径下。

点击OK;并在Add items to the Project窗口点击Close关闭该窗口;6、这时候在Workspace窗口中出现了Project选项卡,在其中有文件名.vhd,其状态栏有一个问号,表示未编译,我们双击该文件,这时候出现编辑窗口,在其中我们输入我们的设计文件7、点击File->Save,并退出该窗口(File->Close);8、在WorkSpace窗口的文件名.vhd上点击右键,选择Compile->Compile All;9、在脚本窗口中将出现一行绿色字体Compile of DivClkHDL.vhd was successful.,说明文件编译成功,在该文件的状态栏后有一绿色的对号,表示编译成功;10、下面我们开始仿真,点击菜单Simulate->Simulate,展开Design选项卡下的work库,并选中其中的behavioral,这是在Simulate中出现了work.实体名(behavioral)表示我们所要仿真的对象,Resolution为仿真的时间精度,这里我们使用默认值,点击OK;11、为了观察波形窗口,我们点击菜单View->Wave;12、这时候出现的Wave窗口为空,里面什么都没有,我们要为该窗口添加我们需要观察的对象,首先在主窗口而不是波形窗口中点击View->Signals打开信号列表窗口,在改窗口中点击Add->Wave->Signals in Design,这时候在波形窗口中就可以看到这些信号了;13、下面我们就开始仿真了,在主窗口中输入命令对信号进行驱动仿真14、退出仿真,在主窗口中点击Simulate->End Simulation,会出现对话框,提示我们是否确认退出仿真,我们点击是退出仿真;。

quartus的modesim仿真过程

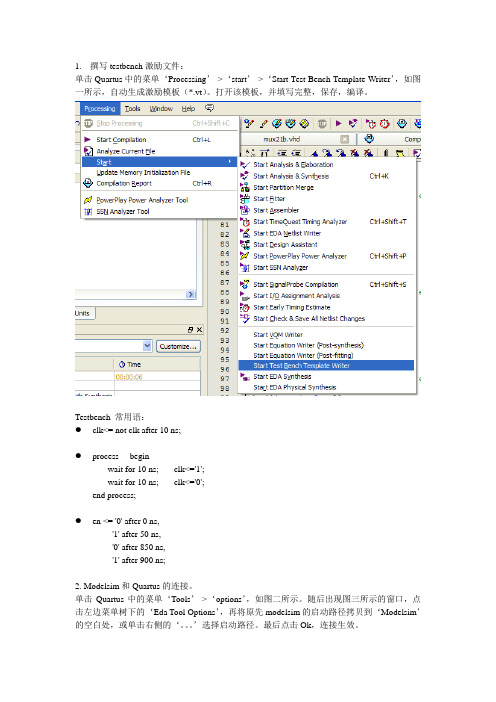

1.撰写testbench激励文件:单击Quartus中的菜单‘Processing’->‘start’->‘Start Test Bench Template Writer’,如图一所示,自动生成激励模板(*.vt)。

打开该模板,并填写完整,保存,编译。

Testbench 常用语:●clk<= not clk after 10 ns;●process beginwait for 10 ns; clk<='1';wait for 10 ns; clk<='0';end process;●en <= '0' after 0 ns,'1' after 50 ns,'0' after 850 ns,'1' after 900 ns;2. Modelsim和Quartus的连接。

单击Quartus中的菜单‘Tools’->‘options’,如图二所示。

随后出现图三所示的窗口,点击左边菜单树下的‘Eda Tool Options’,再将原先modelsim的启动路径拷贝到‘Modelsim’的空白处,或单击右侧的‘。

’选择启动路径。

最后点击Ok,连接生效。

图二图三3. 设置编译信息。

单击Quartus中的菜单‘Assignment’->‘Settings’,如图四所示。

随后进入图五所示的Settings 界面,点击左侧菜单树‘EDA Tool Settings’下的‘Simulation’,右边的窗口出现Simulation 界面,并进行如图五的设置。

其中点中‘Compile test bench’左边的圈圈后,再点击右侧的按钮‘Test Benches。

’进入图六所示的界面,点击右上按钮‘New’进入图七所示的‘New Test Bench Settings’界面,填入相关信息:激励文件名(1),激励文件实体名(2),激励文件中的例化名(3),最大仿真时间(4),和激励文件的具体路劲(5)。

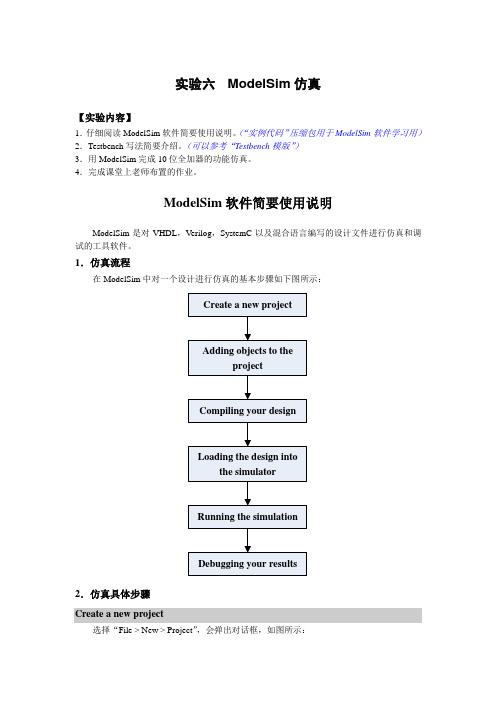

实验六 Modelsim仿真

实验六ModelSim仿真【实验内容】1.仔细阅读ModelSim软件简要使用说明。

(“实例代码”压缩包用于ModelSim软件学习用)2.Testbench写法简要介绍。

(可以参考“Testbench模版”)3.用ModelSim完成10位全加器的功能仿真。

4.完成课堂上老师布置的作业。

ModelSim软件简要使用说明ModelSim是对VHDL,V erilog,SystemC以及混合语言编写的设计文件进行仿真和调试的工具软件。

1.仿真流程在ModelSim中对一个设计进行仿真的基本步骤如下图所示:2.仿真具体步骤Create a new project选择“File > New > Project”,会弹出对话框,如图所示:其中:“Project Name”项:填写要创建的工程的名字。

“Project Location”项:确定创建的工程所要存放的位置。

“Default Library Name”项:填写工程的工作库的名字。

注:在用ModelSim进行仿真之前,必须要对设计文件进行编译,生成与设计文件逻辑功能相对应的设计单元。

由于ModelSim是用库文件来进行仿真的,所以编译后的设计单元需要存放在库文件里。

这个库文件叫作“工作库”。

以上三项填写完毕后,点击“OK”按钮,会在指定的位置处创建工程及工作库,如图所示:在工作库文件夹内,有一个名为“_info”的特殊格式文件,如图所示:这个文件指定了此文件夹为ModelSim的工作库文件夹。

在编译步骤内生成的所有设计单元都会被添加到工作库文件夹内。

Adding objects to the project在上一步点击OK后,ModelSim会弹出一个对话框,如图所示:其中:“Create New File”项:在工程中创建新的设计文件。

“Add Existing File”项:把已经存在的设计文件加入到工程中。

“Create Simulation”项:在工程中创建仿真配置文件。

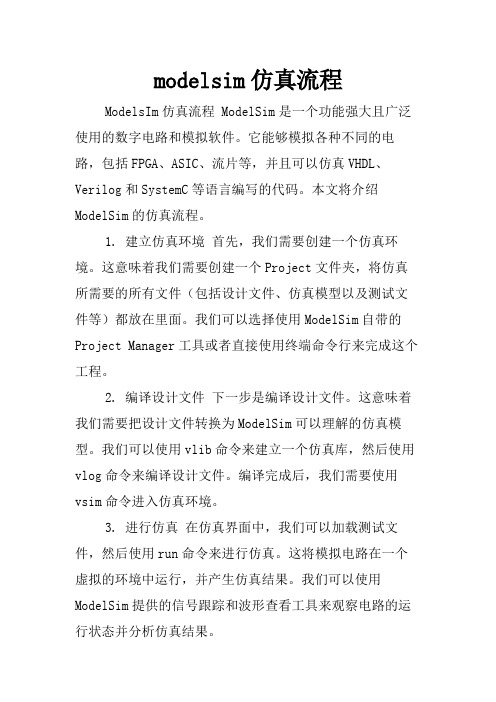

modelsim仿真流程

modelsim仿真流程

ModelsIm仿真流程 ModelSim是一个功能强大且广泛使用的数字电路和模拟软件。

它能够模拟各种不同的电路,包括FPGA、ASIC、流片等,并且可以仿真VHDL、Verilog和SystemC等语言编写的代码。

本文将介绍ModelSim的仿真流程。

1. 建立仿真环境首先,我们需要创建一个仿真环境。

这意味着我们需要创建一个Project文件夹,将仿真所需要的所有文件(包括设计文件、仿真模型以及测试文件等)都放在里面。

我们可以选择使用ModelSim自带的Project Manager工具或者直接使用终端命令行来完成这个工程。

2. 编译设计文件下一步是编译设计文件。

这意味着我们需要把设计文件转换为ModelSim可以理解的仿真模型。

我们可以使用vlib命令来建立一个仿真库,然后使用vlog命令来编译设计文件。

编译完成后,我们需要使用vsim命令进入仿真环境。

3. 进行仿真在仿真界面中,我们可以加载测试文件,然后使用run命令来进行仿真。

这将模拟电路在一个虚拟的环境中运行,并产生仿真结果。

我们可以使用ModelSim提供的信号跟踪和波形查看工具来观察电路的运行状态并分析仿真结果。

4. 仿真结束仿真完成后,我们可以使用exit命令退出仿真环境,并使用ModelSim提供的波形分析和统计工具来评估仿真结果。

如果需要进行更详细的分析,我们可以将波形数据导出到其他工具进行进一步处理。

总之,ModelSim是一个非常强大的数字电路和模拟软件。

掌握其基本操作和仿真流程,可以帮助我们更高效地进行数字电路设计和开发工作。

EDK工程ModelSim仿真流程

EDK工程ModelSim仿真流程前期准备:1.已经安装软件工具:Xilinx ISE 11.1ModelSim 6.5Debussy5.4v92.EDK和ModelSim6.5联合仿真库设置完毕3.EDK和ModelSim6.5可以生成”.FSDB”文件,供Debussy波形查看器观察波形以参加电子设计竞赛的H.264工程为例,进行仿真演示。

1.首先确保工程simulation文件夹下没有文件。

2.如果有文件,要通过如下方式清除,不能直接删除。

3.清除后,点击Simulation Generate Simulation HDLFiles,重新生成工程仿真的库文件。

Console控制台显示生成了Simulation ModelSimulation文件夹下生成了一堆文件。

4.在Simulation文件夹下,找到“system_tb.v”文件,打开,添加如下语句initial begin$dumpfile("aa.fsdb");$dumpvars;end以便仿真时,生成fsdb文件。

5.返回XPS界面,选择Simulation->Launch HDL Simulator,通过这种方式,打开了ModelSim6.5软件6.打开了ModelSim6.5软件,如下图所示7.打开Simulation文件夹中的system_setup.do文件,该文件中存放了系统生成的仿真脚本语句。

8.返回ModelSim6.5,在命令行下先输入“do system.do”命令。

9.输入如下命令“vsim -novopt -t ps D:/modeltech_6.5/win32/novas.dll -Lxilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”理由(复制system_setup.do文件中第二条脚本语句”vsim -novopt -t ps -L xilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”,注意到要仿真生成fsdb波形文件,所以在ps和-L前添加一条新的语句”D:/modeltech_6.5/win32/novas.dll”,要链接这个“novas.dll”动态链接文件。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

Modelsim 仿真步骤总结

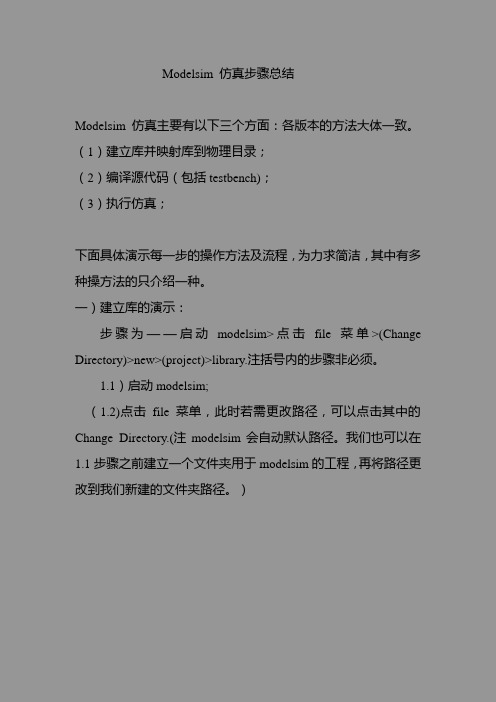

Modelsim 仿真步骤总结Modelsim 仿真主要有以下三个方面:各版本的方法大体一致。

(1)建立库并映射库到物理目录;(2)编译源代码(包括testbench);(3)执行仿真;下面具体演示每一步的操作方法及流程,为力求简洁,其中有多种操方法的只介绍一种。

一)建立库的演示:步骤为——启动modelsim>点击file菜单>(Change Directory)>new>(project)>library.注括号内的步骤非必须。

1.1)启动modelsim;(1.2)点击file菜单,此时若需更改路径,可以点击其中的Change Directory.(注modelsim会自动默认路径。

我们也可以在1.1步骤之前建立一个文件夹用于modelsim的工程,再将路径更改到我们新建的文件夹路径。

)(1.3)点击file子菜单中的new,选择project用于新建立一个modelsim工程。

(虽然此步非必须,但是建立一个新工程有益于接下来整个仿真文件的管理。

)1.4)点击file子菜单new,再点击new下的library,用于建立一个库。

(仔细观察1.3步,新建工程的同时亦可建立库)。

至此,modelsim仿真第一大步建立库的工作完毕。

二)编译源代码(包括testbench):大家都已知道在quartus中编译源代码的方法,这里说明一下在modelsim中编译源代码及testbench的方法。

步骤为——建立一个新工程(同时建立库)后,会自动提示你四个选项。

如图:选create new file后提示对话框,(也可以在有源文件的情况下选择add existing file到工程中。

例如我们用quartus写好文件后,可以用此方法将quartus中的文件添加到modelsim工程中来)让你命名你即将创建的新文件,完毕后,会自动出现一个空白的编辑窗口,在那里输入源代码和testbench。

Modelsim的功能仿真的详细过程适合初学者

11 看波形文件为

12 右击输出信号

13 在 Format 中点击 Analog,观看模拟信号,改变宽带

14 正旋波

6.

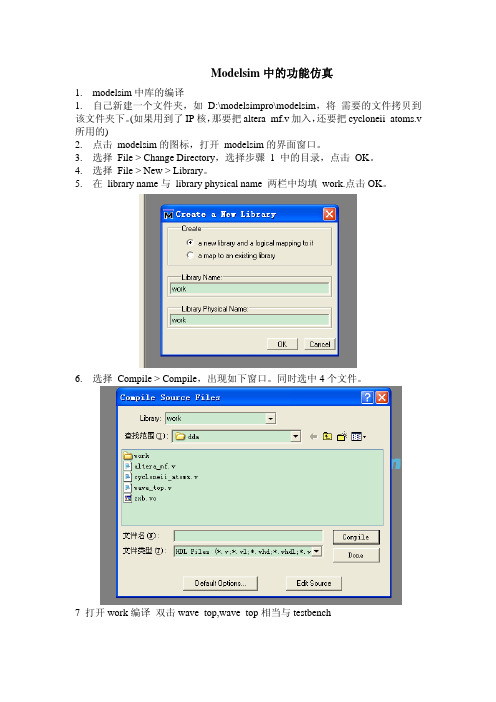

选择 Compile > Compile,出现如下窗口。同时选中 4 个文件。

7 打开 work 编译 双击 wave_top,wave_top 相当与 test加波形文件

10 在 Transcript 栏中打 run 10us (自己根据实际的情况)

Modelsim 中的功能仿真

1. modelsim 中库的编译 1. 自己新建一个文件夹,如 D:\modelsimpro\modelsim,将 需要的文件拷贝到 (如果用到了 IP 核, 该文件夹下。 那要把 altera_mf.v 加入, 还要把 cycloneii_atoms.v 所用的) 2. 点击 modelsim 的图标,打开 modelsim 的界面窗口。 3. 选择 File > Change Directory,选择步骤 1 中的目录,点击 OK。 4. 选择 File > New > Library。 5. 在 library name 与 library physical name 两栏中均填 work.点击 OK。

modelsim基本仿真流程

modelsim基本仿真流程ModelsSim基本仿真流程ModelsSim是一款常用的数字电路仿真工具,主要用于验证和调试硬件设计。

本文将介绍ModelsSim的基本仿真流程,帮助读者了解如何使用ModelsSim进行数字电路仿真。

一、创建工程我们需要创建一个ModelsSim工程。

在ModelsSim界面上方的菜单栏中选择"File",然后选择"New",再选择"Project"。

在弹出的对话框中,输入工程名称和工程路径,点击"OK"按钮即可创建工程。

二、添加设计文件在创建好的工程中,我们需要添加要仿真的设计文件。

在ModelsSim界面左侧的"Project"窗口中,右键点击工程名称,选择"Add Existing File"。

然后选择要添加的设计文件,点击"OK"按钮即可将设计文件添加到工程中。

三、设置仿真编译选项在添加完设计文件后,我们需要设置仿真编译选项。

在ModelsSim 界面左侧的"Project"窗口中,双击工程名称,打开工程设置窗口。

在"Compile"选项卡中,选择仿真模型和仿真器,并设置仿真选项。

根据需要,可以选择不同的仿真模型和仿真器,以及设置仿真时钟周期等参数。

四、编译设计设置完仿真编译选项后,我们需要编译设计。

在ModelsSim界面左侧的"Project"窗口中,右键点击工程名称,选择"Compile"。

ModelsSim将会对设计文件进行编译,生成仿真所需的文件。

五、创建仿真波形在编译设计后,我们需要创建仿真波形。

在ModelsSim界面下方的"Wave"窗口中,点击"New Wave"按钮。

在弹出的对话框中,选择要仿真的信号和时钟,并设置仿真时间范围。

Modelsim工具的一般仿真流程

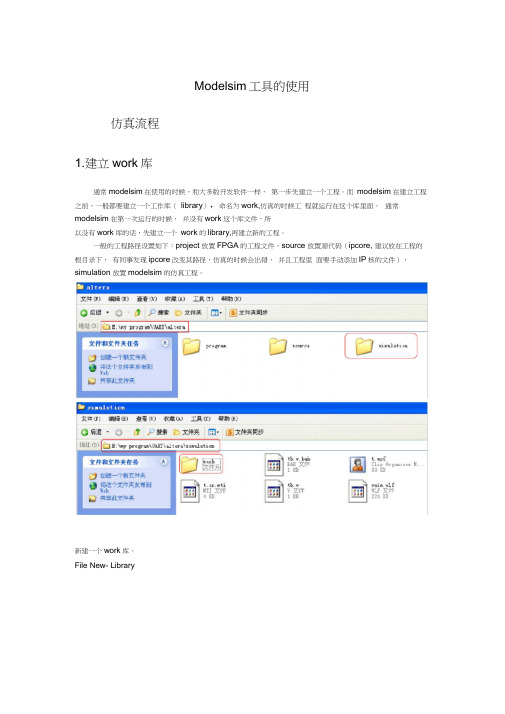

Modelsim工具的使用仿真流程1.建立work库通常modelsim在使用的时候,和大多数开发软件一样,第一步先建立一个工程。

而modelsim在建立工程之前,一般都要建立一个工作库(library),命名为work,仿真的时候工程就运行在这个库里面。

通常modelsim在第一次运行的时候,并没有work这个库文件,所以没有work库的话,先建立一个work的library,再建立新的工程。

一般的工程路径设置如下:project 放置FPGA的工程文件,source 放置源代码(ipcore, 建议放在工程的根目录下,有同事发现ipcore改变其路径,仿真的时候会出错,并且工程里面要手动添加IP核的文件),simulation 放置modelsim的仿真工程。

新建一个work库。

File New- Library^Hamc Type|旳thlibrary □fate 冋叶 djibs/dltera 兰沖忡阿」iflibraryGsfrfr^r^/vM 」ih 叩袖暮 A 』I F土扛就am_nF 』Pt Library冷忡怕.VFTl ihr^iy U Mr 耳丫日皿 ^clgrsiLibrary U fJter 耳什 d.libqkydbMii r 車 cyclorigii^ver 匸• fbalfi 讨 bIpm Library C :fafcsr^/Y«riag 」ts|cy!cbn“i 』er Library 押 aOEL.TECHT 简 adfbdb Library C; I'dtere/Yf-dJib 訓 pm r 血 IfTTl fCF Library Cii'dterc/Ycrioq itsl|prn vei (K nr 匚E 」b (emipo) Library JHODEL lEO-i/.JirEiJb —机 rrtlA/m 上rrtCWm Library Library SwaEiBL_TEOf.,^IIi J1MCiCiELJEOif,.jbm-2J 2 4-jt^ nrtPA 上虫nrtU^F Library 4MaOELJBOf..#ia_lb Library ^OCEL_lKHf../upfJlb 七 >[■ nrtlJ /in Library 4HariELjEa-v.,Aj^-i.]d 二九 Oiv^fn Libr^^y jH0CEL_lEair..1iO5V'7TTT jrtL 驹肚哼 Ubhfiiy C ; |前岀i ■訝计M 」ibs/sMEef 4t 珂aS_Vd Llbifliy C^i'dlsre/Yri 1匚电_11&4护1口_样「 + A L #_血 ULr^ryinciriELjrciir.js^sd 二 4^ vtaLocu Library iNUDEL.IECHf ../Vt^OCO 二 jL IPlibrary钿 tWEL-TECHLQ*_ 血 iTcddsinni 」ti library 榔口DEL JEO#. /rrcrtslcm 」H函山,ddlibrary $WCiLELJEO*../£td 上 JtL ctdjdsssIc-ptrMt Library iMQLEL_7EO+skps* 抄it丄血 a^ncpsyi Library 4b<GDEL_7EQf ii/syncpsyi 工忙 vsrilog Library!|NCi[jEL_IE'CHf../voracgHl Ubraiy — ■pgM 丄::灯血刃向dl H K , ±O -I Mirai-dtei e_rf dtei 0jrf_W5T J L 业 dteia_^-r +札i y 叭戸■ 1血ryderal ■湘于 土丸1幻畝惟」血 ± -fl.晌 1 JL 布肝■榆 血 (mptr) t-血 + 脚.fil":皿1 七 J^lntFAffltllTmtUMnO5>*TTi占艸 列4_¥・■5i,i_^fd MtdiZDEO■see _____ tn 处加i 」t> 1,直泅4- 血 ^itd rfevd-^rrTS^I : t_ 刊「即裤 £ 血 Wl IJIJtrtrra v UbTs y Lltrof!/li 啊母章 Llbrsr/ Libi Lib ary Libitr^ Llbrcrj^ Ubi-arji Libi BTy Libror^ Lihi aru LltfWy Li 輛屮 Hfeiar^ Ubtar^ Uts a 3LlbiSTy Liti it JLibi CT 'JLltieryUbiery 心灯t 冋vMIJte/dm U.Ttinqghdl Ib5]l 或er 士 nf U idtei ■5,lm1kgJt5jdiiT!r3_Tf_ver ■"LMlteldJ^lkg 」二吋*阳 d.-'if!C\ i^tti 时』hdl 」b5」cytkKiH* G :jairHi^iv**lkgJr^ci<l0rFl!_wi 『Ibsjdbgrs^nfC ; t^tri ■5,lwUcgJb^!dii ,?r3_Tf_ver口 i^tei 讯 \rhdl 」b5」cytki 『前口円忙叭 FijIVfldlrgJr^cyclDnFlI.^『刚建立的work 库是空的,因为里面什么东西都没有,但是当添加了相应的文件后,编译一 次,work 就会有容了。

使用ModelSim进行仿真

使用Modelsim仿真本文档主要介绍单独用Modelsim进行FPGA仿真的具体步骤以及相关仿真文件的生成方法。

对于FPGA设计,仿真主要分为三类:功能仿真、综合后仿真和时序仿真。

功能仿真是在理想的状态下(不考虑延迟)验证电路的功能是否符合设计要求。

综合后仿真,即门级仿真,是对综合后的门级网表文件进行仿真,此时只考虑门的延时,而没有加入延时文件。

时序仿真是在综合后仿真的基础上加上延时文件,这综合考虑了设计的路径延时和门延时的情况,以验证电路在实际电路有各种延时的情况下是否有错误。

下面我们将分步骤讲解用ModelSim进行FPGA仿真的方法。

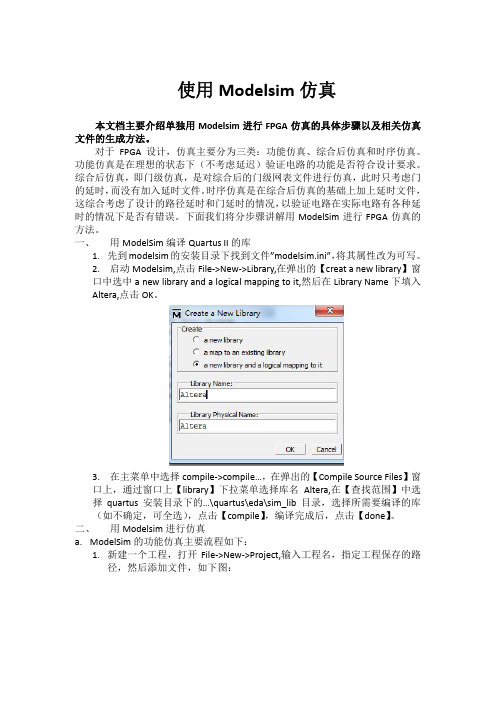

一、 用ModelSim编译Quartus II的库1.先到modelsim的安装目录下找到文件”modelsim.ini”,将其属性改为可写。

2.启动Modelsim,点击File‐>New‐>Library,在弹出的【creat a new library】窗口中选中a new library and a logical mapping to it,然后在Library Name下填入Altera,点击OK。

3.在主菜单中选择compile‐>compile…,在弹出的【Compile Source Files】窗口上,通过窗口上【library】下拉菜单选择库名Altera,在【查找范围】中选择quartus安装目录下的…\quartus\eda\sim_lib目录,选择所需要编译的库(如不确定,可全选),点击【compile】,编译完成后,点击【done】。

二、 用Modelsim进行仿真a.ModelSim的功能仿真主要流程如下:1.新建一个工程,打开File‐>New‐>Project,输入工程名,指定工程保存的路径,然后添加文件,如下图:在project的空白处,单击右键也可以再添加存在的文件或创建新的文件。

2.添加文件到工程中去。

Modelsim脚本仿真教程

Modelsim脚本仿真教程

以计数器C OUNTER为例

第1步:建立工程文件夹

在电脑中任意位置建立一个空文件夹(路径不能包含中文),把设计源代码.v文件,仿真激励文件.v,仿真脚本文件.do拷贝到该目录下。

打开Modelsim软件,点击菜单项File->Change Directory..,选择刚才建立的文件夹作为当前工程路径。

第2步:执行脚本文件

在Transcript栏中输入“do sim.do”,按回车键,执行仿真脚本文件。

如果Modelsim软件中没有出现Transcript栏,只需在菜单项选择View->Transcript即可。

第3步:在Wave窗口中观察波形

第4步:结束仿真

在菜单项选择Simulate->End Simulation即可结束当前仿真。

如若波形有错,则修改源代码或激励文件后重新执行第2步。

附件:。

Modelsim6.5基本仿真步骤

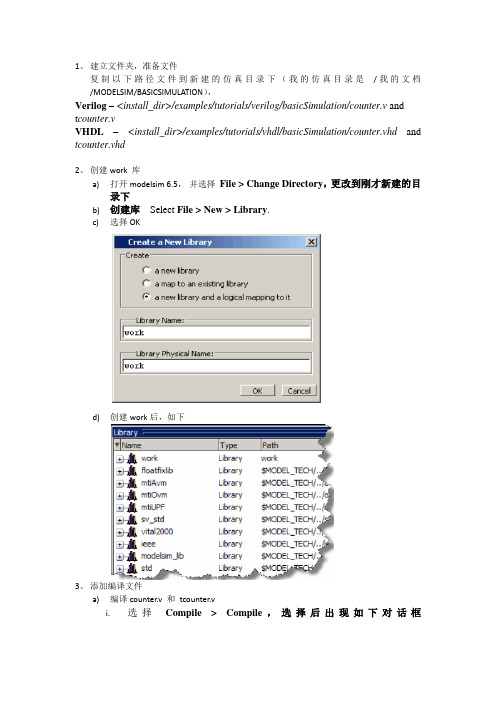

复制以下路径文件到新建的仿真目录下(我的仿真目录是/我的文档/MODELSIM/BASICSIMULATION),

Verilog–<install_dir>/examples/tutorials/verilog/basicSimulation/counter.vand tcounter.v

a)在主窗口中选择Simulate > End Simulation

b)输入命令vsim -novopt counter

14、打开之前生成的波形文件

a)输入view wave

b)选择File > Load

c)双击waveedit.do文件

15、导出刚才创建的波形

a)第一种是导出格式为HDL格式的test bench文件。

i.File > Export > Waveform

ii.选择Verilog Testbench(你用什么就选什么)

iii.如果必要的话输入1000for End Time

iv.在文件名中输入“export”然后点OK

v.

vi.通过以上步骤,modelsim就根据波形自动创建了一个名为export.v的test bench文件。

*/

for (i = 4'b0; ((carry == 4'b1) && (i <= 7)); i = i+ 4'b1)

begin

increment[i] = val[i] ^ carry;

carry = val[i] & carry;

end

end

endfunction

always @ (posedge clk or posedge reset)

modelsim仿真流程

modelsim仿真流程ModelSim6.4仿真的操作流程1. ModelSim简介ModelSim是Mentor公司的产品。

在业界,它被认为是最优秀的HDL语言仿真软件。

它提供友好的仿真环境,是支持VHDL和Verilog混合仿真的仿真器。

它采用直接优化的编译技术、T cl/Tk技术和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核。

其个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

其主要特点可概括如下:RTL和门级优化,本地编译结构,编译仿真速度快,跨平台跨版本仿真;VHDL和Verilog混合仿真;源代码模版、项目管理;集成了性能分析、波形比较、代码覆盖、数据流ChaseX、Signal Spy、虚拟对象(Virtual Object)、Memory窗口、Assertion窗口、源码窗口显示信号值、信号条件断点等众多调试功能;C和T cl/Tk接口,C调试;对SystemC的直接支持和HDL任意混合;支持SystemVerilog的设计功能;对系统级描述语言的最全面支持,SystemVerilog,SystemC,PSL;ASIC Sign off。

ModelSim分几种不同的版本:它们分别是SE、PE、LE和OEM,其中SE(System Edition)是最高级的版本,PE是版本,LE是版本,而集成在Actel、Atmel、Altera、Xilinx以及Lattice 等FPGA厂商设计工具中的均是其OEM(Original Equipment Manufacture,原始设备生产商)版本。

SE版和OEM版在功能和性能方面有较大差别,比如对于大家都关心的仿真速度问题,以Xilinx公司提供的OEM版本ModelSim XE为例,对于代码少于40000行的设计,ModelSim SE 比ModelSim XE要快10倍;对于代码超过40000行的设计,ModelSim SE要比ModelSim XE快近40倍。

Modelsim仿真流程-经验总结

Modelsim仿真流程-经验总结Modelsim仿真流程-经验总结1.Modelsim简介略。

2.modelsim仿真流程:modelsim基本的仿真流程包括建立库、建立工程并编译、仿真、调试、但在libero环境中运行modelsim时,软件自动映射库和生成工程文件。

其中功能仿真、综合仿真以及后仿真分别映射presynth、postsynth和postlayout库。

基本流程是:建立工作库→编译源代码→启动仿真→分析、调试。

2.1建立库并映射在modelsim中,任何使用VHDL、Verilog HDL、SystemC等语言实现的设计,都被编译到一个库中。

方法一:File>New>Library选择新建并映射到该库;方法二:在modelsim>提示符下运行命令vlib work2-建立库,vmap work work2-建立映射库;2.2建立工程Modelsim仿真需要建立自己的工程,同时modelsim还提供了文件夹管理工程的功能。

step1:File>New>project,并指定库文件名;step2:新建文件或导入文件;2.3编译文件建立好工程后,使用compile功能对源文件进行编译。

Libero环境启动modelsim时,系统执行run.do脚本文件自动编译源文件。

鼠标右击文件,选择compile All对所有的工程文件执行编译操作;?启动仿真,使用simulation>start simulation>选择design选项卡功能使modelsim进入仿真状态,之后可以运行仿真。

在libero 环境下,运行modelsim直接从运行仿真这一步骤开始。

运行仿真可以设置仿真时间或选择仿真全部tcl命令:do run.do –当设计修改后,使用此命令重新导入设计;Do wave.do-打开波形列表文件,或者向当前波形添加列表;Restart-复位当前仿真,从0时刻重新仿真;Run 1ms-运行仿真1ms时间;Run all-运行全部的仿真;在libero环境下,可以自己编写脚本文件代替run.do文件,在项目比较大的情况下可以大大简化仿真的操作。

modelsim 10仿真教程

Modelsim仿真教程一、前期准备1、正确安装好modelsim和quartus软件。

我用的平台的版本是Modelsim SE10.1和Quartus II10.1。

2、在ModelSim中加入Quartus提供的仿真库在ModelSim中进行仿真需要加入Quartus提供的仿真库,原因是下面三个方面:·Quartus不支持Testbench;·调用了megafunction或者lpm库之类的Altera的函数;·时序仿真要在Modelsim下做仿真。

下面以Altera器件为例,介绍如何在ModelSim中加入Altera的仿真库,Quartus II 软件中自带有Altera的仿真库,只要把它拿到ModelSim中去编译一下就可以了,具体步骤如下:(1).设置仿真库路径打开ModelSim安装目录(我用的是ModelSim SE10.1版本,安装在C:\modeltech_10.1目录下),新建文件夹altera,我们就在该目录下存放预编译的各种Altera库。

启动ModelSim SE,在主窗口执行【File】/【Change Directory】命令将路径转到altera文件夹。

(2).新建库Quartus II中提供的仿真库文件存放的路径是....\altera\10.1sp1\quartus\eda\sim_lib,每个库文件提供了两种形式:.v(Verilog)格式和.vhd(VHDL)格式两种,根据你所用的语言选择使用。

用于编译资源库的文件有220model.v,220model.vhd,220pack.vhd,altera_mf.v,altera_mf.vhd,altera_mf_components.vhd,altera_primitives.v,altera_primitives.vhd,altera_primitives_components.vhd文件。

modelsim仿真详细过程(功能仿真与时序仿真)

序,这样比较方便些。软件自带的编辑环境不是很好,使用第三方的编辑工

具是推荐的方法。建议使用UltraEdit或Notepad++这些专业的代码编辑软

件。

UltraEdit偏重于功能的强大和丰富的用户可定制化特性,而

Notepad++更加注重易用性。两者在普通功能上差异不是特别大,根据自己的

喜好选择一款即可。

图5给工程中添加文件

在路径G:\FPGA_Project\ModelSim\counter8下新建两个文件,一个

是counter8.v,一个是test_counter8.v,前者是我们的原始的设计文件,后者

是其相应的仿真测试文件。在这个路径的Windows目录下,在空白处右键选

择新建一个文本文档.TXT格式,然后在这个文件上右键选择UltraEdit或Edit

modelsim仿真详细过程(功能仿真与时序仿真)

ModelSim仿真入门:功能仿真

本实验的目的就是在ModelSim环境下学习掌握该软件的一般仿真测

试流程和仿真测试方法,另外学习编写简单的Test Bench程序并在ModelSim

下进行调试。

实验步骤如下:

1.打开ModelSim软件,如图1所示:

withNotepad++就可以启动相应的代码编辑工具进行编辑了,保存的时候注意

存成.v或格式即可。

新建一个工程,在弹出的对话框中,给该工程命名并指定一个存放的路径,

如图4所示:

图4新建工程

在这里,工程名和你的顶层文件名保持一致是推荐的做法。路径的注

意事项已经说过,这里不再提及。默认的库名就是work,这个无需更改,点

modelsim仿真详细过程

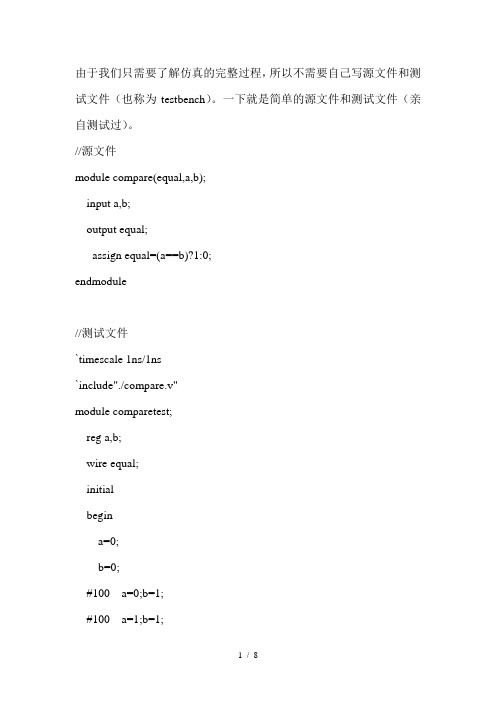

由于我们只需要了解仿真的完整过程,所以不需要自己写源文件和测试文件(也称为testbench)。

一下就是简单的源文件和测试文件(亲自测试过)。

//源文件module compare(equal,a,b);input a,b;output equal;assign equal=(a==b)?1:0;endmodule//测试文件`timescale 1ns/1ns`include"./compare.v"module comparetest;reg a,b;wire equal;initialbegina=0;b=0;#100 a=0;b=1;#100 a=1;b=1;#100 a=1;b=0;#100 $stop;endcompare compare1(.equal(equal),.a(a),.b(b));endmodule有了源文件和测试文件下面就开始用modelsim进行仿真了。

步骤一:新建工程和.v文件(也就是源文件和测试文件)打开modelsim软件,点击file,选择new—>project 然后就会弹出下面窗口:然后在project name那一栏写上工程名(随便去,一般是字母),在project location选择工程路径(路径最好没有中文,听说的),然后点OK。

进入下个界面:然后点击小框里面的“create new file”.弹出界面:在file name中写下源文件名,由于这是比较两数的大小,我取为:compare。

在“add file as type”中选择verilog,点OK,然后有:双击compare.v文件会弹出编译窗口:复制上面源文件代码,粘贴到上图右边窗口里面。

然后点击保存图标,然后再新建测试文件。

点击下图的新建文件图标。

过程如同上。

你会看见下图的两个.v文件。

步骤二:编译文件在添加文件在已建的工程后,两个文件的status都是问号,编译后就变成勾。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

由于我们只需要了解仿真的完整过程,所以不需要自己写源文件和测

试文件(也称为testbenet)。

一下就是简单的源文件和测试文件(亲自测试过)。

〃源文件

module ComPare(equal,a,b);

in PUt a,b;

OUtPUt equal;

assig n equal=(a==b)?1:0;

en dmodule

〃测试文件

'timescale 1ns∕1ns

'in elude"./COmPare.v" module COmParetest;

reg a,b;

Wire equal;

in itial

begi n

a=0;

b=0;

#100 a=0;b=1;

#100 a=1;b=1;

#100 a=1;b=0; #100 $stop; end

COmPare ComPare1(.equal(equal),.a(a),.b(b)); en dmodule

有了源文件和测试文件下面就开始用

modelsim 进行仿真了

步骤一:新建工程和∙v 文件(也就是源文件和测试文件) 打开modelsim 软件,点击file ,选择new — >project 然后就会弹

出下面窗口:

reα a

Wire iniEi begin a≡0 b=o

≠ιoo

≠100 #100 ≠100

end

-all I -CcIlltinUe I -finish I -iπit I -next I -SteP I -OVer

s√4* 1 ⅛ ι m a i m i

然后在PrOjeCt name 那一栏写上工程名(随便去,一般是字母),在

PrOjeCt location 选择工程路径(路径最好没有中文,听说的),然后点 OK 。

进入下个界面:

l

..∕sy nops¥E

仁/sv 」Id

∖.∣sl

...5t =A J, '■■M

'.Jn '..∕□J

CotnPare endmod

口

*

Module. V M

Create new file” •弹出界面:

然后点击小框里面的“

HelP I Colur™ILaVoUt AlICOLUJl∏3

l⅛⅝l Project - E:/SirTI∕lx4∕compare

StatugType ]θrd 皀{l⅜di⅜ecj

Γ⅛me

IM I COmPareHV

5

双击

GGmPare.v 文件会弹出编译窗口:

Ln-S

module GOInPdre (equal t IrLPUt a, t ; output equal ;

ASSign equal≡{a≡≡b) ?

e τιdι∏Q dule

复制上面源文件代码,粘贴到上图右边窗口里面

IIt WindOW HeIP

]>] ⅛

I M J E⅛m∕lχ4∕QQ<nPare l V i+ X

然后点击保存图标,然后再新建测试文件。

点击下图的新建文件图标过程如同上。

你会看见下图的两个.v文件

:i ⅛Λ(I∣梧式© ZMCD 表格(Δ)奇口辿)⅛⅛(W 办公兰闫医

j⅛∣ModelSim SE IO r Oa

存>单*| 韦耒ITILda⅜E Add ProjeCt Toerl5

Lay

H ⅛

b

LaVtMJt I7Q I⅞3▼

Y∞t [AllColumna

l'⅜ Project -E:/Sim∕lχ4∕c□n∏i>are ------ R COmPaire a V

步骤二:编译文件

HeJ

P d 2J

V J erilog 1 08/10/12 08:53:12 PM

VeriIog 0 0S∕10∕12 08≈52≈54PM

在添加文件在已建的工程后,两个文件的StatuS都是问号,编译后就变成勾。

具体步骤为:

点击compile all图标就可以了。

I^IUUUUiAI U UlU I

「

6⅛Γ~1∣

Cmncsl ∣

步骤三:仿真,添加波形

选中compare”文件,点击仿真图标如下图:

接着会弹出界面:

Work

E ; /sIrTI ι∕tχ4∕testcompare. V E ; ⅛∣m ⅛χ4∕√c□mpare , V

SWODa_TECH/..何 ta ∣ ZClOo 5MODEL JΓECH∕../VeriiOg SMODELJTECH/. ./synopsyE

SMODELJTECH /. √s V -Std SMODELJrEeH /. ./std_de Vekjperskit 5MODELJTECHΛ√≡td

ResOIUtIon

[default ▼

OPtInnIZatiOn

I - Enable optimization

M Stalrt Simulation

DeSlgn

VHCL ] Verilog ] LibrarieS ] SDF ] OtherS

√>l

T

Nanne P TyPe Path

十血L WWk

J

I c□mparctEst

HJ compare vita ∣20∞ verilog SynOPSyS 5√-≡td

StCl_de v eloperskit

Lbrary r<iodJe M□dde LiJrarV Litrary Library Lbrary Lbrary Library

Design Unlt(S)

选中 ComPareteSt 点击 OK ,有:

•] 4 ÷ * 3 Sff f 1 αi ⅛ IlEEB ta©

∣ [⅞ <⅛ 1». <⅛ ∣ [Y ⅛ ÷l -i ^i∙⅛. ≡

0^ |

做徹歡缺鱼

Lsyour SJJsLlLate

d Trarfiatrt ---------------------------------------------------------------------------------------------------------- ■:

t LciAdLELg Wcirk b 亡亡珂:白上巴二己9匕

# Soeiin 百 WSriC-CQ3φiBFC -

VSrM 73A

选中COmPareI 右击鼠标,选择add,继续选择To Wave.我用的是10.0a 版本,还要选择all items in region.然后就有界面:

□ ∙G ⅛H & 冬庇醪口二 ⅛⅝ gz ¾ ⅛⅛S⅛ β ⅛5

倉 ⅛g 〒香 **∣Ef ∣

i32¾⅛⅛⅛⅛⅛⅛[¾⅛⅛∣l⅛ 护存 T⅛ ” 範 包| 迎| 旳

I ⅛旦鱼]垂丨劭

Jr 占 玉一二L .E 』*吨i ・樹⅛⅝ |]辭I 孙|]亀 Q 毎疑f ¾ H ΓL JJ ・H ■ F J

C⅛⅛κ⅛a⅞,WJ⅛ AlICalU±ιn±

ITrO [« [□ ΛLL ∣>⅛

M 谢醪闻⅛⅛冷啜囹忌|冷

Cnmpefel 蠢 UNEALfffi

∣!¾

t¥arn_QPaar >■:?

CDfnParE MDdLJE

Pracesa

FOrelgn

Oi PraCX l SSu. MbdhRiI j^iuG

—-H i! K

IT J Nam

ITyPe CNteretO ∣5⅝ate * #]NmMS6

EtiaJ

RC a dF

Jl

J

S⅛ Xl ~^Γ∣Jf

W⅛ve

M ∣ Wave

M ModdSlirrl SE 10.0⅛

File Edit 里lew £01TlPile SimUIate A l dd StrUCtUFe TQOlS Layout Window HeIP

b⅞s⅞^nc

e

:⅛sr M⅛κSJc

Mi E: ⅛m ∣⅛3∕dk βιtop s v

5* I

J

elwsys⅜■■ cIlt 匚YdU 匚ILk Inl⅞ZQI

mo*dul< Clk^top; reg CIk Ir

re3e<: MIre clk , QUt :;

h

t11πe3cale IIIa/IOps

File Edit VieW Add FDrrTbeIi TeelS WinIdiaW

点击run图标就会出现仿真波形。