基于DDS的数字移相信号发生器

基于DDS的数字移相正弦信号发生器的设计

基于DDS的数字移相正弦信号发生器的设计

肖炎根

【期刊名称】《电子元器件应用》

【年(卷),期】2009(11)12

【摘要】给出了采用DDS设计思路和FPGA+MCU来设计一款数字移相正弦信号发生器的具体方法.本系统只存储0-π/2的采样值,然后通过变换得到0-2π的采样值,从而节约了波形存储器的容量.另外,系统还在相位累加器输出的相位序列上加入了随机抖动序列,从而降低了DDSS相位截断误差带来的杂散.

【总页数】4页(P53-55,58)

【作者】肖炎根

【作者单位】株洲职业技术学院电子工程系,湖南,株洲,412001

【正文语种】中文

【中图分类】TN6

【相关文献】

1.基于DDS与数字电位器的正弦信号发生器设计 [J], 孙莹莹;卢京阳;刘思久;贲洪奇

2.基于FPGA的DDS移相变频正弦信号发生器设计 [J], 杨春红;李石

3.基于单片机的数字式可移相正弦信号发生器设计 [J], 刘晓艳;杨宁

4.DDS数字移相正弦信号发生器的设计 [J], 高银;林其伟

5.基于DDS技术的数字移相正弦信号发生器的CPLD设计与仿真 [J], 雷能芳;苏变玲

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DDS的数字移相信号发生器

R G 4的高 1 E 3 O位输 出作为 P A路 R M与 P O B路 A D R 0的 D E 1

图 1 基 于 D S的数 字 移 相 信 号 发 生器 的原 理 图 D

输入 , 在此 , 将该输 出称为 D, D一方面作为一个 R M 的地址 O 端, 决定读取 R M的内容 , O 也就是 F U 。D另 一方 面与输人 OT

一

直 接 数 字 频 率 合 成 D S ( ic it r un y D Dr tDga Fe e c e il q Snhs e)是一种采用数字化技术、通过控制相位的变化速 yt ir ez

出, 完成一个周期性的动作 , 这个周期就是 D S合成信号 的一 D 个周期。

1 D S 相 的 实现 . 2 D 移 器 件 采 用 美 国 A T R 公 司 的 F G ( yl e LE A P A C c n o E 1 6 20 6 芯 片 来 实 现 。 于 A ea yl e P C Q 4 C PC Q 4C ) 对 h r c n I 6 2 0 6 C o E 的 应 用 开发 使 用 A e h r 司 的 E A开 发 软 件 ( ur s1 .) a公 D Q au一1 0 。 t 5

图 2:

1 基 于 D S的数 字移 相信 号发生 器 D

11 基 于 D S的数 字 移 相 信 号 发 生器 的工 作 原 理 . D

该 移相 信 号 发 生 器 是 基 于 D S技 术 而 实 现 的 ,其 原 理 框 D

图如 图 l 。 图 2 基 于 D S的 数 字移 相 信 号 发 生器 的 设 计 框 图 D 系 统 由一 个 3 加 法 器 ( D E 3 )一 个 3 寄 存 器 4位 A D R4、 4位

移相信号发生器实验

移相信号发生器设计实验 一、数字移相正弦信号发生器设计1. 实验目的:学习直接数字综合器DDS及基于此模块的数字信号发生器的设计和实现。

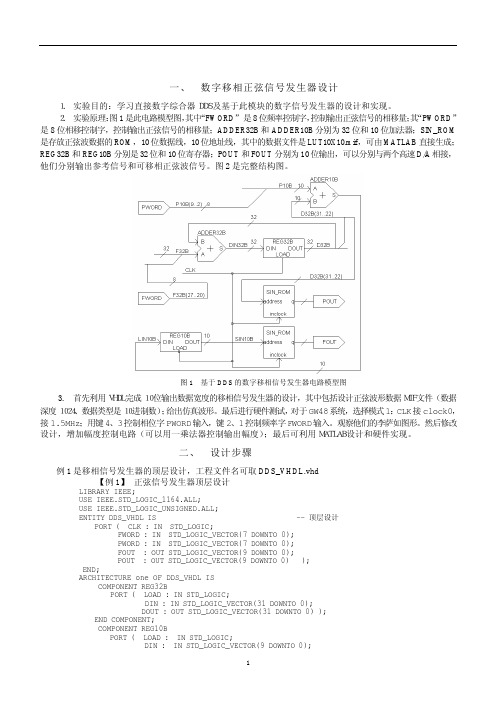

2. 实验原理:图1是此电路模型图,其中“FWORD”是8位频率控制字,控制输出正弦信号的相移量;其“PWORD”是8位相移控制字,控制输出正弦信号的相移量;ADDER32B和ADDER10B分别为32位和10位加法器;SIN_ROM 是存放正弦波数据的ROM,10位数据线,10位地址线,其中的数据文件是LUT10X10.mif,可由MATLAB直接生成;REG32B和REG10B分别是32位和10位寄存器;POUT和FOUT分别为10位输出,可以分别与两个高速D/A相接,他们分别输出参考信号和可移相正弦波信号。

图2是完整结构图。

图1 基于DDS的数字移相信号发生器电路模型图 3. 首先利用VHDL完成10位输出数据宽度的移相信号发生器的设计,其中包括设计正弦波形数据MIF文件(数据深度1024、数据类型是10进制数);给出仿真波形。

最后进行硬件测试,对于GW48系统,选择模式1:CLK接clock0,接1.5MHz;用键4、3控制相位字PWORD输入,键2、1控制频率字FWORD输入。

观察他们的李萨如图形。

然后修改设计,增加幅度控制电路(可以用一乘法器控制输出幅度);最后可利用MATLAB设计和硬件实现。

二、设计步骤例1是移相信号发生器的顶层设计,工程文件名可取DDS_VHDL.vhd【例1】正弦信号发生器顶层设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DDS_VHDL IS -- 顶层设计PORT ( CLK : IN STD_LOGIC;FWORD : IN STD_LOGIC_VECTOR(7 DOWNTO 0);PWORD : IN STD_LOGIC_VECTOR(7 DOWNTO 0);FOUT : OUT STD_LOGIC_VECTOR(9 DOWNTO 0);POUT : OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );END;ARCHITECTURE one OF DDS_VHDL ISCOMPONENT REG32BPORT ( LOAD : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );END COMPONENT;COMPONENT REG10BPORT ( LOAD : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(9 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );END COMPONENT;COMPONENT ADDER32BPORT ( A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );END COMPONENT;COMPONENT ADDER10BPORT ( A : IN STD_LOGIC_VECTOR(9 DOWNTO 0);B : IN STD_LOGIC_VECTOR(9 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );END COMPONENT;COMPONENT SIN_ROMPORT ( address : IN STD_LOGIC_VECTOR(9 DOWNTO 0);inclock: IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR(9 DOWNTO 0));END COMPONENT;SIGNAL F32B : STD_LOGIC_VECTOR(31 DOWNTO 0);SIGNAL D32B : STD_LOGIC_VECTOR(31 DOWNTO 0);SIGNAL DIN32B : STD_LOGIC_VECTOR(31 DOWNTO 0);SIGNAL P10B : STD_LOGIC_VECTOR( 9 DOWNTO 0);SIGNAL LIN10B : STD_LOGIC_VECTOR( 9 DOWNTO 0);SIGNAL SIN10B : STD_LOGIC_VECTOR( 9 DOWNTO 0);BEGINF32B(27 DOWNTO 20)<=FWORD ; F32B(31 DOWNTO 28)<="0000";F32B(19 DOWNTO 0)<="00000000000000000000" ;P10B( 9 DOWNTO 2)<=PWORD ; P10B( 1 DOWNTO 0)<="00" ;u1 : ADDER32B PORT MAP( A=>F32B,B=>D32B, S=>DIN32B );u2 : REG32B PORT MAP( DOUT=>D32B,DIN=> DIN32B, LOAD=>CLK );u3 : SIN_ROM PORT MAP( address=>SIN10B, q=>FOUT, inclock=>CLK );u4 : ADDER10B PORT MAP( A=>P10B,B=>D32B(31 DOWNTO 22),S=>LIN10B );u5 : REG10B PORT MAP( DOUT=>SIN10B,DIN=>LIN10B, LOAD=>CLK );u6 : SIN_ROM PORT MAP( address=>D32B(31 DOWNTO 22), q=>POUT, inclock=>CLK );END;1、创建工程和编辑设计文件首先建立工作库目录,以便设计工程项目的存储。

数字移相信号发生器设计说明书

课程设计任务书(指导教师填写)课程设计名称现代电子系统课程设计学生姓名专业班级设计题目数字移相信号发生器设计一、课程设计目的掌握数字移相信号发生器的工作原理和设计方法;掌握DDS技术的工作原理;掌握GW48_SOPC实验箱的使用方法;了解基于FPGA的电子系统的设计方法。

二、设计内容、技术条件和要求基于DDS技术利用VHDL设计并制作一个数字式移相信号发生器。

(1)基本要求:a.频率范围:1Hz~4kHz,频率步进为1Hz,输出频率可预置。

b.A、B两路正弦信号输出,10位输出数据宽度c.相位差范围为0~359°,步进为1.4°,相位差值可预置。

d.数字显示预置的频率(10进制)、相位差值。

(2)发挥部分a.修改设计,增加幅度控制电路(如可以用一乘法器控制输出幅度)。

b.输出幅度峰峰值0.1~3.0V,步距0.1Vc.其它。

三、时间进度安排布置课题和讲解:1天查阅资料、设计:4天实验:3天撰写报告:2天四、主要参考文献何小艇《电子系统设计》浙江大学出版社2008.1潘松黄继业《EDA技术实用教程》科学出版社2006.10王勇《EDA》实验指导书电工电子实验教学中心2006.8指导教师签字:2009年12月14日摘要在现代的信号分析和处理领域,高精度的频率和相位测量非常重要,它是理论和工程分析的重要工具。

使用模拟或数字示波器测量频率,是我们最常用的方法,同时也是不是很精确的方法;同时如果要测量两路信号的相位差,使用示波器又不是很方便。

而且示波器的价格最低需要几千元,对于普通人来讲不是最佳选择。

在本文中,我们设计了一个数字移相信号发生器设计。

主要分为如下几个部分:●键盘和显示模块:用键盘输入,数码管显示频率控制字和相位控制字。

采用按键复用的方法。

●数字DDS模块:分为频率合成模块和相位合成模块。

具体的方案论证将在下面进行。

●时钟模块:由于系统需要时钟频率和实验箱上的不匹配,需要频率变换,具体的方案论证将在下面进行。

基于AVR单片机和FPGA实现DDS的数字式移相信号发生器设计方案

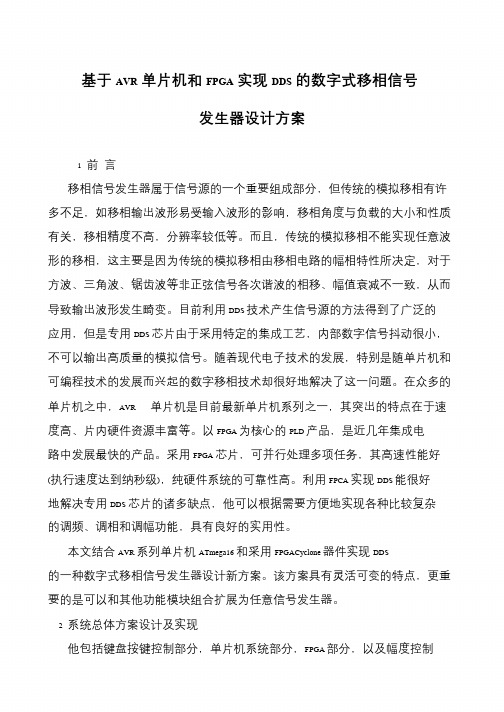

基于AVR单片机和FPGA实现DDS的数字式移相信号发生器设计方案1 前言移相信号发生器属于信号源的一个重要组成部分,但传统的模拟移相有许多不足,如移相输出波形易受输入波形的影响,移相角度与负载的大小和性质有关,移相精度不高,分辨率较低等。

而且,传统的模拟移相不能实现任意波形的移相,这主要是因为传统的模拟移相由移相电路的幅相特性所决定,对于方波、三角波、锯齿波等非正弦信号各次谐波的相移、幅值衰减不一致,从而导致输出波形发生畸变。

目前利用DDS 技术产生信号源的方法得到了广泛的应用,但是专用DDS 芯片由于采用特定的集成工艺,内部数字信号抖动很小,不可以输出高质量的模拟信号。

随着现代电子技术的发展,特别是随单片机和可编程技术的发展而兴起的数字移相技术却很好地解决了这一问题。

在众多的单片机之中,AVR 单片机是目前最新单片机系列之一,其突出的特点在于速度高、片内硬件资源丰富等。

以FPGA 为核心的PLD 产品,是近几年集成电路中发展最快的产品。

采用FPGA 芯片,可并行处理多项任务,其高速性能好(执行速度达到纳秒级),纯硬件系统的可靠性高。

利用FPCA 实现DDS 能很好地解决专用DDS 芯片的诸多缺点,他可以根据需要方便地实现各种比较复杂的调频、调相和调幅功能,具有良好的实用性。

本文结合AVR 系列单片机ATmega16 和采用FPGACyclone 器件实现DDS 的一种数字式移相信号发生器设计新方案。

该方案具有灵活可变的特点,更重要的是可以和其他功能模块组合扩展为任意信号发生器。

2 系统总体方案设计及实现他包括键盘按键控制部分,单片机系统部分,FPGA 部分,以及幅度控制。

基于DDS的数字移相信号发生器

基于DDS的数字移相信号发生器摘要频率源是雷达、通信、电子对抗与电子系统实现高性能指标的关键,很多现代电子设备和系统的功能都直接依赖于所用频率源的性能,因此频率源被人们喻为众多电子系统的“心脏”。

而当今高性能的频率源均通过直接数字频率合成(DDS)技术来实现。

直接数字式频率合成技术DDS(Direct Digital Synthesis)是新一代的频率合成技术,它采用数字控制信号的相位增量技术,具有频率分辨率高,频率切换快,频率切换时相位连续和相位噪声低以及全数字化易于集成等优点。

本文首先对信号发生器以及DDS的发展和现状进行了归纳叙述。

其次对DDS的原理及其输出信号的性能进行了分析。

再次通过对系统的分析,总结归纳出了系统的硬件结构,硬件主要由FPGA芯片、数模转换电路、幅度调节电路、功率放大电路和输入、显示电路组成。

采用FPGA实现了正弦信号发生器,信号发生器主要由累加器和ROM查询表组成,可由频率和相位控制字使信号发生器的输出改变。

最后完成了软件和硬件的设计和调试,对实验样机进行了测试,结果显示的数据基本能够达到输出频率变化围在4.992kHz—1272.96kHz,输出幅度为1.8V—2.1V的设计要求。

关键词直接数字频率合成器;信号发生器;现场可编程门阵列word格式.Digital Phase Shifter Signal Generator Base on DDSAbstractThe frequency source is the radar, the correspondence,the electronic countermeasure and the electronic system realization high performance target key, the very many modem electronic installation and the system function all directly relies on in uses the frequency source the performance,therefore the frequency source is explained by the people for the multitudinous electronic system” the heart”.But the high performance frequency source realizes now through the direct digital frequency synthesizes(DDS).Direct digital synthesizing is a new frequency synthesizing technology, which adopts phase increment controled by digital. It has so many virtues such as high frequency resolving, fast frequency switching ability, continuous phase, low phase noise and integration easily for its digital operation.This article first DDS signal generator, as well as the development and summarized description of the status quo. Second, the principle of the DDS output signal and its performance analyzed. Again through the system analysis, a summary of the system's hardware architecture, hardware mainly by the FPGA chip, digital-to-analog conversion circuit, the rate adjustment circuit, power amplifier circuit and input, display circuit. The use of FPGA realization of a sinusoidal signal generator, signal generator by the accumulator and ROM look-up table composed by the word frequency and phase control signal generator so that the output change. Finally completed the hardware and software design and debugging of the experimental prototype has been tested, the data the results showed shows that it is able to meet the design requirements of frequency range between 4.992kHz and 1272.96kHz and output range between 1.8V and 2.1V.Keywords DDS;Signal Generating;FPGAword格式.目录摘要 (I)Abstract ........................................................... I I第1章绪论 (1)1.1 信号发生器技术 (1)1.2 频率合成技术 (2)1.2.1 频率合成技术概述 (2)1.2.2 频率合成技术的发展 (2)1.2.3 DDS研究现状及意义 (3)1.3 FPGA在DDS技术实现 (4)1.4 论文主要研究容 (5)第2章 DDS技术 (6)2.1 DDS频率合成的原理与结构 (6)2.1.1 DDS的基本原理 (6)2.1.2 DDS的结构 (7)2.1.3 DDS的工作特点 (9)2.2 DDS的频谱分析 (9)2.3 DDS的杂散特性分析 (10)2.3.1 相位截断产生的杂散 (10)2.3.2 幅度量化产生的杂散 (12)2.3.3 DAC转换误差产生的杂散 (12)2.3.4 其他噪声源带来的杂散 (13)2.4 DDS的优点和不足 (13)2.5 本章小结 (14)第3章信号发生器系统的硬件设计 (15)3.1 系统硬件总体设计 (15)3.2 FPGA芯片 (15)3.3 数模转换电路 (17)3.4 幅度调节电路 (19)3.5 功率放大电路 (19)3.6 时钟电路 (21)3.7 电源电路 (21)3.8 键盘输入电路 (22)3.9 LED显示电路 (23)3.10 电路抗干扰措施 (24)3.11 本章小结 (25)word格式.第4章基于FPGA的系统实现及测试 (26)4.1 FPGA的总体设计 (26)4.2 FPGA的模块 (28)4.3 FPGA的编辑及下载 (33)4.4 系统的测试 (34)4.4.1 时序仿真 (34)4.4.2 嵌入式逻辑分析仪的使用 (34)4.4.3 硬件的测试 (35)4.5 本章小结 (35)结论 (37)致 (38)参考文献 (39)附录A (41)附录B (46)附录C (51)word格式.第1章绪论1.1信号发生器技术信号发生器作为一种常用的信号源,在现代通信领域和测量领域得到广泛的应用,例如:电子测量、产品检修以及各种电类实验室等。

数字移相信号发生器设计

分类号编号XXXXXX本科毕业论文(设计)基于DDS的数字移相信号发生器设计Design of digital phase shifted signal generator based on DDSXXX指导教师姓名单位名称及地址专业名称论文提交日期论文答辩日期答辩委员会主席论文评阅人XX年XX 月XX 日XXXX大学本科毕业设计(论文)任务申请书承担指导任务单位XXXX 导师姓名XXX导师职称X带教学生人数 1 专业X 年级X级论文题目基于DDS的数字移相信号发生器设计题目分类1.应用与非应用类:〇工程〇科研○√教学建设〇理论分析〇模拟2.软件与软硬结合类:〇软件〇硬件○√软硬结合〇非软硬件(1、2类中必须各选一项适合自己题目的类型在〇内打√)主要内容1.掌握数字移相信号发生器的工作原理和设计方法;2.基于DDS设计实现一个频率、相位可控的数字信号发生器。

主要技术指标1.输出两路正弦信号,由两路10位D/A实现波形输出;2.频率范围:1Hz~4kHz,频率步进为1Hz,输出频率可预置。

实施要求1.具备EDA技术的基础知识;2.具备数字电路和编程基础。

主要参考文献:1.潘松黄继业,EDA技术使用教程科学出版社2005. 2.COMS集成电路国防工业出版社1985.3.阎石,数字电子技术基础,高等教育出版社2000. 4.白居宪,直接数字频率合成,西安交通大学出版社2007.开题时间XXXX年X月完成时间XXXX年X月系所(单位)审定意见:系所(单位)主官签字:年月日教学指导委员会审定意见:教学指导委员主任委员签字:年月日摘要随着现代电子技术的发展,数字式信号发生器的应用越来越广泛。

本文介绍了一种以DDS为基本单元的数字移相信号发生器的设计方法。

设计采用直接数字频率合成(DDS)技术,利用FPGA芯片及D/A转换器,实现了一个频率、相位可控的正弦信号发生器。

直接数字频率合成(DDS)技术是一种新型频率合成技术,所产生的信号具有频率分辨率高、频率切换速度快、频率切换时相位连续、输出相位噪声低和可以产生任意波形等诸多优点。

基于DDS信号发生器的设计

基于DDS信号发生器的设计基于DDS(Direct Digital Synthesis)信号发生器的设计是一种使用数字技术生成模拟信号的方法。

DDS信号发生器采用数字频率合成技术,具有频率范围广、频率分辨率高、频率稳定性好等优点,被广泛应用于通信、测量、无线电频率合成等领域。

在本文中,将详细介绍基于DDS信号发生器的设计方案。

一、DDS信号发生器的基本原理DDS信号发生器利用数字技术生成模拟信号,主要由时钟、相位累加器(Phase Accumulator)、相位调制器(Phase Modulator)和数模转换器(Digital-to-Analog Converter)等部分组成。

其基本原理如下:1.时钟:提供稳定的时钟信号,作为DDS信号发生器的时间基准。

2.相位累加器:接收时钟信号,用于累加相位增量,并生成数字相位信息。

3.相位调制器:将数字相位信息转换为模拟的、连续的相位信息。

4.数模转换器:将相位信息转换为模拟信号,并提供给外部使用。

二、基于DDS信号发生器的设计方案1.频率范围:DDS信号发生器的频率范围应满足实际应用需求。

一般DDS芯片的频率范围为几千Hz到几百兆Hz,可以选择适当的芯片。

2.频率分辨率:DDS信号发生器的频率分辨率应足够高,能够满足对精细频率调整的需求。

一般DDS芯片的频率分辨率为1Hz或更高。

3.频率稳定性:DDS信号发生器的频率稳定性应较高,能够保证频率输出的准确性和稳定性。

可以通过选择高质量的时钟源来提高频率稳定性。

4.输出波形:DDS信号发生器可以生成多种波形,如正弦波、方波、三角波、锯齿波等。

设计时应根据应用需求选择适合的波形。

5.控制接口:DDS信号发生器通常需提供控制接口,如USB、串口、以太网等,方便用户对信号发生器进行控制和调整。

设计方案可以按以下步骤进行:1.选择DDS芯片:根据需求选择合适的DDS芯片,如AD9850、AD9833等。

2.系统架构设计:根据芯片和性能要求设计系统架构,包括时钟源、数模转换器、滤波电路等。

FPGA基于DDS的移相调频调幅信号发生器..

《EDA》课程设计报告实验题目:基于DDS的数字移相信号发生器基于DDS的数字移相信号发生器一、课程设计目的1、进一步熟悉Quartus Ⅱ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

二、设计任务1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

2、完成8位输出数据宽度的频率可调的移相三角波、方波信号发生器。

3、以上三种波形使用一个按键依次切换。

4、波形发生器实现幅度可调。

5、信号发生器的原始数据存储在外部存储器里,由FPGA进行读取,经过D/A转换输出,由示波器观察最终结果。

三、基本原理直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图 1 直接数字频率合成器原理图其中K为频率控制字, fc为时钟频率,N为相位累加器的字长,D为ROM数据位及D/A 转换器的字长。

相位累加器在时钟 fc的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= fc K/2n,f0为输出频率,fc 为时钟频率。

当K=1时,DDS输出最低频率(也既频率分辩率)为fc /2nDDS的最大输出频率由 Nyguist 采样定理决定,即fc /2,也就是说K的最大值为2n-1.因此,只要N足够大,DDS可以得到很细的频率间隔。

基于DDS的移相正弦信号发生器设计

基于DDS 的移相正弦信号发生器设计一. 设计原理1.1 利用DDS 产生正弦波信号的工作原理由DDS 产生频率、相位可控制的正弦波。

频率累加器对输入信号进行累加运算, 产生频率控制数据M( 或相位步进量)。

读出的数据送入D/A 转换器和低通滤波器以恢复实际波形。

频率控制字M 和相位控制字分别控制DDS 输出正(余)弦的频率和相位。

DDS 系统的核心是相位累加器, 它由一个累加器和一个N 位相位寄存器组成。

每来一个时钟脉冲, 相位寄存器以步长M 增加。

相位寄存器的输出与相位控制字相加, 其结果作为正(余)弦查找表的地址。

ROM 查找表中储存着一个完整周期的正弦波数字幅度信息, , 每个查找表的地址对应正弦波中O 一360度范围中的一个相位点。

ROM 查找表把输入的地址信息映射成正(余)弦幅度信号, 同时输出数模转换器(DAC)的输入端, DAC 输出的模拟信号经过低通滤波器(LPF), 可得到一个频谱纯净的正(余)弦波。

从而实现正弦波信号的产生。

直接数字合成DDS 的可移相数字信号发生器原理图:1.2 DDS 的数字移相原理DDS 技术的核心是相位累加器, 它类似一个计数器.每来一个时钟信号, 相位累加器的输出就增加一个步长的相位增量, 相位增量的大小由频率控制字确定.经DDS 输出的信号可描述为)2sin()sin(t f A wt A S out out π== (1)其中, Sout 为经DDS 输出的信号, fout 为对应的输出频率, 时间t 是连续的。

为便于数字逻辑描述该表达式, 需进行离散化处理, 用基准时钟信号clk 进行抽样, 设正弦信号的相位φ= 2πfout t , 而在一个时钟周期Tclk 相位φ变化量为clkout clk out f f T f ππφ22==∆ (2) 式(2)中, fclk 是clk 的频率, 对于2π可以看成是满相位的1为了对输出的相位进行控制, 通过一个常数P 来实现, 而每个clk 周期的相位增量Δθ用P 来表示, 即Δθ= P ·Δφ式1 与式(2) 联立可得clkout f f P πθ2⋅=∆ (3) 显然, 信号发生器的输出可描述为)sin().sin(θφφφ∆+=∆+=A p A S out上式中, φ代表正弦信号发生器原始相位值, 可看出, 对相位值进行简单的累加运算, 就可以得到正弦信号当前相位值, 也就得到了DDS 输出的正弦信号。

基于DDS技术的数字移相信号发生器的设计及FPGA的实现

基于DDS技术的数字移相信号发生器的设计及FPGA的实现张妍;陈涛;石蕊;梁晔

【期刊名称】《信息通信》

【年(卷),期】2014(000)011

【摘要】直接数字频率合成(DDS)技术采用全数字的合成方法,所产生的信号分辨率高、频率切换速度快、频率切换时相位连续并可以产生任意波形。

本设计在理论上对DDS的原理及其输出信号的性能进行了分析,采用VHDL语言编写出数字移相信号发生器设计程序,并在QuartusII软件环境中,对编写的程序进行了仿真,得到了很好的效果,各项性能指标达到了实验要求。

【总页数】1页(P59-59)

【作者】张妍;陈涛;石蕊;梁晔

【作者单位】兰州城市学院培黎工程技术学院,甘肃兰州730070;中核兰州铀浓缩有限公司,甘肃兰州730065;兰州城市学院培黎工程技术学院,甘肃兰州730070;兰州城市学院培黎工程技术学院,甘肃兰州730070

【正文语种】中文

【中图分类】TP332.3

【相关文献】

1.基于FPGA与MSP430的单相数字移相系统的设计与实现 [J], 黄成;朱亮;肖伟翔

2.基于直接数字频率合成的三角载波移相PWM控制FPGA的设计实现 [J], 诸江;

董金明

3.基于直接数字频率合成的三角载波移相PWM控制FPGA的设计实现 [J], 诸江;董金明

4.基于DDS技术的数字移相正弦信号发生器的CPLD设计与仿真 [J], 雷能芳;苏变玲

5.基于FPGA的移相时钟数字内插TDC电路设计与实现 [J], 刘景岩;路美娜;王羿;蔡伟杰;宋茂新;洪津

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DDS技术的信号发生器讲解

现代电子学实验报告实验题目:基于DDS技术的信号发生器姓名:陈思年级: 2010级电子信息科学与技术指导教师:马莉完成日期: 2013.10.10原创性声明本人声明本实验报告涉及的电路图、程序代码均为自己设计,没有抄袭他人的成果。

特此声明!声明人:陈思摘要 (1)1. 实验目的 (2)2. 实验原理及内容 (2)2.1实验的总体结构 (2)2.2 实验的理论基础和原理 (3)3. 实验内容 (4)4. 实验设计与测试 (5)4.1 频率控制模块 (5)4.2 按键选择模块 (7)4.3 正弦波信号产生模块 (8)4.4 总体测试 (13)5. 实验结论与测试 (14)参考文献 (15)摘要函数信号发生器简介在频率合成(Fs,Frequency Synthesis)领域中,直接数字合成(Direct Digital Synthesis—DDS)是近年来新的FS技术。

单片集成的DDS产品是一种可代替锁相环的快速频率合成器件。

因其精度高、变换频率快、输出波形失真小成为优先选用技术。

具体体现在频带宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。

DDS以稳定度高的参考时钟为参考源,通过精密的相位累加器和数字信号处理,通过高速D/A变换器产生所需的数字波形(通常是正弦波形),这个数字波形经过一个模拟滤波器后,得到最终的模拟信号波形。

函数信号发生器在生产实践和科技领域有着广泛的应用。

本设计是采用了EDA 技术设计的函数信号发生器。

此函数信号发生器的实现是基于VHDL语言描述各个波形产生模块,然后在QuartusⅡ软件上实现波形的编译,仿真和下载到Cyclone芯片上。

基于DDS技术的信号发生器1. 实验目的1. 掌握DDS频率合成原理;2. 掌握正弦信号产生的原理;3. 掌握MCU8951 IP核合成任意频率脉冲信号的设计;4.掌握给定一个频率字或相位字用按键改变频率合成正弦信号的设计。

根据DDS的数字移相信号发生器

EDA课程设计课题名称_ 基于DDS的数字移相信号发生器专业_ 电子信息工程____ _ _ 班级_____ _________ __ __ 学号_姓名_ __ __ 成绩_____ ____________ _指导教师___ _ ___ ___2014年5 月7日一、课程设计目的 (3)二、设计任务 (3)三、工作原理及模块分析 (3)1、频率预置与调节电路 (4)2、累加器 (4)3、波形存储器 (5)4、D/A转换器 (5)四、相关程序 (5)1、加法器 (5)(1)ADD10 (5)(2)ADD32 (7)2、寄存器 (9)(1)REG10B (9)(2)REG32B (11)3、ROM (13)4、主程序 (16)五、仿真结果: (20)六、引脚配置和下载 (20)七、实验心得 (22)一、课程设计目的1、进一步熟悉Quartus Ⅱ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM_ADD_SUB、LPM ROM、LPM_FF 的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计二、设计任务完成10位输出数据宽度的频率可调的移相正弦信号发生器,通过按键调节频率和初始相位,实现相位和频率可调的正弦信号发生器三、工作原理及模块分析直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:fc图1直接数字频率合成器原理图其中K为频率控制字,fc为时钟频率,N为相位累加器的字长,D为ROM 数据位及D/A转换器的字长。

相位累加器在时钟fc的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

基于dds技术的信号发生器设计与实现

基于dds技术的信号发生器设计与实现基于DDS技术的信号发生器设计与实现1、引言信号发生器是电子测试与测量领域中的重要仪器之一,用于产生各种形式的信号,以供电子设备的测试、校准和研发使用。

传统的信号发生器通常采用模拟电路设计,存在精度不高、调节麻烦等问题。

而基于Direct Digital Synthesis (DDS) 技术的信号发生器,能够以数字方式生成精确的任意波形信号,具备灵活性、精度高、调节方便等特点。

本文将重点探讨基于DDS技术的信号发生器的设计与实现。

2、DDS技术原理DDS技术是一种通过数字方式生成任意波形信号的技术,其核心是一个快速数字频率合成器 (NCO)。

NCO通过参考频率和累加器的相位变化,生成具有不同频率、相位和幅度的数字信号,然后通过数字模拟转换器 (DAC) 将数字信号转换为模拟信号输出。

DDS技术的关键在于通过调整参考频率和相位累加器的步进值,可以在很短的时间内生成高精度和高稳定度的任意波形信号。

3、基于DDS技术的信号发生器设计在设计基于DDS技术的信号发生器时,需要考虑以下几个关键要素:3.1 参考频率参考频率是DDS信号发生器中的基准频率,它决定了信号发生器能够产生的最高频率。

通常选择一个稳定、精确的参考时钟作为参考频率源,这可以是一个稳定的晶振或者其他同步源。

参考频率的选择应当考虑设备的应用场景,以及对生成信号频率范围和分辨率的需求。

3.2 相位累加器相位累加器是DDS技术中的核心组成部分,它记录了信号的相位信息,并根据参考频率的步进值来更新相位。

相位累加器的位宽决定了相位分辨率,位宽越高,相位分辨率越高,生成的信号表现越精细。

相位累加器的更新速度也决定了信号发生器的输出速率,更新速度越快,信号发生器的输出频率范围越大。

3.3 数字模拟转换器DDS技术生成的是数字信号,因此需要通过数字模拟转换器将数字信号转换为模拟信号输出。

DAC的精度和速度决定了信号发生器的输出质量和速率。

林家彬王辉龙DDS直接数字移相信号发生器告

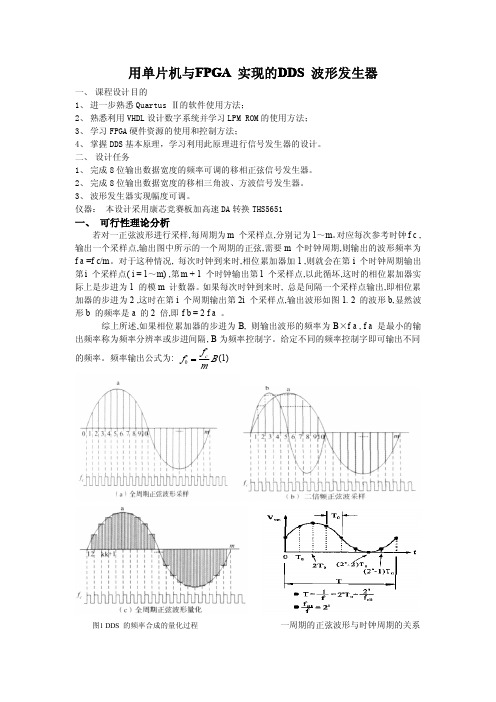

出频率称为频率分辨率或步进间隔, B 为频率控制字。给定不同的频率控制字即可输出不同

的频率。频率输出公式为:

f0

=

fc mB (1)源自图1 DDS 的频率合成的量化过程

一周期的正弦波形与时钟周期的关系

在实际设计中,如果累加器长度为N ,则可以有2N 个存储单元存储采样数据,如果我们

对一个周期的波形进行2N 个点的采样,即m = 2N , 此时输出频率f o 和系统时钟频率f c ,相

7.FPGA 实现的功能

单片机与FPGA 的接口模块根据P2. 0 、P2. 1 口的不同状态分类读取并锁存单片机数

据,将锁存的频率控制字、波形控制字、幅度控制字分别发送给相位累加器、波形存储器 、

DAC 控制模块。

表1 波形控制字编码

WAVE[1 ∶0 ]

00

01

10

11

输出波形

正弦波

三角波

矩形波

际上是步进为 1 的模 m 计数器。如果每次时钟到来时, 总是间隔一个采样点输出,即相位累

加器的步进为 2 ,这时在第 i 个周期输出第 2i 个采样点,输出波形如图 1. 2 的波形 b,显然波

形 b 的频率是 a 的 2 倍,即 f b = 2 f a 。

综上所述,如果相位累加器的步进为 B, 则输出波形的频率为 B×f a , f a 是最小的输

采样点的值为采样值2 ,以此类推,第i 组K 个采样点的值为采样值i , 共需要m/K个存储单元

来存储m/K个采样点。

DDS 的杂散来源之一就是相位累加器相位舍位造成的杂散。现有的频率控制主要采用

二进制频率控制原理。这是因为 FPGA 采用二进制的数据处理机制以及波形存储器的二进

基于DDS的信号发生器设计

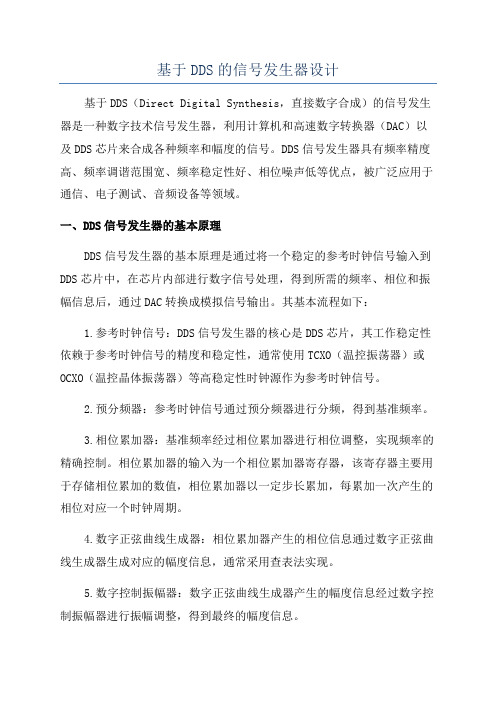

基于DDS的信号发生器设计基于DDS(Direct Digital Synthesis,直接数字合成)的信号发生器是一种数字技术信号发生器,利用计算机和高速数字转换器(DAC)以及DDS芯片来合成各种频率和幅度的信号。

DDS信号发生器具有频率精度高、频率调谐范围宽、频率稳定性好、相位噪声低等优点,被广泛应用于通信、电子测试、音频设备等领域。

一、DDS信号发生器的基本原理DDS信号发生器的基本原理是通过将一个稳定的参考时钟信号输入到DDS芯片中,在芯片内部进行数字信号处理,得到所需的频率、相位和振幅信息后,通过DAC转换成模拟信号输出。

其基本流程如下:1.参考时钟信号:DDS信号发生器的核心是DDS芯片,其工作稳定性依赖于参考时钟信号的精度和稳定性,通常使用TCXO(温控振荡器)或OCXO(温控晶体振荡器)等高稳定性时钟源作为参考时钟信号。

2.预分频器:参考时钟信号通过预分频器进行分频,得到基准频率。

3.相位累加器:基准频率经过相位累加器进行相位调整,实现频率的精确控制。

相位累加器的输入为一个相位累加器寄存器,该寄存器主要用于存储相位累加的数值,相位累加器以一定步长累加,每累加一次产生的相位对应一个时钟周期。

4.数字正弦曲线生成器:相位累加器产生的相位信息通过数字正弦曲线生成器生成对应的幅度信息,通常采用查表法实现。

5.数字控制振幅器:数字正弦曲线生成器产生的幅度信息经过数字控制振幅器进行振幅调整,得到最终的幅度信息。

6.高速DAC:数字振幅信息通过高速DAC转换成模拟信号输出,DAC 的速度和分辨率决定了信号发生器的输出品质。

7.滤波器:由于DAC输出是离散的,需要通过滤波器对其进行滤波,以去除高频成分和伪像,得到平滑的连续信号。

二、基于DDS的信号发生器设计思路在设计基于DDS的信号发生器时,需要考虑以下几个关键问题:1.DDS芯片选择:选择合适的DDS芯片作为信号发生器的核心,要考虑芯片的性能、频率范围、精度等因素。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA课程设计课题名称_ 基于DDS的数字移相信号发生器专业_ 电子信息工程____ _ _ 班级_____ _________ __ __学号_姓名_ __ __ 成绩_____ ____________ _指导教师___ _ ___ ___2014年5 月7日一、课程设计目的 (3)二、设计任务 (3)三、工作原理及模块分析 (3)1、频率预置与调节电路 (4)2、累加器 (4)3、波形存储器 (4)4、D/A转换器 (5)四、相关程序 (5)1、加法器 (5)(1)ADD10 (5)(2)ADD32 (7)2、寄存器 (9)(1)REG10B (9)(2)REG32B (11)3、ROM (13)4、主程序 (16)五、仿真结果: (19)六、引脚配置和下载 (20)七、实验心得 (21)一、课程设计目的1、进一步熟悉Quartus Ⅱ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM_ADD_SUB、LPM ROM、LPM_FF 的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计二、设计任务完成10位输出数据宽度的频率可调的移相正弦信号发生器,通过按键调节频率和初始相位,实现相位和频率可调的正弦信号发生器三、工作原理及模块分析直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:fc图1直接数字频率合成器原理图其中K为频率控制字,fc为时钟频率,N为相位累加器的字长,D为ROM 数据位及D/A转换器的字长。

相位累加器在时钟fc的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM 输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= fc K/2n,f0为输出频率,fc为时钟频率。

当K=1时,DDS输出最低频率(也既频率分辩率)为fc /2nDDS的最大输出频率由Nyguist 采样定理决定,即fc /2,也就是说K的最大值为2n-1.因此,只要N足够大,DDS可以得到很细的频率间隔。

要改变DDS 的输出频率,只要改变频率控制字K即可。

2、累加器相位累加器的原理图如下图图2 相位累加器原理图相位累加器由N为加法器与N位寄存器级联构成。

每来一个时钟脉冲fc,加法器将频率控制字与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端,寄存器将加法器在上一个时钟作用后所产生的下数据反馈到加法器的输入端;以使加法器在下一个时钟作用下继续频率控制字进行相加。

这样,相位累加器在时钟的作用下,进行相位累加,当相位累加器累加满量时,就产生一次溢出,完成一个周期性的动作,这个周期应为uk= 2n / GCD(2N ;k),其中GCD表示最大公约数。

3、波形存储器用相位累加器输出的数据作为波形存储器的取样地址进行波形的相位——幅值转换,即可在给定的时间上确定输出的波形的抽样幅值。

N位的寻址ROM 相当于把00--- 3600的正弦信号离散成具有2n 样值的序列,若波形ROM有D 位数据位,则2n个样值的幅值以D位二进制数值固化在ROM 中,按照地址的不同可以输出相宜相位的正弦信号的幅值。

相位----幅值变换原理图如下所示。

图3相位-幅度变换原理图4、D/A转换器D/A转换器的作用是把已经合成的正弦波的数字量转换成模拟量,正弦幅度量化序列S(n)经D/A转换后变成了包络为正弦波的阶梯波S(t),S(t)的周期为T=uk*Tc.。

需要注意的是,频率合成器对D/A转换器的分辨率有一定的要求,D/A转换器的分辨率越高,合成的正弦波S(t)台阶数就越多,输出波形的精度也就越高。

四、相关程序1、加法器(1)ADD10LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY lpm;USE lpm.all;ENTITY ADD10 ISPORT(dataa : IN STD_LOGIC_VECTOR (9 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (9 DOWNTO 0);result : OUT STD_LOGIC_VECTOR (9 DOWNTO 0));END ADD10;ARCHITECTURE SYN OF add10 ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (9 DOWNTO 0); COMPONENT lpm_add_subGENERIC(lpm_direction : STRING;lpm_hint : STRING;lpm_type : STRING;lpm_width : NATURAL);PORT(dataa : IN STD_LOGIC_VECTOR (9 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (9 DOWNTO 0);result : OUT STD_LOGIC_VECTOR (9 DOWNTO 0));END COMPONENT;BEGINresult <= sub_wire0(9 DOWNTO 0);lpm_add_sub_component : lpm_add_subGENERIC MAP(lpm_direction => "ADD",lpm_hint => "ONE_INPUT_IS_CONSTANT=NO,CIN_USED=NO", lpm_type => "LPM_ADD_SUB",lpm_width => 10)PORT MAP(dataa => dataa,datab => datab,result => sub_wire0);END SYN;(2)ADD32LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY lpm;USE lpm.all;ENTITY ADD32 ISPORT(dataa : IN STD_LOGIC_VECTOR (31 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (31 DOWNTO 0);result : OUT STD_LOGIC_VECTOR (31 DOWNTO 0) );END ADD32;ARCHITECTURE SYN OF add32 ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (31 DOWNTO 0); COMPONENT lpm_add_subGENERIC(lpm_direction : STRING;lpm_hint : STRING;lpm_type : STRING;lpm_width : NATURAL);PORT(dataa : IN STD_LOGIC_VECTOR (31 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (31 DOWNTO 0);result : OUT STD_LOGIC_VECTOR (31 DOWNTO 0));END COMPONENT;BEGINresult <= sub_wire0(31 DOWNTO 0);lpm_add_sub_component : lpm_add_subGENERIC MAP(lpm_direction => "ADD",lpm_hint => "ONE_INPUT_IS_CONSTANT=NO,CIN_USED=NO", lpm_type => "LPM_ADD_SUB",lpm_width => 32)PORT MAP(dataa => dataa,datab => datab,result => sub_wire0);END SYN;2、寄存器(1)REG10BLIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY lpm;USE lpm.all;ENTITY REG10B ISPORT(clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (9 DOWNTO 0);q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0) );END REG10B;ARCHITECTURE SYN OF reg10b ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (9 DOWNTO 0); COMPONENT lpm_ffGENERIC(lpm_fftype : STRING;lpm_type : STRING;lpm_width : NATURAL);PORT(clock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0);data : IN STD_LOGIC_VECTOR (9 DOWNTO 0) );END COMPONENT;BEGINq <= sub_wire0(9 DOWNTO 0);lpm_ff_component : lpm_ffGENERIC MAP(lpm_fftype => "DFF",lpm_type => "LPM_FF",lpm_width => 10)PORT MAP(clock => clock,data => data,q => sub_wire0);END SYN;(2)REG32BLIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY lpm;USE lpm.all;ENTITY REG32B ISPORT(clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (31 DOWNTO 0);q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0) );END REG32B;ARCHITECTURE SYN OF reg32b ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (31 DOWNTO 0); COMPONENT lpm_ffGENERIC(lpm_fftype : STRING;lpm_type : STRING;lpm_width : NATURAL);PORT(clock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0);data : IN STD_LOGIC_VECTOR (31 DOWNTO 0));END COMPONENT;BEGINq <= sub_wire0(31 DOWNTO 0);lpm_ff_component : lpm_ffGENERIC MAP(lpm_fftype => "DFF",lpm_type => "LPM_FF",lpm_width => 32)PORT MAP(clock => clock,data => data,q => sub_wire0);END SYN;3、ROMLIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY altera_mf;USE altera_mf.all;ENTITY ROM ISPORT(address : IN STD_LOGIC_VECTOR (9 DOWNTO 0);clock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0));END ROM;ARCHITECTURE SYN OF rom ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (9 DOWNTO 0); COMPONENT altsyncramGENERIC(address_aclr_a : STRING;init_file : STRING;intended_device_family : STRING;lpm_hint : STRING;lpm_type : STRING;numwords_a : NATURAL;operation_mode : STRING;outdata_aclr_a : STRING;outdata_reg_a : STRING;widthad_a : NATURAL;width_a : NATURAL;width_byteena_a : NATURAL);PORT (clock0 : IN STD_LOGIC ;address_a : IN STD_LOGIC_VECTOR (9 DOWNTO 0);q_a : OUT STD_LOGIC_VECTOR (9 DOWNTO 0));END COMPONENT;BEGINq <= sub_wire0(9 DOWNTO 0);altsyncram_component : altsyncramGENERIC MAP (address_aclr_a => "NONE",init_file => "LUT10X10.MIF",intended_device_family => "Cyclone",lpm_hint => "ENABLE_RUNTIME_MOD=YES, INSTANCE_NAME=NONE", lpm_type => "altsyncram",numwords_a => 1024,operation_mode => "ROM",outdata_aclr_a => "NONE",outdata_reg_a => "CLOCK0",widthad_a => 10,width_a => 10,width_byteena_a => 1)PORT MAP (clock0 => clock,address_a => address,q_a => sub_wire0);END SYN;4、主程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGiC_UNSIGNED.ALL;ENTITY DDS_SIN_YANGTIANJUN_CHENYAOSHUAI ISPORT( CLK: IN STD_LOGIC;--系统时钟FWORD: IN STD_LOGIC_VECTOR(7 DOWNTO 0);--频率控制字PWORD: IN STD_LOGIC_VECTOR(7 DOWNTO 0);--相位控制字FOUT: OUT STD_LOGIC_VECTOR(9 DOWNTO 0);--可移相正弦信号输出POUT: OUT STD_LOGIC_VECTOR(9 DOWNTO 0);CLKOUT:OUT STD_LOGIC);--参考信号输出END DDS_SIN_YANGTIANJUN_CHENYAOSHUAI;ARCHITECTURE one OF DDS_SIN_YANGTIANJUN_CHENYAOSHUAI IS COMPONENT REG32B --32 位锁存器PORT(clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (31 DOWNTO 0);q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0) );END COMPONENT;COMPONENT REG10B --10 位锁存器PORT(clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (9 DOWNTO 0);q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0));END COMPONENT;COMPONENT ADD32 --32位加法器PORT(dataa : IN STD_LOGIC_VECTOR (31 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (31 DOWNTO 0);result : OUT STD_LOGIC_VECTOR (31 DOWNTO 0) );END COMPONENT;COMPONENT ADD10 -- 10位加法器的设计PORT(dataa : IN STD_LOGIC_VECTOR (9 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (9 DOWNTO 0);result : OUT STD_LOGIC_VECTOR (9 DOWNTO 0) );END COMPONENT;COMPONENT ROM --10位地址10位数据正弦信号数据ROM PORT(address : IN STD_LOGIC_VECTOR (9 DOWNTO 0);clock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0));END COMPONENT;SIGNAL F32B,D32B, DIN32B:STD_LOGIC_VECTOR(31 DOWNTO 0); SIGNAL P10B,LIN10B,SIN10B:STD_LOGIC_VECTOR(9 DOWNTO 0); BEGINCLKOUT<=CLK;F32B(27 DOWNTO 20)<=FWORD;F32B(31 DOWNTO 28)<="0000";F32B(19 DOWNTO 0)<="00000000000000000000";P10B(9 DOWNTO 2)<=PWORD;P10B(1 DOWNTO 0)<="00";u1 : ADD32 PORT MAP(dataa=>F32B,datab=>D32B,result=>DIN32B);u2 : REG32B PORT MAP(q=>D32B,data=>DIN32B,clock=>CLK);u3 : ROM PORT MAP(address=>SIN10B,q=>FOUT,clock=>CLK);u4 : ADD10 PORT MAP(dataa=>P10B,datab=>D32B(31 DOWNTO 22),result=>LIN10B);u5 : REG10B PORT MAP(q=>SIN10B,data=>LIN10B,clock=>CLK);u6 : ROM PORT MAP(address=>D32B(31 DOWNTO22),q=>POUT,clock=>CLK);END one;五、仿真结果:图4仿真波形由仿真结果来看改变相位和频率输入,相应输出的频率和相位也跟随着相应的变化。