一种分布式共享内存计算机FPGA原型系统的设计与实现_刘金广

基于共享内存和多进程的分布式数据库架构及其实现方法[发明专利]

![基于共享内存和多进程的分布式数据库架构及其实现方法[发明专利]](https://img.taocdn.com/s3/m/93babee6f12d2af90342e628.png)

专利名称:基于共享内存和多进程的分布式数据库架构及其实现方法

专利类型:发明专利

发明人:王效忠,冀贤亮,何振兴,李英帅

申请号:CN202010772287.5

申请日:20200804

公开号:CN111949687A

公开日:

20201117

专利内容由知识产权出版社提供

摘要:本发明公开了一种基于共享内存和多进程的分布式数据库架构及实现方法,属一种分布式数据库架构,其包括分布式数据库节点,分布式数据库内置系统共享内存单元与系统进程单元;系统共享内存单元包括任务堆栈信息模块与共享缓存模块;任务堆栈信息模块内置多个进程任务;进程任务为系统进程任务信息中的多种用途的系统信息,每个系统信息均对应一个进程任务;通过在分布式数据库节点使用系统共享内存单元,使得在该分布式数据库架构中用户的连接数不与进程或者线程存在对应关系,整个节点的进程或者线程数都不会因为用户连接数的增加而增加,从而有效避免因瞬时用户连接数过多而导致系统响应速度变慢,从而使系统性能不会因此而受到影响。

申请人:贵州易鲸捷信息技术有限公司

地址:550000 贵州省贵阳市贵阳综合保税区都拉营综保路349号海关大楼8楼801

国籍:CN

代理机构:成都中炬新汇知识产权代理有限公司

代理人:罗韬

更多信息请下载全文后查看。

[信息与通信]第三届“ZLG杯”大学生FPGADIY创新电子设计竞赛获奖作品论文集

![[信息与通信]第三届“ZLG杯”大学生FPGADIY创新电子设计竞赛获奖作品论文集](https://img.taocdn.com/s3/m/f299450aa31614791711cc7931b765ce05087aee.png)

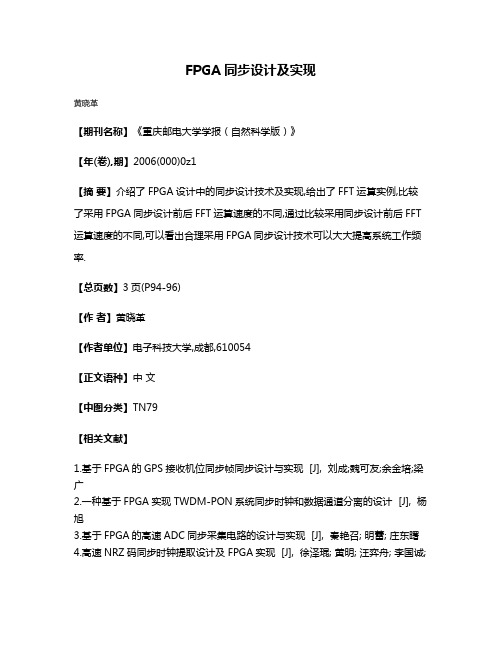

目录一等奖作品 (3)基于EasyFPGA030的矩阵键盘管理 (4)1概述 (4)2实现原理 (4)3设计实现 (5)4系统测试结果 (9)5结束语 (10)6参考文献 (10)二等奖作品 (11)基于EasyFPGA030的矩阵键盘管理 (12)1概述 (12)2实现原理 (12)3设计实现 (13)4系统测试结果 (15)5结束语 (16)6参考文献 (16)基于EasyFPGA030的开平方算法设计 (17)1概述 (17)2实现原理 (17)3设计实现 (18)4系统测试结果 (20)5结束语 (21)6参考文献 (21)基于EasyFPGA030的同步FIFO设计 (22)1概述 (22)2实现原理 (23)3设计实现 (23)4系统测试结果 (26)5结束语 (27)6参考文献 (27)三等奖作品 (28)基于EasyFPGA030的开平方运算设计 (29)1概述 (29)2实现原理 (29)3设计实现 (29)4系统测试结果 (32)5结束语 (33)6参考文献 (33)基于EasyFPGA030的同步FIFO设计 (34)1概述 (34)2实现原理 (35)3设计实现 (36)4系统测试结果 (39)5结束语 (39)6参考文献 (40)基于EasyFPGA030的同步FIFO设计 (41)1概述 (41)2实现原理 (41)3设计实现 (41)4系统测试结果 (44)5结束语 (45)6参考文献 (45)基于EasyFPGA030的同步FIFO设计 (46)1概述 (46)2实现原理 (46)3设计实现 (46)4系统测试结果 (49)5结束语 (49)6参考文献 (49)基于EasyFPGA030开平方算法设计 (50)1概述 (50)2实现原理 (50)3设计实现 (50)4系统测试结果 (52)5结束语 (53)一等奖作品基于EasyFPGA030的矩阵键盘管理参赛学校:华南理工大学参赛队员:钟启标樊国勇【摘要】这是一个矩阵键盘管理应用,它能将相应的结果通过数码管显示出来。

一种基于共享内存的多核处理器交互总线设计方法[发明专利]

![一种基于共享内存的多核处理器交互总线设计方法[发明专利]](https://img.taocdn.com/s3/m/968904df4bfe04a1b0717fd5360cba1aa8118ca8.png)

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 201810683337.5(22)申请日 2018.06.28(71)申请人 南京南瑞继保电气有限公司地址 211102 江苏省南京市江宁区苏源大道69号申请人 南京南瑞继保工程技术有限公司(72)发明人 周谷庆 文继峰 周强 刘伟 侯先栋 王浩 赵天恩 (51)Int.Cl.G06F 13/40(2006.01)G06F 9/54(2006.01)(54)发明名称一种基于共享内存的多核处理器交互总线设计方法(57)摘要本发明公开一种基于共享内存的多核处理器交互总线设计方法,适用于大容量数据实时交互的多核处理器系统。

初始化阶段解析多核处理器的数据交互配置,获取每个核处理器输出和输入数据配置信息。

根据输出配置信息初始化共享内存,依次分配每个核处理器输出数据区的内存段。

建立每个核处理器输入数据的链表,保存输入数据对应的映射内存地址。

在实时中断任务中采用乒乓式循环读写缓存,读取上次中断任务的交互数据,更新本次中断任务的输出数据并写入共享内存。

本方法具有系统架构简洁、数据传输可靠和数据交互低延时等特点,在嵌入式多核处理器系统有较好的应用前景。

权利要求书1页 说明书3页 附图1页CN 108959149 A 2018.12.07C N 108959149A1.一种基于共享内存的多核处理器交互总线设计方法,其特征在于:包括,步骤1,解析多核处理器的数据交互配置,获取每个核处理器输出和输入数据配置信息;步骤2,根据配置信息初始化共享内存,在共享内存分配每个核处理器输出数据区的内存段;建立每个核处理器输入数据的链表;步骤3,初始化多核处理器中断配置,通过周期产生中断信号,触发每个核处理器同时进入实时中断任务;步骤4,多核处理器中采用乒乓式循环读写缓存,读取上次中断任务的交互数据,更新本次中断任务的输出数据并写入共享内存。

一种多核多模型并行分布式实时仿真系统的制作方法

一种多核多模型并行分布式实时仿真系统的制作方法多核多模型并行分布式实时仿真系统是一种能够利用多个处理器核心和多个仿真模型进行并行计算的系统。

通过并行计算,系统能够实现更高的性能和更快的响应速度,从而能够更准确地模拟和分析各种复杂系统的行为。

本文将介绍一种制作多核多模型并行分布式实时仿真系统的方法。

首先,为了搭建多核多模型并行分布式实时仿真系统,我们需要选择一个适合的仿真引擎。

常用的仿真引擎包括MATLAB Simulink、AnyLogic、Arena等。

在选择仿真引擎的过程中,我们需要考虑系统的仿真需求、计算资源、性能要求等因素,并选择一个能够满足这些需求的仿真引擎。

其次,我们需要设计系统的模型。

系统的模型是描述系统行为和性能的数学模型,它包括系统的结构、参数、状态方程等。

在设计模型的过程中,我们需要考虑系统的仿真需求、可扩展性、灵活性等因素,并设计出一个适合的模型结构。

接着,我们需要将系统的模型分解成多个子模型,并将这些子模型分配给不同的处理器核心进行并行计算。

在这个过程中,我们需要考虑子模型之间的依赖关系、计算负载平衡、通信开销等因素,并设计出一个合理的分配策略。

然后,我们需要搭建分布式计算环境。

分布式计算环境是多核多模型并行分布式实时仿真系统的基础,它包括计算节点、通信网络、数据存储等组件。

在搭建分布式计算环境的过程中,我们需要考虑系统的性能需求、通信延迟、数据传输速度等因素,并设计出一个高效稳定的分布式计算环境。

最后,我们需要实现系统的并行计算和实时仿真。

在实现并行计算的过程中,我们需要编写并行计算代码、优化计算算法、调试代码等工作。

在实现实时仿真的过程中,我们需要考虑仿真精度、仿真速度、数据可视化等因素,并设计出一个能够满足实时仿真需求的系统。

综上所述,制作多核多模型并行分布式实时仿真系统是一个复杂而又具有挑战性的任务。

通过合理的设计和实现,我们可以搭建一个高性能、准确可靠的多核多模型并行分布式实时仿真系统,为各种复杂系统的仿真和分析提供有力支持。

分布式系统文献阅读综述(李海广S130201036)

如果我们只有一组连接到一起的计算机,尚不能称其为分布式系统,分布式系统的另一个组成部分是分布式软件。只有硬件和软件结合到一起,才能形成一个具有活力的系统[1]。下面列举出一些分布式软件:

1、分布式操作系统

负责管理分布式处理系统资源和控制分布式程序运行。它和集中式操作系统的区别在于资源管理、进程通信和系统构等方面。文献阅读综述

综述内容:分布式系统

姓 名:李海广

学 号:S130201036

任课教师:刘群

完成时间:2013/12/16

摘 要

显然,未来对计算速度、系统可靠性和成本实效性的要求必将促使发展另外的计算机模型来取代传统的冯诺依曼结构的计算机。随着计算机网络的出现,一个新的梦想成为可能—分布式系统。当用户需要完成任何任务时,分布式系统提供对尽可能多的计算机能力和数据的透明访问,同时实现高效能和高可靠性的目标。在过去的10年里,人们对分布式系统的兴趣迅猛发展。有关分布式系统的主题是多种多样的,许多研究人员正在研究关于分布式硬件结构和分布式软件设计的各方面问题以开发利用其潜在的并行性和容错性。

浏览器/服务器模型最大的优点是简化了系统的开发与维护。客户机上无需安装特殊的“客户”程序,只要一个通用的浏览器。这样不仅节省用户的存储空间,而且缩短了系统的安装调试周期。每个用户可以在自己的权限范围内调用Web服务器的各种服务。对系统维护者来说,Web服务的升级换代不会影响到用户一端,既不需要改变用户程序,也不需要对用户培训。其次,这种模型对用户更加友好。在传统的客户/服务器模型里,不同厂家开发的客户程序都有自己的风格和规范,使用者往往要经过专门培训才能胜任。而浏览器的使用方式已基本家喻户晓,即便对任何没有计算机经验的人来说,只需稍加指点,就会进行网上购物和网上拍卖。

FPGA综合实验期末课程设计

FPGA综合实验期末课程设计一、教学目标本课程的教学目标是使学生掌握FPGA的基本原理和应用技能,能够综合运用FPGA进行电子系统设计。

具体目标如下:1.掌握FPGA的基本工作原理和结构。

2.熟悉FPGA的编程语言和开发环境。

3.了解FPGA在电子系统中的应用。

4.能够使用FPGA开发工具进行程序设计。

5.能够进行FPGA硬件编程和调试。

6.能够独立完成FPGA综合实验。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.培养学生对新技术的敏感性和持续学习的意识。

3.培养学生对电子工程领域的兴趣和热情。

二、教学内容本课程的教学内容主要包括以下几个部分:1.FPGA的基本原理和结构。

2.FPGA的编程语言和开发环境。

3.FPGA在电子系统中的应用案例。

4.FPGA综合实验的设计和实现。

具体的教学内容安排如下:第一章:FPGA概述1.1 FPGA的基本原理1.2 FPGA的结构和分类1.3 FPGA的应用领域第二章:FPGA编程语言2.1 硬件描述语言(HDL)2.2 VHDL语言的基本语法2.3 Verilog语言的基本语法第三章:FPGA开发环境3.1 FPGA开发工具的使用3.2 设计流程和步骤3.3 FPGA硬件编程和调试第四章:FPGA应用案例4.1 数字信号处理应用4.2 数字通信应用4.3 嵌入式系统应用第五章:FPGA综合实验5.1 实验目的和意义5.2 实验内容和步骤5.3 实验结果和分析三、教学方法本课程采用多种教学方法相结合的方式,包括:1.讲授法:讲解FPGA的基本原理和应用案例。

2.讨论法:引导学生进行问题讨论和思考。

3.案例分析法:分析具体的FPGA应用案例。

4.实验法:进行FPGA综合实验的设计和实现。

通过多样化的教学方法,激发学生的学习兴趣和主动性,提高学生的实践能力。

四、教学资源本课程的教学资源包括:1.教材:《FPGA综合实验》2.参考书:相关的FPGA技术书籍3.多媒体资料:PPT课件、实验视频等4.实验设备:FPGA开发板、编程器等教学资源的选择和准备将充分支持教学内容和教学方法的实施,丰富学生的学习体验。

一种基于任务调度的分布式GPU计算机系统[发明专利]

![一种基于任务调度的分布式GPU计算机系统[发明专利]](https://img.taocdn.com/s3/m/0cca3b36cd1755270722192e453610661ed95a39.png)

(10)申请公布号 CN 102929718 A(43)申请公布日 2013.02.13C N 102929718 A*CN102929718A*(21)申请号 201210344326.7(22)申请日 2012.09.17G06F 9/50(2006.01)(71)申请人江苏九章计算机科技有限公司地址215500 常熟市南经济开发区东南大道68号1幢(72)发明人谢小轩 乐德广 胡永禄(74)专利代理机构北京远大卓悦知识产权代理事务所(普通合伙) 11369代理人史霞(54)发明名称一种基于任务调度的分布式GPU 计算机系统(57)摘要本发明公开了一种基于任务调度的分布式GPU 计算机系统,系统内的GPU 处理单元来自于网络,在与中央处理单元建立通信之前,可能正处于运算状态,利用任务调度模块根据计算机系统内的各GPU 处理单元的当前处理能力对任务块进行分配,根据各GPU 处理单元的性能分配工作,保证对资源的高效率利用;同时,实时计算GPU 处理单元的利用率,以便及时将系统内多余的GPU 处理单元转入待机状态或者在系统内GPU 处理单元处理能力不足时,激活GPU 处理单元以满足系统需要,也可以保证充分利用GPU 处理单元的资源。

本发明所述的基于任务分解与调度的分布式GPU 计算机系统,解决现有传统的CPU 计算存在的计算能力不足的问题,大大提高计算能力。

系统设计简单,具有良好的扩展性。

(51)Int.Cl.权利要求书1页 说明书6页 附图2页(19)中华人民共和国国家知识产权局(12)发明专利申请权利要求书 1 页 说明书 6 页 附图 2 页1/1页1.一种基于任务调度的分布式GPU 计算机系统,其特征在于,包括:GPU 处理单元,所述GPU 处理单元用于处理任务块;中央处理单元,所述GPU 处理单元与所述中央处理单元通信,其包括任务分解模块和任务调度模块,所述中央处理单元监测当前与所述中央处理单元通信的GPU 处理单元的个数N 以及N 个GPU 处理单元中的各GPU 处理单元的当前处理能力Wi ,并计算各GPU 处理单元的当前处理能力在N 个GPU 处理单元的当前处理能力的总和的权重i ,其中i =Wi/∑Wi ,所述任务分解模块将当前任务均分为M 个任务块,所述任务调度模块依据各GPU 处理单元的当前处理能力在所有GPU 处理单元的当前处理能力的总和的权重i ,向各GPU 处理单元分配n 个任务块,其中n =i×M ,所述任务调度模块向各中央处理单元分配任务块时,所述中央处理单元建立有一任务队列响应程序,其中所述任务队列响应程序中包括有一任务队列文件,且所述任务队列文件中记录有n 个任务块以及处理所述n 个任务块的GPU 处理单元,当所述GPU 处理单元完成对一个任务块的处理,所述GPU 处理单元首先将处理完成的一个任务块的任务数据发送到所述中央处理单元,并响应所述任务队列响应程序,所述中央处理单元将已经被响应的任务块从所述任务队列文件中删除,并且计算所述N 个GPU 处理单元中各GPU 处理单元的利用率,向所述N 个GPU 处理单元中利用率低于30%的GPU 处理单元发出待机命令,则由所述任务调度模块将其当前处理的任务块迁移至剩余GPU 处理单元中利用率最低的GPU 处理单元,所述中央处理单元修改所述任务队列文件,当位于所述任务队列文件中的GPU 处理单元的利用率均高于80%时,所述中央处理单元向当前处于待机状态的GPU 处理单元发出激活命令,由所述任务调度模块将当前利用率最高的GPU 处理单元的当前处理的任务块迁移至被激活的GPU 处理单元,所述中央处理单元修改所述任务队列文件,直至所述任务队列文件中的GPU 处理单元的平均利用率达到70%。

FPGA同步设计及实现

FPGA同步设计及实现

黄晓革

【期刊名称】《重庆邮电大学学报(自然科学版)》

【年(卷),期】2006(000)0z1

【摘要】介绍了FPGA设计中的同步设计技术及实现,给出了FFT运算实例,比较了采用FPGA同步设计前后FFT运算速度的不同,通过比较采用同步设计前后FFT 运算速度的不同,可以看出合理采用FPGA同步设计技术可以大大提高系统工作频率.

【总页数】3页(P94-96)

【作者】黄晓革

【作者单位】电子科技大学,成都,610054

【正文语种】中文

【中图分类】TN79

【相关文献】

1.基于FPGA的GPS接收机位同步帧同步设计与实现 [J], 刘成;魏可友;余金培;梁广

2.一种基于FPGA实现TWDM-PON系统同步时钟和数据通道分离的设计 [J], 杨旭

3.基于FPGA的高速ADC同步采集电路的设计与实现 [J], 秦艳召; 明蕾; 庄东曙

4.高速NRZ码同步时钟提取设计及FPGA实现 [J], 徐泽琨; 黄明; 汪弈舟; 李国诚;

黄炎

5.无人机测控链路位同步环路的设计与FPGA实现 [J], 白园; 李成; 刘婵; 陈飞因版权原因,仅展示原文概要,查看原文内容请购买。

Super-Object模型: 在分布存储器多计算机上实现共享存储器程序设计模式

Super-Object模型:在分布存储器多计算机上实现共享存

储器程序设计模式

窦勇;周兴铭

【期刊名称】《计算机学报》

【年(卷),期】1995(018)007

【摘要】Super-Object模型提出了一种新的方法,在分布存储器多计算机上实现语言级虚拟共享存储器以支持共享存储器通信模式.Super-Object模型引入新的概念super-object,不同于其它模型,基于super-object,它提出了新的共享数据定位方法,全局地址标识<name,offset>.Super-Object模型与Fortran77结合,我们实现了一个运行时间系统和库调用,支持程序员使用Fortran语言编写并行程序,最后介绍了系统的实现和取得的性能.

【总页数】7页(P481-487)

【作者】窦勇;周兴铭

【作者单位】国防科学技术大学计算机科学系,长沙,410073;国防科学技术大学计算机科学系,长沙,410073

【正文语种】中文

【中图分类】TP3

【相关文献】

1.分布式共享存储器系统的设计与实现 [J], 陈霞

2.分布式共享存储器(DSM)的可扩展模型设计 [J], 傅晓菲;林锦贤

3.小型分布式控制系统中共享存储器的使用 [J], 郑晓青;郑晓明

4.小型分布式控制系统中共享存储器的使用 [J], 郑晓青;郑晓明

5.分布式共享存储器的实现 [J], Ramac.,U;王津涛

因版权原因,仅展示原文概要,查看原文内容请购买。

主从式多处理机系统中双CPU共享RAM的一种实现方法

主从式多处理机系统中双CPU共享RAM的一种实现方法张晴;陶俊才

【期刊名称】《南昌大学学报:工科版》

【年(卷),期】1999(021)001

【摘要】介绍了通过内存共享实现主从式多机系统中双机通信的一种设计思想,给出了软件、硬件的实现方法。

【总页数】5页(P88-92)

【作者】张晴;陶俊才

【作者单位】南昌大学计算中心;南昌大学计算中心

【正文语种】中文

【中图分类】TP368.1

【相关文献】

1.克服多处理机系统高速缓存中假共享方法研究 [J], 唐俊奇;郑志明

2.双CPU共享RAM技术及其在数控系统中的应用 [J], 郭冰菁;朱坚民;姜琳

3.以共享RAM方式实现的主从式多机通信 [J], 蒋贻濂

4.多处理机系统中一种共享内存交互技术与实现 [J], 文富荣;胡多勋;汪自云

5.利用TWI硬件中断实现AVR单片机主从式I2C通讯的一种方法 [J], 张洪林因版权原因,仅展示原文概要,查看原文内容请购买。