DSP硬件开发教程

DSP入门教程(非常经典)

5、如何高效开始 TI DSP 的软件开发 如果你不是纯做算法,而是在一个目标版上进行开发, 需要使用 DSP 的片上外设,需要控 制片外接口电路,那么建议在写程序前先好好将这个目标 版的电路设计搞清楚。最重要的是 程序、数据、I/O 空间的译码。不管是否纯做算法还是软硬结合, DSP 的 CPU,memory,program memory addressing, data mem.ory addressing 的资料都需要看.

DSP 的内部指令周期较高,外部晶振的主频不够,因此 DSP 大多Байду номын сангаас片内均有 PLL。但每个 系列不尽相同。

1)TMS320C2000 系列: TMS320C20x:PLL 可以÷2,×1,×2 和×4,因此外部时钟可以为 5MHz-40MHz。 TMS320F240:PLL 可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5 和×9,因此外部时钟 可 以为 2.22MHz-40MHz。 TMS320F241/C242/F243:PLL 可以×4,因此外部时钟为 5MHz。 TMS320LF24xx:PLL 可 以由 RC 调节,因此外部时钟为 4MHz-20MHz。 TMS320LF24xxA:PLL 可以由 RC 调节,因此外部时钟为 4MHz-20MHz。

3)C6000 系列:C62XX,C67XX,C64X 该系列以高性能著称,最适合宽带网络和数字 影 像应用。32bit,其中:C62XX 和 C64X 是定点系列,C67XX 是浮点系列。该系列提供 EMIF 扩展 存储 器接口。该系 列只提供 BGA 封 装,只能制作 多层 PCB。且功耗较 大。同为浮点 系列的 C3X 中的 VC33 现在虽非主流产品,但也仍在广泛使用,但 其速度较低,最高在 150MIPS。

DSP硬件开发

DSP系统的硬件设计又称为目标板设计,是在考虑算法需求、成本、体积和功耗核算的基础上完成的,一个典型的DSP目标板主要包括:DSP芯片及DSP基本系统程序和数据存储器数/模和模/数转换器模拟控制与处理电路各种控制口和通信口电源处理电路和同步电路系统硬件设计过程:第一步:确定硬件实现方案;在考虑系统性能指标、工期、成本、算法需求、体积和功耗核算等因素的基础上,选择系统的最优硬件实现方案。

第二步:器件的选择;一个DSP硬件系统除了DSP芯片外,还包括ADC、DAC、存储器、电源、逻辑控制、通信、人机接口、总线等基本部件。

① DSP芯片的选择首先要根据系统对运算量的需求来选择;其次要根据系统所应用领域来选择合适的DSP芯片;最后要根据DSP的片上资源、价格、外设配置以及与其他元部件的配套性等因素来选择。

② ADC和DAC的选择A/D转换器的选择应根据采样频率、精度以及是否要求片上自带采样、多路选择器、基准电源等因素来选择;D/A转换器应根据信号频率、精度以及是否要求自带基准电源、多路选择器、输出运放等因素来选择。

③存储器的选择常用的存储器有SRAM、EPROM、E2PROM和FLASH等。

可以根据工作频率、存储容量、位长(8/16/32位)、接口方式(串行还是并行)、工作电压(5V/3V)等来选择。

④逻辑控制器件的选择系统的逻辑控制通常是用可编程逻辑器件来实现。

首先确定是采用CPLD还是FPGA;其次根据自己的特长和公司芯片的特点选择哪家公司的哪个系列的产品;最后还要根据DSP的频率来选择所使用的PLD器件。

⑤通信器件的选择通常系统都要求有通信接口。

首先要根据系统对通信速率的要求来选择通信方式。

然后根据通信方式来选择通信器件。

一般串行口只能达到19kb/s,而并行口可达到1Mb/s 以上,若要求过高可考虑通过总线进行通信;⑥总线的选择常用总线:PCI、ISA以及现场总线(包括CAN、3xbus等)。

可以根据使用的场合、数据传输要求、总线的宽度、传输频率和同步方式等来选择。

第四章DSP开发方法及开发工具_85详解

在V3.0的基础上,可以支持各种处理器的开发。

VisualDSP++中集成的开发工具

▪ C/C++编译器 ▪ 超过100种的数学、DSP实时库和C实时库 ▪ 汇编器 ▪ 链接器 ▪ 分配器 ▪ 加载代码产生器 ▪ 硬件仿真器 ▪ 软件模拟器

与之配套的硬件仿真器

▪ MTN-ICE ▪ SUMMIT-ICE ▪ APEX-ICE ▪ Trek-ICE

▪ 指定一个输出类型,有以下两种输出类型

▪ Debug类型,编译链接的工程文件可用来进

行Debug调试。

▪ Release类型,生成具有限制的或不能进行

Debug调试的工程文件,Release类型通常 用来进行优化程序性能。

▪ 一般在调试过程中选择Debug类型,当程序调 试好以后,选择Release类型。

汇编文件 .asm

3.模拟 调试

链接描述文件 .ldf

工程文件 .dpj

编译链接 Build

可执行代码 .dxe

开发实验板

软件模拟 器

Simulator

4.目标 板调试

目标板

EZ-ICE仿真器 Emulator

5.制作/调 试DSP系统

测试/调试 DSP

产生 EPROM代码

DSP程序开发方法示意图

如TESTFF。

▪ TOOL CHAIN 组:

▪ Complier: 指定C编译器; ▪ Assembler: 指定汇编器; ▪ Linker: 指定链接器; ▪ Loader: 指定加载器 ▪ Splitter: 指定加载方式的镜像文件管理器;

Project选项的意义(2)

▪ Setting for选项

DSP硬件设计基础PPT学习教案

第16页/共18页

第17页/共18页

设计必须通过相关的专业软件才能完成。目前能够同时进行电原理图和 电路板图设计的软件工具比较多,比较盛行的有Protel公司、Cadence 公司、Mentor公司等的设计工具。

第4页/共18页

5、设计印制电路板图 当完成原理图的绘制并经过审核以后,就可以进行PCB的设计。对

于复杂的硬件设计,一般在设计电原理图时,还有一个原理图仿真过程 ,尤其对于模拟器件和高频器件等的设计。这个过程通常是必需的。在 完成PCB的设计进行制板以前,还要对PCB设计进行仿真,用以完成对 信号完整性、电磁干扰、热仿真等的功能检验。

第5页/共18页

10.2 3.3V和5V混合逻辑系统设计

1、各种电平转换标准

其中,VOH表示输出高电平的最低电压,VIH表示输入高电平的最 低电压, VIL表示输入低电平的最高电压, VOL表示输出低电平的最高 电压。

第6页/共18页

2、3.3V器件与5V器件接口的四种情况 根据实际应用场合,下面考虑3.3V器件与5V器件接口的四种不

第12页/共18页

TMS320LF240x系列DSP的时钟是外部振荡器方式的时钟输入电路图。

LF240x具有内部锁相环,用来从一个较低频率的外部时钟通过锁 相环倍频电路实现内部倍频。这对于整个电路板的电磁兼容性是很有好 处的,因为外部只需要使用较低频率的晶振,避免外部电路干扰时钟, 同时也避免了高频时钟干扰板上其他电路。

3.3V电源一般需要通过对5V电源进行变换得到。对于电源芯片 的选择,需要从以下几个方面考虑:

基于DSP的硬件、软件开发流程(精)

周期内完成。

・快速的指令周期目前,C6000系列、C5000系列的最高工作主频已经达到600MHz,指令周期降到了1.67ns,随着微电子技术的不断发展,工作频率还将进一步提高,指令周期进一步缩短。

・特殊的DSP指令DSP芯片有专门为数字信号处理而设计的指令系统。

此外,DSP还具有良好的多机并行运行特性、内部RAM等不同于普通单片机的特点,正是由于这些特征,使得DSP芯片非常适合于实时的数字信号处理。

3.2.2DSP的硬件设计流程第一步:设汁硬件实现方案,根据性能指标、成本、工期等,确定最优的硬件实现方案。

控制、通信、人机接口、总线等基本部件,他们大致的确定原则如下:根据采样频率、精度、是否要求片上自带采保、多路器、基准电源等来确定A/D型号:内存(EPROM,SDRAM,SBSRAM等的选择主要考虑工作频率、内存容量位长、接口方式、工作电压等。

第三步:进行原理图的设计,原理图的设计是关键的一步,在原理图的设计时必须清楚的了解器件的使用和系统的开发,对于~些关键的环节有必要做一定的仿真。

原理图设计的成功与否,是DSP系统能否正常工作的最重要的~个因素。

第四步:PCB图的设计,PCB即印刷电路板,PCB的设计要求设计人员清楚布线工艺和系统原理图。

第五步:硬件调试。

3.2.3DSP系统软件编程的步骤(1、用汇编语言、c语言或汇编语言和c语言的混合编程来编写程序,然后把它们分别转化成TMS320的汇编语言并送到汇编语言编译器进行编译,生成目标文件。

(2、将目标文件送入链接器进行链接,得到可执行文件。

(3、将可执行文件调入到调试器进行调试,检查运行结果是否正确,如果正确进入第四步,如果不正确则返回第一步。

(4、进行代码转换,将代码写入EEPROM,并脱离仿真环境运行程序,检查结果是否正确。

(5、软件测试,如果测试结果合格,则软件调试完毕,如果不合格,返回第一步。

在完成系统的软硬件设计之后,将进行系统集成。

第五讲:DSP的硬件开发1

系统组成

DSP的选择 DSP的选择

• • • • • • • •

数据格式:定点/ 数据格式:定点/浮点 数据宽度:16bit/32bit 数据宽度:16bit/32bit 速度:MIPS, 速度:MIPS, FLOPS 外设接口,片内ram容量 外设接口,片内ram容量 开发配套工具的完善:CCS, 开发配套工具的完善:CCS,visualDSP++ 多片互连能力 功耗和电源管理:休眠/ 功耗和电源管理:休眠/等待模式 成本

DSP的最小系统组成 DSP的最小系统组成

一个DSPs要能够正常的运行程序完成 简单的任务,并能够通过JTAG被调试,它 的最小系统应该包括DSPs芯片、电源、时 钟源、复位电路、JTAG电路、程序ROM以 JTAG ROM 及对芯片所做的设置。

DSP的最小系统 DSP的最小系统

电源设计

• I/O电压,核电压. I/O电压,核电压. • 估计功耗大小. • 使用ti的电源设计软件swift design 使用ti的电源设计软件swift

MCBSP接口信号 MCBSP接口信号

MCBSP

MCBSP

MCBSP

Hpi接口 Hpi接口

主机口HPI是一个 是一个16bits宽度的并行端口.主机 宽度的并行端口. 主机口 是一个 宽度的并行端口 也叫做上位机)掌管该接口的主控权, (也叫做上位机)掌管该接口的主控权,通过它可以 直接访问CPU的存储空间.另外,主机还可以直接访 的存储空间. 直接访问 的存储空间 另外, 片内的存储映射的外围设备. 问C6000片内的存储映射的外围设备. 片内的存储映射的外围设备 HPI与CPU存储空间的互连是通过 与 存储空间的互连是通过DMA控制器实 存储空间的互连是通过 控制器实 现的.借助专门的地址和数据积存器,通过DMA辅助 现的.借助专门的地址和数据积存器,通过 辅助 通道,完成HPI对存储空间的访问.主Байду номын сангаас和 对存储空间的访问. 通道,完成 对存储空间的访问 主机和CPU都可 都可 以对HPI控制积存器(HPIC)进行访问,主机一方还 控制积存器( 以对 控制积存器 )进行访问, 可以访问HPI地址寄存器以及 可以访问 地址寄存器以及HPI数据寄存器. 数据寄存器. 地址寄存器以及 数据寄存器

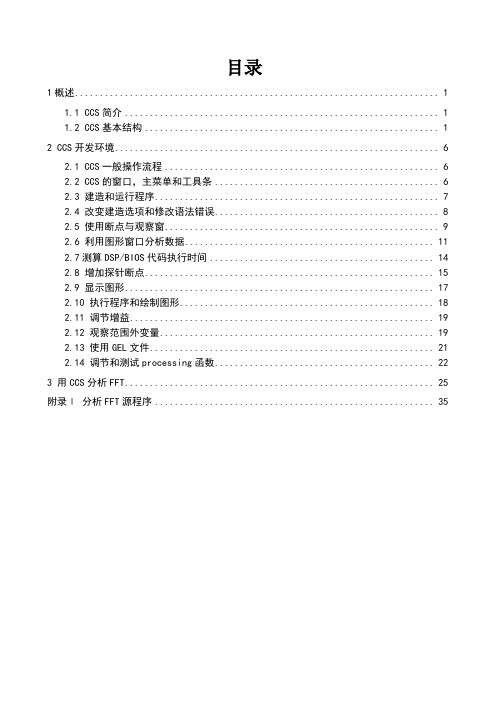

CCS_DSP开发环境教程

CCS_DSP开发环境教程第二步:配置DSP开发板在开始使用CCS_DSP开发环境之前,你需要将DSP开发板与你的计算机连接,并配置好相关硬件设置。

连接开发板到计算机的方法因开发板型号而异,你可以参考TI的开发板用户手册来了解具体的连接方法和配置过程。

第三步:创建新的CCS_DSP项目启动CCS_DSP开发环境后,你将看到一个工程资源视图,该视图列出了你所有的项目和文件。

要创建一个新的CCS_DSP项目,你可以右键单击工程资源视图中的空白处,然后选择“新建项目”选项。

在弹出的对话框中,选择DSP型号和目标设备,并为你的新项目指定一个名称和存储路径。

第四步:配置项目设置创建完新项目后,你需要配置一些项目设置,以便让CCS_DSP开发环境正确地编译、运行和调试你的应用程序。

在新项目的属性设置中,你可以指定编译器选项、调试器选项和目标设备选项等。

这些设置可能因具体项目而异,你可以根据实际需求进行修改。

第五步:编写代码第六步:编译和构建项目完成代码编写后,你可以利用CCS_DSP开发环境的编译器将你的代码编译成可执行文件。

首先,你需要选择“生成”选项来编译你的代码。

如果代码没有错误,编译过程将会成功完成,并生成可执行文件。

你还可以在编译过程中查看编译日志和编译警告等信息。

第七步:调试和测试应用程序在构建完成后,你可以使用CCS_DSP开发环境提供的调试器工具来调试和测试你的应用程序。

通过连接开发板和计算机,你可以在CCS_DSP中启动调试会话,并逐步执行你的代码,查看变量的值和程序的执行路径等信息。

你还可以设置断点、监视表和观察窗口等来辅助调试。

第八步:优化和部署应用程序一旦你的应用程序在调试过程中没有问题,你可以将它优化并部署到目标设备上。

CCS_DSP提供了许多优化选项和工具,可以帮助你提高DSP 应用程序的性能。

你可以根据具体需求选择合适的优化方式,并通过CCS_DSP将优化后的应用程序烧录到目标设备上。

dsp硬件设计课程设计

dsp硬件设计课程设计一、教学目标本课程的教学目标是使学生掌握DSP硬件设计的基本原理和方法,培养学生进行DSP硬件系统设计和实现的能力。

具体目标如下:1.掌握DSP芯片的基本结构和原理。

2.了解DSP硬件设计的基本流程和步骤。

3.熟悉DSP系统的硬件架构和关键模块。

4.能够使用DSP芯片进行硬件系统设计。

5.能够进行DSP系统的硬件调试和验证。

6.能够分析和解决DSP硬件设计中遇到的问题。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.培养学生对DSP硬件设计的兴趣和热情。

3.培养学生对科技发展的关注和对工程实践的重视。

二、教学内容本课程的教学内容主要包括以下几个部分:1.DSP芯片的基本结构和原理:介绍DSP芯片的内部结构、工作原理和特性。

2.DSP硬件设计的基本流程和步骤:讲解DSP硬件设计的过程,包括需求分析、硬件架构设计、硬件电路设计、硬件调试和验证等。

3.DSP系统的硬件架构和关键模块:介绍DSP系统的硬件架构,包括中央处理单元、存储器、输入输出接口等关键模块。

4.DSP硬件设计的实践案例:通过实际案例分析,使学生掌握DSP硬件设计的方法和技巧。

三、教学方法本课程的教学方法将采用多种教学手段相结合的方式,以激发学生的学习兴趣和主动性。

1.讲授法:通过教师的讲解,使学生掌握DSP硬件设计的基本原理和方法。

2.讨论法:通过分组讨论和实践案例的分析,培养学生的思考能力和团队合作精神。

3.实验法:通过实验操作,使学生熟悉DSP硬件设计的实践过程和技巧。

四、教学资源本课程的教学资源包括教材、参考书、多媒体资料和实验设备等。

1.教材:选择适合本课程的教材,为学生提供系统的学习资料。

2.参考书:提供相关的参考书籍,为学生提供更多的学习资源。

3.多媒体资料:制作课件和教学视频,以图文并茂的形式展示教学内容。

4.实验设备:提供DSP实验板和相关的实验设备,为学生提供实践操作的机会。

五、教学评估本课程的教学评估将采用多元化评估方式,全面客观地评价学生的学习成果。

开发DSP硬件驱动程序的一种方法

开发DSP硬件驱动程序的一种方法目前,TI公司的应用很广泛,随着DSP的功能越来越强大,片上外设种类及应用日趋复杂。

传统的DSP程序开发包含两方面程序:即配置、控制、中断等管理DSP片内外设、接口的硬件相关程序和基于应用的算法程序。

这样的系统结构,应用程序与硬件相关程序紧密的结合一起,限制了程序的可移植性和通用性,软件开发总要从零开头,存在诸多重复工作。

一旦硬件平台有变幻,往往与硬件程序捆绑一起的应用程序也需改动,代码的维护性和可移植性均不高。

通过建立硬件驱动程序的开发模式,可使上述现象得到充实。

因此,本文介绍一种开发TI公司DSP片内及片外硬件外设驱动程序的办法,并以C5000 DSP的McBSP/DMA及TMS320C5509的驱动程序开发为详细对象,介绍这种办法的应用。

基于DSP/BIOS的IOM硬件驱动在CCS应用环境中集成的实时操作系统DSP/BI-OS[1]中,硬件驱动程序终于以函数库的形式被封装起来,应用程序可不关怀底层硬件外设的详细操作,通过调用DSP/BIOS相关的标准API与不同外设接口。

接口按统一标准定义,即在DSP/BIOS中创建并配置硬件设备驱动模块为IOM(I/O Mini-driver)模式。

IOM[2]是DSP/BIOS的设备驱动模块的一种接口方式,配置硬件设备驱动模块为IOM模式可在DSP/BIOS的图形化界面(GUI)中便利完成。

IOM 模式将设备驱动程序分为两个层次:上一层是"类"驱动程序(class driv-er),这部分程序负责对存储缓冲区管理、由DSP/BIOS各类标准的API函数与应用程序接口,与设备硬件无关。

下一层是"迷你"驱动程序 (mini-driver),这部分程序集成了实际硬件相关的代码。

IOM 接口将"迷你"驱动程序与"类"驱动程序联系一起,包括定义I/O数据包 (IOM_Packet)以提交"迷你"驱动程序读写,定义功能函数包(IOM Fxns)完成相关初始化,打开或关闭通道,提交I/O数据传输与控制等任务,确保"迷你"驱动程序与"类"驱动程序运行协调全都。

数字音频DSP开发流程

选择正确的架构开发人员在开发数字信号处理应用时,根据他们的系统注意事项有多种架构可供选择。

数字信号处理器 (DSP) | ARM 与通用处理器 (GPP) | 微处理器 (MCU) | 专用集成电路 (ASIC) | 现场可编程门阵列 (FPGA) | 专用标准产品 (ASSP)•数字信号处理 (DSP)已成为数字革命的基础。

在手机的核心部分、音频和视频播放器、数码摄像机、电话基础设施、电机控制系统、甚至生物辨识安全设备中,您都能找到数字信号处理器 (DSP)。

不用太强的技术性,大多数信号处理函数将两列数字相乘,然后把结果相加:结果= x1 * c1 + x2 * c2 + x3 * c3 …xn * cn与通用处理器 (GPP) 相比,DSP 更加适合于信号处理应用。

DSP 提供了许多架构特性,有效减少了进行高效信号处理所需的指令数。

换言之,比较性能比计算指令数更加重要。

您真正需要测量的是实际完成的工作量。

例如,TI 的 C64x 系列 DSP 的 VLIW 架构每个周期时钟最多能够启动 8 个操作。

集成的专门计算引擎通过执行硬件中的复杂函数提高性能。

DSP 还通过提供性能、集成外设和片上存储器的平衡组合,针对特定应用进行优化。

DSP 的可编程灵活性让开发人员能在软件中执行复杂的算法。

DSP 不但能够支持视频编解码器(例如 MPEG-2)以及使用简单的软件升级方便地处理不同的分辨率,它还能实施新兴的编解码器和标准,因为它们不用硬件重新设计就能升级。

如果低功率、高性能、功能灵活性和上市时间是主要考虑因素,那么 DSP 是绝佳选择。

o来源:DSP 和 ARM MPU 选择工具页首•ARM 与通用处理器 (GPP)提供可编程性,因此具有灵活性。

但是,许多非信号处理应用,例如电子邮件、数据库管理和文字处理则不要求乘法的扩展使用。

为了不断降低这些应用的芯片成本,GPP 通常适度地提供需要几个周期来完成的高效乘法指令。

DSP开发环境和流程的简单例程

图1-3典型的软件开发流程图

1.2.3硬件仿真和实时数据交换

TI DSPs提供在片仿真支持,它使得CCS能够控制程序的执行,实时监视程序运行。增强型JTAG连接提供了对在片仿真的支持,它是一种可与任意DSP系统相连的低侵扰式的连接。仿真接口提供主机一侧的JTAG连接,如TI XSD510。为方便起见,评估板提供在板JTAG仿真接口。

图2-2装载程序

图2-3反汇编(Disassembly)窗口

现在可以开始运行我们的程序:在主菜单中单击“Debug”,选择“Go Main”,让程序从主函数开始执行。程序会停在main()处,并会有一个黄色的箭头标记当前要执行的C语言代码。如果希望同时看到C语言代码和对应编译生成的汇编代码,在主菜单中单击“View”,选择“Mixed Source/ASM”,此时会有一个绿色的箭头量标记当前要执行的汇编代码,如图2-4所示。

此时,在浅灰色显示的汇编指令上单击鼠标,然后按F1键,CCS会对该汇编指令进行搜索并弹出帮助窗进行解释。可以利用该功能来了解不熟悉的汇编指令。

在主菜单中单击“Debug”,选择“Run”,或单击工具条图标(Run),让程序全速执行。在主菜单中单击“Debug”,选择“Halt”,或单击工具条(Halt),让程序退出运行。

工程窗口用来组织用户的若干程序构成一个项目,用户可以从工程列表中选中需要编译和调试的特定程序。在源程序编译/调试窗口中用户既可以编译程序又可以设置断点、探针,调试程序。反汇编窗口可以帮助用户查看机器指令,查找错误。内存和寄存器显示窗口可以查看、编辑内存单元和寄存器。图形显示窗口可以根据用户需要直接或经过处理后显示数据。用户可以通过主菜单Windows条目来管理窗口。

第2章 DSP硬件开发系统的使用(C55x DSP)

第2章 DSP硬件开发系统的使用 ICETEK-5100USB V2.0A仿真器实物说明如图2-1所示, 其中USB接口负责与计算机USB接口相连接,在计算机开机 时,当仿真器USB接口与计算机USB接口连接好时,红色的 电源指示灯将会亮,如果不亮,请检查是否连接好。JTAG 仿真接口用于与目标板上DSP的JTAG仿真接口的插头相连, 为了防止反插,一般将JTAG接口的6脚堵上,其引脚定义如 图2-2所示。

第2章 DSP硬件开发系统的使用

图2-3 ICETEK–VC5509-AE评估板接口说明实物图

第2章 DSP硬件开发系统的使用 2.1.5 仿真器驱动程序的安装 仿真器使用的驱动软件是Blackhawk XDS510 Driver CCS v3.1.。运行驱动软件BH510-SetupCCS_v3.1.5.1.exe,用 户可以安装在与CCS v3.1同一个目录下,也可以单击Custom Location选择相应的路径。本实验安装在CCS v3.1同一个目 录下,其路径为C:\CCStudio_v3.1,安装界面如图2-4所示。

图2-8 安装驱动软件BH510-SetupCCS_v3.1.5.1.exe界面(五)

第2章 DSP硬件开发系统的使用 (5) 单击OK按钮,就进入了如图2-9所示的安装界面。

第2章 DSP硬件开发系统的使用

图2-9 安装驱动软件BH510-SetupCCS_v3.1.5.1.exe界面(六)

第2章 DSP硬件开发系统的使用 (6) 在图2-9所示的安装界面上点击Install按钮进行安装, 直到安装结束。

第2章 DSP硬件开发系统的使用

图2-11 USB接口的硬件配置

第2章 DSP硬件开发系统的使用 (4) 硬件仿真设置可以在CCS_v3.1仿真环境中进行,可 在主菜单中选择File→Import命令进行导入设置,也可以从 Factory Boads中加入设置,或者从Creats Board选项卡中创 建设置。在这里只介绍从Creats Board选项卡中创建设置, 前两种方法由读者自行研究。

dsp芯片开发流程

dsp芯片开发流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!DSP 芯片开发流程。

1. 需求分析。

收集和分析客户对 DSP 芯片的需求,包括功能、性能、成本、尺寸等。

简述使用dsp芯进行系统开发的一般流程

简述使用DSP芯片进行系统开发的一般流程1. 概述DSP(Digital Signal Processor)芯片是一种专门用于处理数字信号的芯片,广泛应用于通信、音视频处理等领域。

使用DSP芯片进行系统开发需要经过一系列的步骤和流程,本文将简要介绍一般的开发流程。

2. DSP系统开发流程2.1 需求分析首先,在进行DSP系统开发之前,需进行需求分析,明确系统的功能和性能要求。

根据需求,确定DSP芯片的型号和规格,并确定系统的硬件和软件接口要求。

2.2 硬件设计硬件设计是DSP系统开发的重要一环。

根据需求分析,进行DSP系统的硬件设计,包括电路原理图和PCB设计。

在设计过程中,需要考虑电源、时钟、接口电路等因素,确保硬件设计满足系统要求。

2.3 软件设计软件设计是DSP系统开发的关键环节。

根据需求和硬件设计,进行DSP系统的软件设计。

具体步骤包括编写算法和信号处理流程、选择适当的编程语言和开发工具、设计系统框架和接口等。

2.4 软件开发在软件设计的基础上,进行DSP系统的软件开发。

根据软件设计确定的算法和接口,使用相应的编程语言和开发工具,编写软件代码。

在开发过程中,需要进行代码调试、性能优化和错误修复等工作。

2.5 硬件调试完成软件开发后,进行DSP系统的硬件调试。

通过连接电源、外部设备和接口,对DSP系统进行调试和测试。

此阶段还可以进行性能测试和功能验证。

2.6 系统集成在完成硬件调试后,进行DSP系统的系统集成。

将软件和硬件组合起来,确保系统正常运行。

在此阶段,需要进行整体测试和交付前的验收。

2.7 产品发布和维护完成系统集成后,进行DSP系统的产品发布。

将DSP系统交付给客户或用于实际应用。

同时,需要进行系统的维护和迭代,及时修复BUG和优化性能。

3. 总结使用DSP芯片进行系统开发涉及多个步骤和流程,包括需求分析、硬件设计、软件设计、软件开发、硬件调试、系统集成、产品发布和维护等。

通过合理的规划和有序的流程,可以确保DSP系统开发的顺利进行,并最终得到可靠和高性能的系统。

使用CCS软件开发DSP的流程

使用CCS软件开发DSP的流程1. 概述在进行DSP(Digital Signal Processor,数字信号处理器)开发时,使用CCS (Code Composer Studio)软件可以提供一套全面的开发环境和工具集。

本文将介绍使用CCS软件开发DSP的流程和基本步骤。

2. 准备工作在开始使用CCS软件开发DSP之前,需要进行一些准备工作,包括: - 安装CCS软件:前往官网下载最新版本的CCS软件,并按照官方指南进行安装。

- 选择合适的DSP平台:根据项目需求选择合适的DSP芯片,并了解该DSP芯片的技术规格和开发文档。

- 准备开发板:根据选择的DSP芯片,准备相应的开发板,并进行连接和配置。

3. 创建项目在CCS软件中创建一个新的项目是开始开发DSP的第一步。

以下是创建项目的步骤: 1. 打开CCS软件,点击“File”菜单,选择“New”的选项。

2. 在新建项目对话框中,选择“CCS Project”,并点击“Next”按钮。

3. 输入项目名称和存储路径,选择目标DSP芯片型号,并点击“Finish”按钮。

4. 编写代码一旦项目创建完成,可以开始编写DSP代码。

以下是编写代码的步骤: 1. 在CCS软件中打开新建的项目。

2. 在项目资源管理器中,选择“Source Files”文件夹,右键点击并选择“New”的选项。

3. 在新建文件对话框中,输入文件名称和文件类型(.c或.cxx),并点击“Finish”按钮。

4. 在新建的源文件中编写DSP相关的代码,可以使用CCS提供的开发工具和库函数。

5. 编译和调试完成代码编写后,需要对代码进行编译和调试。

以下是编译和调试的步骤: 1.点击CCS软件界面上的“Build”按钮,进行代码的编译和构建。

2. 在构建完成后,选择“Debug”菜单,点击“Start Debug Session”选项,进入调试模式。

3. 在调试模式下,可以设置断点、单步执行、查看变量和寄存器等操作,以调试和验证代码的正确性。

C6000 DSP硬件板卡开发1

1.原理框图设计

RJ45

DDRII SDRAM DDRII SDRAM DDRII SDRAM DDRII SDRAM

光纤 接口 (4个)

C6474

C6474

C6474

C6474

2个1x AIF 两两之间各 2个1x通道

Design file: AED0.TLN Designer: Image BoardSim/LineSim, HyperLynx 7.000 Probe 1:U(A0)

6.000

5.000

4.000

4.000

3.000

3.000

V ol t ag e -V -

V ol t ag e -V -

2.000

--程序ROM寻址空间的扩展问题

3.DSP最小系统设计

3.电源—加电顺序要求

3.DSP最小系统设计

3.电源—加电顺序控制方法

(方法1)

(方法2)

3.DSP最小系统设计

3.电源—加电顺序控制方法

方法3

方法4

ห้องสมุดไป่ตู้

3.DSP最小系统设计

3.电源—电源监测需求

为了保证C6000芯片在电源未达到要求的电平时,不会产生不受 控制的状态,建议在系统中加入电源监测电路。该电路能确保在系统 加电的过程中,DVdd和CVdd达到要求的电平之前,DSP 始终处于 复位状态。同时,一旦电源电压降到一定的门限值以下(例如88%), 将强制芯片进入复位状态。

起始地址 (0X) 00800000 E0000000 A0000000 B0000000 C0000000 D0000000

终止地址 (0X) 00A00000 FFFFFFFF A0800000 B0400000 C0002000 D0002000

简述dsp的应用软件开发流程

简述dsp的应用软件开发流程英文回答:DSP (Digital Signal Processing) software development involves a series of steps to create applications that process digital signals. These applications are used in various fields such as telecommunications, audio processing, image and video processing, and control systems. In this answer, I will outline the general process of developing DSP software.First, the development process starts with requirements gathering. This involves understanding the specific needs and goals of the DSP application. For example, if we are developing an audio processing application, therequirements could include noise reduction, equalization, and audio enhancement.Once the requirements are defined, the next step is system design. This involves designing the overallarchitecture of the DSP application and deciding on the algorithms and techniques to be used. For example, in the audio processing application, we might decide to use a Fast Fourier Transform (FFT) algorithm for frequency analysis and a digital filter for noise reduction.After the system design is complete, the next step is algorithm development. This involves implementing the chosen algorithms and techniques using programming languages such as C or MATLAB. For example, we would write code to perform the FFT and digital filtering operations.Once the algorithms are implemented, the next step is integration and testing. This involves combining all the individual components of the DSP application and testing their functionality. For example, we would test the audio processing application by inputting different audio signals and evaluating the output for noise reduction and equalization.After successful integration and testing, the next step is optimization and performance tuning. This involvesoptimizing the code and algorithms to improve theefficiency and speed of the DSP application. For example, we might optimize the FFT algorithm to reduce the computational complexity and improve real-time performance.Once the optimization is complete, the final step is deployment and maintenance. This involves deploying the DSP application in the target environment and providing ongoing support and maintenance. For example, we might deploy the audio processing application on a mobile device or a dedicated DSP hardware.In summary, the DSP software development process involves requirements gathering, system design, algorithm development, integration and testing, optimization, and deployment. Each step is crucial for creating efficient and reliable DSP applications that meet the specific requirements of the target domain.中文回答:DSP(数字信号处理)软件开发涉及一系列步骤,用于创建处理数字信号的应用程序。

DSP系统设计开发流程

DSP系统设计开发流程在设计需求规范,确定设计目标时,其实要解决二个方面的问题:即信号处理方面和非信号处理的问题。

信号处理的问题包括:输入、输出结果特性的分析,DSP算法的确定,以及按要求对确定的性能指标在通用机上用高级语言编程仿真。

非信号处理问题包括:应用环境、设备的可靠性指标,设备的可维护性,功耗、体积重量、成本、性能价格比等项目。

算法研究与仿真这是DSP应用实际系统设计中重要的一步。

系统性能指标能否实现,以何种算法和结构应对需求,都是在这一步考虑的。

这种仿真是在通用机上用高级语言编程实现的,编程时最好能仿DSP处理器形式运行,以达到更好的真实性。

DSP芯片选择中通常有下列几条应注意的:(1)精度:表数格式(定点或浮点),通常可以用定点器件解决的问题,尽量用定点器件,因为它经济、速度快、成本低,功耗小。

但是在编程时要关注信号的动态范围,在代码中增加限制信号动态范围的定标运算。

(2)字长的选择:一般浮点DSP芯片都用32位的数据字,大多数定点DSP芯片是16位数据字。

而MOTOROLA公司定点芯片用24位数据字,以便在定点和浮点精度之间取得折中。

字长大小是影响成本的重要因素,它影响芯片的大小、引脚数以及存储器的大小,设计时在满足性能指标的条件下,尽可能选用最小的数据字。

(3)存储器安排:包括存储器的大小,片内存储器的数量,总线寻址空间等。

片内存储器的大小决定了芯片运行速度和成本,例如TI公司同一系列的DSP芯片,不同种类芯片存储器的配置等硬件资源各不相同。

(4)开发工具:在DSP系统设计中,开发工具是必不可少的,一个复杂的DSP系统,必须有功能强大的开发工具支持。

开发工具包括软件和硬件两部分。

软件开发工具主要包括:C编译器、汇编器、链接器、程序库、软件仿真器等,在确定DSP算法后,编写的程序代码通过软件仿真器进行仿真运行,来确定必要的性能指标。

硬件开发工具包括在线硬件仿真器和系统开发板。

在线硬件仿真器通常是JTAG周边扫描接口板,可以对设计的硬件进行在线调试;在硬件系统完成之前,不同功能的开发板上实时运行设计的DSP软件,可以提高开发效率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

远见品质

2.程序ROM—接口

BCE1 AOE AWE BEA[N+1:1] EMIFB BED[7:0] ARE VDD ARDY

CE OE WE A[N:0] FLASH D[7:0]

PDF 文件使用 "pdfFactory Pro" 试用版本创建

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质

v DSPs硬件系统组成 v DSPs芯片的选择 v DSPs最小系统设计 v DSPs的结构及外设接口 v DSPs系统设计

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质

DSPs芯片的选择(3)

v 存储器容量

Ø 内存 Ø 外存

PDF 文件使用 "pdfFactory Pro" 试用版本创建

含义

BECLKIN管脚外输入 1/4 CPU时钟 1/6 CPU时钟 保留 禁止(PCI_EN=0时必须禁止) 使能(初始化时刻McBSP2_EN 必须为0) 禁止(McBSP1使能) 使能(McBSP1禁止) 禁止 使能 HPI16 HPI32 禁止 使能

BEA11 PCI_EN HD5 McBSP2_EN

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质 设置内容 设置管脚

1.功能设置(2)

数值

B’00’ EMIFB接口时钟选择 BEA[15:14] B’01’ B’10’ B’11’ PCI接口由EEPROM自 动配置 UTOPIA接口使能 PCI接口使能 HPI宽度选择 McBSP2接口使能 B’0’ BEA13 B’1’ B’0’ B’1’ B’0’ B’1’ B’0’ B’1’ B’0’ B’1’

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质

DSPs芯片的选择(4)

v 数据格式

Ø 定点 vs. 浮点

PDF 文件使用 "pdfFactory Pro" 试用版本创建

PDF 文件使用 "pdfFactory Pro" 试用版本创建

PDF 文件使用 "pdfFactory Pro" 试用版本创建

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质

DSPs芯片的选择(1)

v GPP vs. DSPs vs. ASIC

PDF 文件使用 "pdfFactory Pro" 试用版本创建

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质

DSPs系统组成

A/D

DSP

D/A、 数 字 IO 等

MEM

PDF 文件使用 "pdfFactory Pro" 试用版本创建

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质

DSPs芯片的选择(5)

v 电源管理和功耗

Ø 降低工作电压 Ø “休眠”或“空闲”模式 Ø 可编程时钟分频器

远见品质

2.程序ROM—编程(2)

PDF 文件使用 "pdfFactory Pro" 试用版本创建

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质

最小系统组成(1)

一个DSPs要能够正常的运行程 序完成简单的任务,并能够通过 JTAG被调试,它的最小系统应该 包括DSPs芯片、电源、时钟源、复 位电路、JTAG电路、程序ROM以 及对芯片所做的设置。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

远见品质

v DSPs硬件系统组成 v DSPs芯片的选择 v DSPs最小系统设计 v DSPs的结构及外设接口 v DSPs系统设计

PDF 文件使用 "pdfFactory Pro" 试用版本创建 wÿ

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

远见品质

最小系统组成(2)

电源

I/O 电压 核 电压

时钟 源

时钟 管理

复位 电路

DSPs

‘上下拉’ 功能 设置 EMIF 接口 JTAG 口 JTAG 电路

远见品质

DSPs芯片的选择(2)

v DSPs的速度

Ø 算法计算的时间 < 系统提供的时间 Ø 时间估算最可靠的方法是对信号处理算法的 “核心”功能(往往占运算量80%以上,但代 码小于20%)进行编程仿真(Simulation) Ø 选择要有富裕量,以便系统功能的增加或升 级。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

DSPs硬件开发

刘国满

PDF 文件使用 "pdfFactory Pro" 试用版本创建 ÿ

远见品质

2.程序ROM—自加载

指令 1 低 8bit 指令 1 中 8bit 指令 1 中 8bit 指令 1 高 8bit 指令 2 低 8bit • • • 片外程序 ROM 或 Flash

Boot 自加载 指令 1 字 32bit(或指令包) • • • 片内程序 RAM

加载后 PC 指针

PDF 文件使用 "pdfFactory Pro" 试用版本创建

程序 ROM

PDF 文件使用 "pdfFactory Pro" 试用版本创建 ÿ

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.SPs的一些I/O管脚是双向的,方向 由内核控制。I/O电压一旦被加上以后, I/O管脚就立即被驱动,如果此时还没加 核电压,那么I/O的方向可能就不确定是 输入还是输出。如果是输出,且这时与 之相连的其它器件的管脚也处于输出状 态,那么就会造成时序的紊乱或者对器 件本身造成损伤。这种情况下,就需要 核电压比I/O电压先加载,至少是同时加 载。

远见品质

1.功能设置(1)

设置内容 设置管脚 数值

B’00’ 片内锁相环模式 CLKMODE[1:0] B’01’ B’10’ B’11’ 芯片的ENDIAN模式 BEA20 B’0’ B’1’ B’00’ 芯片的引导模式 BEA[19:18] B’01’ B’10’ B’11’ B’00’ EMIFA接口时钟选择 BEA[17:16] B’01’ B’10’ B’11’

PDF 文件使用 "pdfFactory Pro" 试用版本创建 wÿ

Edited by Foxit PDF Editor Copyright (c) by Foxit Software Company, 2004 - 2007 For Evaluation Only.

含义

1倍频 6倍频 12倍频 保留或20倍频 Big Endian Little Endian 无加载 主机加载 8bit ROM加载 保留 AECLKIN管脚外输入 1/4 CPU时钟 1/6 CPU时钟 保留

PDF 文件使用 "pdfFactory Pro" 试用版本创建 À