电子元件封装形式大全演示教学

常用PCB封装图解

常用集成电路芯片封装图doc文档可能在WAP端浏览体验不佳。

建议您优先选择TXT,或下载源文件到本机查看。

PCB 元件库命名规则2.1 集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N 和W 两种,用来表示器件的体宽N 为体窄的封装,体宽300mil,引脚间距2.54mm W 为体宽的封装, 体宽600mil,引脚间距 2.54mm 如:DIP-16N 表示的是体宽300mil,引脚间距2.54mm 的16 引脚窄体双列直插封装 2.2 集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M 和W 三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距 1.27mm M 为介于N 和W 之间的封装,体宽208mil,引脚间距1.27mm W 为体宽的封装, 体宽300mil,引脚间距 1.27mm 如:SO-16N 表示的是体宽150mil,引脚间距1.27mm 的16 引脚的小外形贴片封装若SO 前面跟M 则表示为微形封装,体宽118mil,引脚间距0.65mm 2.3 电阻 2.3.1 SMD 贴片电阻命名方法为:封装+R 如:1812R 表示封装大小为1812 的电阻封装2.3.2 碳膜电阻命名方法为:R-封装如:R-AXIAL0.6 表示焊盘间距为0.6 英寸的电阻封装 2.3.3 水泥电阻命名方法为:R-型号如:R-SQP5W 表示功率为5W 的水泥电阻封装 2.4 电容 2.4.1 无极性电容和钽电容命名方法为:封装+C 如:6032C 表示封装为6032 的电容封装 2.4.2 SMT 独石电容命名方法为:RAD+引脚间距如:RAD0.2 表示的是引脚间距为200mil 的SMT 独石电容封装 2.4.3 电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4 表示引脚间距为200mil, 外径为400mil 的电解电容封装 2.5 二极管整流器件命名方法按照元件实际封装,其中BAT54 和1N4148 封装为1N4148 2.6 晶体管命名方法按照元件实际封装,其中SOT-23Q 封装的加了Q 以区别集成电路的SOT-23 封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名 2.7 晶振HC-49S,HC-49U 为表贴封装,AT26,AT38 为圆柱封装,数字表规格尺寸如:AT26 表示外径为2mm,长度为8mm 的圆柱封装 2.8 电感、变压器件电感封封装采用TDK 公司封装 2.9 光电器件 2.9.1 贴片发光二极管命名方法为封装+D 来表示如:0805D 表示封装为0805 的发光二极管 2.9.2 直插发光二极管表示为LED-外径如LED-5 表示外径为5mm 的直插发光二极管2.9.3 数码管使用器件自有名称命名 2.10 接插件 2.10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm 如:SIP7-2.54 表示针脚间距为 2.54mm 的7 针脚单排插针 2.10.2 DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm 如:DIP10-2.54 表示针脚间距为2.54mm 的10 针脚双排插针 2.10.3 其他接插件均按E3 命名 2.11 其他元器件详见《Protel99se 元件库清单》3 SCH 元件库命名规则3.1 单片机、集成电路、二极管、晶体管、光电器件按照器件自有名称命名 3.2 TTL74 系列和COMS 系列是从网上找的元件库,封装和编码需要在画原理图时重新设定 3.3 电阻 3.3.1 SMD 电阻用阻值命名,后缀加-F 表示1%精度,如果一种阻值有不同的封装,则在名称后面加上封装如:3.3-F-1812 表示的是精度为1%,封装为1812,阻值为 3.3 欧的电阻 3.3.2 碳膜电阻命名方法为:CR+功率-阻值如:CR2W-150 表示的是功率为2W,阻值为150 欧的碳膜电阻 3.3.3 水泥电阻命名方法为:R+型号-阻值如:R-SQP5W-100 表示的是功率为5W,阻值为100 欧的水泥电阻 3.3.4 保险丝命名方法为:FUSE-规格型号,规格型号后面加G 则表示保险管如:FUSE-60V/0.5A 表示的是60V,0.5A 的保险丝 3.4 电容3.4.1 无极性电容用容值来命名,如果一种容值有不同的封装,则在容值后面加上封装。

LED 引脚式封装课件

关于LED封装

第六页,编辑于星期日:十三点 十三分。

LED封装的光学问题

LED的pn结电子和空穴的复合产生可见、紫外、 红外光。

pn结发出的光向各个方向的几率相同。 为了使光尽可能发射到感兴趣的方向上,LED

封装要考虑封装结构对光的变换作用,即一次 光学设计。

关于LED封装

第七页,编辑于星期日:十三点 十三分。

一、引脚式封装引言

第十六页,编辑于星期日:十三点 十三分。

引脚式封装工艺流程及设备

1、划片机——划片

二、工艺流程及选用设备

第十七页,编辑于星期日:十三点 十三分。

2、芯片分选机——芯片分选

二、工艺流程及选用设备

第十八页,编辑于星期日:十三点 十三分。

3、芯片扩张机——芯片扩张

二、工艺流程及选用设备

第三十页,编辑于星期日:十三点 十三分。

15、烘干箱——烘干

二、工艺流程及选用设备

第三十一页,编辑于星期日:十三点 十三分。

16、LED分选机——分选

二、工艺流程及选用设备

第三十二页,编辑于星期日:十三点 十三分。

17、打包机(手动)——打包

二、工艺流程及选用设备

第三十三页,编辑于星期日:十三点 十三分。

三、管理机制和生产环境

做好LED的四大重要因素 人、物、设备、生产环境

说明:

只是从生产的角度 公司企业:物料采购、生产、销售、人事、财务、

信息——企业六管

三、管理机制和生产环境

第三十六页,编辑于星期日:十三点 十三分。

管理机制

ISO9000质量体系 国际标准化组织(International Organization

2.1 引脚式封装

(整理)最全的芯片封装方式图文对照.

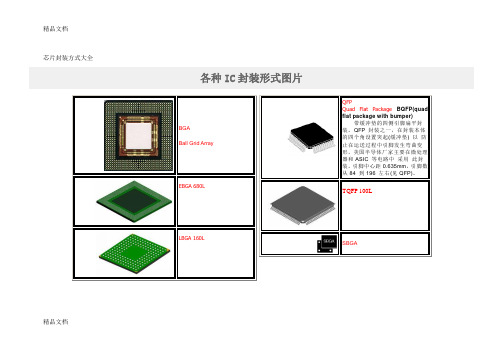

芯片封装方式大全各种IC 封装形式图片BGABall Grid Array EBGA 680L LBGA 160L QFPQuad Flat Package BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

TQFP 100LSBGA精品文档PBGA 217LPlastic Ball Grid Array SBGA 192LTSBGA 680L SC-70 5LSDIPSIPSingle Inline PackageSOSmall Outline Package精品文档CLCCCNRCommunication and Networking Riser Specification Revision 1.2CPGACeramic Pin Grid Array SOJ 32LSOJSOP EIAJ TYPE II 14L SOT220精品文档DIPDual Inline PackageDIP-tabDual Inline Package with Metal HeatsinkFBGAFDIP SSOP 16L SSOPTO18精品文档FTO220 Flat Pack HSOP28TO220 TO247 TO264精品文档ITO220 ITO3p JLCC LCC TO3 TO5 TO52 TO71精品文档LDCC LGA LQFP PCDIP TO72 TO78 TO8 TO92精品文档PGAPlastic Pin Grid ArrayPLCC详细规格PQFPPSDIP TO93TO99TSOPThin Small Outline PackageTSSOP or TSOP IIThin Shrink Outline Package精品文档LQFP 100L详细规格METAL QUAD 100L 详细规格PQFP 100L详细规格uBGAMicro Ball Grid ArrayuBGAMicro Ball Grid ArrayZIPZig-Zag Inline Package精品文档QFPQuad Flat Package SOT220SOT223 SOT223TEPBGA 288L TEPBGAC-Bend LeadCERQUADCeramic Quad Flat Pack详细规格精品文档SOT23SOT23/SOT323 SOT25/SOT353 SOT26/SOT363 SOT343Ceramic CaseLAMINATE CSP 112L Chip Scale Package 详细规格Gull Wing Leads LLP 8La详细规格PCI 32bit 5V精品文档SOT523 SOT89 SOT89Peripheral Component Interconnect 详细规格PCI 64bit 3.3VPCMCIAPDIP精品文档Socket 603FosterLAMINATE TCSP 20L Chip Scale PackageTO252PLCC详细规格SIMM30Single In-line Memory Module SIMM72Single In-line Memory Module SIMM72Single In-lineSLOT 1For intel Pentium II Pentium III & Celeron CPU精品文档TO263/TO268SO DIMMSmall Outline Dual In-line Memory ModuleSOCKET 370For intel 370 pin PGA Pentium III & Celeron CPU SLOT AFor AMD Athlon CPU SNAPTKSNAPTKSNAPZPSOH精品文档SOCKET 423For intel 423 pin PGA Pentium 4CPUSOCKET 462/SOCKET AFor PGA AMD Athlon & DuronCPUSOCKET 7For intel Pentium & MMXPentium CPU精品文档各种封装缩写说明BGA 精品文档BQFP132BGA精品文档BGA 精品文档BGABGA 精品文档BGACLCCCNR 精品文档PGADIPDIP-tabBGA精品文档DIPTOFlat Pack 精品文档HSOP28TO精品文档TOJLCCLCCCLCC(ceramic leaded chip carrier)带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。

常用电子元件封装及介绍PPT课件

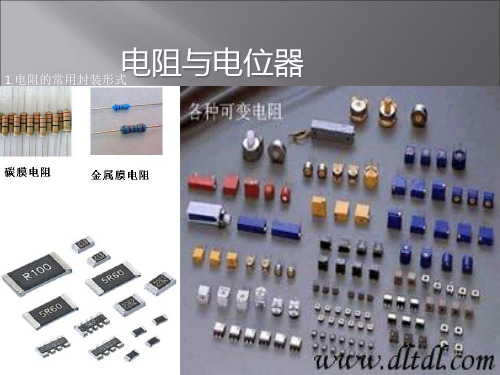

1.电阻的常用封装形式

2电阻表示方法

•直标法:直接标出阻值,百分数表示误差,若电阻上未注偏差,则均为±20%。 •数码法:算法:XXXY=XXX*10Y。 X为2位:多用于E-24系列,精度为J(±5%);例:272,表示2.7KΏ。 X为3位:多用于E-24、E-96系列,精度为F(±1%);例:3323,表示332KΏ。 Y为字母:前两位指有效数代码,具体值查E-96乘数代码表,后一位指10的几次 幂代码,从E-96阻值代码表查找;用于E-96系列,精度为F、D。用于E-96系列。 例:02C=102*102=10.2KΏ。 •文字符号法:m(豪欧)、R(欧)、K(千欧)、M(兆欧) ,例:6R2J,表示 6.2Ώ,允许偏差±5%。 •色标法:紧靠电阻体一端头的色环为第一环,末环表示允许误差,倒数第二环 表示乘数。 •封装:贴片电阻:0201、0402、0603、0805、1206、1210、1812、2010、2512 等,前两位与后两位分别表示长与宽,单位为英寸。 直插电阻:AXIAL-0.3、AXIAL-0.4、AXIAL-0.5、AXIAL-0.6、AXIAL-0.7、 AXIAL-0.8、AXIAL-0.9、AXIAL-1.0,数字表示焊盘中心距,单位为英寸。

适用场合:

以手机,PDA为代表的高密度电子产品多使用0201、0402的器 件;一些要求稳定和安全的电子产品,如医疗器械、汽车行驶 记录仪、税控机则多采用1206、1210等尺寸偏大的电阻。

碳膜电阻:

优点:

价格便宜,阻值范围宽 (从1ω-l0mω),具有良好的稳定性和高频特 性,电庇的变化对其阻值的影响很小,工作温度和极限电压都比 较高。温度系数和电压系数低. 缺点:承受的功率较小,一般是1/8-2w

第9章--制作元件封装PPT课件

正在编辑的元件封装图形放到已打开的PCB文件中。

•11

第9章 制作元件封装 “Rename”(元件改名)按钮:单击该按钮,可对

当前正在编辑的元件封装图形重新命名。 “ Add” ( 增 加 新 元 件 ) 按 钮 : 该 按 钮 的 作 用 与

2. 设置工作层、焊盘、过孔等显示颜色

执 行 “ Tools” 菜 单 下 的 “ Options” 命 令 , 在 弹 出 的 “Preferences”(特性选项)”窗内,有六项选项卡(Options、 Color、Display、Show/Hide、 Defaults、Signal Integrity),

第9章 制作元件封装

第9章 制作元件封装

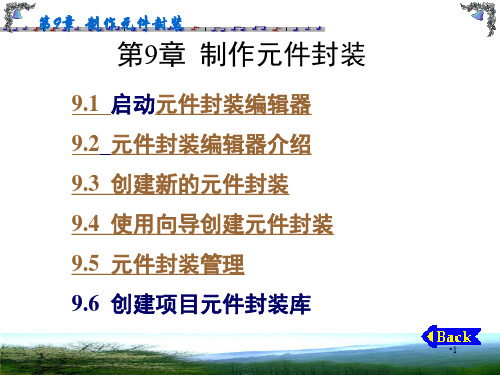

9.1 启动元件封装编辑器 9.2 元件封装编辑器介绍 9.3 创建新的元件封装 9.4 使用向导创建元件封装 9.5 元件封装管理 9.6 创建项目元件封装库

•1

第9章 制作元件封装

9.1 启动元件封装编辑器

元件封装编辑器(PCBLib)的启动:

启动Protel99SE印制板元件封装图编辑器的方法与 启动SCH、PCB等编辑器的方法相同。

•7

第9章 制作元件封装

•8

第9章 制作元件封装

图9-3 新建立的元件封装图形库

•9

第9章 制作元件封装

9.2 元件封装编辑器介绍

元件封装编辑器窗口: 元件封装(PCBLib)编辑器窗口如图9-2、9-3所示,

与印制电路板编辑器PCB窗口相似,窗口各部分名称及 作用如下:

1) Components(元件列表)窗 元件列表窗内显示了元件封装图形库内的元件,及当 前元件封装图形引脚焊盘。在元件列表窗下还有下列按 钮:

芯片封装详细图解通用课件

焊接方法主要有两种:热压焊接 和超声焊接。

焊接过程中需要控制温度、时间 和压力等参数,以保证焊接质量

和可靠性。

封装成型

封装成型是将已贴装和焊接好的芯片封装在保护壳内的过程。

封装材料主要有金属、陶瓷和塑料等。

成型过程中需要注意保护好芯片和引脚,防止损坏和短路。同时要保证封装质量和 外观要求。

质量检测

VS

详细描述

高性能的芯片封装需要具备低延迟、高传 输速率和低功耗等特性,以满足电子设备 在运行速度、响应时间和能效等方面的需 求。同时,高可靠性的封装能够确保芯片 在各种环境条件下稳定运行,提高产品的 使用寿命和可靠性。

多功能集成化

总结词

为了满足电子设备多功能化的需求,芯片封 装也呈现出多功能集成化的趋势。

02

芯片封装流程

芯片贴装

芯片贴装是芯片封装流程的第 一个环节,主要涉及将芯片按 照设计要求粘贴在基板上。

粘贴方法主要有三种:粘结剂 粘贴、导电胶粘贴和焊接粘贴 。

粘贴过程中需要注意芯片的方 向和位置,确保与设计要求一 致,同时要保的引脚与基板 的引脚对应焊接在一起的过程。

塑料材料具有成本低、重量轻、加工方便等优点,常用于 封装壳体和绝缘材料等。

常用的塑料材料包括聚苯乙烯、聚酯、聚碳酸酯等,其加 工工艺包括注塑成型、热压成型等。

其他材料

其他材料包括玻璃、石墨烯、碳纳米管等新型材料,具有优异的性能和广阔的应 用前景。

这些新型材料的加工工艺尚在不断发展和完善中。

05

芯片封装发展趋势

02

陶瓷材料主要包括95%Al2O3、 Al2O3-ZrO2、Al2O3-TiO2等, 其加工工艺包括高温烧结、等静 压成型和干压成型等。

金属材料

第2章 常用电子元器件的封装工艺(电子工艺与电子课件)

负极

电容耐压值: 6.3V

3.偏差

误差等级﹐一般采用六级

±1% ±2% ±5% ±10% ±20% ±80%-20%

F

G

J

KM

Z

E 332M 1KV SEC

温度特性 容值/误差 耐压值 生产厂商

陶瓷电容

ቤተ መጻሕፍቲ ባይዱ

电容容值的读取方法与电阻一样,如下表,单位 为pF。

0123456789

第一位 0 1 2 3 4 5 6 7 8 9

色环电阻阻值读取:

四色环电阻,以前两色环对应的数值为有效值,第三环为倍 率,第四环为精密度;

五色环电阻,以前三色环对应的数值为有效值,第四环为倍 率,第五环为精密度。

色码还可用来表示元器件的某项参数,原电子 工业部标准规定,用色点标在半导体三极管的 顶部,表示共发射极直流放大倍数β或hFE的分 档,其意义见下表:

按照使用范围及用途分:

普 能适应一般技术要求的电阻,额定功率范围 通 为0.05~2W,阻值为1Ω~22MΩ,允许偏 型 差±5%、±10%、±20%等。

精 有较高精密度及稳定性,功率一般不大于2 密 瓦,标称值在0.01Ω~20MΩ之间,精度在 型 ±2%~±0.001%之间分档。

高 电阻自身电感量极小,常称为无感电阻。用 频 于高频电路,阻值小于1kΩ,功率范围宽, 型 最大可达100W。

X

线绕

9 特殊 特殊

材料

分类

字母 代号

意义

数字

意

义

代号 温度 光敏 压敏

F 负温度系数热敏 1 普通 - 碳化硅 Z 正温度系数热敏 2 稳压 - 氧化锌

G

光敏

Y

压敏

S

湿敏

常用电子元器件的封装形式

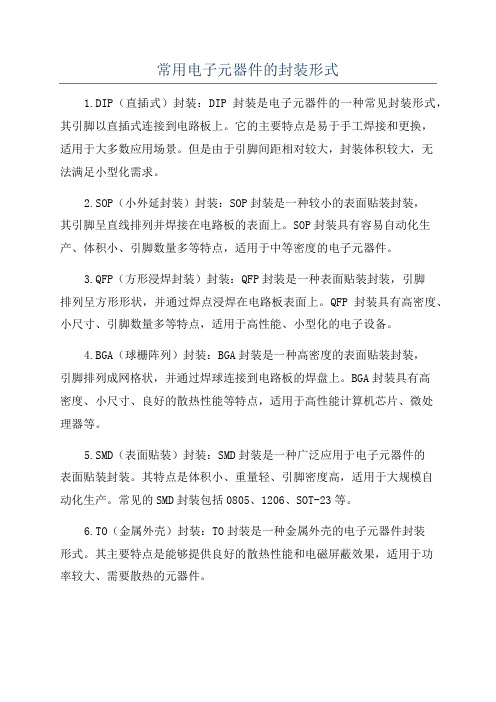

常用电子元器件的封装形式1.DIP(直插式)封装:DIP封装是电子元器件的一种常见封装形式,其引脚以直插式连接到电路板上。

它的主要特点是易于手工焊接和更换,适用于大多数应用场景。

但是由于引脚间距相对较大,封装体积较大,无法满足小型化需求。

2.SOP(小外延封装)封装:SOP封装是一种较小的表面贴装封装,其引脚呈直线排列并焊接在电路板的表面上。

SOP封装具有容易自动化生产、体积小、引脚数量多等特点,适用于中等密度的电子元器件。

3.QFP(方形浸焊封装)封装:QFP封装是一种表面贴装封装,引脚排列呈方形形状,并通过焊点浸焊在电路板表面上。

QFP封装具有高密度、小尺寸、引脚数量多等特点,适用于高性能、小型化的电子设备。

4.BGA(球栅阵列)封装:BGA封装是一种高密度的表面贴装封装,引脚排列成网格状,并通过焊球连接到电路板的焊盘上。

BGA封装具有高密度、小尺寸、良好的散热性能等特点,适用于高性能计算机芯片、微处理器等。

5.SMD(表面贴装)封装:SMD封装是一种广泛应用于电子元器件的表面贴装封装。

其特点是体积小、重量轻、引脚密度高,适用于大规模自动化生产。

常见的SMD封装包括0805、1206、SOT-23等。

6.TO(金属外壳)封装:TO封装是一种金属外壳的电子元器件封装形式。

其主要特点是能够提供良好的散热性能和电磁屏蔽效果,适用于功率较大、需要散热的元器件。

7.COB(芯片上下接插封装)封装:COB封装是一种将芯片直接粘贴到电路板上,并通过金线进行引脚连接的封装形式。

COB封装具有体积小、重量轻、引脚数量多等特点,适用于小型化、高集成度的电子设备。

8.QFN(无引脚封装)封装:QFN封装是一种无引脚的表面贴装封装,引脚位于封装的底部。

QFN封装具有体积小、引脚密度高、良好的散热性能等特点,适用于小型、高性能的电子产品。

9.LCC(陶瓷外壳)封装:LCC封装是一种使用陶瓷材料制成的封装形式,具有较高的耐高温性和良好的散热性能。

电子元器件封装图示大全可编辑全文

1.AGP封装AGP 封装形式脚位封装技术介绍。

2.AMR封装AMR 封装形式脚位封装技术介绍。

3.AX14封装AX14 封装形式脚位封装技术介绍。

4.AX078封装AX078 封装形式脚位封装技术介绍。

5.BGA封装BGA 封装形式脚位封装技术介绍。

6.C-BEND LEAD封装C-BEND LEAD 封装形式脚位封装技术介绍。

7.CERAMIC 封装CERAMIC 封装形式脚位封装技术介绍。

8.CERPACK封装CERPACK 封装形式脚位封装技术介绍。

9.CERQUAD封装CERQUAD 封装形式脚位封装技术介绍。

R封装CNR 封装形式脚位封装技术介绍。

11.DIP封装DIP 封装形式脚位封装技术介绍。

12.DO-4封装DO-4 封装形式脚位封装技术介绍。

13.DO-5封装DO-5 封装形式脚位封装技术介绍。

14.DO-8封装DO-8 封装形式脚位封装技术介绍。

15.DO-9封装DO-9 封装形式脚位封装技术介绍。

16.FBGA封装FBGA 封装形式脚位封装技术介绍。

17.FTO封装FTO 封装形式脚位封装技术介绍。

18.GULL WING LEADS封装GULL WING LEADS 封装形式脚位封装技术介绍。

19.ITO封装ITO 封装形式脚位封装技术介绍。

20.LCC 封装LCC 封装形式脚位封装技术介绍。

21.LCCC封装LCCC 封装形式脚位封装技术介绍。

22.LDCC封装LDCC 封装形式脚位封装技术介绍。

23.LGA封装LGA 封装形式脚位封装技术介绍。

24.LLP封装LLP 封装形式脚位封装技术介绍。

25.LQFP封装LQFP 封装形式脚位封装技术介绍。

26.MDIP封装MDIP 封装形式脚位封装技术介绍。

27.PGA封装PGA 封装形式脚位封装技术介绍。

28.PLCC封装PLCC 封装形式脚位封装技术介绍。

29.PSDIP封装PSDIP 封装形式脚位封装技术介绍。

30.PSOP封装PSOP 封装形式脚位封装技术介绍。

元器件封装大全:图解文字详述

元器件封装类型:A.Axial轴状的封装(电阻的封装)AGP (Accelerate raphical Port)加速图形接口AMR(Audio/MODEM Riser) 声音/调制解调器插卡BBGA(Ball Grid Array)球形触点阵列,表面贴装型封装之一。

在印刷基板的背面按阵列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点阵列载体(PAC)BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP封装之一,在封装本体的四个角设置突(缓冲垫)以防止在运送过程中引脚发生弯曲变形。

C 陶瓷片式载体封装C-(ceramic) 表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

Cerdip 用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

带有玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。

CERQUAD(Ceramic Quad Flat Pack)表面贴装型封装之一,即用下密封的陶瓷QFP,用于封装DSP 等的逻辑LSI 电路。

带有窗口的Cerquad 用于封装EPROM 电路。

散热性比塑料QFP 好,在自然空冷条件下可容许1.5~2W 的功率CGA(Column Grid Array) 圆柱栅格阵列,又称柱栅阵列封装CCGA(Ceramic Column Grid Array) 陶瓷圆柱栅格阵列CNR是继AMR之后作为INTEL的标准扩展接口CLCC 带引脚的陶瓷芯片载体,引脚从封装的四个侧面引出,呈丁字形。

带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。

此封装也称为QFJ、QFJ-G COB(chip on board) 板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子元件封装形式大全封装形式BGADIPHSOPMSOPPLCCQFNQFPQSOPS DIPSIPSODSOJSOPSotSSOPTO - DeviceTSSOPTQFPBGA(ballgridarray)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225.现在也有一些LSI厂家正在开发500引脚的BGA.BGA的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

序号封装编号封装说明实物图1 BGA封装内存2 CCGA3 CPGA CerAMIcPin Grid4 PBGA 1.5mmpitch5 SBGA ThermallyEnhanced6 WLP-CSP Chip Scale PackageDIP(du ALI n-line package)返回双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

引脚中心距2.54mm,引脚数从6到64.封装宽度通常为15.2mm.有的把宽度为7.52mm和10.16mm的封装分别称为skinnyDIP 和slimDIP(窄体型DIP)。

但多数情况下并不加区分,只简单地统称为DIP.另外,用低熔点玻璃密封的陶瓷DIP也称为cerdip。

序号封装编号封装说明实物图双列直插2 DIP16M3双列直插 3 DIP18M3双列直插 4 DIP20M3双列直插 5 DIP24M36 DIP24M6双列直插7 DIP28M38 DIP28M69 DIP2M 直插10 DIP32M6 双列直插11 DIP40M6双列直插12 DIP48M613 DIP8 双列直插HSOP 返回H-(withheatsink)表示带散热器的标记。

例如,HSOP表示带散热器的SOP。

序号封装编号封装说明实物图1 HSOP202 HSOP243 HSOP284 HSOP36MSOP (Miniature small outline package)返回MSOP是一种电子器件的封装模式,一般称作"小外形封装",就是两侧具有翼形或J形短引线的一种表面组装元器件的封装形式。

MSOP封装尺寸是3*3mm。

序号封装编号封装说明实物图1 MSOP102 MSOP8PLCC 返回PLCC为特殊引脚芯片封装,它是贴片封装的一种,这种封装的引脚在芯片底部向内弯曲,因此在芯片的俯视图中是看不见芯片引脚的。

这种芯片的焊接采用回流焊工艺,需要专用的焊接设备,在调试时要取下芯片也很麻烦,现在已经很少用了。

PLCC(Plastic Leaded Chip Carrier),带引线的塑料芯片载体。

表面贴装型封装之一,外形呈正方形,32脚封装,引脚从封装的四个侧面引出,呈丁字形,是塑料制品,外形尺寸比DIP封装小得多。

PLCC封装适合用SMT表面安装技术在PCB上安装布线,具有外形尺寸小、可靠性高的优点。

序号封装编号封装说明实物图1 PLCC202 PLCC283 PLCC324 PLCC445 PLCC84QFN 返回QFN(Quad Flat No-lead Package,方形扁平无引脚封装)是一种焊盘尺寸小、体积小、以塑料作为密封材料的新兴的表面贴装芯片封装技术。

由于底部中央大暴露的焊盘被焊接到PCB的散热焊盘上,使得QFN具有极佳的电和热性能。

序号封装编号封装说明实物图1 QFN162 QFN243 QFN324 QFN40QFP 返回这种技术的中文含义叫方型扁平式封装技术(PlaSTic Quad Flat Package),该技术实现的CPU芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。

该技术封装CPU时操作方便,可靠性高;而且其封装外形尺寸较小,寄生参数减小,适合高频应用;该技术主要适合用SMT表面安装技术在PCB上安装布线。

序号封装编号封装说明实物图1 LQFP1002 LQFP323 LQFP484 LQFP645 LQFP806 QFP1287 QFP448 QFP529 QFP64QSOP 返回序号封装编号封装说明实物图1 QSO162 QSO243 QSO204 QSO28SDIP 返回收缩型DIP.插装型封装之一,形状与DIP相同,但引脚中心距(1.778mm)小于DIP(2.54mm),因而得此称呼。

引脚数从14到90.也有称为SH-DIP的。

材料有陶瓷和塑料两种。

序号封装编号封装实物图说明1 SDIP24M32 SDIP28M33 SDIP30M34 SDIP42M35 SDIP52M36 SDIP56M37 SDIP64M3SIP 返回SIP(System In a Package系统级封装)是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。

与SOC(System ON a Chip系统级芯片)相对应。

不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而SOC则是高度集成的芯片产品。

序号封装编号封装说明实物图1 SIP82 SIP9SOD 返回序号封装编号封装说明实物图1 SOD1062 SOD1103 SOD1235 SOD276 SOD3237 SOD5238 SOD579 SOD6410 SOD72311 SOD923SOJ 返回序号封装编号封装说明实物图1 SOJL282 SOLJ183 SOLJ205 SOLJ266 SOLJ327 SOLJ328 SOLJ409 SOLJ44SOP 返回序号封装编号封装说明实物图1 SOP14 引脚间距1.272 SOP16 引脚间距1.273 SOP18 引脚间距1.274 SOP20 引脚间距1.275 SOP28 引脚间距1.276 SOP32 引脚间距1.27SOT 返回序号封装编号封装说明实物图1 D2PAK2 D2PAK53 D2PAK74 D3PAK5 DPAK6 SOT1437 SOT2238 SOT239 SOT2510 SOT2611 SOT34312 SOT52313 SOT53314 SOT89SSOP 返回SSOP(Shrink Small-Outline Package)窄间距小外型塑封。

序号封装编号封装说明实物图1 SSOP20 GullWingFine-Pitch2 SSOP243 SSOP344 SSOP365 SSOP446 SSOP487 SSOP568 SSOP-EIAJ-16L9 SSOP-EIAJ-20L10 SSOP-EIAJ-24L11 SSOP-EIAJ-28L12 SSOP-EIAJ-40LTO - Device 返回序号封装编号封装说实物图明1 D2PAK2 TO-1003 TO-1264 TO-1275 TO-186 TO-2027 TO-2148 TO-2159 TO-21810 TO-22011 TO-236AB12 TO-24314 TO-25315 TO-25716 TO-26117 TO-263-218 TO-263-319 TO-263-520 TO-263-721 TO-26422 TO-26823 TO-27624 TO-326 TO-527 TO-5228 TO-6629 TO-7230 TO-7531 TO-7832 TO-833 TO-834 TO-8435 TO-8736 TO-88TQFP 返回序号封装编号封装说明实物图1 TQFP-1002 TQFP-1283 TQFP-1444 TQFP-325 TQFP-446 TQFP-487 TQFP-648 TQFP-809 TQFP-EXP-PAD-100EXP-PAD-64TSSOP ,薄小外形封装返回序号封装编号封装说明实物图1 TSSOP14薄小外形封装2 TSSOP16薄小外形封装3 TSSOP20薄小外形封装4 TSSOP24薄小外形封装5 TSSOP24薄小外形封装6 TSSOP48薄小外形封装7 TSSOP56薄小外形封装8 TSSOP8薄小外形封装9 TSSOP-EXP-PAD-20L 薄小外形封装精品资料仅供学习与交流,如有侵权请联系网站删除 谢谢21 10 TSSOP-EXP-PAD-28L 薄小外形封装 11TSSOP-TSOP-II 薄小外形封装。