DSP中断系统及其应用

14-2812DSP-08中断系统

电气与信息工程学院

DSP技术及应用

281x中断系统

三级中断机制

2

电气与信息工程学院

DSP技术及应用

281x中断系统

三级中断机制

• 一当外设产生中断事件,对应外设的中断标志寄存器中相 应位置的中断标识 IF 位就置1,如果对应的中断使能位设 外设 为1,则外设中断请求信号INTx.y(x=1-12,y=1-8)可以送到P 级 IE控制器。如果外设的中断被禁止输入进来,则外设中断 标志保持为1,直到软件清0。 • 一旦 PIE 控制中来了中断请求,相应的PIE 中断标志位PI EIFRx.y 置1,如果PIEIERx.y也设为1,则PIEACKx 可以 决定CPU 是否可以响应该中断。如果PIEACKx 清0,则PI PIE级 2 E将中断请求INTx 送入CPU,如果PIEACKx=1,PIE 等 待它变0,从而可以将中断请求送入CPU。 • 一旦中断请求送入 CPU 后, CPU 级的中断标志寄存器中 的标志位就置1。如果此时CPU 中断使能寄存器IER 或仿 CPU 真中断使能寄存器DBGIER 中的相应位置1,且全局中断 屏蔽INTM 位(ST1 寄存器中的第0 位)为0,CPU 就进入中 级 断服务程序开始中断响应。 电气与信息工程学院

Default Vector Table Remapped when ENPIE = 1

Memory

0

PIE Vectors 256 W

0x00 0D00

BROM Vectors 64 W

0x3F FFC0 0x3F FFFF

PIE vector generated by config Tool

Used to initialize PIE vectors

dsp课程设计中中断的应用

dsp课程设计中中断的应用一、教学目标本课程的教学目标是使学生掌握数字信号处理器(DSP)中中断的应用原理和编程方法,培养学生解决实际工程问题的能力。

具体目标如下:1.知识目标:–掌握DSP中断的基本概念和分类。

–理解中断服务程序的编写和调试方法。

–熟悉中断优先级和中断嵌套的设置与处理。

–了解中断在不同应用场景下的应用实例。

2.技能目标:–能够运用中断机制优化DSP程序性能。

–具备编写和调试中断服务程序的能力。

–能够根据实际需求设计中断优先级和中断嵌套策略。

–能够分析并解决中断应用过程中的常见问题。

3.情感态度价值观目标:–培养学生对DSP技术的兴趣和好奇心,激发学生的创新意识。

–培养学生的团队合作精神和自主学习能力。

–使学生意识到中断技术在实际工程中的重要性,提高学生的工程实践能力。

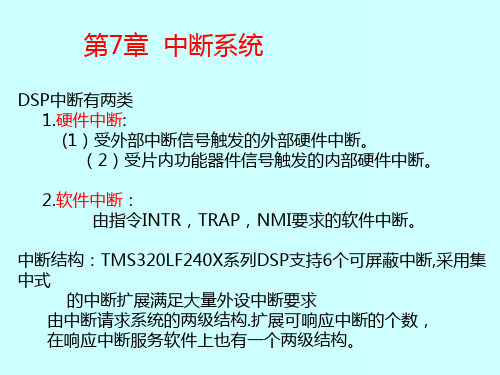

二、教学内容本课程的教学内容主要包括以下几个部分:1.DSP中断的基本概念和分类:讲解中断的定义、作用以及常见的中断类型,如硬件中断和软件中断等。

2.中断服务程序的编写和调试:介绍中断服务程序的编写方法,包括中断入口地址的设置、中断向量的配置等,并通过实例讲解中断服务程序的调试技巧。

3.中断优先级和中断嵌套:讲解中断优先级的设置方法,以及中断嵌套的概念和应用场景,并通过实例分析如何合理设置中断优先级和中断嵌套。

4.中断在不同应用场景下的应用实例:介绍中断在实时操作系统、通信系统、控制系统等领域的应用实例,使学生了解中断技术在实际工程中的重要性。

三、教学方法为了提高教学效果,本课程将采用以下教学方法:1.讲授法:教师讲解DSP中断的基本概念、原理和方法,引导学生掌握相关知识。

2.案例分析法:通过分析实际工程案例,使学生了解中断技术在实际应用中的重要作用。

3.实验法:安排实验室实践环节,让学生动手编写和调试中断服务程序,提高学生的实际操作能力。

4.讨论法:学生进行小组讨论,分享学习心得和经验,培养学生团队合作精神和沟通能力。

DSP实验十三 定时器中断及应用

实验十三 定时器中断及应用

一、实验目的

l、掌握在汇编条件下如何编写中断服务程序; 2、利用定时器中断,来实现一个 8 进制计数器。

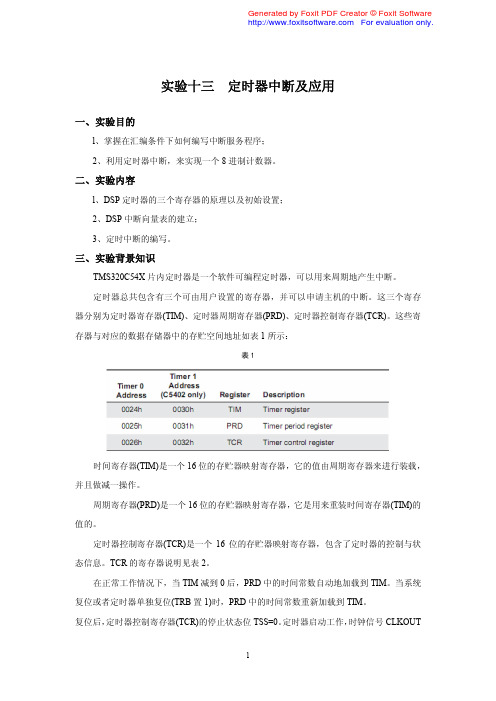

在正常工作情况下,当 TIM 减到 0 后,PRD 中的时间常数自动地加载到 TIM。当系统 复位或者定时器单独复位(TRB 置 1)时,PRD 中的时间常数重新加载到 TIM。 复位后,定时器控制寄存器(TCR)的停止状态位 TSS=0。定时器启动工作,时钟信号 CLKOUT

1

Generated by Foxit PDF Creator © Foxit Software For evaluation only. 加到预定标计算器 PSC。PSC 也是一个减 1 计数器,每当复位或其减到 0 后,自动地将定 时器分频系数 TDDR 加载到 PSC。 PSC 在 CLKOUT 作用下,作减 l 计数。当 PSC 减到 0,产生一个借位信号,令 TIM 作 减 l 计数。TIM 减到 0 后,产生定时中断信号 TINT,传送到 CPU 和定时器输出引脚 TOUT。 因此,定时中断的周期为: CLKOUT*(TDDR+1)*(PRD+1) 其中,CLKOUT 为时钟周期,TDDR 和 PRD 分别为定时器的分频系数和时间常数。 表2

B$

/*******************************************

* 时钟中断处理程序

*

*******************************************/

timerint:

CALL _ecounter

dsp原理与应用技术中的中断

DSP原理与应用技术中的中断什么是中断中断是指当处理器执行某个任务时,受到一个信号或事件的触发而暂停当前任务,跳转到指定的中断处理程序执行,处理完成后再返回原来的任务。

在DSP(数字信号处理)领域中,中断机制起着重要的作用。

中断可以分为硬件中断和软件中断两种。

硬件中断是由外部设备或芯片发出的中断信号触发,如计时器中断、外部设备输入中断等。

而软件中断是由程序的执行过程中的特殊指令或软件的调用而产生的中断。

DSP中的中断在DSP中,中断主要用于处理实时要求较高的应用,如音频处理、实时图像处理等。

中断的出现可以有效地降低系统的响应时间,提高系统的实时性。

DSP芯片通常提供多个中断向量,每个中断向量对应一个特定的中断源。

中断向量用来指示中断处理程序的入口地址,当中断发生时,处理器会根据中断向量跳转到相应的中断处理程序。

DSP中的中断优先级在DSP中,不同的中断有不同的优先级。

当多个中断同时发生时,处理器会根据中断优先级决定响应哪个中断。

中断优先级通常通过特定的寄存器配置。

处理器会根据中断触发的先后顺序以及中断优先级来决定响应的中断。

DSP中的中断处理过程中断处理过程通常包括以下几个步骤:1.中断触发:当中断源产生中断信号时,处理器会检测中断信号,并做出响应。

2.中断优先级判断:处理器会根据中断优先级判断是否响应当前中断请求。

3.中断向量跳转:如果中断请求被接受,处理器会根据中断向量找到相应的中断处理程序的入口地址,并跳转到该地址处执行中断处理程序。

4.中断处理程序:中断处理程序是中断的实际执行部分,它会处理中断所需的任务,如保存寄存器状态、处理中断源的数据等。

5.中断结束:当中断处理程序执行完成后,处理器会返回到原来的任务继续执行,完成中断的处理过程。

DSP中的中断应用技术中断在DSP应用中有广泛的应用,如音频处理、图像处理、通信等方面。

下面列举几个常见的DSP中的中断应用技术:1.实时音频处理:中断机制可以使得DSP实时响应音频输入信号,实现实时的音频处理,如音效处理、语音识别、语音合成等。

DSP(TMS320C6713)入门之旅三、中断的理解和使用

学习一个芯片的功能时,我的建议是先学会如何用C语言点亮一个LED灯,然后就是学习一下使用他的中断,因为在做芯片的时候,各个厂家有自己的一套自己的方法。

所以使用中断的就必须了解很多概念,比如如何打开中断,如何安装自己的中断子服务程序,等等!先介绍一下什么叫中断:你在下象棋,突然电话响了,你回屋接电话,然后回来继续下象棋,这个过程就叫做中断响应过程(中断过程)。

CPU执行正常任务———————下象棋保护现场———————————-你已经想好要―将军‖,先在脑海中记下来。

中断发生———————————-电话响-中断服务程序—————————-接电话恢复现场———————————-回来后恢复刚才想法中断返回———————————-你回来继续下象棋中断屏蔽———————————-Boss 正在训话,要求所有电话关机,你不能接电话了。

非屏蔽中断——————————-你内急,即使是Boss 在训话,你还是得到外面去嘘嘘。

可屏蔽中断——————————-你在―闭关修炼‖,可以不受外界干扰所以我们在使用中断之前先得告诉CPU,我们要使用那个中断,当中断发生的时候,你的执行程序的去向(也就是中断服务子程序),最后在返回我们被中断的函数。

这样就完成了我们的中断历程!看看6713执行中断的流程:一、使能了全局中断和子中断,那么CPU每执行一条指令之前就去查询一下有没有中断被置位,如果有产生的,那么CPU就要跳转!二、软件把CPU内部的寄存器A0~A15,B0~B15,等等这些寄存器的值推入堆栈保存,把当前PC寄存器的值放入IRP寄存器中以备中断返回能找到当前被打断的位置(保存现场,中断函数前面得加interrupt关键字)三、CPU的PC指针读出中断向量表的地址,也就是把(ISTP寄存器的值+子中断向量偏移量)装入PC寄存器,这样就执行跳转。

四、在中断向量表里一般有就用跳转指令,这样就可以跳转到我们用C语言编写的中断服务子程序中。

DSP第08章 中断系统及其应用+页码

be fetched from INTR1.1 to INTR12.1 locations if the respective interrupt flag is set.

All other TRAP, INTR, OR IFR,#16-bit operations fetch

the vector from the respective table location. You should avoid using such operations for INTR1 to INTR12.

The TRAP #0 operation returns a vector value of 0x000000

PIEIER&PIEIFR的数据结构

25

典型的PIEICPU响应流程图

一旦PIE控制器有中

断产生,相应的中 断标志位(PIEIFRx.y) 将被臵1。 若相应的PIE中断使 能位被臵1,PIE将 检查相应PIEACKx 确定CPU是否准备响 应该中断。 如果相应PIEACKx 被清零,PIE向CPU 申请中断。 如果PIEACKx被臵1 ,PIE将等待直到相 应的IEACKx被清零 才向CPU申请中断。

外部中断源

XINT1 XINT2

ቤተ መጻሕፍቲ ባይዱ

• • •

INT12 INT13 INT14

PDPINTx

RS XNMI_XINT13

F2812的中断类别

1. 硬件中断

所有外设中断(EV、ADC、SCI、SPI、ECAN等)和引 脚(XINT1、XINT2、XNMI_XINT13)引起的中断。

中断在TMS320C54x系列DSP中的应用(精)

中断在TMS320C54x系列DSP中的应用摘要:实现了一种全集成可变带宽中频宽带低通滤波器,讨论分析了跨导放大器-电容(OTA—C)连续时间型滤波器的结构、设计和具体实现,使用外部可编程电路对所设计滤波器带宽进行控制,并利用ADS软件进行电路设计和仿真验证。

仿真结果表明,该滤波器带宽的可调范围为1~26 MHz,阻带抑制率大于35 dB,带内波纹小于0.5 dB,采用1.8 V电源,TSMC 0.18μm CMOS工艺库仿真,功耗小于21 mW,频响曲线接近理想状态。

关键词:Butte摘要:详细分析了TMS320C54x系列DSP的中断机制,以及在扩展地址模式下中断控制所具有的一些特点,并给出了DSP/BIOS下中断的管理。

关键词:中断中断向量表 TMS320C54x DSP/BIOS DSP中断是嵌入式芯片的灵魂,这是因为多数嵌入式系统对实时性都有很高的要求,即对出现事件的响应要极为迅速。

中断与软件查询方式相比有着更高的执行效率。

在TI公司的TMS320C54x系列(以下简称C54x系列)DSP中,同样也提供了很好的中断机制。

1 C54x中的中断机制中断信号实质上是由硬件或者是软件驱动的信号,它能使DSP暂停正在执行的程序并进入中断服务程序(ISR)。

在最典型的DSP系统中,如果A/D转换器需要送数据到DSP中,或者D/A转换器需要从DSP中取走数据,都是通过硬件中断向DSP发出请求的。

C54x系列DSP支持软件中断和硬件中断。

软件中断是由指令(INTR、TRAP、RESET)触发的,硬件中断是由外围器件触发的。

硬件中断实际上又分为两类:一类是由DSP的片外外设(如A/D转换器)触发的,另外一类是由DSP的片内外设(如定时器中断)触发的。

硬件中断又有优先级的区分,这是为了处理同一时刻有多个硬件中断源触发中断的情况。

硬件中断的种类和优先级请参看具体使用的芯片资料。

如果按照可屏蔽情况分类,中断又可分为可屏蔽中断(C54x至多支持16个)和不可屏蔽中断。

DSP的中断学习

(2)、中断初始化 • 中断标志寄存器IFR中的定时中断位TINT=1,清除未 处理完的定时中断。 • 中断屏蔽寄存器IMR中的定时屏蔽位TINT=1,开放定 时中断。 • 状态控制寄存器ST1中的中断标志位INTM清0,开放 全部中断。 (3)、程序清单:

2、脉冲频率检测

其中,定时器控制寄存器TCR包括:预标定分频系 数TDDR,预标定计数器PSC、控制位TRB和TSS等及相 应的逻辑控制电路组成。

TCR中包含有定时器的控制位和状态位:

注1:

• 正常工作情况下,当TIM减到0后,PRD中的时间常 数自动地加载到TIM。当系统复位或定时器单独复位 时,PRD中的时间常数重新加载到TIM。 • 复位后,定时器控制积存器(TCR)的停止状态位 TSS=0,定时器启动工作,时钟信号CLKOUT加到预 定标计数器PSC。 • PSC也是一个减1计数器,每当复位或减到0后,自动 将定时器分频系数TDDR加载到PSC。 所以,定时中断的周期为: CLKOUT*(TDDR+1)*(PRD+1) • 若要关闭定时器,只要将TCR的TSS置1,就能切断时 钟输入,定时器停止工作。

二、时钟发生器

时钟发生器为C54X提供时钟信号。时钟发生器由 内部振荡器和锁相环(PLL)电路两部分组成。时钟发 生器要求有一个参考时钟输入,可以有两种方法提供:

C54X内部的PLL兼有频率放大和信 号提纯的功能。用高稳定的参考振荡器 锁定,可以提供高稳定的频率源。所以, C54X的外部频率源的频率可以比CPU的 机器周期CLKOUT的速率低,这样就能 降低因高速开关时钟所造成的高频噪声。

3、中断服务程序

CPU执行中断服务程序的步骤如下: • 保护现场,将PC值压入栈顶; • 载入中断矢量表,将中断矢量表地址送入PC; • 执行中断矢量表中指令,程序进入中断入口; • 执行中断服务程序,直至遇到返回指令; • 恢复现场,将栈顶值弹回PC; • 继续主程序。

第6章 DSP中断系统

• •

2.不可屏蔽中断(NMI) 不可屏蔽中断(NMI)为第二优先级的中断,通常用来向CPU发出类似突然掉电 之类的硬件问题告警。为了处理该中断,中断使能寄存器中的NMIE位必须置 1。如果NMIE位置1,阻止NMI处理的唯一条件是在分支跳转的延迟时间段内 发生不可屏蔽中断。

3.可屏蔽中断(INT4~INT15) 假设一个可屏蔽中断不在分支跳转的延迟阶段发生,则必须满足如下条件时可

屏蔽中断才能被处理:

控制状态寄存器(CSR)中的全局中断使能位(GIE)置1;

中断使能寄存器(IER)中的NMIE位置1;

IER中的相应中断使能位置1; 相应的中断发生,将中断标志寄存器(IFR)的相应为置1,且在IFR中设置更高

优先级的中断标志(IF)位。

4.中断应答(IACK和INUMX) IACK和INUMX信号通知TMS320C6000外部硬件,正在对发生的中断进行处理。 IACK信号指出CPU已经开始处理一个中断。INUMX信号(INUM3~INUM0)指出正在 处理的是哪个中断。 例如: INUM3 = 0 (MSB) INUM2 = 1 INUM1 = 1 INUM0 = 1 (LSB)

5~9

HPEINT

10~31

ISTB

【例6.1】 中断服务部的重定位。 (1)重定位IST到800h: 将地址为0h~200h的IST复制到地址800h~A00h之间。 写800h到ISTP寄存器: MVK 800h, A2 MVC A2, ISTP ISTP = 800h = 1000 0000 0000b (2)ISTP引导CPU到重定位的IST对应的ISFP: 假设:IFR = BBC0h = 1011 1011 1100 0000b IER = 1230h = 0001 0010 0011 0001b

DSPF28335---中断系统

DSPF28335---中断系统28335的中断系统中断概述通过硬件或软件驱动的信号,使CPU将当前的程序挂起,执行另一个称为中断服务子程序称为中断。

28335内部有16根中断线,其中有两个不可屏蔽中断(RESET、NMI)与16个可屏蔽中断(INT1-14、RTOSINT、DLOGINT),这里主要说明INT1-14。

在28335中,CPU定时器1、2一般预留给实时操作系统使用,中断线单独分配给INT13、INT14。

其余12个可屏蔽中断直接连接在外设中断扩展模块PIE上,供外部中断和处理器内部单元使用。

这就有一个问题,28335内部有很多个外设模块,这些外设都有自己的中断而且有很多个,那么剩余12个中断怎么够用。

为了解决这个问题所有引入PIE模块。

PIE通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8=96根线分别连接到外设,如AD、SPI、EXINT等等。

说明:PIE和CPU的中断标志寄存器由硬件来清零;但外部中断的标志位要通过软件来清零。

一.三级中断1.外设级中断如果有外设产生中断事件,则寄存器中相应的中断标志位被置一,如果相应的中断使能为(IE)被置位,那么外设就像PIE发出一个中断请求。

如果外设使能位没有被置位,那么中断标志(IF)位将保持为1直到软件清除。

2.PIE中断对于复用的中断源,PIE模块有相应的标志寄存器[PIEIFR(x,y) x=1-12,y=1-8]和中断使能寄存器PIEIER(x,y) ;对于每一个PIE中断组来说还有一个中断应答寄存器PIEACKx。

当有中断请求进入PIE模块的时候,如果相应的PIE中断标志位PIEIFR(x.y)和中断使能寄存器PIEIER(x,y)置1;这是PIE控制器就会检查PIEACKx标志位看CPU 是否已经准备好接收这个PIE中断组的中断。

说明:如果PIEACKZx被清零,PIE会把这个中断请求送到CPU 级的INTx。

DSP原理及应用技术第4.1-4.3节 系统控制与中断

4.1 系统时钟和PLL

PLL模块的三种配置模式如表4-1所述。

PLL模式 PLL关闭 PLL旁路 PLL使能

表4-1 PLL的3种配置模式

描述

PLLSTS[DI VSEL]

通过设置PLLSTS寄存器中PLLOFF可使PLL工作在

该模式且在该模式下PLL模块被禁止。该模式可 0,1

用于减少系统噪声和低功耗操作。在进入该模

➢ 片内外设所使用的低速外设时钟LSPCLK。这个时钟信号通过对CPU时钟SYSCLKOUT 分频得到。

4.1 系统时钟和PLL

4.1.2 晶体振荡器和PLL模块

F2833x系列DSP可以 通过外置振荡器或外部时 钟信号提供时钟,并通过 内部PLL锁相环电路倍频 后提供给系统。用户可以 根据实际运行频率计算所 需的倍频系数,并通过软 件设置PLL的倍频系数。 图4-1为片上外设时钟的 产生。

➢ OSCCLK通过锁相环(PLL)模块后或直接送至CPU,这个时钟信号为CPU时钟输入, 记为CLKIN。

➢ CLKIN输入CPU后,CPU将其输出,称为CPU时钟输出或系统输出时钟,记为 SYSCLKOUT。SYSCLKOUT与CLKIN频率相同。

➢ 片内外设所使用的高速外设时钟HSPCLK。这个时钟信号通过对CPU时钟SYSCLKOUT 分频得到。

2 OSSCLK×k/2

至PLL锁定住新的频率。

4.1 系统时钟和PLL

1. XCLKOUT信号的产生 XCLKOUT信号是直接由系统时钟SYSCLKOUT产生的,如图4-3所示。XCLKOUT频率

可以配置为SYSCLKOUT/1、SYSCLKOUT/2或SYSCLKOUT/4,默认状态下,XCLKOUT = SYSCLKOUT/4 或XCLKOUT = OSCCLK/16。

DSP技术及应用(08)

8.1 中断概述

2、中断分类

• 可屏蔽中断:可用软件加以屏蔽或使能。是由外设 产生的中断。 非屏蔽中断:这些中断不能够被屏蔽。所有软件触 发的中断都属于该类中断。

• CPU将立即响应该种中断并转入相应的子程序去执 行。

退出

退出

8.1 中断概述 4、中断的处理过程 3、中断向量及中断向量表

• • 中断向量:中断服务程序的入口地址 中断向量号:中断向量按一定顺序0、1、 2、… n,编排的序号称为中断向量号 • 中断向量表:按中断向量号的顺序把中断向量放在一块 连续的存储器空间,这块存储器空间称为中断向量表 • 中断向量地址:中断向量所存放的存储器单元的地址称 为中断向量地址 • •

XINT1 INT2 INT2.4=1 INT2.4=1 来自外设 或外部中断 XINT2

PIE级中断

外设级中断 使用PIE控制器的复用中断

退出

退出

第8章、第2页

2

2013/10/31

8.2 PIE中断扩展

8.2 PIE中断扩展

所有中断都是通过PIE中断扩展单元连接到各自相关 的中断线上。

PIE中断扩展原理 退出 退出

2013/10/31

8 中断系统及其应用Fra bibliotek中断系统及其应用

8.1 中断概述 8.2 PIE中断扩展

第8章:中断系统及其应用

8.3 中断向量 8.4 中断源 8.5 可屏蔽中断处理 8.6 定时器中断

退出

8.1 中断概述 基本概念 1、中断申请

• 中断请求信号是由软件或硬件驱动的信号,可暂停 目前执行的主程序,转而去执行一个中断服务子程 序。 • 通常中断请求由外设和硬件产生,以便CPU实现数据 的传送或接收。(ADC,DAC等设备)。 • 中断也可以作为特殊事件发生的标志信号。 •

第11章 中断系统-张蕾——DSP原理及应用课件PPT

可屏蔽中断和不可屏蔽中断

可屏蔽中断就是这些中断可以用软件加以屏蔽或 者解除屏蔽。X2812片内外设所产生的中断都是 可屏蔽中断,每一个中断都可以通过相应寄存器 的中断使能位来禁止或者使能该中断。

不可屏蔽中断就是这些中断是不可以被屏蔽的, 一旦中断申请信号发出,CPU必须无条件的立即 去响应该中断并执行相应的中断服务子程序。 X281X的不可屏蔽中断主要包括软件中断(INTR 指令和TRAP指令等)、硬件中断NMI、非法指令 陷阱以及硬件复位中断。

DSP原理及应用

第11章 X2812的中断系统 电信学院:张 蕾

11.1 什么是中断

在任何一款事件驱动型的CPU里面都应该会有 中断系统,因为中断就是为响应某种事件而存 在的。

中断的灵活应用不仅能够实现想要实现的功能, 而且合理的中断安排可以提高事件执行的效率, 因此中断在DSP应用中的地位是非常重要的。

00 0024h

3F FFE4h

00 0026h

3F FFE6h

优先级

1(最高) 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19(最低) 4 2 3

说明

复位中断 可屏蔽中断1 可屏蔽中断2 可屏蔽中断3 可屏蔽中断4 可屏蔽中断5 可屏蔽中断6 可屏蔽中断7 可屏蔽中断8 可屏蔽中断9 可屏蔽中断10 可屏蔽中断11 可屏蔽中断12 可屏蔽中断13 可屏蔽中断14 可屏蔽数据标志中断 可屏蔽实时操作系统中断 保留 不可屏蔽硬件中断 非法指令捕获

CPU中断的寄存器 IER寄存器

该CPU中断是否被使能?

1 打开 使能中断 0 关闭 禁止中断

DSP 第3讲 中断系统

§3.11 中断和中断向量表

中断号(K) 优先级 名 称 向量位置 功 能

16

17 18 19 20 21 22

3

4 5 6 7 8 9

INT0/SINT0

INT1/SINT1 IN12/SINT2 TINT0/SINT3 BRINT0/SINT4 BXINT0/SINT5 DMAC0/SINT6

§3.12 VC5402的中断向量表文件—续

RESET: ;复位中断,优先级最高 BD _c_int00 ;执行完该语句下面的一条语句后,跳转到_c_int00处 STM #128,SP ;设置堆栈大小为128个字 nmi:RETE ;nmi非屏蔽中断返回,下面依次为VC5402的各个中断, NOP ;每个只占4个字节 NOP NOP sint17 .space 4*16 ;VC5402的软中断 sint18 .space 4*16 ;.space表示开辟空间(单位:bit) sint19 .space 4*16 sint20 .space 4*16 sire21 .space 4*16 sint22 .space 4*16 sint23 .space 4*16 sint24 .space 4*16 sint25 .space 4*16 sint26 .space 4*16 sint27 .space 4*16 sint28 .space 4*16 sint29 .space 4*16 sint30 .space 4*16 ;这部分可以直接写为 .space 14*4*16

(3)IMR屏蔽位为1。(使能一个中断)

§3.6 执行中断服务程序(ISR)

当应答中断后,CPU会采取如下的操作:

DSP芯片的中断系统

TMS320C2000、TMS320C5000、TMS320C6000DSP的中断系统的比较以及TMS320C54x在中断编程中的注意事项姓名:刘帅民学号:201120195005 专业:通信与信息系统摘要:本文中主要针对TI公司生产的TMS320C2000系列、TMS320C5000系列和TMS320C6000系列DSP的中断系统进行简要概述,最后又简要叙述了编写TMS320C54x DSP芯片的中断程序应该注意的事项。

Abstract:The article focused on the briefly discusses of TI’s TMS320C2000 Series,TMS320C5000 Series and TMS320C6000 Series DSP’s interrupt system,finally a brief description should be payed attention to when write the interrupt program of the TMS320C54x DSP chip .一、中断的概述中断是指使CPU 暂停执行当前程序而转去执行中断子程序(ISR)的过程。

中断分为两类:(1)可屏蔽中断(可通过软件禁止);(2)不可屏蔽中断(不能被软件禁止)。

CPU一般通过以下四个步骤处理中断:(1)检测到中断请求信号;(2)允许中断:对于可屏蔽中断来说需要满足一定的条件,对于不可屏蔽中断则立即响应;(3)保护现场(自动将寄存器STO,T,AI ,AH,PI ,PH,ARO,AR1,DP,ST1,DBGSTAT,PC,IER压栈保存),读取中断向量并将它赋给程序指针PC。

(4)转入执行中断服务子程序(ISR)。

三大系列DSP芯片的结构不同,实现的功能也不同,所以,三者的中断系统也不同。

下面对三者的中断系统做一个简单的比较。

二、三大系列DSP芯片的中断系统比较1、TMS320C2000的中断系统C2000系列DSP中断可由硬件(中断引脚、外部设备、片内外设)或软件(INTR、IFR指令或TRAP指令)触发。

DSP系统配置和中断_图文(精)

第2章系统配置和中断介绍系统的配置寄存器和有关中断,并介绍用于增加中断请求容量的外设中断扩展(PIE寄存器。

2.1 系统配置概述系统配置和中断操作的内容包括:系统配置寄存器、中断优先级和中断向量表、外设中断扩展控制器(PIE、中断向量、中断响应的流程、中断响应的时间、CPU中断寄存器、外设中断寄存器、复位、无效地址检测、外部中断控制寄存器。

LF2407大部分的I/O口是多路复用的,复位时会被上拉为数字输入的模式。

2.2 系统配置寄存器对功能模块进行配置。

2.2.1 系统控制和状态寄存器(1)系统控制和状态寄存器-SCSR1,映射到数据存储器空间7018h 。

位15:保留位14:CLKSRC,CLKOUT引脚输出源选择0-CLKOUT引脚输出CPU时钟;1-CLKOUT引脚输出WDCLK时钟位13-12:LPM低功耗模式选择,指明在执行IDLE 指令后进入哪一种低功耗模式。

00-进入IDLE1(LPM0)模式;01-进入IDLE2(LPM1)模式;1x -进入HALT (LPM2)模式。

位11-9:PLL时钟预定标选择,对输入时钟选择倍频系数。

000-4;001-2;010-1.33;011-1;100-0.8;101-0.66;110-0.57;111-0.5位8:保留位7:ADC CLKEN,ADC模块时钟使能控制位位6:SCICLKEN, SCI模块时钟使能控制位位5:SPICLKEN, SPI模块时钟使能控制位位4:CANCLKEN, CAN模块时钟使能控制位位3:EVBCLKEN, EVB模块时钟使能控制位位2:EVACLKEN, EVA模块时钟使能控制位0:禁止模块时钟(节能);1:使能模块时钟,且运行位1:保留位0:ILLADR, 无效地址检测位当检测到一个无效地址时,该位被置1,该位需软件清除,写0即可。

初始化时该位写0。

注意:任何无效的地址会导致NMI事件发生。

(2)系统控制和状态寄存器2-SCSR2映射到数据存储器空间7019h 。

DSP-07章中断系统

XINT1优先级 1 XINT2优先级

RW-0

XINT1使能位 0 XINT2使能位

RW-0

R-0

RW-0

R:可读

W:可写

C:写1清0

-0:复位后为0

XINT引脚保持6个CLKOUT的低电平才能被识别

XINT标志 XINT极性 XINT优先级 XINT使能位

0:未检测到跳变 0:下降沿有效 0:高优先级 0:屏蔽中断

CPU

INT1 INT2 INT3

… …

INT6

中断回答

IACK

外设中断 扩展

优先级1

优先级2

优先级3

优先级6

中断向量寄存器 PIVR 中断应答寄存器 PIACKR (0.1.2) 中断请求寄存器 PIRQ(0、1、2)

PIE

中断请求寄存器0

中断请求寄存器2

PIRQR0

PIRQR1

中断向量寄存器 PIVR, 中断请求寄存器 PIRQR 中断应答寄存器 PIACK 是中断扩展模块用来向CPU产生INT1-INT6中断的CPU内部寄存器, 用于测试目的,用户不用,编程时可忽略(但可读)

INT6(000CH)

0004 AD6INT 0001 XINT1 0011 XINT2

非屏蔽中断 0000 000E 0010---0020 0022 0024 0026 0028----003F

INT4(0008H) 0033 0034 0035 0036 0037 0038 CAPINT :捕获中断 CAP2INT CAP3INT CAP4INT CAP5INT CAP6INT 软件中断向量

主程序:

.text _c_int0 : : 中断识别程序:

GISR2:保护现场 LDP #0E0H LACC PIVR,1 ADD #PVECTORS BACC

DSP5-F28335中断系统及定时器

外设(SPI,SCI,McBSP,CAN,I2C ) (ePWM,eCAP,eQEP,ADC)

WDINT LPMINT XINT1 ADC GPIOXINT1SEL(4:0)

MUX

看门狗 低功耗模式

MUX

外设级 各中断源使能 PIE级

支持96个,分12组 19优先级,组内有序

b、PIE中断应答寄存器(PIEACK)

D15 ~ D12 Reserved

R-0

D11 ~ D0 PIEACKx

RW1C-0

D11-D0,INT12至INT1应答位,CPU响应中断时自 动置1,需在ISR中写1淸0。

c、PIE中断标志(PIEIFRx)和使能寄存器(PIEIERx)

D15 ~ D8

外设级

组1

TINT0

PIEACK

PIEIFR1[INTx8:INTx1]

PIEIER1[INTx8:INTx1]

PIEACK[0]

PieCtrlRegs.PIEACK.all=0x0001

2、PIE中断向量表映射

a、定义函数型指针变量

在DSP2833x_PieVect.h文件中有定义: typedef interrupt void (*PINT)(void); PINT为指向interrupt型函数的指针

d、编写中断服务程序

interrupt void TINT0_ISR(void) // CPU-Timer 0 { // Insert ISR Code here // To receive more interrupts from this PIE group, // acknowledge this interrupt PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; // Next two lines for debug only to halt the // processor here // Remove after inserting ISR Code asm (" ESTOP0"); for(;;); }

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2).写在 DSP281x_DefaultIsr.c 中。

void main(void) {

InitSysCtrl();

//禁止和清除所有 CPU 中断 DINT; IER = 0x0000; IFR = 0x0000; InitPieCtrl(); IInitPieVectTable(); // InitPeripherals(); init_eva_timer1();

DINT;

//禁止和清除所有 CPU 中断

IER = 0x0000;

IFR = 0x0000;

InitPieCtrl(); InitPieVectTable();

//初始化 PIE 控制寄存器 //初始化 PIE 中断向量表

EALLOW; PieVectTable.T1PINT = &eva_timer1_isr; // 赋予地址,中断发生时,自动跳转 EDIS;

小结: 外设中断的屏蔽,需要将与该中断相关的外设寄存中的中断使能位置 0; 外设中断标志位的清除,需要将与该中断相关的外设寄存中的中断标志位 置 1;

(2)PIE 级 当外设产生中断事件,相关中断标志位置位,中断使能位使能之后,外设就会把中断请求提交给我们的 PIFra bibliotek 模块。PIE

模块将 96 个外设和外部引脚的中断进行了分组,分为 12 组,每组 8 个中断,分别是 PIE1-PIE12。每个组的中断被多路汇 集进入 1 个 CPU 中断,例如 PDPINDA,PDPINDB,XINT1,XINT2,ADCINT,TINT0,WAKEINT 这 7 个中断都在 PIE1 组内,这 些中断都汇集到 CPU 中断的 INT1。 和外设级类似的,PIE 控制器中的每个组都会有一个中断标志寄存器 PIEIFRx 和和中断 使能寄存器 PIEIERx,当然 x=1.....12。每个寄存器的低 8 位对应于 8 个外设中断,高 8 位保留。

EvaRegs.EVAIFRA.all = BIT7;

//BIT7---0x0080

PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;

}

/*****************************************************************************/

才能再来处理你们的请求。然后,CPU 会存储返回地址并自动保存相关的信息,例如将正在处理的数据放入堆栈等等,做好 这些准备工作之后,CPU 会从 PIE 块中取出对应的中断向量 ISR,从而转去执行中断子程序。

中断 CPU 级总结: CPU 级的操作都是自动的,不管是中断标志位(IFR),还是中断的使能位(IER)。

外设就会向 PIE 控制器发出一个中断请求。如果外设级中断没有被使能(相应的使能位为 0),那么外设就不会向 PIE 发出 中断请求,相应的中断标志位会一直保持置位状态,除非用软件清除。当然,在中断标志位保持在 1 的时候,一旦该中断被 使能了,那么外设立马会向 PIE 发出中断申请。 注:不管在什么情况下,外设寄存器中的中断标志位必须采用软件进行清除。

DSP 中断系统及其应用

TMS320F2812 学习笔记 中断系统及其应用

2812 的中断是 3 级中断机制,分别是外设级,PIE 级以及 CPU 级,对于某一个具体的外设中断请求,任意一级的不许 可,CPU 最终都不会执行该外设中断。

(1)外设级 外设产生中断时,该中断事件相关的中断标志位(IF)置 1。此时,如果该中断相应的中断使能寄存器(IE)也置为 1,

//中断屏蔽位 //清除中断标志位 //响应同组中断 //开全局中断

//初始化 PIE 控制寄存器 //初始化 PIE 中断向量表 //初始化所有外设

//使能 PIE 中断 INT2.4(T1PINT 中断)

PieCtrlRegs.PIEIER2.all = M_INT4;

IER |= M_INT2

//开 CPU 中断

EINT;

// Enable Global interrupt INTM

// InitPeripherals(); //初始化所有外设 init_eva_timer1();

//使能 PIE 中断 INT2.4(T1PINT 中断)

PieCtrlRegs.PIEIER2.all = M_INT4;

IER |= M_INT2

//开 CPU 中断

EINT;

// Enable Global interrupt INTM

2812 中断程序模板

1).先定义中断函数,再给相应的 PIE 中断赋地址。写在在 main.c 中

interrupt void eva_timer1_isr(void);

void main(void)

//主函数

//对中断函数 eva_timer1_isr 进行声明

{

InitSysCtrl(); //系统初始化

ERTM ; // Enable Global realtime interrupt DBGM

for(;;);

}

在 DSP281x_DefaultIsr.c 中

interrupt void T1PINT_ISR(void) {

........... EvaRegs.EVAIMRA.bit.T1PINT = 1; EvaRegs.EVAIFRA.bit.T1PINT=1; PieCtrlRegs.PIEACK.bit.ACK2=1; EINT; }

K 寄存器,同一时间只能放一个中断过去,只有等到这个中断被响应,给 PIEACK 置位,才能让同组的下一个中断过去,被 CPU 响应

(3)CPU 级 CPU 也有标志寄存器 IFR 和使能寄存器 IER。当某一个外设中断请求通过 PIE 发送到 CPU 时,CPU 级中与 INTx 相关

的中断标志位就会被置位。 例如,T1 的周期中断 T1PINT 的请求到达 CPU 这边时,与其相关的 INT2 的标志位就会被置位。这时候,该标志位就会

小结: PIE 中断的使能。就得将其相应组的使能寄存器 PIEIERx 的相应位进行置位; PIE 中断的屏蔽。这是和使能相反的操作; PIE 应答寄存器 PIEACK 相关位的清除,以使得 CPU 能够响应同组的其他中断。 PIE 级的中断和外设级的中断比较 外设中断的中断标志位是需要软件清除的,而 PIE 级的中断标志位都是自动置位或者清除的。但是 PIE 多了一个 PIEAC

被所存在 IFR 中,这时候,CPU 不会马上去执行相应的中断,而是等待 CPU 使能 IER 寄存器的相关位,并且对 CPU 寄存 器 ST1 中的全局中断屏蔽位做适当的使能。如果 IER 中的相关位被置位了,并且 INTM 的值为 0,则中断就会被 CPU 响应。 在 T1PINT 里,当 IER 的第 2 位即 INT2 被置位,INTM 为 0,则 CPU 就会响应定时器 T1 的周期中断。 CPU 接到了终端的 请求,就得暂停正在执行的程序,转而去响应中断程序,但是此时,它必须得做一些准备工作,以便于执行完中断程序之后 回过头来还能找到原来的地方和原来的状态。CPU 会将相应的 IER 和 IFR 位进行清除,EALLOW 也被清除,INTM 被置位, 就是不能响应其他中断了,CPU 向其他中断发出了通知,正在忙,没空来处理你们的请求了,得等到处理完手上的中断之后

ERTM ;

// Enable Global realtime interrupt DBGM

for(;;);

}

//EV-A 定时器 1 中断服务函数

interrupt void eva_timer1_isr(void)

{

.........

//中断内容

//清除定时器标志位

EvaRegs.EVAIMRA.bit.T1PINT = 1;