周立功新书解读:使用逻辑覆盖设计单元测试用例

学生成绩管理系统设计与实现毕业论文

学生成绩管理系统设计与实现毕业论文目录一、内容概述 (2)1.1 研究背景与意义 (3)1.2 国内外研究现状综述 (4)1.3 论文结构安排 (5)二、系统需求分析 (7)2.1 功能需求分析 (8)2.2 性能需求分析 (9)2.3 用户需求分析 (10)三、系统设计 (11)3.1 系统架构设计 (12)3.2 数据库设计 (15)3.3 模块设计 (16)四、系统实现 (18)4.1 前端页面实现 (20)4.2 后端逻辑实现 (21)4.3 数据库操作实现 (22)五、系统测试与评价 (24)5.1 系统测试计划 (25)5.2 测试用例设计 (26)5.3 测试结果分析 (27)5.4 系统评价 (28)六、总结与展望 (29)6.1 工作成果总结 (30)6.2 存在问题与改进措施 (31)6.3 后续研究方向展望 (33)一、内容概述本文旨在设计并实现一个高效的学生成绩管理系统,旨在解决学校对学生成绩管理的需求。

系统的主要目标是提供一个集中、有序、高效的平台,以便教师、学生和家长能够实时查看学生的成绩信息,同时能够进行成绩的录入、修改、查询和统计分析等操作。

系统需求分析:首先,通过深入调查和了解实际场景,详细分析系统的功能需求、性能需求、安全性需求等,明确系统的设计目标和方向。

系统设计:在需求分析的基础上,进行系统的总体设计,包括系统的架构设计、数据库设计、界面设计、算法设计等。

确定系统的技术路线和实现方式。

系统实现:根据系统设计,采用合适的技术和工具,实现系统的各项功能。

包括数据库的建立、界面的开发、算法的实现等。

系统测试与优化:对系统进行全面测试,包括功能测试、性能测试、安全性测试等。

根据测试结果,对系统进行优化,提高系统的稳定性和效率。

系统应用与效果评估:将系统应用于实际场景中,收集用户反馈,评估系统的应用效果和性能。

系统文档编写:整理系统的设计、实现、测试和应用过程,形成完整的毕业论文。

《高性能并行运行时系统:设计与实现》随笔

《高性能并行运行时系统:设计与实现》读书随笔目录一、内容综述 (2)1.1 背景与动机 (3)1.2 高性能并行运行时系统的意义 (3)二、并行运行时系统的基本概念 (4)2.1 并行计算与并行运行时系统 (6)2.2 并行运行时系统的组成部分 (7)三、高性能并行运行时系统的设计要素 (9)3.1 性能优化策略 (10)3.2 可扩展性与可维护性 (12)3.3 容错与稳定性 (13)四、典型高性能并行运行时系统分析 (15)4.1 MapReduce及其应用场景 (16)4.2 Spark的工作原理与应用 (17)4.3 分布式内存计算系统TBB (19)五、并行运行时系统的实现技术 (21)5.1 编程模型与语言支持 (22)5.2 数据存储与管理 (24)5.3 网络通信与通信协议 (25)六、高性能并行运行时系统的测试与调试 (27)6.1 测试方法与工具 (28)6.2 常见问题与解决方案 (30)七、总结与展望 (31)7.1 本书主要内容回顾 (32)7.2 对未来发展的展望 (34)一、内容综述《高性能并行运行时系统:设计与实现》是一本关于高性能并行计算的经典著作,作者是著名的计算机科学家和教授。

本书详细介绍了高性能并行运行时系统的设计与实现过程,旨在为读者提供一套完整的理论框架和技术方法,以便在实际项目中构建高效、可扩展的并行计算系统。

本书共分为五个部分,分别是:并行计算基础、并行编程模型、并行数据结构与算法、并行运行时系统设计及实例分析和总结。

在前三部分中,作者首先介绍了并行计算的基本概念、原理和技术,包括共享内存模型、消息传递接口(MPI)等;接着详细讲解了并行编程模型,如任务划分、同步与互斥、负载均衡等;作者还介绍了一些常用的并行数据结构与算法,如哈希表、B树、红黑树等。

在第四部分中,作者深入探讨了并行运行时系统的设计与实现,包括线程管理、进程管理、资源分配等方面。

通过一系列实例分析,作者展示了如何根据具体问题选择合适的并行计算模型和编程技术,以及如何在实际项目中实现高效的并行运行时系统。

InforSuite Flow 练习题一

InforSuite Flow 练习题一中创软件商用中间件股份有限公司2009年5月前言前言感谢您选用InforSuite Flow工作流产品。

本系列手册是针对使用InforSuite Flow工作流产品进行流程应用开发的技术人员编写的。

读者在使用该手册之前应具备一定JEE项目开发经验,并且已阅读《InforSuite Flow 白皮书》或对工作流的概念有一定了解。

本文档将通过一个案例来引导读者运用InforSuite Flow 进行实际的应用开发,使读者能够快速运用InforSuite Flow搭建自己的应用系统。

本文档中的案例都是经过认真设计的,并且全部在InforSuite Flow中调试通过。

本文档提供了完整的分析方案及实现方案,可帮助读者快速掌握InforSuite Flow的开发方法和技巧,了解标准任务表处理器使用方法。

如果您希望继续深入了解InforSuite Flow,请继续关注该系列文档及《InforSuite Flow 使用手册》。

目录前言 (I)目录 ............................................................................................................................................. I I 1场景描述 (4)1.1环境需求 (4)1.2场景需求 (4)2需求分析 (4)2.1引擎服务 (4)2.2流程开发 (5)2.2.1流程定义开发 (5)2.2.2应用开发 (5)2.3流程运行 (6)2.3.1流程定义实例化 (6)2.3.2流程实例生命周期 (6)2.4流程监控 (7)3场景实现 (8)3.1引擎服务 (8)3.1.1配置文件管理 (8)3.1.2服务部署 (9)3.1.3服务管理 (9)3.2流程开发 (10)3.2.1工作流项目创建 (10)3.2.2流程定义文件创建 (11)3.2.3流程设计 (11)3.3流程运行 (17)3.3.1标准任务表处理器部署 (17)3.3.2标准任务表处理器使用 (19)3.4流程监控 (21)4名词解释 (25)场景描述1场景描述1.1环境需求操作系统:Windows XP数据库:Derby数据库浏览器:IE6.0或IE7.01.2场景需求某公司是一家开发、销售模式运营的公司,在销售团队与开发团队之间经常有一些业务处理上的依赖关系,公司总经理为规范公司内部管理,提出一种业务需求:如图 1-1:图 1-1图1-1 中展示了这个流程的过程,销售人员在与客户进行沟通时,如果遇到技术方面的支持需求,可以向开发部门提出任务支持要求,技术部门相关人员接到要求之后可以帮助销售人员解决问题。

敏捷需求文档模板

敏捷需求文档模板篇一:敏捷开发总结Intro:简单的说,敏捷开发是一种以人为核心、迭代、循序渐进的开发方法。

在敏捷开发中,软件项目的构建被切分成多个子项目,各个子项目的成果都经过测试,具备集成和可运行的特征。

换言之,就是把一个大项目分为多个相互联系,但也可独立运行的小项目,并分别完成,在此过程中软件一直处于可使用状态。

敏捷开发是由一些业界专家针对一些企业现状提出了一些让软件开发团队具有快速工作、响应变化能力的价值观和原则,并于2001初成立了敏捷联盟。

他们正在通过亲身实践以及帮助他人实践,揭示更好的软件开发方法。

敏捷开发(agile development)概念从2004年初开始广为流行。

Bailar非常支持这一理论,他采取了"敏捷方式"组建团队:Capital One的"敏捷团队"包括3名业务人员、两名操作人员和5~7名IT人员,其中包括1个业务信息指导(实际上是业务部门和IT部门之间的"翻译者");另外,还有一个由项目经理和至少80名开发人员组成的团队。

这些开发人员都曾被Bailar送去参加过"敏捷开发"的培训,具备相关的技能。

每个团队都有自己的敏捷指导(Bailar聘用了20个敏捷指导),他的工作是关注流程并提供建议和支持。

最初提出的需求被归纳成一个目标、一堆记录详细需要的卡片及一些供参考的原型和模板。

在整个项目阶段,团队人员密切合作,开发有规律地停顿--在9周开发过程中停顿3~4次,以评估过程及决定需求变更是否必要。

在Capital One,大的IT项目会被拆分成多个子项目,安排给各"敏捷团队",这种方式在"敏捷开发"中叫"蜂巢式(swarming)",所有过程由一名项目经理控制。

为了检验这个系统的效果,Bailar将项目拆分,从旧的"瀑布式"开发转变为"并列式"开发,形成了"敏捷开发"所倡导的精干而灵活的开发团队,并将开发阶段分成30天一个周期,进行"冲刺"--每个冲刺始于一个启动会议,到下个冲刺前结束。

周立功单片机 Verilog 黄金参考指南说明书

Verilog®黄金参考指南V1.0 1996年8月©版权1996Doulos保留所有权力本刊物的任何部分在得到DOULOS的书面许可前都不能通过包括电子机械影印录像或其他任何形式或任何方式复制保存在搜索系统或发布在英国和北爱尔兰印刷Verilog-XL TM是商标Verilog®是Cadence Design System Inc的注册商标DOULOSChurch Hatch,22 Market Place,Ringwood.Hampshire.BH24 1AWEngland.Tel (+44) (0)1425 471223Fax (+44) (0)1425 471573Email**************.ukURL 序言 (4)指南的使用 (4)索引 (4)用于定义Verilog语法的记号说明 (4)Verilog的简单介绍 (5)背景 (5)语言 (5)编译 (6)模块结构 (6)语句 (7)按字母顺序参考的部分 (9)Always (9)Begin (10)Case (12)编码标准 (13)注释 (14)连续赋值 (15)Defparam (16)Delay (17)设计流程 (18)Disable (18)错误 (19)事件 (20)表达式 (21)For (22)Force (23)Forever (24)Fork (25)函数 (26)函数调用 (27)门 (27)IEEE1364 (30)If (31)Initial (32)实例化 (33)模块 (35)名字 (37)线网 (38)数字 (41)运算符 (43)参数 (44)PATHPULSE$ (46)端口 (47)过程赋值 (48)过程连续赋值 (50)编程语言接口 (51)寄存器 (51)Repeat (53)保留字 (53)Specify (54)Specparam (57)语句 (57)强度 (58)字符串 (60)任务 (61)任务使能 (64)定时控制 (65)用户定义的原语 (67)While (70)编译器伪指令 (71)编译器伪指令 (71)`define (72)`ifdef (74)`timescale (74)系统任务和函数 (76)系统任务和函数 (76)$display和$write (81)$fopen和$fclose (82)$monitor等 (83)$readmemb和$readmemh (84)$strobe (85)$timeformat (86)随机建模 (86)定时检查 (89)值改变转储 (91)命令行选项 (93)命令行选项 (93)序言Verilog黄金参考指南是Verilog硬件描述语言及其语法语义合并以及将它应用到硬件设计的一个简明的快速参考指南Verilog黄金参考指南并不是要代替IEEE的标准Verilog语言参考手册它不像IEEE的标准手册提供了Verilog完整正式的描述相反黄金参考指南以一种方便的参考格式解答了在Verilog的实践应用过程中经常遇到的问题Verilog黄金参考指南也不想成为介绍性的指南这里所提出的信息是一种扼要的参考格式而不是学习像Verilog这种复杂的主题所必要的渐进和共鸣方式但必须承认的是已经熟悉计算机语言的人希望将这个参考指南作为Verilog的课本因此在开始本指南就会对这个主题进行一个简单的非正式介绍Verilog黄金参考指南的主要特征是它包含了从许多Verilog项目中积聚起来的大量实践知识指南不仅提供方便的语法参考很多类似的书也有还对最常见的语言错误提出警告在代码不能编译的时候给出线索指出要看什么地方警告你注意合并问题并对改善你的编码形式提出建议Verilog黄金参考指南是为了给Doulos的系列Verilog训练课程增值也是HDL PaceMaker Doulos Verilog计算机基础训练包的补充指南的使用本指南的主体被分成3个主要部分每个部分都按字母顺序组织每一部分都以每页顶部的关键字词条作为索引通常你只要快速翻阅指南查找相应的关键字词条的就可以找到想要的信息如果找不到也可以用最后的完整索引查找本指南的很多信息都围绕Verilog的句法组织但也有另外一些有关编码标准设计流程错误保留字以及在正文按字母顺序参考部分后面的编译器伪指令系统任务和函数以及命令行选项等特殊的部分如果你是Verilog的新手请先阅读次页的Verilog简单介绍索引粗体的索引条目在指南的主体有对应的页剩下的索引条目按重要性的顺序在字符参考部分的页参考后面用于定义Verilog语法的记号说明在任何可能的时候语法定义要写得和例子相似但有需要引入一些额外的记号简单地来说方括号[ ]包含可选的项目三个点号…表示重复花括号{ }包含的是注释斜体表示语法该部分在别处定义记号的完整描述如下包含注释的花括号{ }所不是被定义的Verilog语法的一部分但它向你提供了有关语法定义的补充信息粗体的花括号{ }是Verilog句法的一部分连接运算符包含在方括号[ ]中的语法是可选的粗体的方括号是[ ]Verilog语法的一部分矢量范围位和部分选择存储器元素…表示前面的项目或行的重复0次或者多次或者表示一个列表例如Item…表示Item重复0次或多次,…表示在用逗号分隔的列表重复例如A,B,C列表中至少有一个项目列表的结尾没有,号小写的字是保留字是Verilog语言的组成部分例如module以大写字母开头的字不是斜体是Verilog的标识符即用户定义的名字它们都不是保留的标识符例如InstanceName斜体的字是句法范畴即在别处完整给出句法名字的定义句法范畴可以在相同的页里定义也可以在独立的页定义还可以在下面定义的其中一个特殊范畴中定义斜体=表示在同一页定义和使用的句法范畴特殊的语法范畴MinTypMaxExpression以Expression定义UnsignedNumber以Number定义SomethingExpression=Expression其中Something给出有关表达式的含意信息例如ConstantExpression ConstantMinTypMaxExpressionVerilog的简单介绍下面向不懂Verilog语言的读者在技术上简要介绍一下Verilog背景Verilog硬件描述语言HDL是描述电子电路行为和结构的一种语言是一种IEEE标准IEEEStd.1364-1995Verilog用于模拟从随机和纯行为到门级和开关级的抽象范围等层次的数字电子电路功能也用于从许多抽象寄存器传输级描述合并即自动产生门级描述Verilog一般用于支持高层次的设计或基于语言的设计其中电子设计在用自动合并工具进行详细设计前要通过高层次的完全抽象仿真来检验Verilog也广泛应用于IC的门级检验包括仿真故障仿真和定时检验Verilog最初是在1984年由Gateway Design Automation公司开发Verilog-XL仿真器的时候一起开发出来1989年Cadence Design Systems公司并购Gateway公司同时拥有对Verilog语言和Verilog-XL 仿真器的权力1990年Cadence将Verilog语言不是Verilog-XL放到公共领域为了使Verilog语言通过IEEE标准化过程一个非赢利性组织Open Verilog International OVI将它不断推进结果在1995年Verilog成为一个IEEE标准此后OVI仍继续不断维护和开发这种语言语言在本部分和指南剩下的部分以大写字母开头的斜体字都是技术术语都可以在本指南的主体中找到硬件设计的层次部分在Verilog中用模块Module描述模块定义了硬件单元的接口即输入和输出及其内部结构或行为大量的原语或者门Gates都内置在Verilog语言内它们表示基本的逻辑门例如and or另外还可以定义用户定义的原语User Defined Primitives UDPs电子电路的结构通过在高层模块内对模块和原语UDPs和门举实例Instances来描述而且实例之间通过线网Nets连接线网表示一个电气连接一条线路或总线端口Port连接列表用于将线网连接到模块的端口或者连接到原语的实例其中一个端口表示一个管脚寄存器Registers见下面也可以连接到实例的输入端口只能连接到输入端口线网和寄存器的值由逻辑值01X未知或未初始化的和Z高阻或悬空组成除了逻辑值外线网还有强度Strength值强度广泛地用于开关级模型以及解释网络有超过一个驱动器的情况电子电路的行为是用Initial和Aways结构以及连续赋值Continuous Assignments描述这些结构以及UDPs和门表示设计的层次树的叶子每个Initial Always连续赋值UDP和门实例相对于所有其他结构是同时执行的Initial或Always内的语句Statements在很多方面上都和软件编程语言的语句相似它们在用定时控制Timing Controls规定的时间例如延迟以及用仿真事件控制触发执行语句在Begin-End块顺序地执行在Fork-Join块并行地执行连续赋值语句修改线网的值Initial和Aways修改寄存器的值Initial或Always可以分解成有给定变量的指定的任务Tasks和函数FunctionsVerilog语言还有大量内置的系统任务System Tasks和函数Functions编程语言接口ProgrammingLanguage Interface PLI是Verilog语言的一个组成部分它提供了一种和调用系统任务和函数相同的方法调用以C写的函数编译Verilog源代码通常输入到计算机的一个或多个文本文件中然后这些文本文件被提交到Verilog编译器或解释器编译用于仿真或合并的数据文件有时候仿真在编译后立即进行不创建中间的数据文件模块结构module M (P1, P2, P3, P4);input P1, P2;output [7:0] P3;inout P4;reg [7:0] R1, M1[1:1024];wire W1, W2, W3, W4;parameter C1 = "This is a string";initialbegin : BlockName// 语句endalwaysbegin// 语句end// 连续赋值...assign W1 = Expression;wire (Strong1, Weak0) [3:0] #(2,3) W2 = Expression;// 模块实例...COMP U1 (W3, W4);COMP U2 (.P1(W3), .P2(W4));task T1;input A1;inout A2;output A3;begin// 语句endendtaskfunction [7:0] F1;input A1;begin// 语句F1 = Expression;endendfunctionendmodule语句#delaywait (Expression)@(A or B or C)@(posedge Clk)Reg = Expression;Reg <= Expression;VectorReg[Bit] = Expression; VectorReg[MSB:LSB] = Expression; Memory[Address] = Expression; assign Reg = Expression deassign Reg;TaskEnable(...);disable TaskOrBlock;-> EventName;if (Condition)...else if (Condition)...else...case (Selection)Choice1 :...Choice2, Choice3 :...default :...endcasefor (I=0; I<MAX; I=I+1)...repeat (8)...while (Condition)...forever...这个快速参考语法摘要不遵从本指南剩余部分所使用的符号惯例Verilog黄金参考指南按字母顺序参考的部分Always包含一条或多条语句过程赋值任务使能if case和循环语句这些语句在仿真运行中重复执行由定时控制管理语法alwaysStatement在何处使用module-<HERE>-endmodule规则• always只能赋值寄存器reg integer real time realtime类型• 启动仿真时所有always都开始执行而且在仿真过程中持续执行当到达always的最后一条语句时程序返回到always的第一条语句继续执行注意• 如果Always包含超过一条语句语句要包含在begin-end或fork-join块中• 没有定时控制的always将永远循环合并always是其中一条很有用的Verilog合并语句但always通常是不合并的为了使结果最好代码应受到下面其中一种模板的限制always @(Inputs) // 所有输入begin... // 组合逻辑endalways @(Inputs) // 所有输入if (Enable)begin... // 锁存器的动作endalways @(posedge Clock) // 只是时钟begin... // 同步的动作endalways @(posedge Clock or negedge Reset)// 只是时钟和复位beginif (!Reset) // 测试异步复位的有效激活电平... // 异步行动else... // 同步行动end // 给出触发器+逻辑举例下面的例子是一个寄存器传送级alwaysalways @(posedge Clock or negedge Reset)beginif (!Reset) // 异步复位Count <= 0;elseif (!Load) // 同步载入Count <= Data;elseCount <= Count + 1;end接下来的例子是描述组合逻辑的alwaysalways @(A or B or C or D)beginR = {A, B, C, D}F = 0;begin : Loopinteger I;for (I = 0; I < 4; I = I + 1)if (R[I])beginF = I;disable Loop;endend // 循环endBegin用于组合语句使它们按顺序执行Verilog的语法通常要求例如在always中只有一条语句如果需要超过一条语句语句就要被包含在一个begin-end块内语法begin [: Label[ Declarations...]]Statements...endDeclaration = {either} Register Parameter Event在何处使用见语句规则• begin-end块必须包含至少一条语句• Begin-end块内的语句按顺序执行定时控制与前一语句有关执行完begin-end块的最后一条语句后整个begin-end块的执行也完成• Begin-end和fork-join块可在自己内部或相互之间嵌套• 如果begin-end块要包含局部声明必须先命名这个begin-end块即必须有标记• 如果要禁能一个begin-end块必须先命名这个块注意仿真中Verilog LRM允许begin-end块被交叉执行这就是说即使begin-end块包含的两个相邻语句之间没有定时控制仿真器也可以选择执行另一个过程的部分例如另一个always的语句这就是Verilog语言有不确定性的原因提示• 在没有局部声明和块不会被禁能的情况下也可以给begin-end块加上标记增加其可读性• 不会在别处使用的寄存器可以用局部声明来声明这使声明更明确举例initialbegin : GenerateInputsinteger I;for (I = 0; I < 8; I = I + 1)#Period {A, B, C} = I;endinitialbeginLoad = 0; // 时刻0Enable = 0;Reset = 0;#10 Reset =1; // 时刻10#25 Enable =1; // 时刻35#100 Load = 1; // 时刻135endCase一个语句基于case表达式的值条件地执行最多一个分支语法CaseKeyword ( Expression)Expression,... : Statement {表达式可以是变量}Expression,... : Statement... {任意数量的情况}[default [:] Statement] {不一定在结尾}endcaseCaseKeyword = {either} case casex casez在何处使用见语句规则• casex语句的X和Z以及casez语句的Z表示无关• 最多可以有一条default语句当没有标记表达式符合case表达式时执行default语句标记是在冒号左面的一个表达式或是用逗号分隔的表达式列表也可以是保留字default default后面可以有或者没有冒号• 如果标记是用逗号分隔的两个或多个表达式列表只要case表达式符合其中一个标记表达式就认为标记就符合case表达式• 如果没有标记表达式符合case表达式而且没有default语句case语句不起作用注意• 如果特殊的标记要执行超过一条语句语句必须包含在begin-end或fork-join块内• 如果相应的标记是第一个符合case表达式的标记case只会执行这个分支Case的标记不需要互斥因此当相同的标记被错误地重复使用时Verilog编译器不会报告出错• Casex和casez语句的要用保留字endcase而不是endcasex或endcasez结束• Casex表达式中的X或Z或者casez表达式的Z符合所有case的标记这会使仿真结果混淆合并• case语句内的赋值一般合并到多路复用器如果case标记使用变量例如寄存器或线网那么可以合成优先权译码器• 无时钟的always中的不完全赋值即没有指定某些输入条件的输出被合并到透明锁存器有时钟always中的不完全赋值合并到循环寄存器提示• 仿真时通常用default作为最后一条case语句以捕捉非法的情况• casez通常比casex好因为在仿真中出现X会导致产生误导或混乱的结果• casex和casez标记的Z可用字符?代替这可以清楚地表示值无关而不是高阻举例case (Address)0 : A <= 1; // 选择一个单独的地址值1 : begin // 执行超过一条语句A <= 1;B <= 1;end2, 3, 4 : C <= 1; // 选出几个地址值default : // 其他剩余的地址$display("Illegal Address value %h in %m at %t",Address, $realtime);endcasecasex (Instruction)8'b000xxxxx : Valid <= 1;8'b1xxxxxxx : Neg <= 1;defaultbeginValid <= 0;Neg <= 0;endendcasecasez ({A, B, C, D, E[3:0]})8'b1 : Op <= 2'b00;8'b010 : Op <= 2'b01;8'b00100 : Op <= 2'b10;default : Op <= 2'bxx;endcase编码标准编码标准共有两类词汇编码标准负责控制文本格式命名惯例和注释这种标准增加程序的可读性并简化维护合并编码标准控制Verilog的结构样式避免普通的合并缺陷并在设计流程的早期发现合并错误下面列出的编码标准需要根据所选的工具和个人喜好修改词汇编码标准• 将每个Verilog源文件的内容限制到一个模块不从文件分割模块• 源文件的名字应与文件内容有关例如ModuleName.v• 每行只写一条声明或语句• 使用和例子一样的缩进• 用户定义的名字要注意大小写一致例如第一个字符是大写• 尽管局部名字例如循环变量可能很简洁但用户定义的名字应当是有意义并包含信息的• 写注释来解释不是复制Verilog代码其中注释接口特别重要例如模块参数端口任务和函数变量• 在任何可能的时候用参数或`定义宏避免在声明和语句中直接嵌入文本数字和字符串合并编码标准• 将设计分割成小的功能块并为每个块使用一个行为样式除了设计的主要部分外其他部分要避免门级描述• 有定义好的时钟策略而且在Verilog明确执行该策略例如单时钟多相时钟门时钟多时钟域确保Verilog的时钟和复位信号是清楚的即不从组合逻辑或无意识的门产生• 有定义好制造好的测试策略并适当地编码Verilog例如所有触发器可复位从外部管脚进行测试无功能冗余• 所有Verilog的always应遵守标准合并处理模板的其中一个见Always• 描述组合和锁存逻辑的always必须在always顶部的事件控制列表列出所有输入• 组合的always必须不能包含不完全赋值即所有输入值的组合必须赋值给所有输出• 描述组合和锁存逻辑的always必须不能包含反馈即always中被赋值为输出的寄存器不能作为always的输入• 带时钟的always在事件控制列表中只能有时钟和异步控制输入一般是复位或置位• 避免不必要的锁存器这些多余的锁存器是由于无时钟always的不完全赋值产生• 避免不必要的触发器当用非阻塞赋值在带时钟的always内给寄存器赋值或者当寄存器在连续重复的带时钟always之间和时钟周期之间保持值不变时触发器被合并• 所有内部状态寄存器必须可复位这样寄存器传输极和门级描述在检验的时候可以复位到相同的已知状态这不能应用到流水线寄存器或同步寄存器• 对于有不能到达的状态的有限状态机器和其他时序电路例如一个4位的十进制计数器有6个不可到达的状态如果硬件在这些状态下可以被控制那么所有2N个可能的状态的行为必须在Verilog中明确描述包括不能到达的状态的行为这就允许保留状态机器进行合并• 避免在赋值中使用延时除非要求在寄存器传输级解决0延时时钟的时滞问题• 不要使用integer或time类型的寄存器否则它们会分别合并到32位总线和64位总线• 请仔细检查使用动态索引的Verilog代码即用可变的索引或地址作为位选择或存储器元素循环语句或算术运算符因为这些代码要被合并成大量难以优化的门注释可以应当在Verilog源代码中包含说明性的注释语法{单行注释}//{多行注释}/* ... */在何处使用几乎可以在任何地方使用但不能分割运算符数字字符串名字和关键字规则• 单行注释用两个斜杠字符开始在行的末端结束• 多行注释用/*开始注释可能跨过多行直到*/处结束• 多行注释不能嵌套但多行注释中可以有单行注释它们没有特别的含意注意/* ... /* ... */ ... */注释在第一个*/处结束第二个*/将被忽略这个例子无疑会出现句法错误提示全部使用单行注释只在例如在开发和调试代码的过程中需要注释大段代码时使用多行注释举例// 这是一个注释/*共有三行的多行注释*/module ALU /* 8位ALU */ (A, B, Opcode, F);连续赋值当表达式中的线网或寄存器的值改变时连续赋值在一个或多个线网创建事件语法{either}{见线网}NetLValue = {either}NetNameNetName[ConstantExpression ]NetName[ConstantExpression: ConstantExpression ]{NetLValue,...}在何处使用module-<HERE>-endmodule规则两种形式的连续赋值效果相同Assign左边的线网必须在连续赋值语句的前面的源代码中明确声明注意尽管连续赋值和过程连续赋值很相似但它们是不一样的请确保将assign放在正确的地方连续赋值在initial或always外过程连续赋值在允许使用语句的地方都可以使用initial always任务函数等的内部合并• 合并工具忽略延时和强度使用指定定时限制的工具代替• 连续赋值作为组合逻辑合并提示• 用连续赋值描述组合逻辑可以容易地用一个简单表达式描述函数可以用于组成表达式always 一般能较好地描述许多复杂的组合逻辑而且其仿真速度比用大量独立的连续赋值语句快得多• 当Verilog要求使用线网时连续赋值对传输寄存器的值到线网非常有用例如将在initial中描述的测试激励应用到模块实例的输入输出口举例wire cout, cin;wire [31:0] sum, a, b;assign {cout, sum} = a + b + cin;wire enable;reg [7:0] data;wire [7:0] #(3,4) f = enable ? data : 8'bz;Defparam编译时覆盖参数值通过使用层次名字参数值可以在设计层次内部或外部的任何地方被覆盖语法defparam ParameterName =ConstantExpression,ParameterName = ConstantExpression,... ;在何处使用module-<HERE>-endmodule合并一般不合并提示不要使用defparam它提供了一种有用的方法逆向注释布局延时但现在通常通过使用特殊的程序块和编程语言接口实现对要覆盖的参数请在模块实例化时使用#语法举例`timescale 1ns / 1psmodule LayoutDelays;defparam Design.U1.T_f = 2.7;defparam Design.U2.T_f = 3.1;...endmodulemodule Design (...);...and_gate U1 (f, a, b);and_gate U2 (f, a, b);...endmodulemodule and_gate (f, a, b);output f;input a, b;parameter T_f = 2;and #(T_f) (f,a,b);endmoduleDelay延时可以在UDP和门的实例连续赋值和线网中使用这些延时能为线网元件和连接的传播延时建模语法{either}# DelayValue#( DelayValue[, DelayValue[, DelayValue]]) {上升下降关断}DelayValue = {either}UnsignedNumberParameterNameConstantMinTypMaxExpression在何处使用见连续赋值实例化线网规则• 如果只给出一个延时的值这个值既表示上升和下降传播延时即分别从0或1跳变又表示关断延时如果可用• 如果给出两个延时的值第一个值是上升延时第二个值是下降延时但tranif0tranif1rtranif0和rtranif1除外它们的第一个值表示开启延时第二个值是关断延时• 如果给出三个延时的值第三个延时是关断延时转换到Z但trireg线网除外它的第三个延时是电荷衰减时间• X的延时是最小的指定延时• 对于矢量来说从非0到0的转换被认为是下降转换到Z是关断所有其他转换都被认为是上升注意很多工具强调延时的MintypMax表达式必须包含在括号中例如#(1:2:3)是允许的但#1:2:3是不允许的合并合并工具忽略延时合并线网列表的延时受到合并工具命令例如设置最大的时钟周期约束提示指定的块延时路径延时通常是建模延时的一种很精确的方式而且它还提供了计算延时的机制以及逆向注释布局信息设计流程使用Verilog和合并设计ASIC或复杂FPGA的基本流程如下设计流程需要进行迭代但这里不作介对于每个块写寄存器传输级Verilog边界条件分析门计数和定时对于完整的芯片Verilog或装配接线柱布局仿真故障仿真和定时分析Disable使激活的任务或有名字的块在执行完所有语句前终止其执行语法disable BlockOrTaskName;在何处使用见语句规则• 禁能一个有名字的模块begin-end或fork-join或者一个任务就禁能从该模块或任务使能的所有任务而且向下禁能到使能的任务层次然后继续执行被禁能的任务后面使能的语句或有名字的块• 有名字的模块或任务可以在自己内部用disable语句自我禁能• 当任务被禁能时下面的事件不能确定任何输出或输入输出的值仍未生效的非阻塞赋值预定的事件assign和force语句• 函数不能被禁能注意任务自我禁能与任务返回不一样因为任务自我禁能的输出没有定义合并disable只在有名字的模块或任务自我禁能时合并提示用disable可以从任务早期退出退出循环或继续下一个迭代的循环举例begin : Breakforeverbegin : Continue...disable Continue; // 继续下一个迭代...disable Break; // 退出forever循环...end // 继续end // 终止错误下面列出的是最常见的Verilog错误前五位占了所有错误的50%前5位Verilog错误• 过程赋值的左边不声明为寄存器类型• 缺少begin-end语句或begin-end语句不匹配• 二进制数缺少基’b也就是说编译器将它们看作是十进制数• 在编译器伪指令中错误使用撇号应当是后撇号或重音符号`和数字基应当是一般的单引号或倒转的逗号’• 语句的结尾缺少分号其他常见错误• 尝试在任务或函数名字后面的方括号中定义任务和函数参数• 在测试程序中测试时忘了要将模块实例化• 用过程连续赋值代替连续赋值即assign在错误的地方使用• 尝试用保留字作为标识符例如xor• Always内没有定时控制导致无限循环• 在事件控制例如@(a or b)中用逻辑或运算符||代替保留字or• 用隐式线网连接矢量端口• 模块实例中端口连接的顺序错误• 嵌套的if-else语句中有包含错误begin-end的位置不正确• 等号的形式错误=用于赋值==用于比较数字值===用于匹配01X和Z的精确序列事件事件用于在行为模型中描述通讯和同步语法event Name ,...; {声明事件}-> EventName; {触发事件}在何处使用见->的语句在以下的地方允许有事件声明module-<HERE>-endmodulebegin : Label-<HERE>-endfork : Label-<HERE>-jointask-<HERE>-endtaskfunction-<HERE>-endfunction规则事件没有值或延时它们被事件触发语句触发在跳变沿敏感的定时控制中测试合并一般不合并提示有名字的事件通常用于在测试程序和系统级模型中与相同模块或不同模块使用层次名字的always 之间通讯举例event StartClock, StopClock;alwaysforkbegin : ClockGeneratorClock = 0;@StartClockforever#HalfPeriod Clock = !Clock;end@StopClock disable ClockGenerator;joininitialbegin : stimulus...-> StartClock;...-> StopClock;...-> StartClock;...-> StopClock;end表达式表达式从一组运算符名字文本值和子表达式计算值常数表达式是在编译时可以计算值的表达式标量表达式只计算1位的值延时可以用MinTypMax表达式表示语法Expression = {either}PrimaryOperator Primary{一元运算符}Expression Operator Expression{二元运算符}Expression ? Expression : ExpressionStringPrimary = {either}NumberName {参数线网或寄存器的名字}Name[ Expression]{位选择}Name[Expression: Expression]{部分选择}MemoryName[Expression]{Expression,...}{串联}{Expression{ Expression,...}}{复制}FunctionCall( MinTypMaxExpression){延时使用MinTypMax表达式}MinTypMaxExpression = {either}ExpressionExpression: Expression: Expression规则• 只有矢量的线网和reg以及integer和time允许位和部分选择• 部分选择必须在分号的左边寻址一个比分号右边更高的位最高位是线网或寄存器声明中左边的范围表达式的值• 有X或Z或超出范围的位和部分选择可能会也可能不会被捕捉为编译器错误它们给出的表达式结果是X• 存储器没有位或部分选择机制• 当表达式用整数常数作为操作数无基但带符号的整数例如-5的处理和有基且带符号的整数例如-‘d5不一样前者作为带符号数处理后者作为无符号数处理注意很多工具要求常数MinTypMax表达式的最小典型和最大延时值有序例如min<=typ<=max举例A + B!A(A && B) || CA[7:0]B[1]-4'd12/3 // 一个很大的正数"Hello" != "Goodbye" // 表达式为真1$realtobits(r); // 系统函数调用{A, B, C[1:6]} // 并置8位1:2:3 // MinTypMaxFor通用循环语句允许一条或多条语句重复执行语法for ( RegAssignment; {初始值}Expression; {循环条件}RegAssignment) {循环值}Statement。

周立功CANET-100_200硬件使用及帧格式

产品数据手册

Date:2006/08/18

4/32

Rev 1.01 ©2006 Zhiyuan Electronics CO., LTD.

广州致远电子有限公司 CANET-100/CANET-200

产品数据手册

Date:2006/08/18

2/32

Rev 1.01 ©2006 Zhiyuan Electronics CO., LTD.

广州致远电子有限公司 CANET-100/CANET-200

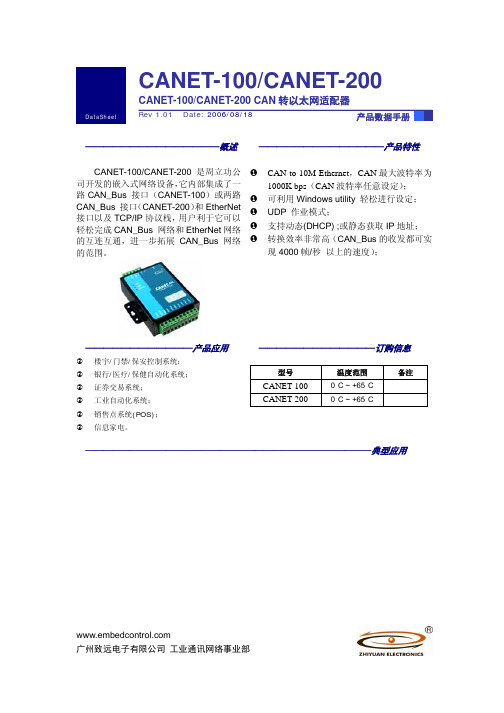

CANET-100/CANET-200 CAN 转以太网适配器

销售信息

如果需要购买本产品,请在办公时间(星期一至五上午 8:30~11:50;下午 1:30~5:30; 星期六上午 8:30~11:50)拨打电话咨询广州致远电子有限公司。

CAN to 10M Ethernet,CAN 最大波特率为 1000K bps(CAN 波特率任意设定); 可利用 Windows utility 轻松进行设定; UDP 作业模式; 支持动态(DHCP) ;或静态获取 IP 地址; 转换效率非常高(CAN_Bus 的收发都可实 现 4000 帧/秒 以上的速度);

DataSheet

CANET-100/CANET-200

CANET-100/CANET-200 CAN 转以太网适配器

Rev 1.01 Date: 2006/08/18

产品数据手册

———————————————概述 ——————————————产品特性

CANET-100/CANET-200 是周立功公 司开发的嵌入式网络设备,它内部集成了一 路 CAN_Bus 接口(CANET-100)或两路 CAN_Bus 接口(CANET-200)和 EtherNet 接口以及 TCP/IP 协议栈,用户利于它可以 轻松完成 CAN_Bus 网络和 EtherNet 网络 的互连互通,进一步拓展 CAN_Bus 网络 的范围。

《AI办公应用实战一本通:用AIGC工具成倍提升工作效率》笔记

《AI办公应用实战一本通:用AIGC工具成倍提升工作效率》读书笔记目录一、内容概述 (2)二、关于本书 (3)三、内容概览 (4)1. AI办公应用概述 (5)2. AIGC工具介绍与使用 (6)3. 实战案例分析 (7)4. 高效工作策略与技巧 (9)四、详细读书笔记 (10)1. AI办公应用的重要性及发展趋势 (12)2. AI办公应用的基础知识 (13)3. AIGC工具介绍 (15)3.1 工具A的功能与使用 (16)3.2 工具B的特点及优势 (17)3.3 工具C的实际应用与技巧 (18)4. 实战案例详解 (20)4.1 案例A的操作步骤与经验分享 (22)4.2 案例B的问题解决与经验总结 (23)4.3 案例C的创新应用与实践 (25)5. 高效工作策略与技巧探讨 (26)5.1 制定合理的工作计划 (27)5.2 有效的时间管理技巧 (28)5.3 优化工作流程和团队沟通方式 (30)5.4 利用AI工具提升工作效率的实用建议 (31)五、心得体会与总结 (32)1. 本书给我带来的启示和收获 (33)2. AI办公应用的实际运用与效果评估 (35)3. 对未来AI办公应用的展望与建议 (36)一、内容概述《AI办公应用实战一本通:用AIGC工具成倍提升工作效率》是一本关于人工智能在办公应用中的实际操作指南。

本书旨在帮助读者了解人工智能技术在办公场景中的应用,掌握如何利用AIGC工具提高工作效率,从而在职场中取得竞争优势。

人工智能基础概念:介绍人工智能的基本概念、发展历程和应用领域,帮助读者建立对人工智能的初步认识。

AIGC工具简介:详细介绍AIGC工具的功能、特点和使用方法,让读者对这些工具有一个全面的了解。

AI办公应用案例:通过实际案例分析,展示如何在办公场景中运用AIGC工具解决实际问题,提高工作效率。

个性化推荐系统:探讨如何利用AIGC工具构建个性化推荐系统,为用户提供更加精准的信息和服务。

ZIGBEE测试建议书

ZIGBEE测试建议书zigbee集中抄表系统(方案建议书) 华立仪表集团股份有限公司holley metering ltd.一. zigbee通信的简单介绍zigbee又叫紫蜂技术,是一个由可多到65000个无线数传模块组成的一个无线数传网络平台,十分类似现有的移动通信的cdma网或gsm网,每一个zigbee网络数传模块类似移动网络的一个基站,在整个网络范围内,它们之间可以进行相互通信;每个网络节点间的距离可以从标准的75米,到扩展后的几百米,甚至几公里。

zigbee技术自诞生以来,已经得到了长足的发展,应用领域主要包括集中抄表(amr)、工业控制、汽车自动化、家庭和楼宇自动化、医用设备控制等。

zigbee协议是开放的国际标准,因此任何国家、任何公司所提供的zigbee产品都必须符合这一标准,并且zigbee联盟提供了完善而严格的测试平台对这些产品进行测试。

这些措施保证了任何zigbee产品都可以实现互连和互操作。

这对于系统的安装、维护和扩展都带来了极大的方便。

二.zigbee技术的主要特点:面向无线传感和工业控制应用领域;采用国际ieee 802.15.4标准和国际zigbee联盟标准;全球通用的免费使用许可证频段ism(2.4ghz);支持双向通信(物理层通信速率250kbps,16通道/2.4ghz频点); ? 支持复杂拓扑结构(星型/树形/网状/混合网)和强大网络管理能力(网络自动建立、修补、优化路由),系统可扩展性和可伸缩性好;支持数据加密;支持超低功耗(电池供电);三.华立zigbee自动抄表系统的先进性与独特优势1. 华立自动抄表系统采用的是国际领先的zigbee无线抄表技术华立zigbee自动抄表技术是华立自己开发的有自己独立知识产权的产品。

其稳定性与成熟性已居世界前列。

华立是国内仪器仪表行业第一家zigbee国际会员(250多家成员公司,包括motorola,ember,ti-chipcon,philips、siemens,honeywell,samsung,等),采用国际ieee 802.15.4标准和国际zigbee联盟标准;2. 华立zigbee自动抄表系统频段免费,运营成本极低采用全球通用的免费使用许可证频段ism(2.4ghz),而且,支持超低功耗(电池供电),运营成本极低。

学习观察:通过价值流图创造价值、消除浪费_笔记

《学习观察:通过价值流图创造价值、消除浪费》读书记录目录一、内容综述 (2)1.1 书籍简介 (3)1.2 作者介绍 (3)二、价值流图的基础知识 (4)2.1 什么是价值流图 (5)2.2 为什么需要价值流图 (7)2.3 如何创建价值流图 (8)三、价值流图的绘制方法 (9)3.1 确定当前状态 (10)3.2 确定目标状态 (11)3.3 识别并绘制流程中的关键环节 (12)3.4 分析并确定瓶颈和浪费 (14)四、价值流图的应用 (15)4.1 如何利用价值流图改进业务流程 (16)4.2 如何利用价值流图提升产品质量 (17)4.3 如何利用价值流图降低成本 (18)五、价值流图的持续改进 (19)5.1 建立持续改进的文化 (20)5.2 如何定期进行价值流图的回顾和分析 (21)5.3 如何利用价值流图进行问题解决和决策支持 (22)六、案例分析 (23)6.1 案例一 (24)6.2 案例二 (25)七、总结与展望 (27)7.1 本书的主要观点总结 (27)7.2 对未来价值流图应用的展望 (28)一、内容综述《学习观察:通过价值流图创造价值、消除浪费》为我们揭示了精益生产的核心理念——通过精确的价值流图分析,发现并消除生产过程中的不增值环节,从而实现价值的最大化传递。

在阅读过程中,我深刻体会到了价值流图在提升生产效率、降低成本和提升产品质量方面的重要作用。

书中详细阐述了如何绘制价值流图,包括识别价值流、确定当前状态、设定目标状态以及制定实施计划等步骤。

通过绘制价值流图,我们可以清晰地看到生产过程中的各个环节,哪些是增值的,哪些是浪费的,从而有针对性地进行改进。

作者还强调了持续改进的重要性,价值流图不是一次性的活动,而是一个持续优化的过程。

只有不断地对价值流图进行分析和调整,才能确保生产过程的持续改进和价值的不断提升。

在阅读这本书的过程中,我深受启发和感动。

精益生产不仅仅是一种生产方式,更是一种思维方式。

首发:周立功教授《嵌入式软件工程方法与实践丛书》在北航正式出版开售

教学参考书,使学生在掌握 MCU 及各类外设使用方法的同时,还可以学习

到在嵌入式开发中使用 C 实现面向对象的编程思想。

<!--

一、《面向 AWorks 框架和接口的编程》(上) 1、内容介绍 代码的优劣不仅直接决定了软件的质量,还将直接影响软件成本。软件成 本是由开发成本和维护成本组成的,而维护成本却远高于开发成本,蛮力开 发的现象比比皆是,大量来之不易的资金被无声无息地吞没,造成社会资源 的严重浪费。为何不将复杂的技术高度抽象呢?如果实现了就能做到让专业 的人做专业的事,AWorks 就是在这样的背景下诞生的。由于其中融入了更 多的软件工程技术方法,因此就能做到将程序员彻底从非核心域中解脱出来, 专注于核心竞争力。 AWorks 制定了统一的接口规范,并对各种 MCU 内置的功能部件与外围 器件进行了高度的抽象,因此无论你选用的是 ARM 还是 DSP,只要以高度 复用的软件设计原则和只针对接口编程的思想为前提,应用软件就可实现“一 次编程、终生使用、跨平台”,AWorks 所带来的最大价值就是不需要重新发 明轮子。 2、适读人群

本书作为 AWorks 的基础教材,重点介绍 ZLG 在平台战略中所推出的 AWorks 开发平台,适合从事嵌入式软件开发、工业控制或工业通信的工程 技术人员使用,也可作为大学本科、高职高专电子信息、自动化、机电一体 化等专业的教学参考书。 二、《程序设计与数据结构》 1、内容介绍 本书是 C 程序设计的进阶书籍,在介绍 C 语言基础知识的同时,重点强 调了软件设计的思想:共性与可变性分析、面向对象的编程思想等,并提供 了详尽的范例程序。使读者体会到思想的重要性,面向对象编程并不局限于 特定语言,使用 C 语言同样可以进行面向对象的编程。 本书分为 4 章:

利用基本不等式求最值 2022-2023学年高一上学期数学人教A版(2019)必修第一册

a

0,

b

0

已知

,且 ab 1 ,

2020天津

1

已知 a , b R ,且 a 3b 6 0 ,则 2 b

8

a

,

且 BD 1,则 4a c 的最小值为___________.

某公司一年购买某种货物 600 吨,每次购买 x 吨,

1

×

5

+1

1

= 2+

+

×

+1

5

4

≥

5

+1

3

5

=

即 = , = 时等号成立.

当且仅当൝+1

2

2

+ =5

◈ 课堂探究◈

变式2 (3)已知a,b>0,

1 1

+ =1,

+ = +

求a+b的最小值.

1 1

+

=1+ + +1

≥2+2

∙ =4

乘1

整理通分

换1

1 1 + +

+ =

+

=1+ + +1≥2+2

∙ =4

◈ 课堂探究◈

变式2

1 4

(1)已知a,b>0,a+9b=7,求 + 的最小值.

考勤时间函数

考勤时间函数篇一:Excel技巧_快速统计公司员工考勤记录半米人才管理对于公司的人力资源或行政人员来说,员工的每月考勤统计一直是很头痛的一个问题。

从各类考勤机、网上考勤与移动考勤系统导出电子考勤数据并借助Excel进行处理是最基本的统计方法。

如果对Excel了解不够深入的话,也许十人以下规模的公司考勤还能靠眼睛人工应付,几百人的就变得不太现实。

本篇技巧就将向大家介绍如何借助Excel的自带高级功能快速统计考勤数据、减少人工工作量提高工作效率。

让我们先来看下借助Excel可以实现的考勤统计最终效果对比:初始考勤导出表:最终完成处理的考勤统计表:是否有考勤数据一目了然豁然的感觉?借助Excel达到最终统计效果仅仅只需要几个步骤几分钟而已!还等什么?赶快来看下面的教程一起学习吧!步骤1:导出原始考勤电子表格首先,我们通过考勤机所连接服务器将考勤数据导入到Excel中,通常我们都会导出以下几项考勤数据内容:员工工号,员工姓名,刷卡日期,刷卡时间。

有时每天每个员工的刷卡时间与次数都是不同的,但不用怕,这些不同的数据会在后续的处理中被过滤掉,不会为最终的统计造成影响。

半米人才管理步骤2:添加上下午标签现在我们需要为打卡时间设置上下午标签,以便为后续统计提供帮助。

在数据表格中插入“上下午”列,并撰写函数:iF(d2然后拖拽整列即可。

步骤3:考勤表格数据分类汇总接下来我们就要做最关的一步,对原始考勤数据表格进行分类汇总。

此时我们要用到的Excel功能就是“数据透视表”。

依次选择菜单:“插入”>“数据透视表”>“数据透视表”,在弹出的选择窗口中,点选“选择一个表或区域”选项,并如示例图中所示,拖拽选择以下数据列:“姓名”“刷卡日期”“刷卡时间”“上下午”。

半米人才管理点击“确定”按钮,在新工作数据表中,右边侧栏会出现“数据透视表字段列表”栏,根据示例中所示,将对应字段拖拽至对应区域内。

然后我们需要对“刷卡时间”数值进行设置,我们将“刷卡时间”设置为“最小值”。

统稿说明讲解

统稿说明:1)本大纲是在ISTQB的初级大纲的框架下,根据中国的实际情况作了适当的修改和调整,调整和修改的幅度符合ISTQB的规定要求。

2)本次的全面统稿是在各位专家修改意见的基础上进行的。

因为各位专家是分工、分章节对大纲进行修改的,故在很多方面没有考虑到大纲的整体连贯性和表达上的一致性,这次统稿从大纲的整体一致性、连贯性及表达方式等方面作了全面把握,修改的地方比较多,对部分不恰当的内容作了删除,也增加了一些内容。

3)由于各位专家在修改时对第五、第六、第七章的内容没作修改,因为这三个章节是根据中国的测试现状调整的部分,没有原稿基础。

在本次统稿过程中进行了全面充实。

4)由于时间紧,加之能力有限,统稿后的大纲中会有不足之处希望大家不吝赐教,我将根据大家的合理意见及时修改。

5)大纲在正式出版前还将进行版面、标点符号等方面的全面修改和完善,到时再通报大家。

CSTQB软件测试初级认证大纲2007 版ISTQB将本书授权给中国软件测试认证委员会(CSTQB)。

本大纲作者(当前的版权所有者,包括中国版修订者)和CSTQB一致同意下面的使用条款:1.本大纲的作者和CSTQB作为本大纲的原始发起者和版权拥有者,并具备在ISTQB认可的国家认证委员会(在中国为CSTQB)官方授权的前提下,个人或培训公司才可以基于本课程大纲开发并使用培训教程。

2.在大纲的作者和CSTQB作为本大纲的原始发起者和版权拥有者认可的前提下, 个人或个人团体可以使用本课程大纲作为文章、书籍或其它资料的参考文献或者主要理论依据。

3.任何ISTQB认可的国家认证委员会可以翻译本课程大纲,同时将本课程大纲(或翻译后的版本)授权给其它组织。

目录1. 软件测试基础(K2) 155分钟 (10)1.1 为什么需要测试 (K2) (10)1.2 什么是测试 (K2) (10)1.3 测试的基本原则 (K2) (10)1.4 基本的测试过程 (K1) (10)1.5 测试的心理学 (K2) (11)2. 软件生命周期中的测试(K2)135分钟 (24)2.1 软件开发模型 (K2) (24)2.2 测试级别(K2) (24)2.3 测试类型(K2) (24)2.4 维护测试 (K2) (25)3. 静态技术(K2) 60分钟 (36)3.1 评审和测试过程(K2) (36)3.2 评审过程(K2) (36)3.3 静态分析的工具支持(K2) (36)4. 测试设计技术(K3)255分钟 (44)4.1 识别测试环境和设计测试用例(K3) (44)4.2 测试设计技术的种类(K2) (44)4.3 基于规格说明的或黒盒测试技术(K3) (45)4.4 基于结构的或白盒测试技术(K3) (45)4.5 基于经验的技术(K2) (45)4.6 选择测试技术(K2) (46)5.传统的结构化软件测试(K3)180分钟 (57)5.1.结构化软件的单元测试(组件测试)(K3) (57)5.2.结构化软件的集成测试(K3) (57)5.3.结构化软件的系统测试(K3) (57)6. 面向对象的软件测试(K3) 150分钟 (61)6.1.面向对象的单元测试(K3) (61)6.2.面向对象的集成测试(K3) (61)6.3.面向对象的系统测试(K3) (61)7.基于GUI的软件测试(K2)120分钟 (65)7.1 GUI测试概述(K1) (65)7.2 GUI测试内容(K3) (65)7.3 GUI测试技术 (K2) (66)8. 测试管理(K3) 180分钟 (69)8.1 测试的组织结构(K2) (69)8.2 测计划划和估算(K2) (69)8.3 测试进度监测(K2) (69)8.4 配置管理(K2) (70)8.5 风险和测试(K2) (70)8.6 缺陷管理(K3) (70)9. 软件测试工具(K2) 80分钟 (84)9.1 测试工具的类型(K2) (84)9.2 高效率使用工具:潜在的利益和风险(K2) (84)9.3 组织中工具的引入(K1) (84)10.参考文献 (95)附录A――课程大纲背景 (97)附录B――学习目标和知识级别 (100)附录C――ISTQB初级课程大纲的规定 (102)附录D――培训机构注意事项 (104)致谢本大纲是在国际软件测试认证委员会初级课程大纲的框架下,按照规定的要求结合中国的实际情况编写。

软件工程实验三-概要设计

软件工程实验三-概要设计人事工资管理系统概要设计目录1.导言 (3)1.1目的 (3)2.系统分析 (4)3.界面设计 (5)图2-5人事管理0层编号1的数据流图 (9)图2-6 人事管理0层编号2的1层数据流图 (9)图2-7 工资管理0层数据流图 (9)4.体系结构 (10)4.1体系结构 (10)4.1.1STRUCT体系结构 (10)4.1.2系统体系结构 (12)4.2系统运行环境 (13)4.2.1 网络结构图............................. 错误!未定义书签。

4.2.2 硬件环境 (13)4.2.3软件环境 (14)5.数据模型 (15)5.1数据库的概念结构模型设计 (15)5.2数据库的逻辑结构模型设计 (15)5.3数据库管理物理结构模型设计 (15)6.模块设计 (16)6.1.1表示层设计 (16)6.1.2控制层 (16)6.1.3模型层 (16)6.2登录管理模块设计 (16)6.2.1表示层设计 (17)6.2.2控制层设计 (18)6.2.3模型层设计 (18)1.导言1.1目的该文档的目的是描述人事工资管理系统项目的概要设计,其主要内容包括:●系统功能简介●系统结构设计●系统接口设计●数据设计●模块设计●界面设计本文档的预期的读者是:●开发人员●项目管理人员●测试人员1.2范围该文档定义了系统的结构和单元接口,但未确定单元的实现方法,这部分内容将在详细设计/实现中确定。

1.3缩写说明UMLUnified Modeling Language(统一建模语言)的缩写,是一个标准的建模语言。

HRHuman resources management(人事工资管理管理)的缩写。

1.4引用标准[1] 《企业文档格式标准》北京长江软件有限公司[2] 《软件概要设计报告格式标准》北京长江软件有限公司软件工程过程化组织1.5参考资料[1] 《实战struct》〔美〕TedHusted机械工业出版社[2] 《软件重构》清华大学出版社2.系统分析本系统可以实现人事工资管理,人事管理者通过该系统进行人事工资管理。

微行为心理学_记录

《微行为心理学》读书随笔目录一、内容概要 (2)1.1 书籍简介 (2)1.2 研究背景与意义 (3)二、基本概念 (4)2.1 微行为的定义 (6)2.2 微行为的分类 (7)2.3 微行为与心理活动的关联 (8)三、微行为的观察与分析 (9)3.1 观察方法与技巧 (10)3.2 分析方法与工具 (12)3.3 微行为在日常生活中的应用 (13)四、微行为背后的心理动机 (14)4.1 驱动力的来源 (16)4.2 驱动力的表现形式 (17)4.3 驱动力对个体行为的影响 (18)五、微行为的心理学原理 (19)5.1 认知心理学视角 (21)5.2 社会心理学视角 (22)5.3 生理心理学视角 (23)六、微行为的实际应用 (24)6.1 在教育领域的应用 (26)6.2 在职场领域的应用 (27)6.3 在人际关系领域的应用 (28)七、结论 (30)7.1 研究成果总结 (31)7.2 对未来研究的展望 (32)一、内容概要《微行为心理学》一书深入浅出地剖析了人类日常行为的背后心理机制,通过观察和分析人们在日常生活中的微小动作、言语以及表情,揭示了隐藏在行为背后的真实想法和情感。

本书不仅拓宽了我们对自我认知的视野,还为我们提供了理解他人、建立和谐人际关系的宝贵工具。

书中内容丰富,涵盖了社交礼仪、职场沟通、恋爱情感等多个方面。

在社交礼仪方面,本书教会我们如何通过微小的肢体语言来展现自己的礼貌和尊重,从而在社交场合中赢得他人的好感和信任。

在职场沟通方面,本书则强调了语言在沟通中的重要性,通过解析人们在职场中常用的微行为,如眼神交流、面部表情等,帮助我们提升沟通技巧,更好地与他人协作。

而在恋爱情感方面,本书更是深入探讨了恋爱中的微妙心理变化,指导我们如何读懂对方的心思,运用心理策略来增强感情,最终收获美满的爱情。

1.1 书籍简介《微行为心理学》是一本深入剖析人类日常行为背后心理机制的书籍,它通过一系列生动的案例和富有洞察力的实验,揭示了人们在日常生活中的非言语交流、决策过程以及情感表达中所隐藏的心理秘密。

周立功的25年嵌入式生涯

周立功:我的25年嵌入式生涯(转)[此帖已被设为推荐]《程序员》杂志的编辑约我写一篇命题作文,想了几天都无从下手不知道写什么才好。

在这篇文章里,我不打算将创业的艰辛与喜悦重新回忆一遍,我确实不想去误导大家,因为我所处的年代是一个物质缺乏的年代,成功相对来说要容易得多。

每个人的成长经历都有其个性化的东西,每个人的成功创业经验虽然有一些可以遵循的普遍规律,但一般来说都很难复制,成功需要不断地创新。

对于今天很多的年轻人来说,一味注重技术至上的观念刻骨铭心,其实很多时候努力并非一定有回报。

事实上,有不少出类拔萃的人才往往做出来的产品就是卖不掉,因为设计者压根儿就不了解用户的需求和心理以及产品功能的恰当定义,而总想在同事及其老板面前卖弄自己的技术和产品功能。

其实有很多思维性的东西恰恰是很多人所忽视的,因为从一开始的出发点就错了,怎么可能取得辉煌的成绩呢?所以有时拥有卓越的技术并不一定代表人生的成功,很多企业就是死在一些自命不凡的“卓越人才”手中。

它山之石可以攻玉,减少“阶段0”的开发有所“创造”确实是人人期待的,令人瞩目的发明虽然激动人心却谈何容易,人们时常将盖茨没有任何爆炸性的发明作为茶余饭后的笑料,我们不妨从另外一个角度去探索微软的成功奥妙从而为我们所用。

确实不假,盖茨的DOS源代码是从帕特森手上“买”来的。

这些年来,我收集了世界各地中英文版有关微软的专著来比较研究,大家仅仅注意到盖茨为建立整个行业架构标准的远见,并叹服盖茨深得市场运作经验的精髓,我认为这些研究成果都是后来者研究微软成功经验,是“牵强附会”不可复制的理论总结。

当初微软公司还仅仅是一家很稚嫩的公司,可以说生存下去是盖茨作为老板唯一的使命。

事实上,正当盖茨决定动手来写IBM所要的OS时,原计划在一年左右完成,但IBM公司只给了他几个月的时间。

尽管帕特森的QDOS并不完善错误百出,但为了履行对IBM的承诺,盖茨购买了QDOS改贴标签后卖给了IBM公司。

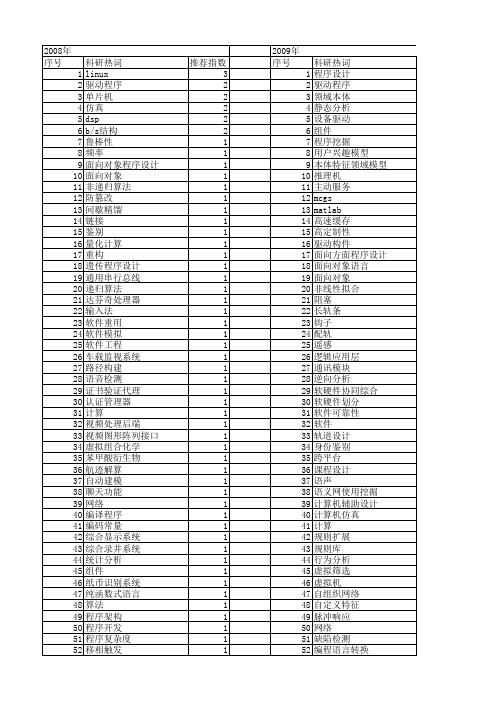

【计算机应用】_程序设计方法_期刊发文热词逐年推荐_20140724

嵌入式系统 嵌入式linux 嵌入式 小数运算 小幅面工程图 封闭 实验设计 实验管理 实时采集系统 实时数据传输 实体对象类 定制引擎 安装程序 学习规则 存储方案 字库 多组分 外推估计 复数取模 基因表达式程序设计 培训系统 域对象 城市通信网络 图像采集 图像处理 唤醒 叶簇替代物 可编程逻辑控制器 可执行连接文件格式 变压边力 取代基 反演 卷积码(cc) 卷积turbo码(ctc) 协同组织管理 协同 化简 励磁控制器 动态结构设计 动态图软件水印 分离集合 共享对象库设计模式 公式识别 公式编辑器 公式关系树 停滞速度 优先图 休眠 仿真平台 任务管理 代码覆1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106

107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160

推荐指数 3 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

软件需求工程09-5(1)

需求规格说明模板--附录

• 附录A: 词汇表 定义所有必要的术语,以便读者可以正确地解释软件需求 说明,包括词头和缩写。你可能希望为整个公司创建一张 跨越多项项目的词汇表,并且只包括特定于单一项目的软 件需求规格说明中的术语。 • 附录B:分析模型 这个可选部分包括或涉及到相关的分析模型的位置,例如 数据流程图、类图、状态转换图或实体-关系图。 • 附录C: 待确定问题的列表 编辑一张在软件需求规格说明中待确定问题的列表,其中 每一表项都是编上号的,以便于跟踪调查。

20121216F

需求规格说明模板--其它非功能需求

• e.4 软件质量标准属性 详尽陈述与客户或开发人员至关重要的其产品质 量特性。 • e.5 业务规则 列举出有关产品的所有操作规则,例如什么人在 特定环境下可以进行何种操作。 • e.6 用户文档 列举出将与软件一同发行的用户文档部分,例如, 用户手册、在线帮助和教程。明确所有已知的用 户文档的交付格式和标准。

20121216F

标识需求

• l)序列号 • 2)层次化编码 • 3)层次化文本标签

20121216F

处理不完整性

• 有时,你觉得缺少特定需求的某些信息。在解决 这个不确定性之前,可能必须与客户商议。检查 与另一个系统的接口或者定义另一个需求。使用 “待确定”(to be determined,TBD)符号作 为标准指示器来强调软件需求规格说明中这些需 求的缺陷(gap)。 • 通过这种方法,你可以在软件需求规格说明中查 找所要澄清需求的部分。记录谁将解决哪个问题、 怎样解决及什么时候解决。 • 把每个TBD编号并创建一个TBD列表,这有助于 方便地跟踪每个项目。

20121216F

需求规格说明模板--综合描述

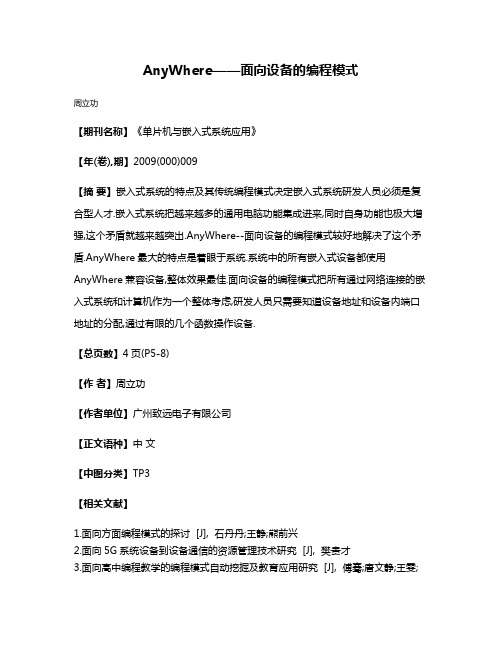

AnyWhere——面向设备的编程模式

AnyWhere——面向设备的编程模式

周立功

【期刊名称】《单片机与嵌入式系统应用》

【年(卷),期】2009(000)009

【摘要】嵌入式系统的特点及其传统编程模式决定嵌入式系统研发人员必须是复合型人才.嵌入式系统把越来越多的通用电脑功能集成进来,同时自身功能也极大增强,这个矛盾就越来越突出.AnyWhere--面向设备的编程模式较好地解决了这个矛盾.AnyWhere最大的特点是着眼于系统.系统中的所有嵌入式设备都使用AnyWhere兼容设备,整体效果最佳.面向设备的编程模式把所有通过网络连接的嵌入式系统和计算机作为一个整体考虑,研发人员只需要知道设备地址和设备内端口地址的分配,通过有限的几个函数操作设备.

【总页数】4页(P5-8)

【作者】周立功

【作者单位】广州致远电子有限公司

【正文语种】中文

【中图分类】TP3

【相关文献】

1.面向方面编程模式的探讨 [J], 石丹丹;王静;熊前兴

2.面向5G系统设备到设备通信的资源管理技术研究 [J], 樊贵才

3.面向高中编程教学的编程模式自动挖掘及教育应用研究 [J], 傅骞;唐文静;王雯;

郑娅峰

4.面向设备质量提升的电力设备缺陷大数据分析研究 [J], 王卫斌;陆嘉铭;周韡烨;屈志坚;姚嵘;瞿海妮

5.周德强副部长──网络维护要面向设备面向网络 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

使用逻辑覆盖设计单元测试用例

摘要:周立功教授新书发布系列连载篇:逻辑覆盖是单元测试中常用的测试用例设计方法,本文截取《软件单元测试入门与实践》中逻辑覆盖部分内容,帮助读者理解逻辑覆盖的用法。

本文摘自《软件单元测试入门与实践》第4章。

在单元测试开展过程中,首先需要设计测试用例。

逻辑覆盖是以程序内部的逻辑结构为基础的测试用例设计方法,其目的是为了尽可能的覆盖程序的语句以及不同的判定条件。

逻辑覆盖有语句覆盖(SC)、判定覆盖(DC)、条件覆盖(CC)、条件组合覆盖(MCC)、修正条件判定覆盖(MC/DC)几种方法。

为了便于理解各种方法的不同之处,本文将以闰年判断函数为例进行说明。

闰年判断函数代码如下:

bool IsLeapYear(int year)

{

bool flag = false;

if ((0 == year % 400) || (0 != year %100) && (0 == year % 4))

{

flag = true;

}

return flag;

}

假定该函数在书写过程中可能会出现以下几种错误:

1) “||”被误写为“&&”;

2) “&&”被误写为“||”;

3) “0 == year % 400”被误写为“0 != year % 400”;

4) “0 != year % 100”被误写为“0 == year % 100”;

5) “0 == year % 4”被误写为“0 != year % 4”;

6) 判断条件被误写为“if (0 == year % 4)”。

1. 语句覆盖

语句覆盖的含义是,选择足够多的测试数据,使得程序中的每条语句都至少被执行一次。

为了满足语句覆盖,只需要设计一个测试数据使得第4行的判定语句为真即可,那么使用2000作为输入数据即可满足要求。

使用该数据测试发现问题的情况表1。

表1 语句覆盖发现问题情况

由此可见,测试数据虽然满足了语句覆盖,但是也只能发现少量的问题。

在实际测试过程中,语句覆盖被认为是最弱的一种逻辑覆盖。

2. 判定覆盖

判定覆盖的含义为,选择足够多的测试数据,使得程序中的每个判断语句至少出现一次真值和一次假值。

为了满足判定覆盖,需要第4行的判定语句出现一次真值和一次假值。

当输入值为2000时,该语句的判定结果为真;当输入值为1999时,该语句的判定结果为假。

使用这两个数据进行测试发现问题的情况详见表2。

表2 判定覆盖发现问题情况

由此可见,判定语句虽然比语句覆盖能够发现更多的问题,但还是无法发现所有可能的问题。

3. 条件覆盖

条件覆盖的定义为,当一个判定语句由多个条件组合而成时,选择足够多的测试数据,使得每一判定语句中的每个逻辑条件的可能的值至少出现一次。

符合条件覆盖的测试数据详见下表。

表3 条件覆盖发现问题情况

现所有可能的问题。

4. 条件组合覆盖

条件组合覆盖的含义是,当一个判定语句由多个条件组合而成时,选择足够多的测试数据,使得各个条件的各种可能的组合都出现一次。

三个条件的各种组合情况详见下表。

表4 条件组合

情况如下。

表5 条件组合覆盖发现问题情况

盖方法。

条件组合覆盖的缺点是测试数据的数量会很多,在本例中由于三个条件有相互制约的关系,所以只有4个数据。

在实际情况下可能各个条件并没有相互制约的关系,那么用例数量就有8个了。

当条件数量增多时,测试数据的数量也是成指数增长的,会导致测试效率低下。

所以条件组合覆盖也不是最好的逻辑覆盖方法。

5. 修正条件判定覆盖

修正条件判定覆盖的含义是,画出程序的控制流,选择足够多的测试数据,使得程序控制流中的每一条路径都执行一次。

第一步,将代码中每一条语句都进行编号,如果一条判断语句中有多个条件,则每一个条件单独编号。

编号后的闰年判断函数如下。

bool IsLeapYear(int year)

{

bool flag = false; // 1

if ((0 == year % 400) || (0 != year %100) && (0 == year % 4)) // 2, 3, 4

{

flag = true; // 5 }

return flag; // 6 }

第二步,画出程序的控制流图。

图1 程序控制流图

第三步,找到所有的路径,并为每条路径选取测试数据。

表6 线性无关路径

在本例中,修正判定条件覆盖得到的用例和条件组合覆盖得到的用例是一致的,那是因为本例中各个条件之间的制约关系,实际测试过程中修正判定条件覆盖得到的用例会比条件组合覆盖得到的用例少。

由于修正判定条件覆盖方法中保证每条路径都执行了一次,所以是相对覆盖比较全面的方法。

通过前面的描述可知,逻辑覆盖能够有效的发现问题,然而逻辑覆盖自身的缺点也是显而易见的。

在使用逻辑覆盖设计测试用例时,对实现的依赖性太高,以至于开发者很难考虑到代码本身没有考虑到的地方。

所以在进行单元测试的过程中,除了使用逻辑覆盖之外,还需要使用数据覆盖。

两种方法同时使用,相互补充,才能最大限度的提高测试的覆盖率。

若读者想要了解更多测试用例设计的内容,可阅读《软件单元测试入门与实践》第4章。