AD8138单端转差分放大器模块

差分放大器AD813x常见问题解答

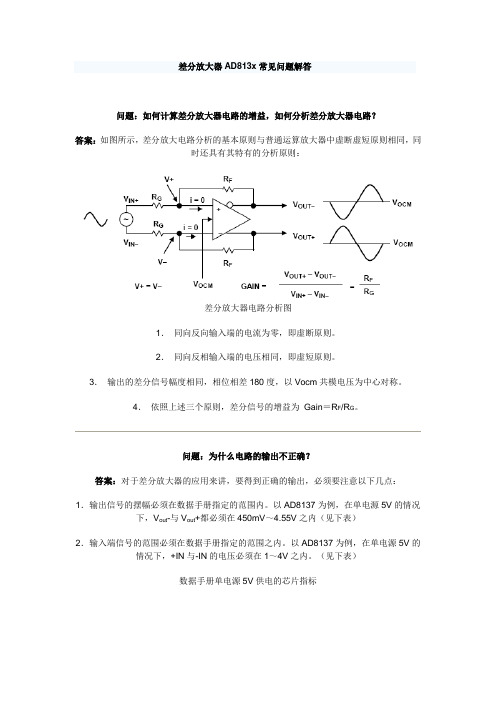

差分放大器AD813x常见问题解答问题:如何计算差分放大器电路的增益,如何分析差分放大器电路?答案:如图所示,差分放大电路分析的基本原则与普通运算放大器中虚断虚短原则相同,同时还具有其特有的分析原则:差分放大器电路分析图1.同向反向输入端的电流为零,即虚断原则。

2.同向反相输入端的电压相同,即虚短原则。

3.输出的差分信号幅度相同,相位相差180度,以Vocm共模电压为中心对称。

4.依照上述三个原则,差分信号的增益为Gain=R F/R G。

问题:为什么电路的输出不正确?答案:对于差分放大器的应用来讲,要得到正确的输出,必须要注意以下几点:1.输出信号的摆幅必须在数据手册指定的范围内。

以AD8137为例,在单电源5V的情况下,V out-与V out+都必须在450mV~4.55V之内(见下表)2.输入端信号的范围必须在数据手册指定的范围之内。

以AD8137为例,在单电源5V的情况下,+IN与-IN的电压必须在1~4V之内。

(见下表)数据手册单电源5V供电的芯片指标在你的电路中,一定要先进行分析计算,检查输出端电压和输入端共模信号的范围是否在数据手册指定范围之内(请注意电源电压的条件)。

对于单电源供电的情况,更容易出现问题。

下面我们以AD8137举例说明怎样判断电路是否能够正常工作?AD8137双电源供电放大电路如图,这是AD8137在+/-5V电源供电情况下的一个放大电路。

输入是一个8Vpp的信号。

按照虚短、虚断的原则,根据2.1的分析,差分信号增益是1,即,差分输出每一端的摆幅都是+/-2V,但相位相差180度。

由于Vocm加入了2.5V的共模电压,因此得到Voutp和Voutn的电压为2.5V+/-2.0 V和2.5V-/+2.0V,即0.5V~4.5V的范围内。

这个信号范围符合数据手册+/-5V电源供电情况下的指标(-4.55V~+4.55V)。

然后我们计算输入端的共模电压,按照虚短、虚断的原则,Vinn的电压是Voutp在两个1K ohm电阻上面的中点分压,即得到如图红色所示的共模电压为Vinn=1.25V+/-1.0V,即0.25V~2.25V,这也符合+/-5V供电下数据手册对输入共模电压的要求(-4V~+4V)。

利用低失真差分ADC驱动器AD8138和 5 mSpS、12位SAR型ADC AD7356实现单端转差分转换

利用低失真差分ADC驱动器AD8138和 5 mSpS、12位SAR型ADC AD7356实现单端转差分转换本电路可对5 MSPS、12位SAR型ADC AD7356的输入信号进行单端转差分转换。

该电路能够提供充足的建立时间和低阻抗,从而确保AD7356实现最高性能。

对AD7356进行差分驱动的理想方法是采用AD8138之类的差分放大器。

该器件可以用作单端转差分放大器或差分转差分放大器。

AD8138还能提供共模电平转换。

欲查看本电路笔记,请访问:/zh/CN-0041。

缓冲器增强时钟完整性,帮助高性能、高速ADC实现额定性能设计人员借助高性能、高速模数转换器(ADC),使系统具备高速度、高精度和高分辨率优势。

选择ADC的主要标准之一是信噪比(SNR)。

辅助设计要素会影响转换器的性能,其中一项重要考虑因素是时钟完整性。

ADC输入时钟的抖动会降低信噪比性能,因此让整个系统时钟树保持良好的低噪声、低抖动时钟信号,的确是个大难题。

解决方案ADI公司拥有种类丰富的时钟缓冲器,旨在帮助设计人员应对时钟完整性挑战。

将时钟缓冲器插在转换器与系统时钟树之间,LVPECL扇出缓冲器可轻松实现75 fs级的抖动性能,并且偏斜极低,约为9 ps。

这些缓冲器IC还能提供多达 12通道的低抖动时钟扇出,并且可以使受PCB上的长走线影响而变得平缓的时钟信号边沿陡峭起来。

用于数据转换器的理想时钟信号不仅应具有低相位噪声和低抖动特性,而且要有非常陡峭的上升沿和下降沿。

如果只有一两个转换器需要非常陡峭的边沿,将时钟缓冲器ADCLK905、ADCLK907、 ADCLK914 和ADCLK925 紧挨着转换器,便可提供极快的边沿,且对时钟信号噪声的影响极小。

除了提供陡峭的边沿外,ADCLK914等器件还能提供高差分电压摆幅,可起到限制ADC耦合噪声的作用。

ADI公司可提供从1路输出到12路输出、采用不同逻辑系列的各种低抖动时钟缓冲器产品,以满足高性能、高速ADC 的时钟要求。

常用单端到差分转换电路

常⽤单端到差分转换电路1、可采⽤AD8138来实现单端到差分的转换电路采⽤的是AD公司的AD8138,该放⼤器具有较宽的模拟带宽(320MHz,⼀3dB,增益1),⽽且可以实现将单端输⼊变成差分输出的功能。

此项功能在现代⾼速模数变换电路中⾮常有⽤,因为⼏乎所有的⾼速A/D芯⽚都要求模拟信号为差分输⼊,虽然部分芯⽚的⼿册中提到对于单端输⼊信号也可使⽤,但这样⼀来会使A/D转换结果的⼆次谐波增⼤,降低信噪⽐(SNR)。

AD8138很好的解决了这个问题,⽤户可以很容易的将单端信号转换成差分输出⽽不必使⽤变压器,并且它的输⼊阻抗⾼达6MQ,可以直接与输⼊信号相连⽽省略隔离放⼤器,⼤⼤精简了电路结构。

相对于运算放⼤器,AD8138在差分信号处理⽅⾯取得了重⼤进步。

AD8138可以⽤作单端⾄差分放⼤器或差分⾄差分放⼤器。

它像运算放⼤器⼀样易于使⽤,并且⼤⼤简化了差分信号放⼤与驱动。

该器件采⽤ADI公司的专有XFCB双极性⼯艺制造,-3 dB带宽为320 MHz,提供差分信号,谐波失真在现有差分放⼤器中最低。

AD8138具有独特的内部反馈特性,可以提供输出增益和相位匹配平衡,从⽽抑制偶数阶谐波。

其典型应⽤电路接法如下图所⽰:2、采⽤AD8042实现⼀⽚AD8042(内部为两个运放)即可实现单端到差分电路的转换,其参数详见datasheet,具体接法见下图:⾼速 DAC,⽐如模拟器件(Analog Devices)公司的 AD9776/78/79 TxDAC 系列,能提供差分输出,但对于低端交流电应⽤或⾼精度电平设置应⽤,配备差分转换电路的单端电流输出 DAC 提供了⼀种新颖的⽅法来⽣成差分波形控制功能。

图 1 中的基本电路组合了电流输出 DAC(即 IC1,如 8 位AD5424 DAC)和⼀个单端⾄差分运算放⼤级IC2、IC3A、IC3B——来产⽣要求的输出。

对于双电源应⽤,可选择 DAC 的单极⼯作模式来达到 DAC 的最优性能。

基于FPGA的数字脉冲压缩系统实现

基于FPGA的数字脉冲压缩系统实现庞龙;陈禾【摘要】针对采用线性调频信号的宽带雷达系统,完成单通道高速数据采集和数字脉冲压缩系统的工程实现.系统使用ADS5500完成14位、60 MSPS的数据采集,使用FPGA实现1024点的数字脉冲压缩.脉冲压缩模块采用快速傅里叶变换IP核进行设计,可以在脉冲压缩的不同阶段对其进行复用,分别完成FFT和IFFT运算,从而使硬件规模大大减少.系统采用块浮点数据格式以提高动态范围,同时减小截断(或舍入)误差对输出信噪比的影响.【期刊名称】《现代电子技术》【年(卷),期】2010(033)014【总页数】4页(P190-192,195)【关键词】数字脉冲压缩;快速傅里叶变换;块浮点;知识产权核;现场可编程门阵列【作者】庞龙;陈禾【作者单位】北京理工大学,信息与电子学院,雷达技术研究所,北京,100081;北京理工大学,信息与电子学院,雷达技术研究所,北京,100081【正文语种】中文【中图分类】TN911;TP2740 引言脉冲压缩体制在现代雷达中被广泛采用,通过发射宽脉冲来提高发射的平均功率,保证足够的作用距离;接收时则采用相应的脉冲压缩算法获得脉宽较窄的脉冲,以提高距离分辨力,从而能够很好地解决作用距离和距离分辨力之间的矛盾问题[1-3]。

线性调频(LFM)信号通过在宽脉冲内附加载波线性调制以扩展信号带宽,从而获得较大的压缩比。

所需匹配滤波器对回波信号的多普勒频移不敏感,因此LMF信号在目前许多雷达系统中仍在广泛使用[4-5]。

本文基于快速傅里叶IP核可复用和重配置的特点,实现一种频域的FPGA数字脉压处理器,能够完成正交输入的可变点LFM信号脉冲压缩,具有设计灵活,调试方便,可扩展性强的特点。

1 系统功能硬件实现方法该系统为某宽带雷达系统的数据采集和数字脉冲压缩部分。

系统要求在1个脉冲重复周期(PRT)内完成距离通道的数据采集及1 024点的数字脉冲压缩,并在当前PRT将脉压结果传送至DSP,其硬件结构如图1所示。

AD8138ARZ-RL资料

Low DistortionDifferential ADC DriverAD8138 Rev. Fnformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.FEATURESEasy to use, single-ended-to-differential conversion Adjustable output common-mode voltage Externally adjustable gainLow harmonic distortion−94 dBc SFDR @ 5 MHz−85 dBc SFDR @ 20 MHz−3 dB bandwidth of 320 MHz, G = +1Fast settling to 0.01% of 16 nsSlew rate 1150 V/μsFast overdrive recovery of 4 nsLow input voltage noise of 5 nV/√Hz1 mV typical offset voltageWide supply range +3 V to ±5 VLow power 90 mW on 5 V0.1 dB gain flatness to 40 MHzAvailable in 8-Lead SOIC and MSOP packagesAPPLICATIONSADC driversSingle-ended-to-differential convertersIF and baseband gain blocksDifferential buffersLine driversPIN CONFIGURATION–INV OCMV++OUT+INNCV––OUTNC=NO CONNECT173-1Figure 1.TYPICAL APPLICATION CIRCUITDIGITALOUTPUTSV173-2Figure 2.GENERAL DESCRIPTIONThe AD8138 is a major advancement over op amps for differential signal processing. The AD8138 can be used as a single-ended-to-differential amplifier or as a differential-to-differential amplifier. The AD8138 is as easy to use as an op amp and greatly simplifies differential signal amplification and driving. Manufactured on ADI’s proprietary XFCB bipolar process, the AD8138 has a −3 dB bandwidth of 320 MHz and delivers a differential signal with the lowest harmonic distortion available in a differential amplifier. The AD8138 has a unique internal feedback feature that provides balanced output gain and phase matching, suppressing even order harmonics. The internal feed-back circuit also minimizes any gain error that would be associated with the mismatches in the external gain setting resistors.The AD8138’s differential output helps balance the input to differential ADCs, maximizing the performance of the ADC. The AD8138 eliminates the need for a transformer with high performance ADCs, preserving the low frequency and dc infor-mation. The common-mode level of the differential output is adjustable by a voltage on the V OCM pin, easily level-shifting the input signals for driving single-supply ADCs. Fast overload recovery preserves sampling accuracy.The AD8138 distortion performance makes it an ideal ADC driver for communication systems, with distortion performance good enough to drive state-of-the-art 10-bit to 16-bit converters at high frequencies. The AD8138’s high bandwidth and IP3 also make it appropriate for use as a gain block in IF and baseband signal chains. The AD8138 offset and dynamic performance makes it well suited for a wide variety of signal processing and data acquisition applications.The AD8138 is available in both SOIC and MSOP packages for operation over −40°C to +85°C temperatures.AD8138Rev. F | Page 2 of 24TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 Pin Configuration.............................................................................1 Typical Application Circuit.............................................................1 General Description.........................................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 ±D IN to ±OUT Specifications......................................................3 V OCM to ±OUT Specifications.....................................................4 ±D IN to ±OUT Specifications......................................................5 V OCM to ±OUT Specifications.....................................................6 Absolute Maximum Ratings............................................................7 Thermal Resistance......................................................................7 ESD Caution..................................................................................7 Pin Configuration and Function Descriptions.............................8 Typical Performance Characteristics.............................................9 Test Circuits.....................................................................................15 Operational Description................................................................16 Definition of Terms....................................................................16 Theory of Operation......................................................................17 Analyzing an Application Circuit............................................17 Setting the Closed-Loop Gain..................................................17 Estimating the Output Noise Voltage......................................17 The Impact of Mismatches in the Feedback Networks.........18 Calculating an Application Circuit’s Input Impedance.........18 Input Common-Mode Voltage Range in Single-SupplyApplications................................................................................18 Setting the Output Common-Mode Voltage..........................18 Driving a Capacitive Load.........................................................18 Layout, Grounding, and Bypassing..............................................19 Balanced Transformer Driver.......................................................20 High Performance ADC Driving.................................................21 3 V Operation.................................................................................22 Outline Dimensions.......................................................................23 Ordering Guide.. (23)REVISION HISTORY1/06—Rev. E to Rev. FChanges to Features..........................................................................1 Added Thermal Resistance Section and Maximum PowerDissipation Section...........................................................................7 Changes to Balanced Transformer Driver Section.....................20 Changes to Ordering Guide. (23)3/03—Rev. D to Rev. EChanges to Specifications................................................................2 Changes to Ordering Guide............................................................4 Changes to TPC 16...........................................................................6 Changes to Table I............................................................................9 Added New Paragraph after Table I.............................................10 Updated Outline Dimensions.......................................................14 7/02—Rev. C to Rev. DAddition of TPC 35 and TPC 36.....................................................8 6/01—Rev. B to Rev. CEdits to Specifications ......................................................................2 Edits to Ordering Guide...................................................................4 12/00—Rev. A to Rev. B 9/99—Rev. 0 to Rev. A 3/99—Rev. 0: Initial VersionAD8138Rev. F | Page 3 of 24SPECIFICATIONS±D IN to ±OUT SPECIFICATIONSAt 25°C, V S = ±5 V , V OCM = 0, G = +1, R L, dm = 500 Ω, unless otherwise noted. Refer to Figure 39 for test setup and label descriptions. All specifications refer to single-ended input and differential outputs, unless otherwise noted. Table 1.Parameter Conditions Min Typ Max Unit DYNAMIC PERFORMANCE −3 dB Small Signal Bandwidth V OUT = 0.5 V p-p, C F = 0 pF 290 320 MHz V OUT = 0.5 V p-p, C F = 1 pF 225 MHz Bandwidth for 0.1 dB Flatness V OUT = 0.5 V p-p, C F = 0 pF 30 MHzLarge Signal Bandwidth V OUT = 2 V p-p, C F = 0 pF 265 MHz Slew Rate V OUT = 2 V p-p, C F = 0 pF 1150 V/μs Settling Time 0.01%, V OUT = 2 V p-p, C F = 1 pF 16 ns Overdrive Recovery Time V IN = 5 V to 0 V step, G = +2 4 ns NOISE/HARMONIC PERFORMANCE 1 Second Harmonic V OUT = 2 V p-p, 5 MHz, R L, dm = 800 Ω −94 dBc V OUT = 2 V p-p, 20 MHz, R L, dm = 800 Ω −87 dBc V OUT = 2 V p-p, 70 MHz, R L, dm = 800 Ω −62 dBc Third Harmonic V OUT = 2 V p-p, 5 MHz, R L, dm = 800 Ω −114 dBc V OUT = 2 V p-p, 20 MHz, R L, dm = 800 Ω −85 dBc V OUT = 2 V p-p, 70 MHz, R L, dm = 800 Ω −57 dBc IMD 20 M Hz −77 dBc IP3 20 M H z 37 dBm Voltage Noise (RTI) f = 100 kHz to 40 MHz 5 nV/√Hz Input Current Noise f = 100 kHz to 40 MHz 2 pA/√Hz INPUT CHARACTERISTICS Offset Voltage V OS, dm = V OUT, dm /2; V DIN+ = V DIN− = V OCM = 0 V −2.5 ±1 +2.5 mV T MIN to T MAX variation ±4 μV/°C Input Bias Current 3.5 7 μA T MIN to T MAX variation −0.01 μA/°C Input Resistance Differential 6 MΩ Common mode 3 MΩ Input Capacitance 1 pF Input Common-Mode Voltage −4.7 to +3.4 V CMRR ∆V OUT, dm /∆V IN, cm ; ∆V IN, cm = ±1 V −77 −70 dB OUTPUT CHARACTERISTICS Output Voltage Swing Maximum ∆V OUT ; single-ended output 7.75 V p-p Output Current 95 mA Output Balance Error ∆V OUT, cm /∆V OUT, dm ; ∆V OUT, dm = 1 V −66 dB1Harmonic distortion performance is equal or slightly worse with higher values of R L, dm . See Figure 17 and Figure 18 for more information.AD8138Rev. F | Page 4 of 24V OCM to ±OUT SPECIFICATIONSAt 25°C, V S = ±5 V , V OCM = 0, G = +1, R L, dm = 500 Ω, unless otherwise noted. Refer to Figure 39 for test setup and label descriptions. All specifications refer to single-ended input and differential outputs, unless otherwise noted. Table 2.Parameter Conditions Min Typ Max UnitDYNAMIC PERFORMANCE −3 dB Bandwidth 250 MHz Slew Rate 330 V/μs INPUT VOLTAGE NOISE (RTI) f = 0.1 MHz to 100 MHz 17 nV/√Hz DC PERFORMANCE Input Voltage Range ±3.8 V Input Resistance 200 kΩ Input Offset Voltage V OS, cm = V OUT, cm ; V DIN+ = V DIN– = V OCM = 0 V –3.5 ±1 +3.5 mV Input Bias Current 0.5 μA V OCM CMRR ∆V OUT, dm /∆V OCM ; ∆V OCM = ±1 V −75 dB Gain ∆V OUT, cm /∆V OCM ; ∆V OCM = ±1 V 0.9955 1 1.0045 V/VPOWER SUPPLY Operating Range ±1.4 ±5.5 V Quiescent Current 18 20 23 mA T MIN to T MAX variation 40 μA/°C Power Supply Rejection Ratio ∆V OUT, dm /∆V S ; ∆V S = ±1 V −90 −70 dB OPERATING TEMPERATURE RANGE−40 +85 °CAD8138Rev. F | Page 5 of 24±D IN to ±OUT SPECIFICATIONSAt 25°C, V S = 5 V , V OCM = 2.5 V , G = +1, R L, dm = 500 Ω, unless otherwise noted. Refer to Figure 39 for test setup and label descriptions. All specifications refer to single-ended input and differential output, unless otherwise noted. Table 3.Parameter Conditions Min Typ Max Unit DYNAMIC PERFORMANCE −3 dB Small Signal Bandwidth V OUT = 0.5 V p-p, C F = 0 pF 280 310 MHz V OUT = 0.5 V p-p, C F = 1 pF 225 MHz Bandwidth for 0.1 dB Flatness V OUT = 0.5 V p-p, C F = 0 pF 29 MHz Large Signal Bandwidth V OUT = 2 V p-p, C F = 0 pF 265 MHz Slew Rate V OUT = 2 V p-p, C F = 0 pF 950 V/μs Settling Time 0.01%, V OUT = 2 V p-p, C F = 1 pF 16 nsOverdrive Recovery Time V IN = 2.5 V to 0 V step, G = +2 4 ns NOISE/HARMONIC PERFORMANCE 1Second Harmonic V OUT = 2 V p-p, 5 MHz, R L, dm = 800 Ω −90 dBc V OUT = 2 V p-p, 20 MHz, R L, dm = 800 Ω −79 dBc V OUT = 2 V p-p, 70 MHz, R L, dm = 800 Ω −60 dBc Third Harmonic V OUT = 2 V p-p, 5 MHz, R L, dm = 800 Ω −100 dBc V OUT = 2 V p-p, 20 MHz, R L, dm = 800 Ω −82 dBc V OUT = 2 V p-p, 70 MHz, R L, dm = 800 Ω −53 dBc IMD 20 M Hz −74 dBc IP3 20 M Hz 35 dBm Voltage Noise (RTI) f = 100 kHz to 40 MHz 5 nV/√Hz Input Current Noise f = 100 kHz to 40 MHz 2 pA/√Hz INPUT CHARACTERISTICS Offset Voltage V OS, dm = V OUT, dm /2; V DIN+ = V DIN– = V OCM = 0 V −2.5 ±1 +2.5 mV T MIN to T MAX variation ±4 μV/°C Input Bias Current 3.5 7 μA T MIN to T MAX variation −0.01 μA/°C Input Resistance Differential 6 MΩ Common mode 3 MΩ Input Capacitance 1 pF Input Common-Mode Voltage −0.3 to +3.2 V CMRR ∆V OUT, dm /∆V IN, cm ; ∆V IN, cm = 1 V −77 −70 dB OUTPUT CHARACTERISTICS Output Voltage Swing Maximum ∆V OUT ; single-ended output 2.9 V p-p Output Current 95 mA Output Balance Error ∆V OUT, cm /∆V OUT, dm ; ∆V OUT, dm = 1 V −65 dB1Harmonic distortion performance is equal or slightly worse with higher values of R L, dm . See Figure 17 and Figure 18 for more information.AD8138Rev. F | Page 6 of 24V OCM TO ±OUT SPECIFICATIONSAt 25°C, V S = 5 V , V OCM = 2.5 V , G = +1, R L, dm = 500 Ω, unless otherwise noted. Refer to Figure 39 for test setup and label descriptions. All specifications refer to single-ended input and differential output, unless otherwise noted. Table 4.Parameter Conditions Min Typ Max UnitDYNAMIC PERFORMANCE −3 dB Bandwidth 220 MHz Slew Rate 250 V/μs INPUT VOLTAGE NOISE (RTI) f = 0.1 MHz to 100 MHz 17 nV/√Hz DC PERFORMANCE Input Voltage Range 1.0 to 3.8 V Input Resistance 100 kΩ Input Offset Voltage V OS, cm = V OUT, cm ; V DIN+ = V DIN– = V OCM = 0 V −5 ±1 +5 mV Input Bias Current 0.5 μA V OCM CMRR ∆V OUT, dm /∆V OCM ; ∆V OCM = 2.5 V ±1 V −70 dB Gain ∆V OUT, cm /∆V OCM ; ∆V OCM = 2.5 V ±1 V 0.9968 1 1.0032 V/V POWER SUPPLY Operating Range 2.7 11 V Quiescent Current 15 20 21 mA T MIN to T MAX variation 40 μA/°C Power Supply Rejection Ratio ∆V OUT, dm /∆V S ; ∆V S = ± 1 V −90 −70 dB OPERATING TEMPERATURE RANGE−40 +85 °CAD8138Rev. F | Page 7 of 24ABSOLUTE MAXIMUM RATINGSTable 5.Parameter Ratings Supply Voltage ±5.5 V V OCM ±V S Internal Power Dissipation 550 mW Operating Temperature Range −40°C to +85°C Storage Temperature Range −65°C to +150°C Lead Temperature (Soldering 10 sec) 300°C Junction Temperature 150°C Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.THERMAL RESISTANCEθJA is specified for the worst-case conditions, that is, θJA is specified for the device soldered in a circuit board in still air. Table 6.Package TypeθJA Unit 8-Lead SOIC/4-Layer 121 °C/W 8-Lead MSOP/4-Layer145 °C/WMaximum Power DissipationThe maximum safe power dissipation in the AD8138 packagesis limited by the associated rise in junction temperature (T J ) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit can change the stresses that the package exerts on the die, permanently shifting the parametric performance of the AD8138. Exceeding a junction temperature of 150°C for an extended period can result in changes in the silicon devices, potentially causing failure. The power dissipated in the package (P D ) is the sum of thequiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent power is the voltage between the supply pins (V S ) times the quiescent current (I S ). The load current consists of the differential and common-mode currents flowing to the load, as well as currents flowing through the external feedback networks and internal common-mode feedback loop. The internal resistor tap used in the common-mode feedback loop places a negligibledifferential load on the output. RMS voltages and currents should be considered when dealing with ac signals.Airflow reduces θJA . In addition, more metal directly in contact with the package leads from metal traces through holes, ground, and power planes reduces the θJA .Figure 3 shows the maximum safe power dissipation in the package vs. the ambient temperature for the 8-lead SOIC (121°C/W) and 8-lead MSOP (θJA = 145°C/W) packages on a JEDEC standard 4-layer board. θJA values are approximations.AMBIENT TEMPERATURE (°C)M A X I M U M P O W E R D I S S I P A T I O N (W )1.751.501.001.250.500.250.7501073-049Figure 3. Maximum Power Dissipation vs. TemperatureESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performancedegradation or loss of functionality.AD8138Rev. F | Page 8 of 24PIN CONFIGURATION AND FUNCTION DESCRIPTIONS–INV OCM V++OUT +IN NC V––OUTNC =NO CONNECT01073-004Figure 4. Pin ConfigurationTable 7. Pin Function DescriptionsPin No. Mnemonic Description1 −IN Negative Input Summing Node.2 V OCM Voltage applied to this pin sets the common-mode output voltage with a ratio of 1:1. For example, 1 V dc on V OCM sets the dc bias level on +OUT and −OUT to 1 V.3 V+ Positive Supply Voltage.4 +OUT Positive Output. Note that the voltage at −D IN is inverted at +OUT (see Figure 42).5 −OUT Negative Output. Note that the voltage at +D IN is inverted at −OUT (see Figure 42).6 V− Negative Supply Voltage.7 NC No Connect.8+INPositive Input Summing Node.AD8138Rev. F | Page 9 of 24TYPICAL PERFORMANCE CHARACTERISTICSUnless otherwise noted, Gain = 1, R G = R F = R L, dm = 499 V , T A = 25°C; refer to Figure 39 for test setup.FREQUENCY (MHz)G A I N (d B )–90–6–336110100100001073-005Figure 5. Small Signal Frequency ResponseFREQUENCY (MHz)G A I N (d B )–90–6–336110100100001073-006Figure 6. Small Signal Frequency ResponseG A I N (d B )–0.50.1–0.3–0.10.30.5FREQUENCY (MHz)11010001073-007Figure 7. 0.1 dB Flatness vs. Frequency FREQUENCY (MHz)G A I N (d B )–9–6–336110100100001073-008Figure 8. Large Signal Frequency ResponseFREQUENCY (MHz)G A I N (d B )–9–6–336110100100001073-009Figure 9. Large Signal Frequency ResponseFREQUENCY (MHz)G A I N (d B )–10102030110100100001073-010Figure 10. Small Signal Frequency Response for Various GainsAD8138Rev. F | Page 10 of 24FUNDAMENTAL FREQUENCY (MHz)D I S T O R T I O N (d B c )–50–120–90–100–110–70–80–6001020304050607001073-011Figure 11. Harmonic Distortion vs. FrequencyFUNDAMENTAL FREQUENCY (MHz)D I S T O R T I O N (d B c )–40–110–80–90–100–60–70–5001020304050607001073-012Figure 12. Harmonic Distortion vs. FrequencyD I S T O R T I O N (d B c )–50–90–100–70–80–60–40–30V OCM DC OUTPUT (V)–4–3–2–10123401073-013Figure 13. Harmonic Distortion vs. V OCM6–120–90–100–110–70–80–6054321DIFFERENTIAL OUTPUT VOLTAGE (V p-p)D I S T O R T I O N (d B c )01073-014Figure 14. Harmonic Distortion vs. Differential Output VoltageDIFFERENTIAL OUTPUT VOLTAGE (Vp-p)D I S T O R T I O N (d B c )–120–90–100–110–70–80–6012301073-0154Figure 15. Harmonic Distortion vs. Differential Output VoltageD I S T O R T I O N (d B c )–90–100–110–70–80–600.251.751.501.251.000.750.50DIFFERENTIAL OUTPUT VOLTAGE (V p-p)01073-016Figure 16. Harmonic Distortion vs. Differential Output VoltageAD8138D I S T O R T I O N (d B c )–90–100–110–70–80–60R LOAD (Ω)20060010001400180001073-017Figure 17. Harmonic Distortion vs. R LOAD–90–100–110–70–80–60–120200600100014001800R LOAD (Ω)D I S T O R T I O N (d B c )01073-018Figure 18. Harmonic Distortion vs. R LOADFREQUENCY (MHz)–50–90–110–70–30–101049.549.749.950.150.350.5P O U T (d B m )01073-019Figure 19. Intermodulation DistortionFREQUENCY (MHz)I N T E R C E P T (d B m )3025354045020406001073-02080Figure 20. Third-Order Intercept vs. Frequency01073-021Figure 21. Large Signal Transient Response01073-022Figure 22. Small Signal Transient ResponseAD813801073-023Figure 23. Large Signal Transient Response01073-024Figure 24. Large Signal Transient Response01073-025Figure 25. Settling Time01073-026Figure 26. Output Overdrive01073-028Figure 27. Large Signal Transient Response for Various Cap Loads (See Figure 40)FREQUENCY (MHz)C M R R (d B )–20–30–40–50–60–70–801101001k01073-029Figure 28. CMRR vs. FrequencyAD8138FREQUENCY (MHz)B A L A NC E E R R O R (d B )–20–30–40–50–60–701101001k 01073-031Figure 29. Output Balance Error vs. Frequency (See Figure 41)FREQUENCY (MHz)P S R R (d B )–20–30–40–50–60–70–10–80–901101001k01073-032Figure 30. PSRR vs. FrequencyFREQUENCY (MHz)I M P E D A N C E(Ω)1000.111011010001073-033Figure 31. Output Impedance vs. Frequency D I F F E R E N T I A L O U T P U T O F F S E T (mV )–5.0–2.52.55.0TEMPERATURE (°C)–40–2002040608010001073-034Figure 32. Output Referred Differential Offset Voltage vs. Temperature24513B I A S CU R R E N T (µA )TEMPERATURE (°C)–40–2002040608010001073-035Figure 33. Input Bias Current vs. Temperature10515202530TEMPERATURE (°C)S U P P L Y C U R R E N T (m A )–40–2002040608010001073-036Figure 34. Supply Current vs. TemperatureAD8138FREQUENCY (MHz)–90–6–336G A I N (d B )1101001k 01073-037Figure 35. V OCM Frequency Response01073-038Figure 36. V OCM Transient Response FREQUENCY (Hz)I N P U T C U R R E N T N O I S E (p AH z )100110100101k 10k 100k 1M01073-039Figure 37. Current Noise (RTI)FREQUENCY (Hz)I N P U T V O L T A G E N O I S E (n VH z )1001101000101001k 10k 100k 1M01073-040Figure 38. Voltage Noise (RTI)AD8138TEST CIRCUITS499Ω01073-003Figure 39. Basic Test Circuit01073-027Figure 40. Test Circuit for Cap Load Drive01073-030Figure 41. Test Circuit for Output BalanceAD8138OPERATIONAL DESCRIPTIONDEFINITION OF TERMSC +D –D V dm01073-041Figure 42. Circuit DefinitionsDifferential voltage refers to the difference between two node voltages. For example, the output differential voltage (or equivalently output differential-mode voltage) is defined asV OUT, dm = (V +OUT − V −OUT )where V +OUT and V −OUT refer to the voltages at the +OUT and −OUT terminals with respect to a common reference. Common-mode voltage refers to the average of two node voltages. The output common-mode voltage is defined asV OUT, cm = (V +OUT + V −OUT )/2Balance is a measure of how well differential signals arematched in amplitude and exactly 180° apart in phase. Balance is most easily determined by placing a well-matched resistor divider between the differential voltage nodes and comparing the magnitude of the signal at the divider’s midpoint with the magnitude of the differential signal (see Figure 41). By this definition, output balance is the magnitude of the outputcommon-mode voltage divided by the magnitude of the output differential mode voltage:dmOUT cm OUT V V Error Balance Output ,,=AD8138 THEORY OF OPERATIONThe AD8138 differs from conventional op amps in that it has two outputs whose voltages move in opposite directions. Like an op amp, it relies on high open-loop gain and negative feedback to force these outputs to the desired voltages. TheAD8138 behaves much like a standard voltage feedback op amp and makes it easy to perform single-ended-to-differential conversion, common-mode level-shifting, and amplification of differential signals. Also like an op amp, the AD8138 has high input impedance and low output impedance.Previous differential drivers, both discrete and integrated designs, have been based on using two independent amplifiers and two independent feedback loops, one to control each of the outputs. When these circuits are driven from a single-ended source, the resulting outputs are typically not well balanced. Achieving a balanced output has typically required exceptional matching of the amplifiers and feedback networks.DC common-mode level-shifting has also been difficult with previous differential drivers. Level-shifting has required the use of a third amplifier and feedback loop to control the output common-mode level. Sometimes the third amplifier has also been used to attempt to correct an inherently unbalanced circuit. Excellent performance over a wide frequency range has proven difficult with this approach.The AD8138 uses two feedback loops to separately control the differential and common-mode output voltages. The differential feedback, set with external resistors, controls only the differential output voltage. The common-mode feedback controls only the common-mode output voltage. This architecture makes it easy to arbitrarily set the output common-mode level. It is forced, by internal common-mode feedback, to be equal to the voltage applied to the V OCM input, without affecting the differential output voltage.The AD8138 architecture results in outputs that are very highly balanced over a wide frequency range without requiring tightly matched external components. The common-mode feedback loop forces the signal component of the output common-mode voltage to be zeroed. The result is nearly perfectly balanced differential outputs of identical amplitude and exactly180° apart in phase. ANALYZING AN APPLICATION CIRCUITThe AD8138 uses high open-loop gain and negative feedback to force its differential and common-mode output voltages in such a way as to minimize the differential and common-mode error voltages. The differential error voltage is defined as the voltage between the differential inputs labeled +IN and −IN in Figure 42. For most purposes, this voltage can be assumed to be zero. Similarly, the difference between the actual output common-mode voltage and the voltage applied to V OCM can also be assumed to be zero. Starting from these two assumptions, any application circuit can be analyzed.SETTING THE CLOSED-LOOP GAINNeglecting the capacitors C F, the differential-mode gain of the circuit in Figure 42 can be determined to be described bySGSFdmOUTdmOUTRRVV=,,This assumes the input resistors, R G S, and feedback resistors, R F S, on each side are equal.ESTIMATING THE OUTPUT NOISE VOLTAGE Similar to the case of a conventional op amp, the differential output errors (noise and offset voltages) can be estimated by multiplying the input referred terms, at +IN and −IN, by the circuit noise gain. The noise gain is defined as⎟⎟⎠⎞⎜⎜⎝⎛+=GFN RRG1To compute the total output referred noise for the circuit of Figure 42, consideration must also be given to the contribution of the Resistors R F and R G. Refer to Table 8 for the estimated output noise voltage densities at various closed-loop gains. Table 8.GainR G(Ω)R F(Ω)Bandwidth−3 dBOutputNoiseAD8138OnlyOutputNoiseAD8138 +R G, R F1 499 499 320 MHz 10 nV/√Hz 11.6 nV/√Hz2 499 1.0 k 180 MHz 15 nV/√Hz 18.2 nV/√Hz 5 499 2.49 k 70 MHz 30 nV/√Hz 37.9 nV/√Hz 10 499 4.99 k 30 MHz 55 nV/√Hz 70.8 nV/√Hz。

AD8138_cn

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. l: 781.329.4700 Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

低失真差分ADC驱动器 AD8138

特性

易于使用,单端至差分转换 可调输出共模电压 外部可调增益 低谐波失真 无杂散动态范围(SFDR):−94 dBc (5 MHz) 无杂散动态范围(SFDR):−85 dBc (20 MHz) −3 dB带宽:320 MHz (G = +1) 0.01%快速建立时间:16 ns 压摆率:1150 V/μs 快速过驱恢复:4 ns 低输入电压噪声:5 nV/√Hz 失调电压:1 mV(典型值) 宽电源电压范围:+3 V至±5 V 低功耗:90 mW (5 V) 0.1 dB增益平坦度达40 MHz 提供8引脚SOIC和MSOP封装

Rev. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

单端转差分运放

单端转差分运放什么是单端转差分运放?单端转差分运放(Single-ended to Differential Amplifier,简称SE to Diff Amp)是一种电路设计中常用的模块。

它可以将单端输入信号转换为差分输出信号,具有放大、滤波、抑制噪声等功能。

在信号处理、通信系统和测量仪器等领域得到广泛应用。

工作原理单端转差分运放主要由输入级、差分放大级和输出级组成。

下面我们逐个来看每个部分的工作原理。

输入级输入级通常由一个晶体管或场效应管构成。

它负责将输入信号转换为电流信号,并提供给差分放大级。

差分放大级差分放大级由两个晶体管或场效应管组成,一个作为正相输入,另一个作为负相输入。

这两个输入信号经过不同的增益系数放大后相减,得到一个差分输出信号。

输出级输出级通常由一个晶体管或场效应管构成。

它负责将差分输出信号转换为单端输出信号,并对其进行进一步增益和滤波。

特点与优势抗干扰能力强由于差分放大器的特性,它对共模信号具有较好的抑制能力。

共模信号是指同时作用于差分输入信号的干扰信号,如电源噪声、环境干扰等。

通过将差分输出信号取差值,可以有效地抵消共模干扰,提高系统的抗干扰能力。

放大增益高单端转差分运放具有较高的放大增益。

通过合理选择放大器的工作点和控制输入电流,可以实现较大的放大倍数。

这对于需要提高信号强度或增加系统灵敏度的应用非常重要。

低噪声单端转差分运放在设计中通常会采用低噪声元器件和布局技术,以降低系统噪声。

通过使用低噪声晶体管、降噪滤波电路等手段,可以有效地减少系统中的噪声源,并提高信号质量。

宽带宽单端转差分运放通常具有较宽的频率响应范围。

这意味着它可以处理更多频率范围内的信号,并保持较好的线性响应特性。

这在一些需要高频信号处理的应用中非常重要,如通信系统、音频放大器等。

灵活性单端转差分运放可以根据具体应用需求进行灵活的配置和调整。

通过选择不同的元器件、电路拓扑和工作参数,可以实现不同的功能和性能要求。

简单分立式单端转差分精密仪表放大器电路介绍

简单分立式单端转差分精密仪表放大器电路介绍

简介

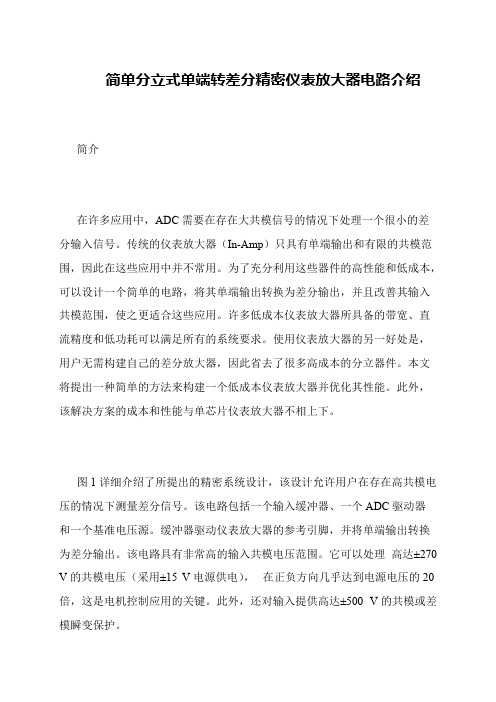

在许多应用中,ADC需要在存在大共模信号的情况下处理一个很小的差分输入信号。

传统的仪表放大器(In-Amp)只具有单端输出和有限的共模范围,因此在这些应用中并不常用。

为了充分利用这些器件的高性能和低成本,可以设计一个简单的电路,将其单端输出转换为差分输出,并且改善其输入共模范围,使之更适合这些应用。

许多低成本仪表放大器所具备的带宽、直流精度和低功耗可以满足所有的系统要求。

使用仪表放大器的另一好处是,用户无需构建自己的差分放大器,因此省去了很多高成本的分立器件。

本文将提出一种简单的方法来构建一个低成本仪表放大器并优化其性能。

此外,该解决方案的成本和性能与单芯片仪表放大器不相上下。

图1详细介绍了所提出的精密系统设计,该设计允许用户在存在高共模电压的情况下测量差分信号。

该电路包括一个输入缓冲器、一个ADC驱动器

和一个基准电压源。

缓冲器驱动仪表放大器的参考引脚,并将单端输出转换为差分输出。

该电路具有非常高的输入共模电压范围。

它可以处理高达±270 V的共模电压(采用±15 V电源供电),在正负方向几乎达到电源电压的20倍,这是电机控制应用的关键。

此外,还对输入提供高达±500 V的共模或差模瞬变保护。

AD831的工作原理及内部电路框图

AD831的工作原理及内部电路框图AD831的工作原理图2 所示是AD831的内部电路框图。

图中,频频输入信号加到晶体管Q1、Q2的基极,由于电阻R1、R2的负反馈潮作用,因而差分电流射频信号的幅度成线性关系。

-10dBm的本振输入信号经过一个高增益、低噪声的限幅放大器转换成方波,而后交叉地加到Q3~Q6的基极,最后混频信号从IFP和IFN 脚输出。

当将IFP、IFN连接到有中心抽头的变压器上时,AD831不可提供从射频到中频的单路输出。

若使用输出放大器,则可降IFP和IFN脚直接与AP 和AN脚相连,这时,片内的负载电阻可将输出电流转换成电压来驱动输出放大器。

2.2 控制偏置电流AD831 的射频输出的最大值与偏置电流成比例,在BIAS引脚与电源之间接一个电阻可使偏置电流减小。

正常工作时可将BIAS脚悬空,而在低功耗工作时,可将BIAS脚直接连接到正电源。

混频器工作电流的调节范围可从正常工作的100mA调整至最小功耗时的45mA。

2.3 低通滤波在混频和输出放大器之间可加入一个简单的低通滤波器,方法是在芯片的内部电阻性负载上并联一个外接电容(芯片的内部电阻性负载为14Ω,允许有20%的偏差),这样在下混频应用中将显著衰减本振信号和射频信号的和频成分。

该一阶低通滤波器的转折频率,应选择在比下混频的IF输出高一个倍频程的位置。

例如,对70MHz中频输出而言,- 3dB点可选在140MHz附近,此时CF应为82pF。

2.4 输出放大器的应用AD831 的输出放大器可将混频的差分电流转换为单端电压输出形式,并可在50Ω的负载上提供高达1V的峰-峰值电压。

把AN和AP直接连接到混频级的集电极输出上,并将输出端(OUT)接至VFB,这样可提供单增益。

改变增益时,可在放大器的输出端外接一个电阻网络R3、R4并连接至VFB。

3 在频踪式雷达本振中的应用图3是基于直接数字频率合成技术(DDS)的某频踪式雷达的本振组成框图。

差分PAL-D制式视频转单端PAL-D制式视频模块设计-EEFocus

差分PAL-D制式视频转单端PAL-D制式视

频模块设计

在系统PAL-D制式视频接收端,采用AD8130来实现差分转单端PAL-D制式视频信号的功能。

AD8130在输出电压峰峰值为2V时,其3dB

-带宽典型值为155MHz,远高于PAL-D制式视频信号的6MHz带宽。

AD8130只能实现一路PAL-D制式视频的转换,因此系统共采用4片AD8130来实现对4路差分PAL-D制式输入视频的转换。

基于AD8130的差分转单端PAL-D制式视频模块的电路原理图如图1所示,电路中配置放大器转换增益为1,符合系统的接口设计约定。

系统采用5V

±电源对其单独供电,整个模块均采用单独的模拟地参考平面。

输入差分视频对间跨接150Ω电阻,而输出的单端视频信号则对地接75Ω匹配电阻。

AD8130的PD管脚直连5V

+电源,确保芯片处于正常工作模式。

图1 差分PAL-D制式视频转单端PAL-D制式视频模块电路原理图。

高速差分ADC驱动放大器AD8137及其应用.

高速差分ADC驱动放大器AD8137及其应用1 引言在混合信号系统中,数据采集部分的速度对系统的效率至关重要,因此就要求有高速的模数转换器和与之配套的驱动器。

AD8137是ADI公司最近推出的一种带有轨-轨输出的低成本全差分高速放大器,它具有低噪声、低失真和宽动态范围,用于驱动12位ADC,适合于要求低成本和低功耗的系统。

AD8137采用ADI公司新一代的XFCB双极型工艺制造,其内部具有共模反馈结构,使之可以通过施加于一个管脚上的电压来控制其输出的共模电压。

它内部的反馈环能实现平衡输出,同时还可以抑制偶次谐波失真。

利用AD8137很容易实现全差分和单端-差分结构,在典型连接下,四个电阻组成的外部反馈网络决定了放大器的闭环增益,使其具有极大的灵活性。

2 AD8137简介2.1 特点AD8137有以下几大特点:全差分;外部增益可调;输出共模电压可调整;低输入偏移电压和电流;110MHz大信号带宽,450V/μs转换速率体现其高速性能;轨-轨输出;供电电压低且有掉电特性;电流小,5V供电时静态电流仅2.6mA,掉电模式时为450μA;有全差分和单端-差分两种工作方式;电源电压工作范围可达3~12V。

2.2 引脚说明图1是AD8137的8脚SOIC封装图,表1是其管脚功能描述。

图1 8脚SOIC封装表1:管脚功能描述2.3 器件工作原理AD8137是一个低功率、低成本、全差分电压反馈放大器,它具有轨-轨输出,含内部共模参考电压的共模电路,以及偏置关断电路,其原理框图如图2所示。

从图中可见,输入跨导部分是一个H桥,它的输出电流镜像到高阻结点CP和CN。

输出部分是传统的H桥驱动电路,带有普通的发射装置驱动结点+OUT和-OUT。

AD8137采用两个反馈环来分别控制差模和共模反馈。

它的差模增益由外部电阻决定,这与传统放大器一样,而输出共模电压由一个受外部V OCM输入控制的内部反馈环决定。

这样的结构使得可以很容易地任意设定输出的共模电压,而不影响放大器的差模增益。

AD8137、AD8138、AD8139简介

AD8137 、AD8138、AD8139简介1、AD8138高性能高速320MHz差分放大器,采用XFCB双极工艺,容易用作单端到差分放大器的转换,从而简化差分信号放大和驱动,-3dB带宽320MHz,可调整共模输出电压,外部调整增益和低的谐波失真(在5MHz和800欧姆负载时二次为-94dBc,三次为-114dBc),它的差分输出帮助平衡输入到差分ADC,最大化ADC的性能和不需要变压器,从而保留了低频和DC信息,到0.01%的建立时间为16ns,转换速率为1150V/us,过驱动的恢复时间为4ns,输入电压噪音5nV/√Hz,失调电压为1mV,工作电压从3V到±5V,5V时的功耗为90mW,8引脚SOIC和MSOP封装,工作温度-40度到85度C,可用在ADC驱动器,单端到差分转换器,IF和基带增益区块,差分缓冲器和线路驱动器。

2、AD8139和AD8137满足驱动12 bit ~18 bit ADC 的性能要求美国模拟器件公司(Analog Devices, Inc., 简称ADI)最新推出的全差分高速放大器具有业界最好的低噪声、低失真和宽动态范围,是用于驱动高速模数转换器(ADC)的理想产品。

ADI公司扩展差分放大器产品种类的最新成员是AD8139 和 AD8137。

它们专为满足驱动12 bit ~18 bit ADC的性能要求而设计,12 bit ~18 bit ADC是宽带仪器仪表、通信设备、军用设备和工业设备应用的关键器件。

● AD8139是目前仅有的能够解决驱动16 bit和18 bit 高速ADC问题的差分放大器,并具 有低噪声、低失真和满电源电压摆幅(R-R)输出特性的最佳组合。

● AD8137是市场上最低功耗、最低成本的高速差分放大器,用于驱动12 bit 电池供电的数据采集系统和其它对功耗和价格要求严格的系统。

①关于AD8139AD8139具有1.9 nV/√Hz/折合到输入端噪声谱密度,115 dBc 无杂散动态范围(SFDR)(1 MHz 时)和370 MHz带宽,非常适合驱动高速、高分辨率16 bit和 18 bit ADC。

AD8138 单端变差分

电路笔记CN-0040连接/参考器件利用ADI公司产品进行电路设计差分输入、双通道、3 MSPS 12位SARADCAD7352放心运用这些配套产品迅速完成设计。

Rev.A“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devicesengineers. Standard engineering practices have been employed in the design and constructionof each circuit, and their function and performance have been tested and verified in a labenvironment at room temperature. However, you are solely responsible for testing the circuitand determining its suitability and applicability for your use and application. Accordingly, inno event shall Analog Devices be liable for direct, indirect, special, incidental, consequential orpunitive damages due to any cause whatsoever connected to the use of any “Circuit from theLab”. (Continued on last page)One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: Fax: 781.461.3113©2009 Analog Devices, Inc. All rights reserved.AD8138低失真差分ADC驱动器欲获得更多信息和/或技术支持,请拨打4006-100-006或访问/zh/circuits。

AD8132差分转单端

AD8132差分转单端AD8132:产品详情AD8132是一款低成本、差分或单端输入至差分输出放大器,通过电阻设置增益。

相对于运算放大器,AD8132在驱动差分输入ADC或驱动信号长线路传输方面取得了重大进步。

它具有独特的内部反馈特性,在10 MHz时可提供于−68 dB达成的输出增益和相位匹配平衡,能够抑制谐波并降低辐射电磁干扰(EMI)。

AD8132采用ADI公司新一代XFCB双极性工艺制造,−3 dB带宽为350 MHz,提供差分信号,5 MHz时的无杂散动态范围(SFDR)为−99 dBc,而且成本低廉。

该器件无需使用具有高性能ADC的变压器,并保留低频和直流信息。

在VOCM引脚上施加电压便可调整差分输出的共模电平,从而使驱动单电源ADC的输入信号可轻松实现电平转换。

快速过载恢复则可确保采样精度。

AD8132也可用作通过低成本双绞线或同轴电缆实现高速信号传输的差分驱动器。

可通过调整反馈网络,来提升信号的高频成分。

AD8132可以用于模拟、数字视频信号或其它高速数据传输,还能够驱动3类、5类双绞线或同轴电缆,且线路衰减极小。

与分立式线路驱动器解决方案相比,AD8132的成本和性能有明显改善。

差分信号处理可降低接地噪声对接地参考系统的影响。

AD8132可用于整个信号链的差分信号处理(增益和滤波),大大简化了差分和单端器件之间的接口转换。

AD8132W属于汽车应用级产品,通过AEC-Q100认证,适合在125°C温度下工作。

更多详情参见“汽车应用级产品”部分。

AD8132提供8引脚SOIC和8引脚MSOP两种封装,工作温度范围为−40°C至+125°C扩展工业温度范围。

应用低功耗差分ADC驱动器差分增益和差分滤波视频线路驱动器差分输入/输出电平转换单端输入至差分输出驱动器特点:高速-3 dB带宽:350 MHz压摆率:1200 V/μs通过电阻设置增益内部共模反馈改进的增益和相位平衡:-68 dB (10 MHz)利用单独的输入设置共模输出电压低失真:−99 dBc SFDR(5 MHz,800 Ω负载)低功耗:10.7 mA(5 V时)电源电压范围:+2.7 V至±5.5 V通过AEC-Q100认证(AD8132W)Low Cost , High speed ,Differential Amplifier350Mhz ,-3 dB bandwidthLow Power :10.7mA @ 5VPower supply range : ±2.7 V to ±5.5V单端转差分设计电路ADI自带的设计软件:Diff Amp Calculaor “电路设计如下:一款很好的单端转差分方案,但是运放电源电压具有局限性。

AD的差分输入与单端输入

AD的差分输入与单端输入

单端输入,输入信号均以共同的地线为基准.这种输入方法主要应用于输入信号电压较高(高于1 V),信号源到模拟输入硬件的导线较短(低于15 ft),且所有的输入信号共用一个基准地线.如果信号达不到这些标准,此时应该用差分输入.对于差分输入,每一个输入信号都有自有的基准地线;由于共模噪声可以被导线所消除,从而减小了噪声误差.

单端输入时, 是判断信号与GND 的电压差. 差分输入时, 是判断两个信号线的电压差.

信号受干扰时, 差分的两线会同时受影响, 但电压差变化不大. (抗干扰性较佳) 而单端输入的一线变化时, GND 不变, 所以电压差变化较大. (抗干扰性较差) 差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面:

a.抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

b.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

c.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。

目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。

当AD的输入信号只有一路时,为了更好地抑制共模噪声,我们可以采用差分输入方式。

这就需要我们首

先要将单端变成差分,可以用运放AD8138实现。

北斗二代中频信号采集设备使用说明书

本设计中采用 SI4133 做为射频本振频综芯片,Si4133 数字锁相式频率合成器芯片的基本模块框 图如图 3 所示。它包含 3 路 PLL(锁相环路)。每路 PLL 由 PD(相位检测器)、LF(环路滤波器)、VCO 和可编程分频器构成。

图3

9

下面以 1 路 PLL 为例,简要介绍该芯片工作原理。参考频率 fin 从 XIN 脚输入,通过放大器、R 分频器后,得到频率 fin/R,同时,这路 VCO 的输出频率 fout 经过一个 N 分频器后,得到频率 fout /N,2 个频率输入到 PD 进行相位比较,产生误差控制电压,该误差电压经过 LF 可得一误差信号的 直流分量作为 VCO 的输入,用于调整 VCO 的输出信号频率,使 VCO 分频后的信号频率 fout/N 向 fin/R 近于相等,直至最后两者频率相等而相位同步实现锁定。环路锁定时,PD 的输人频差为 0, 即 fin/R=fout/N,fout=Nfin/R,可以通过改变输出信号的分频系数 N 和参考信号的分频系数 R 来 改变输出信号的频率。

HMC476SC70 性能指标如图 2 所示

图2 在各级 LNA 输出后接入一级射频带通滤波器(声表滤波器 SAW),实际测试中每级 LNA 达到 15dB 的增益,两级 LNA 联合增益 30dB 左右,实际通道中计入两级 SAW 插损,末级 PI 型匹配网络衰减, 线路和接头插损等,共计约 10dB 的损耗,实际两级低噪放级联获得 20dB 的增益。

二. 北斗二代卫星中频信号采集设备原理设计详细介绍 (1)两级 前端低噪放(LNA)

两级前端低噪放选择 HMC476SC70 芯片,设计原理图所图 1 所示

图1

8

HMC476SC70 是一款 MMIC 增益放大器,频率覆盖 DC 到 6GHz 范围,噪声系数低,并且输出 1dB 压缩点可达+12dBm,非常适合于抗干扰类型接收机前端 LNA 场合使用。

单端转差分 运放

单端转差分运放单端转差分运放是一种常用的放大器电路,用于将单端信号转换为差分信号。

中括号内的内容作为主题,本文将详细介绍单端转差分运放的工作原理、特点、应用以及设计步骤。

一、工作原理单端转差分运放的工作原理是通过引入一个差模输入电阻和差模输出电阻,将单端输入信号转换为差分信号输出。

其基本电路如图1所示,包括输入级、放大级和输出级。

图1 单端转差分运放基本电路1. 输入级:输入级使用差模放大电路,由两个输入电阻R1和R2、晶体管Q1和Q2组成。

其中,输入电阻R1和R2用来提供单端输入信号,晶体管Q1和Q2通过共射极方式放大输入信号。

2. 放大级:放大级使用共射放大电路,由晶体管Q3和电阻RC组成。

放大级通过放大输入级输出的信号,产生差分信号。

3. 输出级:输出级使用共射放大电路,由晶体管Q4和电阻RL组成。

输出级通过放大放大级输出的信号,形成最终的差分信号输出。

二、特点1. 差分放大:单端转差分运放可以将单端输入信号转换为差分输出信号,能够增大信号的幅度,并提高信噪比。

2. 抑制共模干扰:由于差分信号对共模干扰具有较好的抵抗能力,所以单端转差分运放能够有效抑制来自干扰源的共模信号。

3. 输入/输出阻抗匹配:单端转差分运放的输入输出电阻可根据需要进行匹配,以实现更好的信号传递效果。

三、应用单端转差分运放在电子领域有广泛的应用,包括但不限于以下几个方面:1. 信号放大:通过将单端输入信号转换为差分信号输出,单端转差分运放可以实现信号放大,广泛应用于音频放大器、微弱信号放大器等领域。

2. 仪器测量:在实际测量中,经常会遇到共模干扰的问题。

单端转差分运放具有良好的抵抗共模干扰的特点,因此广泛应用于信号测量、仪器仪表等领域。

3. 差分信号传输:单端转差分运放可以将信号进行差分传输,提高信号的传输质量和抗干扰能力。

在远距离信号传输以及高速数据传输等领域有着重要的应用。

四、设计步骤设计一个单端转差分运放电路,需要进行如下步骤:1. 确定输入电阻和放大倍数:根据实际需求,确定输入电阻和放大倍数的大小。