桂林电子科技大学-EDA试卷(guet)

eda期末考试复习题

eda期末考试复习题EDA期末考试复习题一、选择题(每题2分,共20分)1. EDA(Electronic Design Automation)是指:A. 电子设计自动化B. 电子数据交换C. 电子文档自动化D. 电子设备自动化2. 在EDA工具中,用于设计和仿真数字逻辑电路的软件是:A. MATLABB. VHDLC. SPICED. AutoCAD3. 下列哪个不是硬件描述语言(HDL)?A. VerilogB. VHDLC. C++D. SystemVerilog4. FPGA(Field-Programmable Gate Array)是一种:A. 可编程逻辑器件B. 微处理器C. 存储器D. 网络设备5. 在VHDL中,以下哪个关键字用于定义实体?A. entityB. architectureC. processD. package6. 以下哪个是模拟电路设计中常用的EDA工具?A. Quartus IIB. ModelSimC. CadenceD. Xilinx ISE7. 以下哪个不是数字电路设计中的基本逻辑门?A. ANDB. ORC. NOTD. XOR8. 在VHDL中,以下哪个是并行赋值语句?A. ifB. caseC. loopD. when9. 在EDA设计流程中,仿真验证的目的是:A. 检查电路是否能正常工作B. 检查电路的物理尺寸C. 检查电路的功耗D. 检查电路的散热性能10. 以下哪个不是EDA设计流程中的步骤?A. 电路设计B. 仿真验证C. 版图设计D. 电路测试二、填空题(每空2分,共20分)11. 在VHDL中,用于定义端口的关键字是________。

12. FPGA的编程方式包括________和________。

13. 一个完整的EDA设计流程通常包括________、________、________、________和________。

14. 在数字电路设计中,________是一种用于描述电路行为的建模方式。

eda技术及应用考试及答案

eda技术及应用考试及答案一、单选题(每题2分,共20分)1. EDA技术的核心是()。

A. 电子设计自动化B. 电子制造自动化C. 电子测试自动化D. 电子组装自动化答案:A2. 在EDA技术中,HDL指的是()。

A. 高级设计语言B. 硬件描述语言C. 硬件描述逻辑D. 高级描述语言答案:B3. 以下哪个不是EDA软件的主要功能()。

A. 逻辑综合B. 电路仿真C. 布线D. 机械加工答案:D4. 在EDA技术中,FPGA指的是()。

A. 现场可编程门阵列B. 固定可编程门阵列C. 现场可配置逻辑阵列D. 固定可配置逻辑阵列答案:A5. 以下哪个不是EDA技术中常用的仿真工具()。

A. ModelSimB. QuartusC. MATLABD. ISE答案:C6. 在EDA技术中,ASIC指的是()。

A. 应用特定集成电路B. 应用通用集成电路C. 应用特定逻辑阵列D. 应用通用逻辑阵列答案:A7. 在EDA技术中,以下哪个不是硬件描述语言()。

A. VHDLB. VerilogC. C语言D. SystemVerilog答案:C8. 在EDA技术中,以下哪个不是逻辑综合的主要任务()。

A. 优化逻辑B. 布局C. 布线D. 时序分析答案:C9. 在EDA技术中,以下哪个不是FPGA的主要优点()。

A. 可重构性B. 可编程性C. 低成本D. 高性能答案:C10. 在EDA技术中,以下哪个不是ASIC的主要优点()。

A. 高性能B. 低成本C. 低功耗D. 高可靠性答案:B二、多选题(每题3分,共15分)11. EDA技术的主要应用领域包括()。

A. 通信B. 计算机C. 消费电子D. 军事答案:ABCD12. 在EDA技术中,以下哪些是硬件描述语言的特点()。

A. 层次性B. 并行性C. 抽象性D. 可读性答案:ABC13. 在EDA技术中,以下哪些是FPGA的主要缺点()。

A. 成本高B. 速度慢C. 功耗大D. 灵活性差答案:ABC14. 在EDA技术中,以下哪些是ASIC的主要缺点()。

桂林电子科技电子电路试卷

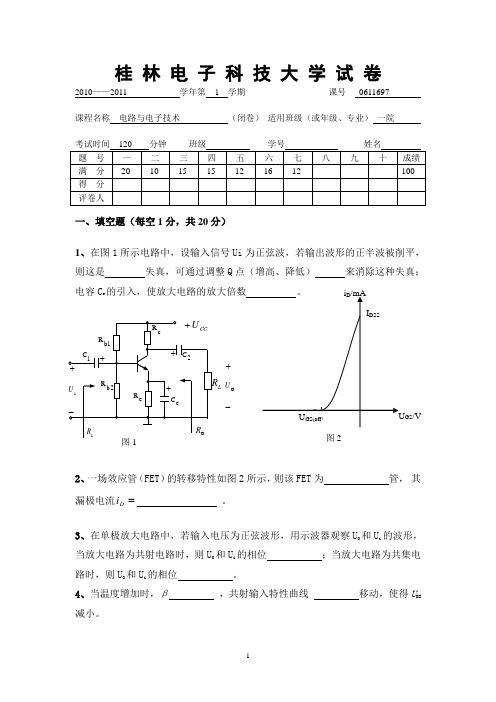

桂林电子科技大学试卷2010——2011 学年第 1 学期课号0611697课程名称电路与电子技术(闭卷)适用班级(或年级、专业)一院一、填空题(每空1分,共20分)1、在图1所示电路中,设输入信号Ui为正弦波,若输出波形的正半波被削平,则这是失真,可通过调整Q点(增高、降低)来消除这种失真;电容Ce2、一场效应管(FET)的转移特性如图2所示,则该FET为管,其漏极电流=Di。

3、在单极放大电路中,若输入电压为正弦波形,用示波器观察UO和Ui的波形,当放大电路为共射电路时,则UO和Ui的相位;当放大电路为共集电路时,则UO和Ui的相位。

4、当温度增加时,β,共射输入特性曲线移动,使得U BE 减小。

5、已知电路如图3所示,T 1 、T 2构成NPN-PNP 互补对称甲乙类功放,在每管 工作时都是 组态。

电路中D、D 的作用是消除 。

6、某放幅频特性如=∙A ,通频带=bw f 。

7、当电路的410=f A ,开环放大电路放大倍数的相对变化10%,闭环放大电路放大倍数的相对变化1%,则此时电路的开环放大倍数为 。

8、图5是某放大器的通用模型。

如果该放大器的端电压增益100o u i U A U ==-&&&,则该放大器的o us s U A U ==&&& ( ), uo A =&( )。

9、正弦波振荡电路的平衡条件 。

正弦波振荡电路起振的幅值条件是 。

10、直流稳压电源由电源变压器、 、 和稳压电路四个部分组成。

CCU图5100Ω2K Ω二、选择题(每题2分,共10分)1、二极管电路如图所示,则二极管的导通关系是( )。

①、 V D1,V D2均导通 ②、 V D1导通,V D2截止 ③、 V D1截止,V D2导通④、 V D1,V D2均截止2、测得放大电路中三极管各极电压为:U A =3.5V ,U B =1.5V ,U C =1.3V ,则该管为( )。

EDA期末考试题A卷(可编辑修改word版)

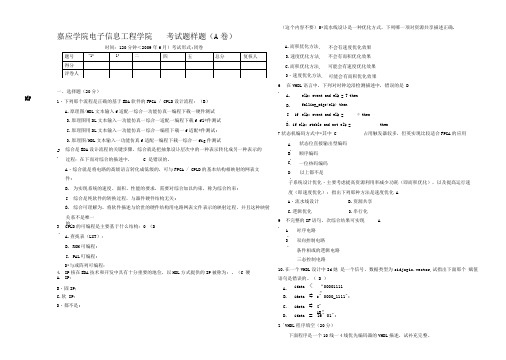

(这个内容不要)5•流水线设讣是一种优化方式,下列哪一项对资源共享描述正确.DlP 嘉应学院电子信息工程学院考试题样题(A卷)时间:120分钟<2009年6月)考试形式:闭卷一、选择题(20分)1・下列那个流程是正确的基于EDA软件的FPGA / CPLD设计流程:(B)A.原理图/HDL文本输入f适配一综合一功能仿真一编程下载一硬件测试B.原理图用DL文本输入一功能仿真一综合一适配一编程下载f fl®件测试C.原理图用DL文本输入一功能仿真一综合一编程下载一f适配®件测试:D.原理图/HDL文本输入一功能仿真f适配一编程下载一综合一fig件测试6.A.而积优化方法,B.速度优化方法,C.而积优化方法,D・速度优化方法,不会有速度优化效果不会有而积优化效果可能会有速度优化效果可能会有而积优化效果在VHDL语言中,下列对时钟边沿检测描述中,错误的是 DA.B.C.ifelk* event and elk = T thenfal1ing_edge(elk) thenelk* event and elk = © thenD. if elk* stable and not elk =then7状态机编码方式中•其中 C 占用触发器较多,但英实现比较适合FPGA的应用A・状态位直接输出型编码2.综合是EDA设讣流程的关键步骤,综合就是把抽象设讣层次中的一种表示转化成另一种表示的过程:在下而对综合的描述中, C 是错误的。

A・综合就是将电路的髙级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件:B・C,D・顺序编码一位热码编码以上都不是子系统设计优化・主要考虑提高资源利用率减少功耗(即而积优化),以及提髙运行速B. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约朿:度(即速度优化):指出下列那种方法是速度优化 A C.综合是纯软件的转换过程,与器件硬件结构无关;A・流水线设计 B.资源共享3・D. 综合可理解为,将软件描述与给世的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的。

2022年桂林电子科技大学计算机科学与技术专业《操作系统》科目期末试卷A(有答案)

2022年桂林电子科技大学计算机科学与技术专业《操作系统》科目期末试卷A(有答案)一、选择题1、某文件系统的簇和磁盘扇区大小分别为1KB和512B。

若一个文件的大小为1026B,则系统分配给该文件的磁盘空间大小是()。

A.1026BB.1536BC.1538BD.2048B2、已知某磁盘的平均转速为r秒/转,平均寻找时间为T秒,每个磁道可以存储的字节数为N,现向该磁盘读写b字节的数据,采用随机寻道的方法,每道的所有扇区组成一个簇,其平均访问时间是()。

A.(r+T)b/NB.b/NTC.(b/N+T)D.bT/N+r3、进程P1和P2均包含并发执行的线程,部分伪代码描述如下所//进程P1 //进程P2int x=0; int x=0;Thread1() Thread3(){int a; {int a:a=1; a=x;x+=1; x+=3;Thread2() Thread4(){ {int a: int b, aa=2; b=x;x+=2; x1=4;} }下列选项中,需要互斥执行的操作是()。

A. a=l与a=2B. a=x与b=xC. x+=1与x+=2D. x+=1与x+=34、下面哪个特征是并发程序执行的特点()。

A.程序执行的间断性B.相通信的可能性C.产生死锁的可能性D.资源分配的动态性5、一次性分配所有资源的方法可以预防死锁的发生,这种方法破坏的是产生死锁的4个必要条件中的()。

A.互斥条件B.占有并请求C.不剥夺条件D.循环等待6、某系统采用改进型CLOCK置换算法,页表项中字段A为访问位,M为修改位。

A=0表示页最近没有被访问,A=1表示页最近被访问过。

M=0表示页没有被修改过,M=1表示页被修改过。

按(A,M)所有可能的取值,将页分为4类:(0,0)、(1,0)、(0,1)和(1,1),则该算法淘汰页的次序为()。

A.(0,0),(0,1),(1,0),(1,1)B.(0,0),(1,0),(0,1),(1,1)C.(0,0),(0,1),(1,1),(1,0)D.(0,0),(1,1),(0,1),(1,0)7、在空白表中,空白区按其长度由小到大进行查找的算法称为()算法。

2021考研复习桂林电子科技大学信息与通信学院 2016硕士研究生入学考试复试试卷208通信电子电路及EDA技术A

(1)画出交流等效电路;

(2)说明振荡器的类型以及振荡器振荡的条件;

(3)计算振荡频率 fs ;

(4)计算反馈系数 F。

EC

Rb1

Rc

Cb

Rb2

Re

Ce

C1 C3

C2 L

3. 某 FM 调 制 器 的 调 制 灵 敏 度 k f 5kHz/V , 调 制 信 号 u (t) 2 cos(2 2000t) , 载 波 uc (t) 10 cos(4 106 t) 。试求:

考研复习

真题讲解

桂林电子科技大学 2016 硕士研究生入学考试复试试卷

考试科目代码 208 考试科目名称:通信电子电路及 EDA 技术 A

请注意:答案必须写在答题纸上(写在试卷上无效)。

通信电子电路

一、填空题(每空1分,共14分)

1. 理想的LC谐振回路的矩形系数是

,单LC谐振回路的矩形系数

是

。

2. 设丙类高频功放开始工作于临界工作状态,则:单独增大集电极直流电源电压Ec(其

uAM (t)

cos o t

6. 已 知 调 制 信 号 为 u (t) U cos 2 103t , 调 相 指 数 mp 10 , 此 时 PM 波 的 带 宽 是

kHz。若

U 、调制信号频率F增大一倍,此时PM波的带宽变为

7. 锁相环路包含

、

和鉴相器。

kHz。

二、计算题(每题12分,共36分)

begin

case(C_ST)

S0: begin COMOUT<= ⑶ ;

共 4页

第3 页

请注意:答案必须写在答题纸上(写在试卷上无效)。

if (SINPUT= = ⑷ ) NEXT_STATE<= ⑸ ; else if(SINPUT= = ⑹ ) NEXT_STATE<= ⑺ ; else NEXT_STATE<= ⑻ ; end

2022年桂林电子科技大学计算机科学与技术专业《操作系统》科目期末试卷B(有答案)

2022年桂林电子科技大学计算机科学与技术专业《操作系统》科目期末试卷B(有答案)一、选择题1、下面关于目录检索的论述中,正确的是()。

A.由于散列法具有较快的检索速度,因此现代操作系统中都用它来替代传统的顺序检索方法B.在利用顺序检索法时,对树形目录应采用文件的路径名,应从根目录开始逐级检索C.在利用顺序检索法时,只要路径名的一个分量名未找到,便应停止查找D.在顺序检索法的查找完成后,即可得到文件的物理地址,2、文件系统用位图法表示磁盘空间的分配情况,位图存于磁盘的32~127号块中,每个盘块占1024B.盘块和块内字节均从0开始编号。

假设要释放的盘块号为409612,则位图中要修改的位所在的盘块号和块内字节序号分别是()。

A.81,1B.81,2C.82,1D.82,23、在操作系统中,一方面每个进程具有独立性,另一方面进程之间具有相互制约性。

对于任何两个并发进程,它们()。

A.必定无关B.必定相关C.可能相关D.可能相同4、可以被多个进程在任意时刻共享的代码必须是()。

A.顺序代码B.机器语言代码C.不能自身修改的代码D.无转移指令代码5、与单道程序相比,多道程序系统的优点是()I.CPU 利用率高II.系统开销小III.系统吞吐量大IV. I/O设备利用率高A.仅I、IIIB.仅I、IVC. 仅II、IIID.仅I、III,IV6、解决主存碎片问题较好的存储器管理方式是()A.可变分区B.分页管理C.分段管理D.单一连续分配7、假定某页式管理系统中,主存为128KB,分成32块,块号为0,1,2,3,....31:某作业有5块,其页号为0,1,2,3,4,被分别装入主存的3,8,4,6,9块中。

有一逻辑地址为[3,70]。

试求出相应的物理地址(其中方括号中的第一个元素为页号,第二个元素为页内地址,按十进制计算)()。

A.14646B.24646C.24576D.345768、()不是操作系统的功能。

2021考研复习桂林电子科技大学信息与通信学院 2016硕士研究生入学考试复试试卷311通信电子电路及EDA技术B

input[4:1] A,B;

reg [7:0] R;

integer i;

always@(A or B)

begin

R=0;

for (i=1;i<=4;i++)

if(B[i]) R=R+(A<<(i-1);

end endmodule

若 A= 4'b1011,B= 4'b1010,程序运行

第 1 次循环后 R=

共4 页

第1 页

请注意:答案必须写在答题纸上(写在试卷上无效)。

L1

C

RL

is

Rs L2

2. 下图所示 LC 正弦波振荡电路,图中 Cb 、 Ce 为旁路电容, Rb1 15kΩ , Rb2 7.5kΩ ,

Rc 2.7kΩ , Re 2kΩ , C1 500pF , C2 1000pF , C3 30pF , L 2.5μH 。

MHz,fm =

kHz。

fc

fI

fm

fL

fm

5. AM 信号的载波频率为 100kHz,载波振幅为 10V,调制信号频率为 10kHz。则 AM 信号带宽为

kHz,AM 信号载波分量消耗在单位电阻上的功率为

W。

6. 已知调制信号为 u (t) U cos 2 103t ,调相指数 mp 10 ,此时PM波的带宽是 若

结束。

2.状态机按信号输出方式分,有米利型和

型两种。

3.阻塞赋值语句的操作符是

,非阻塞赋值语句的操作符是

。

4.对于“a=b?d:c”,若 b=1’b0,d=1’b1,c=1’b0,则 a=

。

5.Verilog HDL 中对于边沿的描述,用关键词 posedge 描述上升沿,以

EDA技术期末试卷(含答案)

EDA技术期末试卷(含答案)班级学号姓名密封线内不得答题⼀、单项选择题(30分) 1.以下描述错误的是 CA .QuartusII 是Altera 提供的FPGA/CPLD 集成开发环境B .Altera 是世界上最⼤的可编程逻辑器件供应商之⼀C .MAX+plusII 是Altera 前⼀代FPGA/CPLD 集成开发环境QuartusII 的更新换代新产品D .QuartusII 完全⽀持VHDL 、Verilog 的设计流程2.以下⼯具中属于FPGA/CPLD 开发⼯具中的专⽤综合器的是 BA .ModelSimB .Leonardo SpectrumC .Active HDLD .QuartusII 3.以下器件中属于Xilinx 公司⽣产的是 CA .ispLSI 系列器件B .MAX 系列器件C .XC9500系列器件D .FLEX 系列器件 4.以下关于信号和变量的描述中错误的是 BA .信号是描述硬件系统的基本数据对象,它的性质类似于连接线B .信号的定义范围是结构体、进程C .除了没有⽅向说明以外,信号与实体的端⼝概念是⼀致的D .在进程中不能将变量列⼊敏感信号列表中 5.以下关于状态机的描述中正确的是 BA .Moore 型状态机其输出是当前状态和所有输⼊的函数B .与Moore 型状态机相⽐,Mealy 型的输出变化要领先⼀个时钟周期C .Mealy 型状态机其输出是当前状态的函数D .以上都不对6.下列标识符中, B 是不合法的标识符。

A .PP0B .ENDC .Not_AckD .sig7.⼤规模可编程器件主要有FPGA 、CPLD 两类,下列对CPLD 结构与⼯作原理的描述中,正确的是 C 。

A .CPLD 即是现场可编程逻辑器件的英⽂简称B .CPLD 是基于查找表结构的可编程逻辑器件C .早期的CPLD 是从GAL 的结构扩展⽽来D .在Altera 公司⽣产的器件中,FLEX10K 系列属CPLD 结构8.综合是EDA 设计流程的关键步骤,在下⾯对综合的描述中, D 是错误的。

EDA工具应用考核试卷

D.都是完全相同的功能

3.以下哪些软件是常用的EDA仿真工具?()

A. ModelSim

B. Multisim

C. PSpice

D. AutoCAD

4.以下哪些是FPGA芯片的特点?()

A.可编程逻辑资源

B.现场可编程

C.功耗低

D.成本较高

5.在电路设计中,以下哪些属于前端设计工具?()

20. ABC

三、填空题

1. Electronic Design Automation

2. module

3. VHDL、Verilog

4.后端

5.时序

6. Place

7. signal

8. MATLቤተ መጻሕፍቲ ባይዱB

9. Xilinx ISE

10. task

四、判断题

1. √

2. ×

3. √

4. ×

5. ×

6. √

B. Protel

C. ModelSim

D. MATLAB

13.以下哪个软件不是Altera公司推出的EDA工具?()

A. Quartus

B. ModelSim

C. Nios II

D. Xilinx ISE

14.在VHDL中,以下哪个关键字用于声明一个信号?()

A. signal

B. variable

3.在EDA工具中,用于电路原理图设计的软件是:()

A. CADENCE Orcad Capture

B. ModelSim

C. PowerPCB

D. MATLAB

4.下列哪种语言不是硬件描述语言?()

A. VHDL

B. Verilog

eda考试试题及答案

eda考试试题及答案一、单项选择题(每题2分,共10题,满分20分)1. EDA技术的核心是什么?A. 电子设计自动化B. 电子数据自动化C. 电子文档自动化D. 电子设备自动化答案:A2. 在EDA软件中,哪个工具用于设计电路原理图?A. PCB DesignerB. Schematic CaptureC. Layout EditorD. Simulation Tool答案:B3. 下列哪个不是EDA软件的功能?A. 电路仿真B. 电路设计C. 电路测试D. 电路制造答案:D4. 在EDA中,PCB布局设计的主要目的是什么?A. 提高电路性能B. 降低成本C. 减少电路板面积D. 以上都是答案:D5. 以下哪个不是数字电路仿真中常用的分析类型?A. 直流分析B. 交流分析C. 瞬态分析D. 热分析答案:D6. 在EDA软件中,哪个工具用于生成电路板的制造文件?A. Gerber ViewerB. Drill File GeneratorC. CAM ProcessorD.以上都是答案:D7. 以下哪个参数不是高速PCB设计中需要考虑的?A. 阻抗匹配B. 信号完整性C. 电源完整性D. 热传导率答案:D8. 在EDA软件中,哪个功能用于检查电路设计的电气规则?A. ERC(电气规则检查)B. DRC(设计规则检查)C. LVS(布局与原理图对比)D. 以上都是答案:A9. 在EDA中,哪个工具用于模拟电路的信号完整性?A. Signal Integrity AnalyzerB. Power Integrity AnalyzerC. Thermal Integrity AnalyzerD.以上都是答案:A10. 以下哪个不是EDA软件中用于优化布局的工具?A. AutorouterB. Constraint ManagerC. 3D ViewerD.以上都是答案:C二、多项选择题(每题3分,共5题,满分15分)1. EDA技术可以应用于以下哪些领域?A. 集成电路设计B. 印刷电路板设计C. 系统级设计D. 软件工程答案:A、B、C2. 在EDA软件中,以下哪些工具用于电路仿真?A. SPICE SimulatorB. Behavioral ModelerC. Timing AnalyzerD. Signal Integrity Simulator答案:A、B、D3. 在高速PCB设计中,以下哪些因素会影响信号完整性?A. 走线长度B. 走线宽度C. 走线间距D. 电源噪声答案:A、B、C、D4. 在EDA软件中,以下哪些工具用于PCB布局优化?A. AutorouterB. Constraint ManagerC. 3D ViewerD. Design Rule Checker答案:A、B、D5. 在EDA中,以下哪些是布局与原理图对比(LVS)的目的?A. 确保布局与原理图一致B. 检查电路的电气连接C. 优化电路性能D. 减少设计错误答案:A、B、D三、简答题(每题5分,共4题,满分20分)1. 简述EDA技术在现代电子设计中的重要性。

精编版-2018年广西桂林电子科技大学半导体物理考研真题A卷

2018年广西桂林电子科技大学半导体物理考研真题A卷请注意:答案必须写在答题册上(写在试题上无效)。

答题纸请注明页码与总页数。

一、解释什么是扩散运动。

(10分)

二、解释什么是PN结内建电场?(10分)

三、解释受主杂质的电离过程(10分)

四、解释N型半导体的简并化条件(10分)

五、解释基区宽度调变效应(10分)

六、作出正向偏压下PN结能带图,并简要说明形成过程(15分)

七、作出半导体、导体、金属的能带图并解释(15分)

八、(20分)已知突变结两边的杂质浓度为NA=1E16cm-3,ND=1E20cm-3,1)求势垒高度和势垒宽度;2)画出电场E(x),V(x)图。

eda考试题及答案

eda考试题及答案一、选择题(每题2分,共10分)1. EDA技术中的“E”代表什么?A. 电子B. 工程C. 教育D. 经济答案:B2. 在EDA软件中,以下哪个不是设计验证工具?A. 仿真器B. 综合器C. 验证器D. 测试器答案:B3. 以下哪个不是数字逻辑设计的基本元素?A. 与门B. 或门C. 非门D. 放大器答案:D4. 在EDA设计流程中,以下哪个步骤是用于优化设计的?A. 综合B. 布局C. 布线D. 时序分析答案:D5. 以下哪个不是EDA软件的功能?A. 电路图绘制B. 电路仿真C. 电路板设计D. 机械加工答案:D二、填空题(每题2分,共10分)1. EDA技术的核心是_______,它能够自动完成电路设计、验证和仿真等过程。

答案:电子设计自动化2. 在EDA设计中,_______是指在电路设计完成后,通过软件工具检查电路是否满足设计要求的过程。

答案:验证3. 电路设计的_______阶段是将电路的逻辑功能转换为可以在特定硬件上实现的物理形态。

答案:综合4. 在EDA软件中,_______是一种用于模拟电路行为的工具,它可以帮助设计者预测电路的实际工作情况。

答案:仿真器5. 电路设计的_______是指在电路板上合理布置电子元件和连接线路的过程。

答案:布局三、简答题(每题5分,共20分)1. 请简述EDA技术在现代电子设计中的重要性。

答案:EDA技术在现代电子设计中至关重要,它通过自动化的设计流程提高了设计效率,减少了人为错误,缩短了产品上市时间,并且能够处理复杂的电路设计问题,是现代电子设计不可或缺的工具。

2. 描述一下在EDA设计流程中,布局和布线阶段的主要任务。

答案:在EDA设计流程中,布局阶段的主要任务是将电路中的各个元件放置在电路板上的合适位置,以优化电路的性能和减少成本。

布线阶段则是在布局完成后,将各个元件通过导线连接起来,确保电路的电气连接正确无误,同时考虑信号完整性和电磁兼容性。

电子科技大学《EDA技术》20春期末考试

电子科技大学《EDA技术》20春期末考试

(单选题)1: 在VHDL的IEEE标准库中,预定义的标准逻辑位STD_LOGIC的数据类型中是用()表示的。

A: 小写字母和数字

B: 大写字母数字

C: 大或小写字母和数字

D: 全部是数字

正确答案: B

(单选题)2: 在VHDL中,IF语句中至少应有1个条件句,条件句必须由()表达式构成。

A: BIT

B: STD_LOGIC

C: BOOLEAN

D: INTEGER

正确答案: C

(单选题)3: “a=4’b1100,b=4’bx110”选出正确的运算结果()。

A: a&b=0

B: a&&b=1

C: b&a=x

D: b&&a=x

正确答案: B

(单选题)4: VHDL的字符是以( )括起来的数字、字母和符号。

A: 单引号

B: 双引号

C: 括号

D: 方括号

正确答案: A

(单选题)5: STD_LOGIG_1164中定义的高阻是字符()。

A: X

B: x

C: z

D: Z

正确答案: D

(单选题)6: 以下不属于EDA技术的特点是()。

A: 用软件方式设计硬件

B: 用硬件方式设计软件

C: 设计过程中可仿真

D: 系统可现场编程

正确答案: D

(单选题)7: 过程调用前需要将过程首和过程体装入()中。

电子科大19春《EDA技术》在线作业3

(单选题)1: 下面哪种语句不是并行语句A: wait语句B: process语句C: 块语句D: 生成语句正确答案:(单选题)2: VHDL程序基本结构包括A: 实体、子程序、配置B: 实体、结构体、配置、函数C: 结构体、状态机、程序包和库D: 实体、结构体、程序包和库正确答案:(单选题)3: 仿真是对电路设计的一种()检测方法。

A: 直接的B: 间接的C: 同步的D: 异步的正确答案:(单选题)4: 常用的硬件描述语言有A: VHDL、Verilog、c语言B: ABEL、c++C: VHDL、Verilog、ABELD: 汇编语言、ABEL、VHDL正确答案:(单选题)5: 在VHDL中,用语句( )表示检测clock的上升沿。

A: clock'EVENTB: clock'EVENT AND clock='1'C: Clok='0'D: clock'EVENT AND clock='0'正确答案:(单选题)6: VHDL常用的库是A: IEEEB: STDC: WORKD: PACKAGE正确答案:(单选题)7: 一般把EDA技术的发展分为CAD、CAE和()三个阶段。

A: CAMB: EDAC: CASED: CAN正确答案:(单选题)8: 根据VHDL语法规则,下面哪个标识符是非法的标识符A: not—AckB: constantC: FFT_1024_1D: state0正确答案:(单选题)9: VHDL常用的库是()标准库。

A: IEEEB: STDC: WORKD: PACKAGE正确答案:(单选题)10: 下列关于变量的说法正确的是A: 变量是一个局部量,它只能在进程和子程序中使用。

B: 变量的赋值不是立即发生的。

C: 在进程的敏感信号表中,既可以使用信号,也可以使用变量。

D: 变量赋值的一般表达式为:目标变量名<= 表达式。

EDA期末试卷

2010—2011学年第一学期期末考试试卷(闭卷)年级专业(本)课程名称 EDA技术基础教师出题时请勿超出边界虚线;2.学生答题前将密封线外的内容填写清楚, 答题不得超出密封线;3.答题请用蓝、黑钢笔或圆珠笔。

一、单项选择题(30分)1. 以下描述错误的是 CA. QuartusII是Altera提供的FPGA/CPLD集成开发环境B. Altera是世界上最大的可编程逻辑器件供应商之一C. MAX+plusII是Altera前一代FPGA/CPLD集成开发环境QuartusII的更新换代新产品D. QuartusII完全支持VHDL、Verilog的设计流程2. 以下工具中属于FPGA/CPLD开发工具中的专用综合器的是 BA. ModelSimB. Leonardo SpectrumC. Active HDLD. QuartusII3. 以下器件中属于Xilinx 公司生产的是 CA. ispLSI系列器件B. MAX系列器件C. XC9500系列器件D. FLEX系列器件4. 以下关于信号和变量的描述中错误的是 BA.信号是描述硬件系统的基本数据对象, 它的性质类似于连接线B. 信号的定义范围是结构体、进程//在整个结构体的任何地方都能使用C.除了没有方向说明以外, 信号与实体的端口概念是一致的D. 在进程中不能将变量列入敏感信号列表中5. 以下关于状态机的描述中正确的是 BA. Moore型状态机其输出是当前状态和所有输入的函数//Mealy型状态机其输出信号是当前状态和当前输入的函数B. 与Moore型状态机相比, Mealy型的输出变化要领先一个时钟周期C. Mealy型状态机其输出是当前状态的函数D. 以上都不对6. 下列标识符中, B 是不合法的标识符。

A. PP0B. ENDC. Not_AckD. sig7.大规模可编程器件主要有FPGA.CPLD两类, 下列对CPLD结构与工作原理的描述中, 正确的是C 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

桂林电子科技大学试题

2010-2011 学年第一学期

课程名称:电子设计自动化(A卷)适用班级:2008级本科

学号姓名机号

一、考试要求:1.本次考试为开卷上机考试,考试时间为120分钟。

考试完成后将试卷留于桌面上。

2.考生应严格按照各项题意要求作题,如在题意要求的路径下没有考生文件,将视为白卷。

3.画图过程中请注意及时存档,以免文件意外丢失!由于误操作引起的死机由考生自己负责。

二、考试内容:

1.(5分)在E:\盘下新建一文件夹F:\□□□□□□□□□□,其中□□□□□□□□□□为考生学号。

然后启动Protel 99并新建一设计项目文件test.DDB,存放于F:\□□□□□□□□□□\文件夹下。

2.(5分)在Documents文件夹中新建一原理图文件,将其命名为test1.SCH,同时将原理图幅面大小设置为650×550(自定义),按照所提供原理图进行编辑。

3.(10分)在Documents文件夹中新建原理图库文件,将其命名为test2.Lib,在原理图中T1和IC1是库中没有的,在test2.lib中做出T1和IC1两个元件,注意不要改动99se系统所带的库。

并把做好的库添加到做原理图的操作库中(注意IC1为分部分元件,分六部分,电源14、地脚7为引藏脚。

)

4.(10分)在原理图中所有电阻封装为AXIAL0.3, 电容为RAD0.2, 电解电容为RB.2/.4, 二极管为RB.2/.4, 三极管为TO-92A, IC1为DIP14, T1为GYB(需自己做封装),PLUG为PLUG(实验时所做)。

原理图完成后,利用整体修改将所有电阻封装改为AXIAL0.5,并将原理图另存为:test3.sch,

5.(10分)在Document文件夹下新建一元件封装库文件,并命名为test4.LIB。

参考提供图画T1的封装,并命名为GYB,其中焊盘直径为180mil;孔径大小为80mil。

.画出PLUG封装(PLUG的焊盘直径为160mil;孔径大小为70mil),其他线条按图中比例画出。

并将所做库添加到PCB的操作库中.

6.(5分)在Document文件夹下新建一PCB文件,命名为test5.pcb。

要求电路板大小为20cm*10cm的矩形。

同时将画好的封装库文件加载到PCB封装管理器中。

7.(5分)调用网络表,解决元件管脚丢失问题。

8.(5分)对元件进行布局。

要求元件排列以简洁整齐为主,交叉线尽量少为宜,接插件尽量放在板子边缘,方便安装。

9.(20分)按网络连接关系进行布线,电路板要求为双面走线,尽量走直线,减少拐角,避免走线绕大弯,必要时允许跳线存在。

安全间距应大于8mil;电源及地走线宽度应等于30mil;其他网络走线应等于20mil。

10.(10分) 将第9项中完成的test5.pcb另存为test6.pcb,在布好的电路板的底层进行大面积敷铜(敷铜接至VCC网络,安全间距为13mil的情况下)。

quartusII部分(40分)

1.在学号文件夹内新建quartusII文件夹

2.题目要求如下:

①新建一个以“kaoshi”命名的工程文件。

②定义器件型号为EPF10K10LC84-4。

③在工程文件下建立一个dfq的顶层实体文件,采用Verilog语言编写一个D触发器程序,要求如下:

A、输入信号为d,时钟触发信号为clk,输出信号为q(同相输出端)和nq(反相输出端)

B、触发器采用时钟下降沿进行触发

④在同一工程文件下建立一个comp的顶层实体文件,采用Verilog语言编写一个1位的数据比较器程序,要求如下:

A、输入信号为a和b(均为1位二进制数),输出信号为y

B、当a=b时,输出信号y=0,否则y=1

⑤在同一工程文件下建立一个文件名为“ylt”的顶层原理图文件,在原理图上放置以上所生成的D触发器和数据比较器,按

照下图进行连接。

⑥在原理图上放置输入端口[端口名为:code和clk],输出端口[(端口名为:a、b、c和y)],按照下图进行连接。

⑦建立一个文件名为“ylt”的仿真文件对原理图进行波形仿真,仿真结束时间为1秒,单位时间长度为10ms,输入时钟信号

clk为20ms周期的时钟,code为50ms周期的随机信号,所有引脚均采用二进制方式显示。

Mutisim部分(20分)

1.在学号文件夹内新建mutisim文件夹

仿真如下图电路,

测量三极管的静态工作点:

测量放大倍数。