跑马灯源程序及测试代码(verilog)

Verilog HDL 跑马灯电路

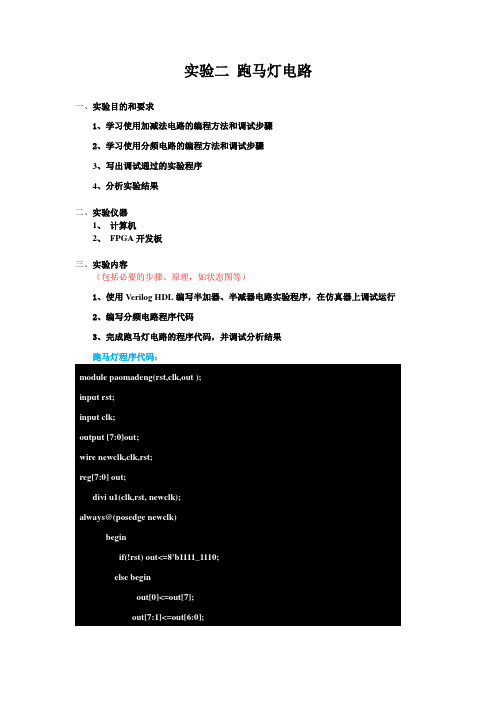

实验二跑马灯电路一、实验目的和要求1、学习使用加减法电路的编程方法和调试步骤2、学习使用分频电路的编程方法和调试步骤3、写出调试通过的实验程序4、分析实验结果二、实验仪器1、计算机2、FPGA开发板三、实验内容(包括必要的步骤、原理,如状态图等)1、使用Verilog HDL编写半加器、半减器电路实验程序,在仿真器上调试运行2、编写分频电路程序代码3、完成跑马灯电路的程序代码,并调试分析结果跑马灯程序代码:➢创建新的项目:[File]->[New Project] 选择器件属性➢创建源文件:[Project]->[New Source]->Verilog Module 输入跑马灯程序代码(上图所示)➢设计综合:使用ISE自带的综合工具XST 检查程序是否有误➢调试仿真波形仿真✓创建测试矢量波形文件:[Project]->[New Source]->Test Bench Waveform✓初始化输入波形✓启动ModelSim进行行为仿真➢设计实现✓启动设计实现:[Implement Design]✓可以在布局规划器(Floorplanner)中查看设计布局:[Place & Route]->[View/Edit Placed Design(Floorplanner)]➢下载调试将Verilog程序完成的电路配置到芯片里,并让芯片运行,观察并调试结果四、实验结果(说明实验的结果显示,最好包括波形和文字的)五、小结(对实验的心得,以及在试验中碰到的问题,你是如何解决这个问题的)➢ 进行软件仿真时要注意源程序代码的修改✓ if(count==25000000) 把数值设的小一点,比如令count=5,不然在短的时间内是看不到仿真效果的。

✓ if(!rst)begincount<=0;newclk<=0; end 在不能同时进行阻塞性赋值和非阻塞性赋值,不然程序会出现错误。

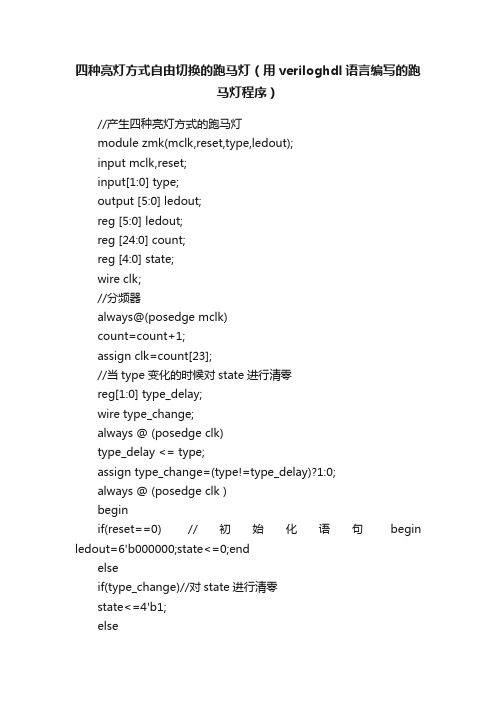

四种亮灯方式自由切换的跑马灯(用veriloghdl语言编写的跑马灯程序)

四种亮灯方式自由切换的跑马灯(用veriloghdl语言编写的跑马灯程序)//产生四种亮灯方式的跑马灯module zmk(mclk,reset,type,ledout);input mclk,reset;input[1:0] type;output [5:0] ledout;reg [5:0] ledout;reg [24:0] count;reg [4:0] state;wire clk;//分频器always@(posedge mclk)count=count+1;assign clk=count[23];//当type变化的时候对state进行清零reg[1:0] type_delay;wire type_change;always @ (posedge clk)type_delay <= type;assign type_change=(type!=type_delay)?1:0;always @ (posedge clk )beginif(reset==0) //初始化语句begin ledout=6'b000000;state<=0;endelseif(type_change)//对state进行清零state<=4'b1;elsebegincase(state)4'b0001:ledout=6'b011111;//第一个灯亮4'b0010:ledout=6'b101111;//第二个灯亮4'b0011:ledout=6'b110111;//第三个灯亮4'b0100:ledout=6'b111011;//第四个灯亮4'b0101:ledout=6'b111101;//第五个灯亮4'b0110:ledout=6'b111110;//第六个灯亮4'b0111:ledout=6'b111101;//第五个灯亮4'b1000:ledout=6'b111011;//第四个灯亮4'b1001:ledout=6'b110111;//第三个灯亮4'b1010:ledout=6'b101111;//第二个灯亮default :ledout=6'b000000;endcasestate=state+1; //计数器产生state的各种状态if(state==4'b1011)state=5'b00001;endelseif(type==2'b01)begincase(state)4'b0001:ledout=6'b101010;4'b0010:ledout=6'b010101;default :ledout=6'b000000;endcasestate=state+1;if(state==4'b0011)state=5'b00001;endelsebegincase(state)4'b0001:ledout=6'b110011;4'b0010:ledout=6'b101101;4'b0011:ledout=6'b011110;4'b0100:ledout=6'b101101; default :ledout=6'b000000; endcasestate=state+1;if(state==4'b0101)state=5'b00001; endelseif(type==2'b11)begincase(state)5'b00001:ledout=6'b111110;5'b00010:ledout=6'b111101;5'b00011:ledout=6'b111011;5'b00100:ledout=6'b110111;5'b00101:ledout=6'b101111;5'b00110:ledout=6'b011111;5'b00111:ledout=6'b001111;5'b01000:ledout=6'b010111;5'b01001:ledout=6'b011011;5'b01010:ledout=6'b011101;5'b01011:ledout=6'b011110;5'b01100:ledout=6'b011100;5'b01101:ledout=6'b011010;5'b01110:ledout=6'b010110;5'b01111:ledout=6'b001110;5'b10000:ledout=6'b000110;5'b10001:ledout=6'b001010;5'b10010:ledout=6'b001100;5'b10011:ledout=6'b001000;5'b10100:ledout=6'b000100;5'b10101:ledout=6'b001000;5'b10110:ledout=6'b000000;5'b10111:ledout=6'b111111;5'b11000:ledout=6'b000000;5'b11001:ledout=6'b111111;5'b11010:ledout=6'b000000;default :ledout=6'b000000;endcasestate=state+1;if(state==5'b11011)state=5'b00001; end endendmodule。

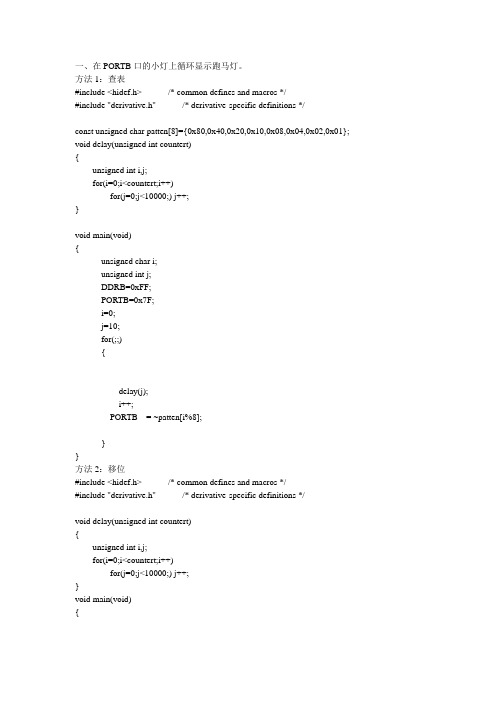

跑马灯实验代码

#include <hidef.h> /* common defines and macros */

#include "derivative.h" /* derivative-specific definitions */

PORTB=PORTA;

}

}

方法2:DIP开关低四位由A口低四位输入,经A口高四位送LED灯低四位输出

#include <hidef.h> /* common defines and macros */

#include "derivative.h" /* derivative-specific definitions */

for(j=0;j<10000;) j++;

}

void main(void)

{

unsigned char i,settime;

unsigned int j;

DDRB=0xFF;

PORTB=0x7F;

DDRA=0xF0;

flag=0;

asm ANDCC #$BF

EnableInterrupts;

i=0;

PORTB|=0x80;

if(PORTB==0xFF)

PORTB=0x7F;

}

}

void interrupt 6 IRQ(void)

{

flag=1;

}

**************************************************************************************************************************************************************

单片机 跑马灯实验

void hold(){

n=8;

while(1){

if(P2==K[4]){//一直按着K4键,逆序点亮跑马灯

oldK=K[4];

if(n==-1)n=7;//D0灯亮后点亮D7

while(n>=0){

out=D[n];

n--;

if(delay4(15))break;

}

}

if(P2==K[0]){//未按下K4键,一直正序点亮跑马灯

void hold(){

n=8;

while(1){

if(P2==K[4]){//一直按着K4键,逆序点亮跑马灯

oldK=K[4];

if(n==-1)n=7;//D0灯亮后点亮D7

while(n>=0){

out=D[n];

n--;

if(delay4(15))break;

}

}

if(P2==K[0]){//未按下K4键,一直正序点亮跑马灯

图43键控的流水灯

五、实验思考题

1、采用I/O口作为输出口时要考虑哪些因素?为什么实验装置中LED要串联一个电阻?

当作为输出口时候就是单片机向外发出数据,或者再产生拉电流,单片机的拉电流一般要比灌电流小,基本上就能点亮2,3个LED,功率很有限,所以一般时候必须用驱动芯片来驱动单片机的外围器件。串联电阻是为了保护电路。

while(1){//开机即正序点亮流水灯

forward();

if(P2!=K[0]){

break;

}

}

while(1){

out=AllOff;

if((P2&0x0f)!=0x0f){//检测有键按下

delay10ms();//延时10ms再去检测

FPGA入门系列实验教程——跑马灯

FPGA入门系列实验教程——LED跑马灯1.实验任务让实验板上的8个LED实现跑马灯的功能。

通过这个实验,进一步掌握采用计数与判断的方式来实现分频的Verilog HDL的编程方法以及移位运算符的使用。

2.实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208C8增强版开发套件。

软件实验环境为Quartus II8.1开发软件。

3.实验原理从LED[0]到LED[7]依次点亮,第二个灯点亮时第一个熄灭,每个灯交换的时间为0.5S;看上去的效果就象一个亮点从LED[0]跑向LED[7],然后重复此循环,故命名跑马灯。

初始状态时,LED[0]亮,其余熄灭。

每来一个时钟脉冲CLK,计数器就加1。

每当判断出计数器中的数值达到25000000时,就会点亮LED[1],同时LED[0]熄灭,并进行移位。

这样,依次点亮所有的灯,就形成了跑马灯。

而当LED[7]点亮时,需要一个操作使得恢复为初始状态,即:LED[0]亮,其余熄灭。

然后,再进行一次跑马灯,重复此循环。

如果是右移位,就出现向右跑马的现象;反之,向左跑马。

4.实验程序module ledwalk(led,clk);input clk;output[7:0]led;reg[7:0]led_out;reg[25:0]buffer;always@(posedge clk)beginbuffer<=buffer+1'b1;if(buffer==26'd2*******)beginled_out=led_out<<1;if(led_out==8'b00000000)led_out=8'b00000001;endendassign led=led_out;endmodule5.实验步骤(1)建立新工程项目:打开Quartus II软件,进入集成开发环境,点击File→New project wizard建立一个工程项目ledwalk。

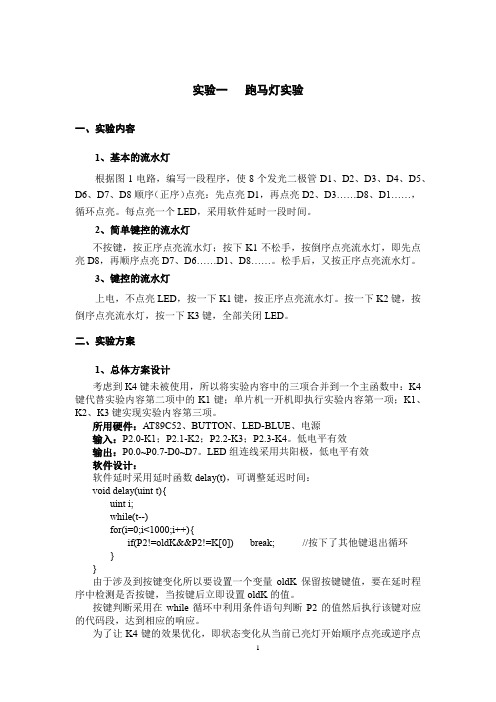

单片机内部结构测试报告-跑马灯

单片机内部结构测试报告姓名:苏汉生班别:09机械1班学号:0915020045指导老师:庞志目录1.跑马灯实验12.跑马灯实验23.跑马灯实验34.按键实验、蜂鸣器5.定时器数码管显示6.看门狗实验7.AD数模转换实验程序运行分析一、跑马灯实验11.测试程序名称:跑马灯实验12.程序功能介绍:跑马灯1的程序功能主要是控制LED灯闪亮的顺序,使八个LED灯按照程序设定闪亮。

但对按键和其他元件不起任何控制作用。

3.程序相关的电路图:8位流水灯电路4.程序总体(主函数)流程图:5(1)(3)1ms延时函数:(4)N ms掩饰函数:6.程序涉及的技术解析:unsigned charLED_table[]={0xFE,0x00,0xFF,0xFE,0xFD,0xFB,0xF7,0xEF,0xDF,0xBF ,0x7F,0xFF,0x00,0xFF,0x7F,0xBF,0xDF,0xEF,0xF7,0xFB,0xFD,0xFE,0 xFF,0x00,0xFF,0x7E,0xBD,0xDB,0xE7,0xFF,0x00,0xE7,0xDB,0xBD,0x7 E,0xFF,0x00};上述这个语句用到了一维数组,命名为LED_table,该数组一共有37个元素,每一个元素是一个十六进制的数,这些十六进制的数代表着开发板上的LED灯闪亮的规律(输出1为不亮,输出0为亮)。

PORTA = 0xFF;DDRA = 0xFF;DDRE=0XFF;PORTE=0XFF;上述语句是I/O口(端口A寄存器)的初始化,A口的8个脚控制开发板上的8个LED灯。

初始化A口设置为输出,8个引脚分别为1111 1111,LED等为全灭的状态。

单片机与LED灯之间连接了一个74HC573八进制3态非反转透明锁存器,E口2脚接在74HC573锁存器的使能端。

当锁存使能端为高电平1时,锁存对于数据是透明的(也就是说输出同步);当锁存使能端为低电平0时,符合建立时间和保持时间的数据会被锁存。

【Easy CPLD570】Verilog实现跑马灯

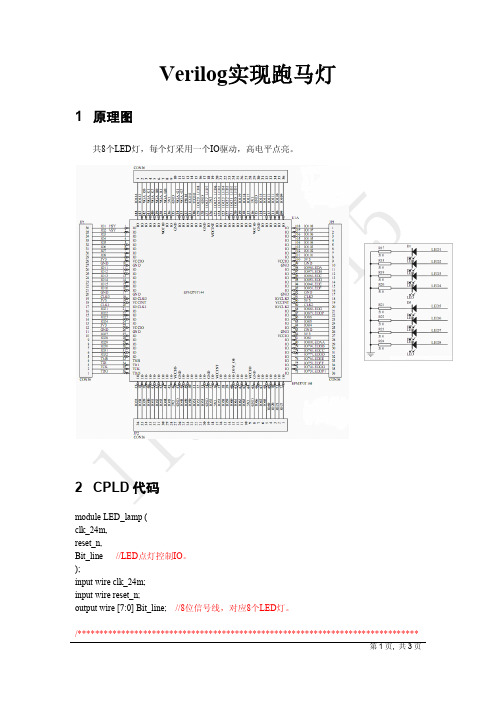

Verilog实现跑马灯1 原理图共8个LED灯,每个灯采用一个IO驱动,高电平点亮。

2 CPLD代码module LED_lamp (clk_24m,reset_n,Bit_line //LED点灯控制IO。

);input wire clk_24m;input wire reset_n;output wire [7:0] Bit_line; //8位信号线,对应8个LED灯。

/******************************************************************************24M时钟分频,用于内部控制及计数等。

******************************************************************************/ reg [16:0] count_div1;wire condition_183; //183 Hz时钟信号。

always @ (posedge clk_24m or negedge reset_n)beginif(reset_n == 1'b0)count_div1 <= 16'h00000;elsecount_div1 <= count_div1 + 16'h00001;end/****************************************************************************** condition_183:183Hz时钟信号,高电平持续一个24MHz时钟周期,其余时间为低电平。

******************************************************************************/ assign condition_183 = &count_div1[16:0]; //24MHz/2^17=183Hz。

跑马灯

#include <reg52.h>//此数组为LED 的段码, 共阴数码管0-9 在本电路中P0.0-P0.7unsigned char code show[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f};//LED的位选P2.4-P2.7unsigned char code w[]={~0x10,~0x20,~0x40,~0x80};//跑马灯的,对应每个灯亮unsigned char code deng[]={0xfe, 0xfd, 0xfb, 0xf7, 0xef, 0xdf,0xbf,0x7f};//函数声明void delay(unsigned int x);void init();void runled(int time);void keycheak();void dis();void delay1();//位定义sbit shift=P2^0;sbit ADD=P2^1;sbit DEC=P2^2;sbit mod=P2^3;sbit swit=P1^0;char change = 0;typedef struct digital_clock{char lowmin;char higmin;char lowhou;unsigned char highou;unsigned char current_bit;}clock;clock time_bit ={0,0,0,0,4}; //由于是顺序扫描,如果切换到调时间模式时最初一定显示在最高位,故赋值为4/************延时函数**********************/void delay1(unsigned int i) //延时{char j;for(i; i > 0; i--)for(j = 200; j > 0; j--);}void main(){init();while(1){runled(0);}}void init(){// P0=0xff; //p0口置1可以输入// P1=0x00; //p1口输出初始化为0// P2=0x0f; //p2口低四位输入,高四位输出置零// P3=0xff; //p3口输出置零TMOD= 0X10; //定时器1的工作方式1EA= 1; //开启总中断ET1= 1; //开启定时器1TH1= 0x3c; //高位赋初值TL1= 0xb0; //低位赋初值 3cb0是15535,则计时为(65535-15535=50000)us,即50msTR1= 1; //启动定时器 T1// TMOD=0x02;//设定计时器,门控位不使能,工作方式2// TH0=256-200; //200us进一次定时器中断// TL0=256-200;// EA=1;//开总中断// ET0=1;//开定时器中断0// TR0=1;//启动定时器中断0}void runled(int time){int i=0;P3=0xff;delay(1000);for(i=0;i<=7;i++){P3=deng[i];delay(1000);for(i=7;i>0;i--){P3=deng[i];delay(1000);}P3=0xe7;delay(1000);P3=0xdb;delay(1000);P3=0xbd;delay(1000);P3=0x7e;delay(1000);}void keycheak(){if(shift==0){delay(150);if(shift==0){time_bit.current_bit++;if(time_bit.current_bit>=5)time_bit.current_bit=1;P2=w[time_bit.current_bit-1];if(time_bit.current_bit==1)P3=show[time_bit.lowmin];if(time_bit.current_bit==2)P3=show[time_bit.higmin];if(time_bit.current_bit==3)P3=show[time_bit.lowhou];if(time_bit.current_bit==4)P3=show[time_bit.highou];delay(150);}if(ADD==0){delay(150);if(ADD==0){switch(time_bit.current_bit){case 1:time_bit.lowmin++; //分的低位小于10,高位小于6,小时的低位小于10,小时的高位小于3(当等于2时,小时的低位小于5)if(time_bit.lowmin>=10)time_bit.lowmin=0;P3=show[time_bit.lowmin]; //实时显示调整的值break;case 2:time_bit.higmin++;if(time_bit.higmin>=6)time_bit.higmin=0;P3=show[time_bit.higmin];break;case 3:time_bit.lowhou++;if(time_bit.highou==2&&time_bit.lowhou>=5)time_bit.lowhou=0;if(time_bit.highou!=2&&time_bit.lowhou>=10)time_bit.lowhou=0;P3=show[time_bit.lowhou];break;case 4:time_bit.highou++;if(time_bit.highou==2&&time_bit.lowhou>4)time_bit.lowhou=4;if(time_bit.highou>=3)time_bit.highou=0;P3=show[time_bit.highou];break;}delay(150);}}if(DEC==0){delay(150);if(DEC==0){switch(time_bit.current_bit){case 1:time_bit.lowmin--;if(time_bit.lowmin<0)time_bit.lowmin=9;P3=show[time_bit.lowmin]; //实时显示调整的值break;case 2:time_bit.higmin--;if(time_bit.higmin<0)time_bit.higmin=5;P3=show[time_bit.higmin];break;case 3:time_bit.lowhou--;if(time_bit.highou==2&&time_bit.lowhou<0)time_bit.lowhou=4;if(time_bit.highou!=2&&time_bit.lowhou<0)time_bit.lowhou=9;P3=show[time_bit.lowhou];break;case 4:time_bit.highou--;if(time_bit.highou<0)time_bit.highou=2;if(time_bit.highou==2&&time_bit.lowhou>4)time_bit.lowhou=4;P3=show[time_bit.highou];break;}delay(150);}}}void time0() interrupt 1{static long int count=0;dis();TH1= 0x3c;TL1= 0xb0;if(count++>=20){time_bit.lowmin++;if(time_bit.lowmin>=10){time_bit.lowmin=0;time_bit.higmin++;if(time_bit.higmin>=6){time_bit.higmin=0;time_bit.lowhou++;if((time_bit.highou!=2&&time_bit.lowhou>=10)||(time_bit.highou==2&&time_bit.lowhou> =4)){time_bit.lowhou=0;time_bit.highou++;if(time_bit.highou>=3)time_bit.highou=0;}}}count=0;}ET0=1;//开定时器中断0TR0=1;//启动定时器中断0}void delay(unsigned int x){int y;for(;x>0;x--)for(y=100;y>0;y--);}void dis(){P2 = 0xff;P0=0;P2=w[0];P0=show[time_bit.lowmin];delay1(150);P2 = 0xff;P0=0;P2=w[1];P0=show[time_bit.higmin];delay1(150);P2 = 0xff;P0=0;P2=w[2];P0=show[time_bit.lowhou]|0x80;delay1(150);P2 = 0xff;P0=0;P2=w[3];P0=show[time_bit.highou];delay1(150);}。

实验 5.2 跑马灯实验

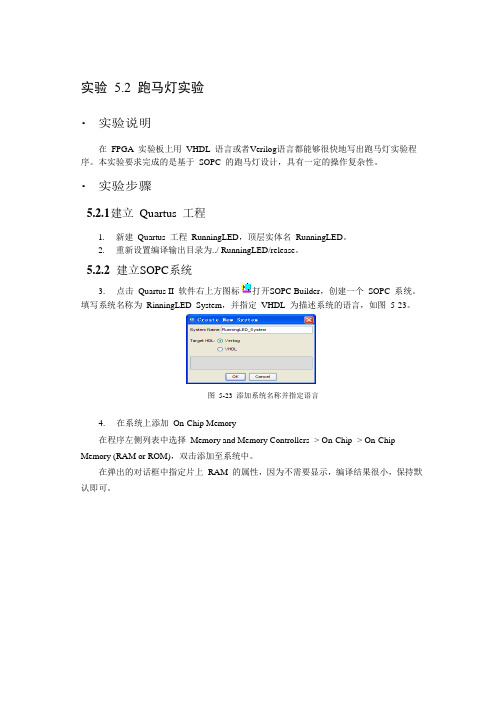

实验5.2 跑马灯实验·实验说明在FPGA 实验板上用VHDL 语言或者Verilog语言都能够很快地写出跑马灯实验程序。

本实验要求完成的是基于SOPC 的跑马灯设计,具有一定的操作复杂性。

·实验步骤5.2.1建立Quartus 工程1.新建Quartus 工程RunningLED,顶层实体名RunningLED。

2.重新设置编译输出目录为../ RunningLED/release。

5.2.2建立SOPC系统3.点击Quartus II 软件右上方图标打开SOPC Builder,创建一个SOPC 系统。

填写系统名称为RinningLED_System,并指定VHDL 为描述系统的语言,如图5-23。

图5-23 添加系统名称并指定语言4.在系统上添加On-Chip Memory在程序左侧列表中选择Memory and Memory Controllers -> On-Chip -> On-Chip Memory (RAM or ROM),双击添加至系统中。

在弹出的对话框中指定片上RAM 的属性,因为不需要显示,编译结果很小,保持默认即可。

图5-24 指定On-Chip Memory 属性鼠标移动到片内存储器的名称onchip_memonry2.0上并点击右键,在弹出菜单中选择Rename,然后更改名称为onchip_mem。

5.添加Nios II Processor双击Altera SOPC Builder -> Nios II Processor,在弹出的对话框中间选择处理器NIOS II/s;硬件乘法器(Hardware Multiply)选择None,即不需要硬件乘法器;复位向量和异常向量存储器(Memory)均选择前面刚刚添加的片内存储器onchip_mem,此时二者的偏移量(Offset)自动设置为0x0和ox20。

复位向量是指整个系统软件复位后启动的程序地址,一般为非易失存储器。

verilog HDL跑马灯报告

跑马灯设计一、实验目的:1.熟悉利用QuartusII开发数字电路的基本流程和QuartusII软件的相关操作;2.掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,利用JTAG/AS进行下载的基本操作;3.了解VerilogHDL语言设计或原理图色剂方法。

二、设计内容使LED成流水的方式,在不同的状态中间进行转换,本设计中主要是让LED显示灯按照一定时间间断来显示,通过这样的间隔来使LED按流水方式显示并循环。

三、实验用到的软件和器材软件:QuartusII软件硬件:实验开发板,计算机四、实验步骤1. 创建工程,选择目标芯片,设置合适的参数,编写设计程序并编译。

源程序如下:module led#(parameter max_length=8)(input clk,rst,output reg[max_length-1:0]led_out);always@(posedge clk,posedge rst)if(rst)led_out<={max_length{1'b0}};elseif(led_out=={max_length{1'b1}})led_out<={max_length{1'b0}};elseled_out<={1'b1,led_out[max_length-1:1]};endmodule2. 编译无误后进行时序仿真,仿真无误后管脚锁定。

管脚锁定图如下:3 .将程序下载至EP1C6+EPCS1 试验箱,观察实验结果。

实验箱上LED灯按照一定的时间间隔顺次点亮,按流水方式显示并循环。