CMOS静态门电路

cmos门电路

CMOS反相器MOSFET有P沟道和N沟道两种,每种中又可分为耗尽型和增强型两类。

由N沟道和P沟道MOSFET组成的电路称为互补MOS或CMOS电路。

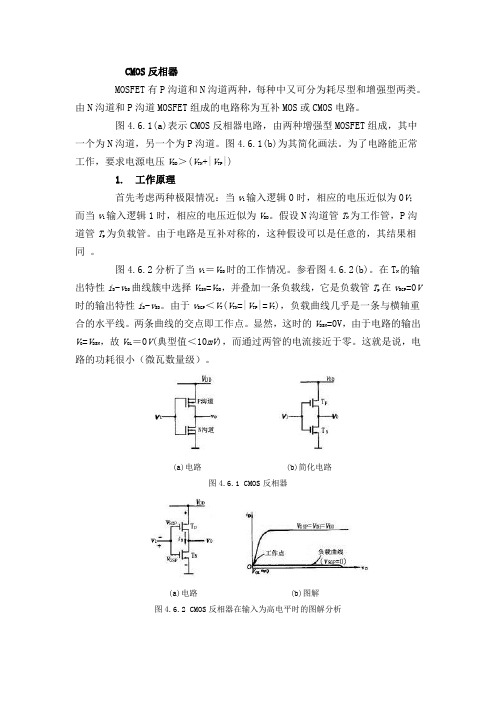

图4.6.1(a)表示CMOS反相器电路,由两种增强型MOSFET组成,其中一个为N沟道,另一个为P沟道。

图4.6.1(b)为其简化画法。

为了电路能正常工作,要求电源电压V DD>(V TN+|V TP|)1. 工作原理首先考虑两种极限情况:当v1输入逻辑0时,相应的电压近似为0V;而当v输入逻辑1时,相应的电压近似为V DD。

假设N沟道管T N为工作管,P沟道管1T为负载管。

由于电路是互补对称的,这种假设可以是任意的,其结果相同。

p图4.6.2分析了当v1=V DD时的工作情况。

参看图4.6.2(b)。

在T N的输出特性i D-v DS曲线簇中选择V GSN=V DD,并叠加一条负载线,它是负载管T p在v SGP=0V时的输出特性i D-v SD。

由于v SGP<V T(V TN=|V TP|=V T),负载曲线几乎是一条与横轴重合的水平线。

两条曲线的交点即工作点。

显然,这时的V DSN=0V,由于电路的输出V O=V DSN,故V OL=0V(典型值<10mV),而通过两管的电流接近于零。

这就是说,电路的功耗很小(微瓦数量级)。

(a)电路(b)简化电路图4.6.1 CMOS反相器(a)电路(b)图解图4.6.2 CMOS反相器在输入为高电平时的图解分析图4.6.3分析了另一种极限情况,此时对应于v I=0V,其工作状态示于图4.6.3(b)中。

此时工作管T N在v GSN=0的情况下运用,其输出特性i D-v DS几乎与横轴重合,负载曲线是负载管T p在v GSP=V DD时的输出特性i D-v DS。

由图可知,工作点决定了V OH≈V DD;通过两器件的电流接近于零值。

可见上述两种极限情况下的功耗都很低。

(a)电路(b)图解图4.6.3 CMOS反相器在输入为低电平时的图解分析由此可知,基本CMOS反相器近似于理想的逻辑单元,其输出电压接近于零,而功耗几乎为零。

CMOS门电路的输出端来说

二❖、低C电M平O输S反出特相性器的静态输入输出特性

IOL:低电平时向内灌入的电流。 随VDD升高,IOL允许值上升。

二❖、高C电M平O输S反出特相性器的静态输入输出特性

IOH:高电平时向外拉的电流。 随VDD升高,IOH允许值上升。

三❖、传C输M延O迟S反时间相器的动态特性

三❖、交C流M噪O声S反容限相器的动态特性

噪声持续时间越 短,噪声容限越

大。

三❖、动C态M功O耗S反-瞬相时器导的通动功态耗P特T 性

T1、T2 同时通

PT=VDDITAV

三❖、动C态M功O耗S反-负相载器电的容动充态放电特功性率PC

PC CL f VDD PS

四、其它类型的CMOS门电路

分布式 二极管

若VDF=0.7V,则vI>VDD+0.7V时,vG=VDD+0.7V vI<-0.7V时,vG=-0.7V。使vC1、vC2均不超过VDD+0.7V。

二❖、输C入M特O性S反相器的静态输入输出特性

D1通

D2通

输入端的绝缘层使电路输入阻抗极高,若有静电感应则会在悬 空端产生不定电位,故CMOS门电路输入端不允许悬空。

②当C的高低电平为VDD和0时,TG可传输0~VDD的信号 ③vO和vI可以互换。

四❖、C其MO它S传类输型门的和CCMMOOSS反门相电器路构成的双向模拟开关

C=0,开关关闭;C=1时,开关接通。 一种常用的典型电路。 SW:Switch

返回

四❖、C其MO它S模类拟型开的关C接M负O载S门电路

四 、三其态它输类出的型C的MCOSM门O电S路门(电3) 路

CMOS门电路输入特性习题(P123 (四)) CMOS门电路输入端接电阻时,相当于接低电平。

CMOS门电路

2.1.4 CMOS门电路的电气特性

CD4000 系列门电路的极限参数( VDD=5V) ◆ 输出高电平电压VOH ,VOH(min)= VDD-0.1V

◆ ◆ ◆

◆

输出低电平电压VOL ,VOL(max)= 0.1V 输入高电平电压VIH ,VIH(min)= 70%VDD 输入低电平电压VIL,VIL(max)= 30%VDD 阈值电压VTH=1/2VDD

PMOS

漏极相连 做输出端 NMOS

柵极相连 做输入端

2.1.2 CMOS反相器

2. CMOS反相器的工作原理

(1)当vI=0V时,vGSN=0V,VTN 截 止 , ∣ vGSP∣=VDD , VTP 导 通 , vO≈VDD,门电路输出输出高电平;

VDD

VTP vI VTN vO

( 2 ) 当 vI=VDD 时 , VGSN=VDD , VTN导通,∣VGSP∣=0V,VTP截止 ,vO≈0V,门电路输出低电平。

问题的提出

异或门的逻辑功能:

A B =1 F

输入相同,输出为“0”

输入不同,输出为“1”

F=AB

内部电路是什么样的,如何实现相应的逻辑功能?

门电路有哪些参数?如何正确使用?

本章的教学目标

■ 理解CMOS门电路结构与工作原理 ■ 掌握CMOS门电路外特性,正确使用CMOS门电路

■ 理解TTL门电路结构与工作原理 ■ 掌握TTL门电路外特性,正确使用TTL门电路

(2)由动态尖峰电流产生的瞬时动态功耗

VDD VTP iD vI vO vO

0 iD

t

VTN

0

t

PT CP DVD2D f

(3)总的动态功耗

2 PD PC PT C L C PD)VDD f (

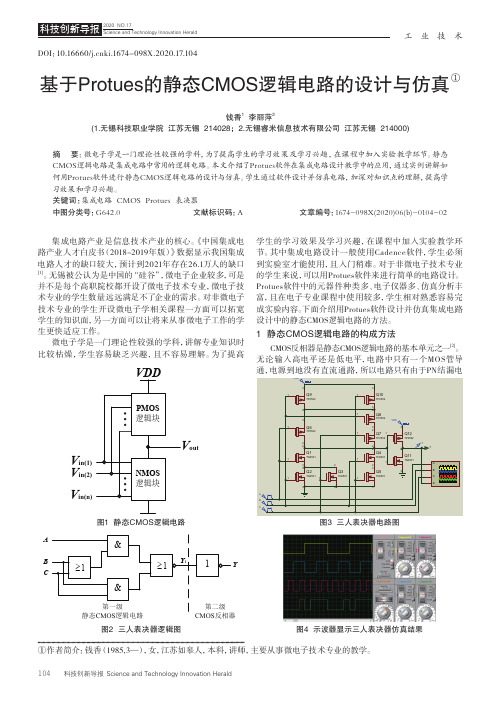

基于Protues的静态CMOS逻辑电路的设计与仿真

工业技术科技创新导报 Science and Technology Innovation Herald104DOI:10.16660/ki.1674-098X.2020.17.104基于Protues的静态CMOS逻辑电路的设计与仿真①钱香1 李丽萍2(1.无锡科技职业学院 江苏无锡 214028;2.无锡睿米信息技术有限公司 江苏无锡 214000)摘 要:微电子学是一门理论性较强的学科,为了提高学生的学习效果及学习兴趣,在课程中加入实验教学环节。

静态CMOS逻辑电路是集成电路中常用的逻辑电路。

本文介绍了Protues软件在集成电路设计教学中的应用,通过实例讲解如何用Protues软件进行静态CMOS逻辑电路的设计与仿真。

学生通过软件设计并仿真电路,加深对知识点的理解,提高学习效果和学习兴趣。

关键词:集成电路 CMOS Protues 表决器中图分类号:G642.0 文献标识码:A 文章编号:1674-098X(2020)06(b)-0104-02①作者简介:钱香(1985,3—),女,江苏如皋人,本科,讲师,主要从事微电子技术专业的教学。

集成电路产业是信息技术产业的核心。

《中国集成电路产业人才白皮书(2018-2019年版)》数据显示我国集成电路人才的缺口较大,预计到2021年存在26.1万人的缺口[1]。

无锡被公认为是中国的“硅谷”,微电子企业较多,可是并不是每个高职院校都开设了微电子技术专业,微电子技术专业的学生数量远远满足不了企业的需求。

对非微电子技术专业的学生开设微电子学相关课程一方面可以拓宽学生的知识面,另一方面可以让将来从事微电子工作的学生更快适应工作。

微电子学是一门理论性较强的学科,讲解专业知识时比较枯燥,学生容易缺乏兴趣,且不容易理解。

为了提高学生的学习效果及学习兴趣,在课程中加入实验教学环节。

其中集成电路设计一般使用Cadence软件,学生必须到实验室才能使用,且入门稍难。

5CMOS电路的电气特性和参数

LVC是低压CMOS逻辑系列的简称。工作电源电压为 (1.65~3.6V);当VDD=5V时,tpd=3.8ns;输出高、低电平 时的最大负载电流达24mA。 ALVC系列是改进的LVC逻辑系列的简称。性能更加优越。 在诸多系列的CMOS电路产品中,只要产品型号最后的数 字相同,则它们的逻辑功能就是一样的;但它们的电气性能和 参数就各不相同了。 型号开头的“74”或“54”是TI公司产品的标志。 74——民用产品,工作环境温度为-40~850C 54 ——军用产品,工作环境温度为-55~1250C

3.2.4 CMOS电路的静电防护和锁定效应

1. 静电防护

为了防止静电击穿,在CMOS集成电路的每个输入端 都设置了输入保护电路。

2. 锁定效应 当CMOS电路的输入端或输出端出现 瞬时高压时,有可能使电路进入这样一种 状态,即电源至电路公共端之间有很大的 电流流过,输入端也失去了控制作用。

通过改进制造工艺,已经可以做到一 般情况下不会发生,但还不能绝对避免。

L 充、

放电产生的功耗 ;P

T:

瞬变功耗)

2 (C L C pd )VDD f

3. 各种系列CMOS数字集成电路的性能比较 4000系列:工作电压范围比较宽(3~18V),但存在着传 输延迟时间长(60~100ns)、负载能力弱的缺点。 HC/HCT系列是高速CMOS逻辑系列的简称。当VDD=5V时, tpd=10ns;输出高、低电平时的最大负载电流达4mA。 HC系列和HCT系列的区别在于:HC系列的工作电压范围 较宽(2~6V),但它的输入、输出电平和负载能力不能和TTL 电路兼容,适用于单纯由CMOS器件组成的系统中。而HCT系 列一般仅工作在5V电源电压下,在输入、输出电平和负载能力 上均可与TTL电路兼容,适用于由CMOS与TTL混合的系统中。 AHC/AHCT系列是改进的高速CMOS逻辑系列的简称。当 VDD=5V时,tpd=3ns左右;输出高、低电平时的最大负载电流 达8mA。

典型的cmos与非门电路使用的电路

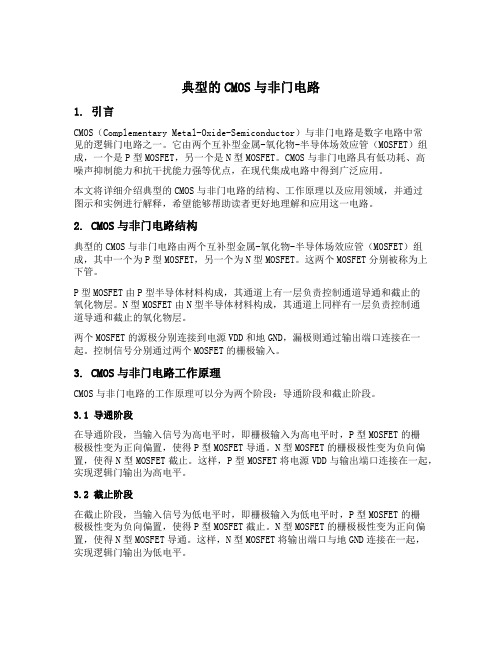

典型的CMOS与非门电路1. 引言CMOS(Complementary Metal-Oxide-Semiconductor)与非门电路是数字电路中常见的逻辑门电路之一。

它由两个互补型金属-氧化物-半导体场效应管(MOSFET)组成,一个是P型MOSFET,另一个是N型MOSFET。

CMOS与非门电路具有低功耗、高噪声抑制能力和抗干扰能力强等优点,在现代集成电路中得到广泛应用。

本文将详细介绍典型的CMOS与非门电路的结构、工作原理以及应用领域,并通过图示和实例进行解释,希望能够帮助读者更好地理解和应用这一电路。

2. CMOS与非门电路结构典型的CMOS与非门电路由两个互补型金属-氧化物-半导体场效应管(MOSFET)组成,其中一个为P型MOSFET,另一个为N型MOSFET。

这两个MOSFET分别被称为上下管。

P型MOSFET由P型半导体材料构成,其通道上有一层负责控制通道导通和截止的氧化物层。

N型MOSFET由N型半导体材料构成,其通道上同样有一层负责控制通道导通和截止的氧化物层。

两个MOSFET的源极分别连接到电源VDD和地GND,漏极则通过输出端口连接在一起。

控制信号分别通过两个MOSFET的栅极输入。

3. CMOS与非门电路工作原理CMOS与非门电路的工作原理可以分为两个阶段:导通阶段和截止阶段。

3.1 导通阶段在导通阶段,当输入信号为高电平时,即栅极输入为高电平时,P型MOSFET的栅极极性变为正向偏置,使得P型MOSFET导通。

N型MOSFET的栅极极性变为负向偏置,使得N型MOSFET截止。

这样,P型MOSFET将电源VDD与输出端口连接在一起,实现逻辑门输出为高电平。

3.2 截止阶段在截止阶段,当输入信号为低电平时,即栅极输入为低电平时,P型MOSFET的栅极极性变为负向偏置,使得P型MOSFET截止。

N型MOSFET的栅极极性变为正向偏置,使得N型MOSFET导通。

这样,N型MOSFET将输出端口与地GND连接在一起,实现逻辑门输出为低电平。

基于Cadence的静态CMOS门电路仿真设计

科学技术创新2019.24基于Cadence 的静态CMOS 门电路仿真设计王文彬杨定坤罗坤欧阳林(成都信息工程大学通信工程(微电子)学院,四川成都610103)1Cadence ADE 简介ADE (Analog Design Environment )是美国Cadence 公司开发的集成电路设计自动化仿真软件,其功能强大,仿真功能多样,包含直流仿真(DC Analysis )、瞬态仿真(Transient Analysis )、交流小信号仿真(AC Analysis )、零极点分析(PZ Analysis )、噪声分析(Noise )、蒙特卡罗分析(Monte Carlo )、周期性稳定分析(Periodic Steady-state Analysis )等,并可对设计仿真结果进行成品率分析和优化,大大提高了复杂集成电路的设计效率。

此外Cadence 公司还和多家半导体晶圆厂家建立了仿真工艺库文件PDK (Process Design Kit ),方便设计者选择PDK 进行设计与仿真,而本文采用的工艺为TSMC 0.18um [1]。

2静态CMOS 电路设计静态互补CMOS 门级电路是使用最广泛的逻辑门的类型,因其具有良好的稳定性、良好的性能以及低功耗等特点而在集成电路的设计中被广泛使用。

静态互补CMOS 门级电路是由上拉网络(PUN )和下拉网络(PDN )的组合而成的,其结构如图1所示。

在静态互补CMOS 门电路设计当中,一般先根据需要待实现的逻辑运算式设计出下拉网络,然后再根据下拉网络的逻辑结构作出上拉网络,具体实施方式即是将下拉网络中MOS 管的串并联方式以及MOS 管的N/P 属性互换后得到新的网络,即是上拉网络。

而在运算方面,对于NMOS 管来说,串联即是做乘法运算,并联即是做加法运算,PMOS 管反之[2]。

图1二输入互补逻辑门结构3静态CMOS 反相器静态互补CMOS 组合逻辑门实际上就是把静态CMOS 反相器扩展为具有多个输入的逻辑门而形成的,故在此处先作反相器的讨论。

8.3CMOS静态门电路的功耗

降低开关活动性举例

减少毛刺和竞争冒险

设计时,使各支路的延时尽可能平衡

2020/2/10

2020/2/10

CMOS静态逻辑门的小结

MOS反相器的静态特性

逻辑门的输入输出电平 逻辑门的噪声容限 逻辑门的逻辑阈值

MOS反相器的动态特性

逻辑门的开关特性 逻辑门的功耗

2020/2/10

2020/2/10

降低待机功耗的方法举例:

• 正常工作时采用低阈 值电压,以减少CMOS

电路的延迟时间ຫໍສະໝຸດ • 待机时采用高阈值 电压,以减少CMOS

电路的泄漏电流

保持速度性能的基础上, 大幅度降低功耗

2020/2/10

高Vt 低Vt

VDD

SL

电路工作时 导通,待机

时截止

低阈值逻辑电路

2020/2/10

2020/2/10

对于深亚微米器件,存在泄漏电流Ileakage VDD Ileakage

Vout

Ipn=A•JS

漏极扩散结漏电流

栅极漏电流

亚阈值漏电流

由越过沟道区的少数载流子扩 散电流引起的

随着特征尺寸的减小,泄漏电流功耗变得不可忽视, 减小泄漏电流功耗是目前的研究热点之一。

2020/2/10

反向偏置二极管漏电流

CMOS静态逻辑门的小结

复合CMOS逻辑门的构成 P网 N网

❖ NMOS、PMOS互补: (并联《====》串联) NMOS 输出为“0” PMOS 输出为“1” ❖ 生成电路为负逻辑: 组成AND和OR时, 加一反向器。

❖ 晶体管数为: 输入端 子数的两倍。

2020/2/10

作业:

名词解释:静态功耗,动态功耗 简述CMOS反相器功耗的构成。

常用CMOS门电路.

(5)因CMOS集成电路的功耗小,其内部发热量小,所以CMOS电路的集成度 要比TTL电路高。 (6)CMOS集成电路的温度稳定性好,抗辐射能力强,适合于特殊环境下工作。 (7)由于CMOS电路的输入阻抗高,使其容易受静电感应而击穿,所以在其内部 一般都设置了保护电路。

数字逻辑电路

常用CMOS门电路

图1 CMOS开关电路

图2 CMOS三态双向传输电路

图2为COMS三态门双向传输控制电路。当 CMOS三态门G1或G2的控制端为高电平时, 该门起传输作用,否则呈高阻状态。即当C =1时,三态门G1接通,三态门G2处于高阻 状态,信号D送至Q;当C = 0时,三态门 G2接通,三态门G1处于高阻状态,信号Q 送至D。某些集成电路就具有这种三态双向 传输控制的功能,在计算机的接口技术中被 广泛使用。

CMOS数字电路的特点有: (1)由于CMOS管的导通内阻比双极型晶体管导通内阻大,所以CMOS电路的工 作速度比TTL电路的工作速度低。

(2)CMOS电路的输入阻抗很高,可达10MΩ以上,在频率不高的情况下,电 路可以驱动的CMOS电路多于TTL电路。

(3)允许CMOS电路的电源电压的变化范围较大,约在5~15V之间,所以其输 出高、低电平的摆幅较大。与TTL电路相比,该电路的抗干扰能力更强,噪音容限 可达30%VDD(VDD为电源电压)。

CMOS 门电路

图2-26

CMOS反相器 LOGO

9

(3)逻辑功能 实现反相器功能(非逻辑)。 (4)工作特点 VTP和VTN总是一管导通而另一管截止,流过 VTP和VTN的静态电流极小(纳安数量级),因而 CMOS反相器的静态功耗极小。这是CMOS电路最突 出的优点之一。

10

LOGO

3. 电压传输特性和电流传输特性 BC段:转折区 阈值电压UTH≈VDD/2 转折区中点:电流最大

截止

图2-24 NMOS管的电路符号及转移特性 (a) 电路符号 (b)转移特性

5

LOGO

(2)PMOS管的开关特性

D接负电源

导通

截止

图2-25 PMOS管的电路符号及转移特性 (a) 电路符号 (b)转移特性

导通电阻相当小

6

LOGO

2.CMOS反相器的工作原理

(1)基本电路结构

PMOS管 负载管 NMOS管 驱动管

3

LOGO

2.5.1

CMOS反相器

MOS管有NMOS管和PMOS管两种。

当NMOS管和PMOS管成对出现在电路中,且二

者在工作中互补,称为CMOS管(意为互补)。 MOS管有增强型和耗尽型两种。 在数字电路中,多采用增强型。 1.MOS管的开关特性

4

LOGO

(1)NMOS管的开关特性

D接正电源 导通电阻相当小 导通

而TTL电路的电源电压只能为5V。 ③ 采用TTL的OC门实现电平转换。 若电源电压不一致时也可选用OC门实现电平转换。

27

LOGO

2. CMOS门驱动TTL门

(1)电平匹配 CMOS门电路作为驱动门,UOH≈5V,UOL≈0V; TTL门电路作为负载门,UIH≥2.0V,UIL≤0.8V。 电平匹配是符合要求的。 (2)电流不匹配 CMOS门电路4000系列最大允许灌电流为0.4mA,

CMOS门电路工作原理介绍课件

工作台台面等良好接地。

操作人员的服装和手套等应选用无静电的原料制作。

3)不用的输入端不应悬空。

学习交流PPT

上页 下页 返回

26

2. 输入电路的过流保护

由于输入保护电路中的钳位二极管电流容量有限, 所以在可能出现较大输入电流的场合, 必须采取以下保护措施: 1)输入端接低内阻信号源时, 应在输入端与信号源之间串进保护电阻, 保证输入保护电路中的二极管导通时电流不超过1mA。 2)输入端接有大电容时, 应在输入端和电容之间接入保护电阻。

DO / DI

D I

G2

线

学习交流PPT

上页 下页 返回

25

五、CMOS电路的正确使用

1. 输入电路的静电防护 为防止静电电压造成的损坏,应注意以下几点:

1)在存储和运输CMOS器件时,

不要使用易产生静电高压的化工材料和化纤织物包装,

最好采用金属屏蔽层作包装材料。

2)组装、调试时,应使电烙铁和其他工具、仪表、

传输门的另一个用途是作模拟开关,用来传输连续 变化的模拟电压信号。

C

vI / vO

TG v O / v I

C

vI / vO

SW v O / v I

C

vI

SW v O

RL

模拟开关的导通内阻为RTG。 C=0时开关截止。

C=1时开关接通。

vO

RL

RL RTG

vI

学习交流PPT

上页 下页 返回

23

5. 三态输出的 CMOS门电路

学习交流PPT

上页 下页 返回

18

3. 漏极开路的门电路(OD门)

VDD1

CC40107

VDD2

第五章(4) 静态CMOS逻辑电路.ppt

CMOS传输门导通电流的变化

传输高电平和传输低电平过程中,NMOS传输管、PMOS传输管以及 CMOS传输门导通电流的变化。

NMOS管和PMOS管的电流都是非线性变化,而CMOS传输门的总电流近 似线性变化。

CMOS传输门直流电压传输特性

CMOS传输门导通电阻的变化

传输门总结

★ NMOS传输管传输低电平性能好,传输高电平有阈值 损失; ★ PMOS传输管传输高电平性能好,传输低电平有阈值 损失; ★ CMOS传输门利用NMOS和PMOS管的互补性能获得 了比单个传输管更优越的性能,性能更接近理想开关。

)

,

Kr

KN KP

8

结论

输出低电平的值不为0,取决于比例因子 Kr;

增大 Kr可使VOL 尽可能小,且电路功耗也会减小;

但K

太小将使电路的上升时间增加;

P

比例因子Kr过大会导致上升时间的增加;

输出低电平时存在静态功耗;

PDC KP (VDD VTP )2 VDD

9

类NMOS电路优缺点

五、MOS传输门逻辑电路

四、类NMOS电路

静态CMOS逻辑门利用NMOS管和PMOS管的 互补特性,使上拉通路和下拉通路轮流导通,从而 获得很好的电路性能。

缺点:每个输入都包含NMOS和PMOS管,不 利于减小芯片面积和提高集成度。

因此,对某些性能要求不太高,但希望面积尽可 能小的电路,可以采用类NMOS电路形式。

有比逻辑 (Ratioed Logic)

Vout VTP : PMOS管工作在线性区;

IDD KP[(VG VS VTP )2 (VG VD VTP )2 ] = KP[(VDD VTP )2 (Vout VTP )2 ] 0

cmos逻辑门电路[最新]

![cmos逻辑门电路[最新]](https://img.taocdn.com/s3/m/6cf0544676232f60ddccda38376baf1ffc4fe3e0.png)

CMOS逻辑门电路CMOS是互补对称MOS电路的简称(Complementary Metal-Oxide-Semiconductor),其电路结构都采用增强型PMOS管和增强型NMOS管按互补对称形式连接而成,由于CMOS 集成电路具有功耗低、工作电流电压范围宽、抗干扰能力强、输入阻抗高、扇出系数大、集成度高,成本低等一系列优点,其应用领域十分广泛,尤其在大规模集成电路中更显示出它的优越性,是目前得到广泛应用的器件。

一、CMOS反相器CMOS反相器是CMOS集成电路最基本的逻辑元件之一,其电路如图11-36所示,它是由一个增强型NMOS管T N和一个PMOS管T P按互补对称形式连接而成。

两管的栅极相连作为反相器的输入端,漏极相连作为输出端,T P管的衬底和源极相连接电源U DD,T N管的衬底与源极相连后接地,一般地U DD>(U TN+|U TP|),(U TN和|U TP|是T N和T P的开启电压)。

当输入电压u i=“0”(低电平)时,NMOS管T N截止,而PMOS管T P导通,这时T N 管的阻抗比T P管的阻抗高的多,(两阻抗比值可高达106以上),电源电压主要降在T N上,输出电压为“1”(约为U DD)。

当输入电压u i=“1”(高电平)时,T N导通,T P截止,电源电压主要降在T P上,输出u o=“0”,可见此电路实现了逻辑“非”功能。

通过CMOS反相器电路原理分析,可发现CMOS门电路相比NMOS、PMOS门电路具有如下优点:①无论输入是高电平还是低电平,T N和T P两管中总是一个管子截止,另一个导通,流过电源的电流仅是截止管的沟道泄漏电流,因此,静态功耗很小。

②两管总是一个管子充分导通,这使得输出端的等效电容C L能通过低阻抗充放电,改善了输出波形,同时提高了工作速度。

③由于输出低电平约为0V,输出高电平为U DD,因此,输出的逻辑幅度大。

CMOS反相器的电压传输特性如图11-37所示。

第三章(1)门电路---CMOS

输入低电平的上限值 VIL(max)

输入高电平的下限值 VIH(min)

输出高电平的下限值 VOH(min)

输出低电平的上限值 VOL(max)

3.1.2 逻辑门电路的一般特性

2.噪声容限:在保证输出电平不 变的条件下,输入电平允许波动 的范围。它表示门电路的抗干扰

驱动门

01 1

数据输入端

EN A B

其他三态与非门: A

&

逻辑符号 B

低电平有效

2.产生的高、低电平半导体器件

iC

VCC Rc

Rb vI

VCC Rc

vo

vCE VCC

工作在饱和区:输出低电平 工作在截止区:输出高电平

3.1.3 MOS开关及其等效电路

场效应三极管

利用电场效应来控制电流的三极管,称为场效应管,也 称单极型三极管。

由金属、氧化物和半导体制成。称为金属 -氧化物-半导体场 效应管,或简称 MOS 场效应管。

2、 逻辑门电路的分类 分立门电路

逻辑门电路 集成门电路

二极管门电路 三极管门电路

MOS门电路

TTL门电路

NMOS 门 PMOS门 CMOS门

TTL系列门

开关速度较快 平均延迟时间:3~10ns 结构复杂、集成度低 功耗高(2~20mw )

MOS门

开关速度稍低

平均延迟时间:75ns 结构和制造工艺简单 容易实现高密度制作 功耗低(0.01mw)

IOL= nIIL

IIL

…

灌电流

1

IIL n个

NOL

?

I OL (驱动门) I IL (负载门)

3.1.2 逻辑门电路的一般特性

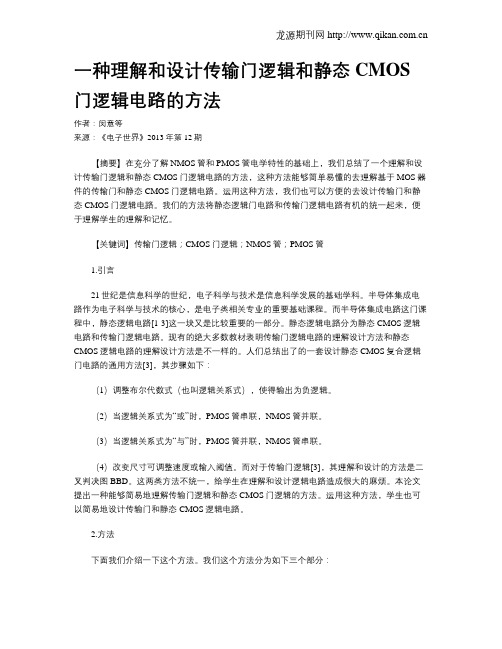

一种理解和设计传输门逻辑和静态CMOS门逻辑电路的方法

一种理解和设计传输门逻辑和静态CMOS 门逻辑电路的方法作者:闵意等来源:《电子世界》2013年第12期【摘要】在充分了解NMOS管和PMOS管电学特性的基础上,我们总结了一个理解和设计传输门逻辑和静态CMOS门逻辑电路的方法,这种方法能够简单易懂的去理解基于MOS器件的传输门和静态CMOS门逻辑电路。

运用这种方法,我们也可以方便的去设计传输门和静态CMOS门逻辑电路。

我们的方法将静态逻辑门电路和传输门逻辑电路有机的统一起来,便于理解学生的理解和记忆。

【关键词】传输门逻辑;CMOS门逻辑;NMOS管;PMOS管1.引言21世纪是信息科学的世纪,电子科学与技术是信息科学发展的基础学科。

半导体集成电路作为电子科学与技术的核心,是电子类相关专业的重要基础课程。

而半导体集成电路这门课程中,静态逻辑电路[1-3]这一块又是比较重要的一部分。

静态逻辑电路分为静态CMOS逻辑电路和传输门逻辑电路。

现有的绝大多数教材表明传输门逻辑电路的理解设计方法和静态CMOS逻辑电路的理解设计方法是不一样的。

人们总结出了的一套设计静态CMOS复合逻辑门电路的通用方法[3],其步骤如下:(1)调整布尔代数式(也叫逻辑关系式),使得输出为负逻辑。

(2)当逻辑关系式为“或”时,PMOS管串联,NMOS管并联。

(3)当逻辑关系式为“与”时,PMOS管并联,NMOS管串联。

(4)改变尺寸可调整速度或输入阈值。

而对于传输门逻辑[3],其理解和设计的方法是二叉判决图BBD。

这两类方法不统一,给学生在理解和设计逻辑电路造成很大的麻烦。

本论文提出一种能够简易地理解传输门逻辑和静态CMOS门逻辑的方法。

运用这种方法,学生也可以简易地设计传输门和静态CMOS逻辑电路。

2.方法下面我们介绍一下这个方法。

我们这个方法分为如下三个部分:(1)对于单个NMOS管而言,漏极输出C等于源极输入A和栅极输入B的“与”。

逻辑表达式为。

图1显示了单个NMOS管。

根据NMOS管高电压通、低电压阻的特性,我们可以得到。

门电路详细课程 (5)

UNL

UNH

G1

B1

S1 TN

0

DE F

UTH

uI /V

VSS

UTN

UTP

噪声DAEB与容UB、UCN限BDN段EHLCT::段:F:N、指输输段::Auuu为入截入IIO:Buu<规为=为I止段OUUV定高低T对T0DNN.值D电5电应,导,V时、平平D,通TTDi,D时时DNNT, 导截允N的的T、0通止许N噪噪,TiT、DP,、波声P(声m:功T的auT动容导x容P)耗OP状。均的限限通 略导极态导最。。下通小与通转大降,。截之折。=范。止电相0围.3压反V。D。D

6. 输入端外接电阻的大小不会引起输入电平的变化。

思考原因?

因为输入阻抗极高 (≥ 108 ) 故 输入电流 0 ,电阻上的压降 0。

uA uGSN uGSP TN

0 V < UTN < UTP 截止 10 V > UTN > UTP 导通

TP

导通 截止

uY

10 V 0V

YA A 1 Y

二、静态特性

1. 电压传输特性: uO f (uI )

+VDD

+ uI

-

S2 TP

G2

B2

D2 iD

uO /V

VDD A B C

D1 uO

2. 3. 5 CMOS 电路使用中应注意的几个问题

一、CC4000 和 C000 系列集成电路

1. CC4000 系列:符合国家标准,电源电压为 3 18 V,功能和外部引线排列与对 应序号的国外产品相同。

2. C000 系列:早期集成电路,电源电压为 7 15 V, 外部引线排列顺序与 CC4000 不同, 用时需查阅有关手册。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

C=0 p p

C nn

VDD

GND C=0

I

CMOS静态组合逻辑门

A=1 B=1

A B

或非门动作原理-4

C=0 p p

C nn

VDD

GND C=0

II

CMOS静态组合逻辑门

A=0 B=0

VDD

A C

B

C=A+B

A=0 B=1

A=1 B=0

VDD

VDD

A=1 B=1

一、两管串联:

Vd

T1 K1

Vg

Vm

T2 K2

Vs

Vd

Vg

Keff

Vs

IDS K[2(VGS VTH )VDS VDS 2 ]

IDS K[(VGS VTH )2 2(VGS VTH )VDS VDS 2 (VGS VTH )2 ]

IDS K[(VGS VTH )2 (VGS VTH VDS )2 ]

12

1

2

同理可推出N个管子串联使用 时,其等效增益因子为:

K eff

1 N1

K i1

i

二、两管并联:

Vd

Vg

K1 K2

Vs

Vd

Vg

Keff

Vs

同理可证,N个Vt相等的管子并联使用时:

与非门电路的驱动能力

VDD

B

在一个组合逻辑电路中,为了使各种

组合门电路之间能够很好地匹配,各

A

个逻辑门的驱动能力都要与标准反相

A=0 B=0

A B

CMOS与非门动作原理-1

C=1

pp C

n

VDD

I VDD C=1

n CMOS静态组合逻辑门

A=0 B=1

A B

CMOS与非门动作原理-2

C=1

pp C

n

VDD

I VDD C=1

n CMOS静态组合逻辑门

A=1 B=0

A B

CMOS与非门动作原理-3

C=1 VDD

pp

C n

A

O

B C

D

O=A·B+C·D

A

O

B C

O

D

O= (A+B)·(C+D)

C

C

D

B

D

A

B

A

B

A

C

A

C

O

B

D

O

C

D

O

B

A

C

A

B

逻辑门的设计

Exclusive OR 逻辑门

2输入EOR(异或门)

AB O

A B

00 0 O 01 1

10 1

11 0

O= A·B+A·B = A·B+A·B = (A·B)·(A·B) = (A+B)·(A+B)

器相当。即在最坏工作条件下,各个

逻辑门的驱动能力要与标准反相器的

特性相同。

设:标准反相器的导电因子为Kn=Kp, 逻辑门:Kn1=Kn2=K’n Kp1=Kp2=K’p

(1)a,b=1,1时,下拉管的等效导电因子:Keffn=K’n/2 (2)a,b=0,0时,上拉管的等效导电因子:Keffp=2K’p (3)a,b=1,0或0,1时,上拉管的等效导电因子:Keffp=K’p

I VDD C=1

n CMOS静态组合逻辑门

A=1 B=1

A B

CMOS与非门动作原理-4

C=0 VDD

pp

C n

GND I C=0

n

CMOS静态组合逻辑门

A=0 B=0

VDD

A C

B

C=A·B

A=0 B=1

A=1 B=0

VDD

VDD

A=1 B=1

VDD

I

I

I

C=1

C=1

C=1

C=0

I

CMOS静态组合逻辑门

Vd

设:Vt相同,工作在线性区。

T1 K1

Vg

Vm

I DS1

K

1

V GV

M V T

2

V GV T V D

2

(1)

T2 K2

Vs

I

DS 2

K

2

V

GV

S V T

2

V GV T V M

2

(2)

I I

DS1

DS 2

V GV M V T

K 2

2

K1 K 2

V GV S V T

•CMOS静态逻辑门电路功耗 与哪些因素有关?

功耗的构成 如何降低功耗

内容提要

CMOS静态逻辑门:CMOS与非门、或非 门、复合门的构成

CMOS门电路的速度(延迟) CMOS门电路的功耗

1.CMOS与非门

A B

C=A·B

A

B

00

01

10

11

C

A B

C 1 1 1 0

pp

C n

n

CMOS静态组合逻辑门

A B C

A OB

C

O=A+B+C

A OB

C

A

B

C

O

O

❖ NMOS、PMOS互补: (并联《====》串联) NMOS 输出为“0” PMOS 输出为“1” ❖ 生成电路为负逻辑:

组成AND和OR时, 加一反相器。

❖ 晶体管数为: 输入端 子数的两倍。

逻辑门的设计

复合逻辑门

A B C

O=A·B+C

K 2

1

K1 K 2

V GV T V D

2

将上式代入(1)得:

I DS1

K 1K 2 [ K1 K 2

V GV

S V T

2

V GV T V D

2

] (3)

2

2

I

DS

K[ eff

V

GV

S V T

V GV T V D ] (4)

比较(3)(4)得:

K K K K K eff

VDD

I C=1

C=0

C=0

C=0

II

I

I

CMOS静态组合逻辑门

基本CMOS逻辑门--1

反相器

A

O

两输入与非门

两输入或非门

A B

O

A B

O

O=A

p

A

B

A

O

n

O=A·B

pp

O

n

A

B

n

O=A+B

p p

O nn

逻辑门的设计

基本CMOS逻辑门--2

三输入与非门 三输入或非门

A B C

O=A·B·C

A

B

C

半导体 集成电路

第6章 CMOS静态逻辑门电路

A

V DD

Out

B

GND

本章设问

•基本的CMOS静态逻辑门有哪些?如何用晶体管构 成基本的静态逻辑门?

•如果任意给定一个逻辑表达 式,如何设计其晶体管级的电 路?

•CMOS静态逻辑门电路速度 取决于哪些因素?

电路结构 晶体管尺寸 如何估算电路速度 如何优化电路速度

逻辑门的设计

反相器

IC版图对应于线路

VDD

N Well PMOS

VDD 2l

PMOS

Contacts

In

Out

In

Out

Metal 1

NMOS

Polysilicon

NMOS

GND

IC版图对应于线路

2-NAND

VDD

VDD

B

A

B

A

Out

GND

MOS管的串、并联特性

晶体管的驱动能力是用其导电因子k来表示的,k值越大, 其驱动能力越强。多个管子的串、并情况下,其等效导 电因子应如何推导?

A

B A

O

B

O= (A+B)·(A+B)

B

B

A

A

A

A

A

B

O

B

BA

B

2020/8/21

西安理工大学 电子工程系 余宁梅

逻辑门的设计

复合逻辑门

❖ 调整逻辑关系式,使得输出为负逻辑 ❖ 逻辑关系为与时,NMOS串联、PMOS并联 ❖ 逻辑关系为或时,NMOS并联、PMOS串联 ❖ 改变尺寸可调整输入阈值或速度

2.CMOS或非门

A C

B

C=A+B

A

B

C

00

1

01

0

10

0

11

0

p

p C

A

B

nn

CMOS静态组合逻辑门

A=0 B=0

A B

或非门动作原理-1

C=1 p p

C nn

VDD

I VDD C=1

CMOS静态组合逻辑门

A=0 B=1

A B

或非门动作原理-2

C=0

p

p C I

nn

VDD

GND C=0

CMOS静态组合逻辑门