高速缓存问题的解决

如何解决网络视频缓冲卡顿的困扰

如何解决网络视频缓冲卡顿的困扰随着互联网的普及和网络速度的提升,越来越多的人开始依赖网络观看视频。

然而,网络视频缓冲卡顿的问题也随之而来,给用户带来了很多困扰。

本文将探讨一些解决网络视频缓冲卡顿的方法,帮助读者提升观看体验。

一、检查网络连接首先,我们需要确保网络连接的稳定性。

网络连接不稳定是导致视频缓冲卡顿的主要原因之一。

我们可以通过以下几个步骤来检查网络连接:1. 检查路由器:确保路由器的电源正常,信号灯显示正常。

如果路由器的信号灯闪烁或者没有亮起,说明存在问题,可能需要重启路由器或者联系网络服务提供商。

2. 测试网络速度:可以使用一些网络测速工具来测试当前网络的速度。

如果网络速度较慢,可能需要联系网络服务提供商进行处理。

3. 距离路由器:如果使用的是Wi-Fi连接,确保距离路由器的距离适中,避免信号衰减。

二、优化设备和软件除了网络连接,设备和软件的优化也可以改善视频缓冲卡顿的问题。

以下是一些优化方法:1. 更新软件和驱动程序:确保设备上的操作系统、浏览器和播放器等软件都是最新版本。

同时,也要及时更新显卡和网卡等驱动程序,以确保设备的正常运行。

2. 关闭后台应用程序:在观看视频时,关闭其他不必要的后台应用程序,以释放设备的资源,提升视频播放的流畅度。

3. 清理缓存和临时文件:定期清理设备中的缓存和临时文件,以释放存储空间和提升设备性能。

三、选择合适的视频播放器和分辨率有时,视频播放器和分辨率的选择也会影响视频缓冲卡顿的情况。

以下是一些建议:1. 使用流行的视频播放器:选择一款流行且稳定的视频播放器,如VLC、PotPlayer等。

这些播放器通常有更好的视频解码能力和网络流媒体支持,可以提供更好的播放体验。

2. 调整视频分辨率:如果网络速度较慢或者设备性能较低,可以尝试降低视频的分辨率。

较低的分辨率可以减少视频的数据量,减轻网络传输的压力,从而减少视频缓冲卡顿的情况。

四、使用VPN或代理服务在某些情况下,网络运营商可能会限制视频流量或者限制特定的视频网站,导致视频缓冲卡顿。

cpu高速缓存的工作原理

cpu高速缓存的工作原理CPU高速缓存的工作原理概述:CPU高速缓存是为了解决CPU与主存之间速度不匹配的问题而设计的,其主要作用是提高CPU的访问速度。

本文将从以下几个方面来详细介绍CPU高速缓存的工作原理。

一、什么是CPU高速缓存?二、为什么需要CPU高速缓存?三、如何实现CPU高速缓存?四、CPU高速缓存的工作原理五、常见的CPU高速缓存类型六、如何优化CPU高速缓存性能一、什么是CPU高速缓存?简单来说,CPU高速缓存就是位于CPU内部的一块小型且容量较小的内存,它用于暂时保存最近使用过的数据和指令,以便在下次访问时可以更快地获取到这些数据和指令。

二、为什么需要CPU高速缓存?由于主板与内存之间存在较大的距离,因此在处理器需要访问内存时会有一定延迟。

而且随着计算机技术不断发展,处理器运行频率越来越快,但内存读写速度却没有相应提升。

这就导致了一个问题:处理器运行时需要等待内存读写操作完成,从而浪费了大量的时间。

为了解决这个问题,CPU高速缓存被设计出来。

三、如何实现CPU高速缓存?CPU高速缓存一般都是由SRAM(静态随机存储器)组成的。

与DRAM(动态随机存储器)不同,SRAM具有更快的访问速度和更低的功耗。

但是,SRAM价格比DRAM贵得多,因此高速缓存容量相对较小。

四、CPU高速缓存的工作原理当处理器需要访问内存时,它首先会检查高速缓存中是否已经存在所需数据或指令。

如果存在,则直接从高速缓存中读取;如果不存在,则需要从内存中读取,并将数据或指令保存到高速缓存中以备下次使用。

CPU高速缓存在工作时分为以下几个步骤:1.地址映射当处理器发出访问请求时,高速缓存会首先将请求地址映射到相应的高速缓存块上。

这个过程一般通过哈希算法来实现。

2.检索数据如果所请求的数据已经存在于高速缓存中,则可以直接从其中读取;否则就需要从主内存中获取数据并将其保存到高速缓存中以便下次使用。

3.替换数据当高速缓存中的空间不足时,就需要将一些数据替换出去以腾出空间。

l2 cache在使用过程中可能遇到的问题

l2 cache在使用过程中可能遇到的问题一、l2 cache概述1.1 l2 cache的作用1.2 l2 cache的结构1.3 l2 cache在计算机系统中的重要性二、常见的l2 cache问题2.1 容量不足导致的性能问题2.2 潜在的故障和稳定性问题2.3 l2 cache与其他硬件的兼容性问题三、解决l2 cache问题的方法3.1 扩大l2 cache容量3.2 定期维护和更新l2 cache3.3 多种方式来解决l2 cache与其他硬件之间的兼容性问题l2 cache在计算机系统中扮演着至关重要的角色。

作为位于CPU和内存之间的高速缓存,l2 cache起着加速数据访问和提高计算机性能的关键作用。

然而,在日常使用中,可能会遇到一些l2 cache的问题,这些问题可能来自容量、稳定性和兼容性等方面。

本文将对l2 cache在使用过程中可能遇到的问题进行全面评估,并提供解决问题的有效方法。

让我们来了解一下l2 cache的基本概念和作用。

l2 cache是一种位于CPU和主内存之间的高速缓存,其作用是存储最常用的数据和指令,以便于CPU快速访问。

通过提供快速的数据读写能力,l2 cache可以大大提高计算机系统的整体性能。

在现代计算机架构中,l2 cache往往采用多层次的结构,以进一步提高缓存的性能和容量。

尽管l2 cache在计算机系统中扮演着重要的角色,但在使用过程中可能会遇到一些问题。

其一,l2 cache容量不足可能会导致性能问题。

随着计算机系统和应用程序的不断发展,数据访问的需求越来越大,而l2 cache的容量却是有限的。

当数据量超过l2 cache的容量时,就会导致数据无法完全缓存,从而影响CPU的访问速度和整体性能。

其二, l2 cache可能存在潜在的故障和稳定性问题。

由于l2 cache通常集成在CPU芯片内部,而且工作在高频、高温环境下,故障和稳定性问题是不可避免的。

第二讲:高速缓存技术

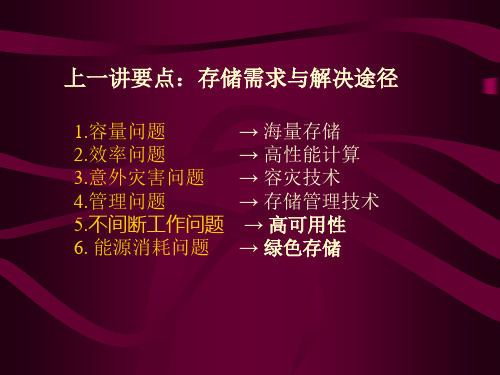

2.1读算法(常用两种) 读算法(常用两种) 读算法 •最近使用(LRU:least recently used)缓存 最近使用( 最近使用 : ) •预先读缓存 预先读缓存

LRU的基本思想:最近读过的数据不久将再次被读。 的基本思想:最近读过的数据不久将再次被读。 的基本思想

缓存内存

操作期间, 在I/O操作期间,读磁盘 操作期间 数据的同时, 数据的同时,数据也拷 贝到缓存 响应 请求

2)设备/子系统中的预先读缓存与在主机内实现不同,它不额 )设备 子系统中的预先读缓存与在主机内实现不同 子系统中的预先读缓存与在主机内实现不同, 外增加主机CPU的负担,及降低竞争主机资源进程的干扰。 的负担, 外增加主机 的负担 及降低竞争主机资源进程的干扰。

3)设备/子系统中透写缓存 对I/O吞吐量要求不高,写操作较 )设备 子系统中透写缓存 吞吐量要求不高, 吞吐量要求不高 少的应用时,透写缓存的效果较好。 少的应用时,透写缓存的效果较好。

磁盘 缓存

图 2.12

设备/子系统中的缓存实现 设备 子系统中的缓存实现

1)设备/子系统中的 )设备 子系统中的 子系统中的LRU缓存效率不如在主机内的缓存系统, 缓存效率不如在主机内的缓存系统, 缓存效率不如在主机内的缓存系统 但它适用主机负荷重的场合(超过75%),或没有适当内存建缓 但它适用主机负荷重的场合(超过 ) 或没有适当内存建缓 存。

1)主机系统的LRU缓存 )主机系统的 缓存 在传输数据并将其装入主 机内存的过程中, 机内存的过程中,LRU对系统性能影响 很小。在主 对系统性能影响 很小。 机内存中实现LRU效率很高。 效率很高。 机内存中实现 效率很高 要消耗更多的CPU周期、 周期、 2)主机系统的预先缓存 要消耗更多的 ) 周期 存储路径、系统I/O总线和系统存储总线的带宽 总线和系统存储总线的带宽。 存储路径、系统 总线和系统存储总线的带宽。 3)主机系统中的透写缓存 ) 一致。 一致。 并可避免数据数据的不

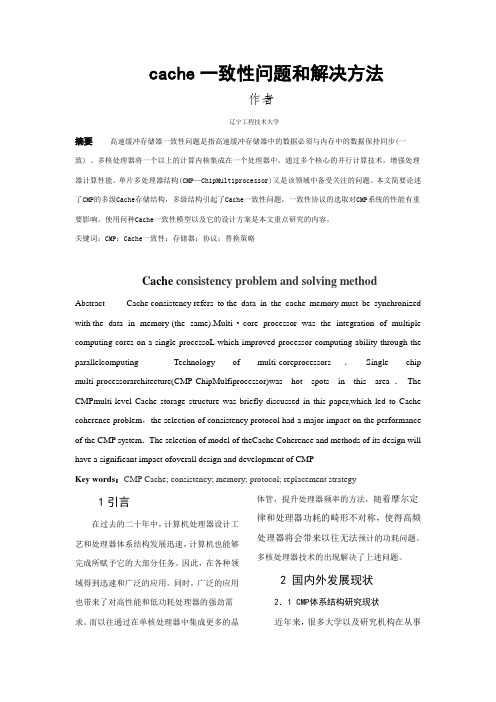

cache一致性问题和解决方法

cache一致性问题和解决方法作者辽宁工程技术大学摘要高速缓冲存储器一致性问题是指高速缓冲存储器中的数据必须与内存中的数据保持同步(一致) 。

多核处理器将一个以上的计算内核集成在一个处理器中,通过多个核心的并行计算技术,增强处理器计算性能。

单片多处理器结构(CMP—ChipMultiprocessor)又是该领域中备受关注的问题。

本文简要论述了CMP的多级Cache存储结构,多级结构引起了Cache一致性问题,一致性协议的选取对CMP系统的性能有重要影响。

使用何种Cache一致性模型以及它的设计方案是本文重点研究的内容。

关键词:CMP;Cache一致性;存储器;协议;替换策略Cache consistency problem and solving methodAbstract Cache consistency refers to the data in the cache memory must be synchronized with the data in memory (the same).Multi·core processor was the integration of multiple computing cores on a single processoL which improved processor computing ability through the parallelcomputing Technology of multi-coreprocessors.Single chip multi-processorarchitecture(CMP-ChipMulfiprocessor)was hot spots in this area.The CMPmulti-level Cache storage structure was briefly discussed in this paper,which led to Cache coherence problem,the selection of consistency protocol had a major impact on the performance of the CMP system.The selection of model of theCache Coherence and methods of its design will have a significant impact ofoverall design and development of CMPKey words:CMP Cache; consistency; memory; protocol; replacement strategy1引言在过去的二十年中,计算机处理器设计工艺和处理器体系结构发展迅速,计算机也能够完成所赋予它的大部分任务。

介绍几个妙招加快内存运行速度

介绍几个妙招加快内存运行速度是否你的电脑运行的速度越来越慢了,是否你找不到何原因你的电脑运行速度会变慢,到底该怎么解决这个问题才好呢,告诉你,可能是内存的问题,下面给大家介绍几个方法来加快电脑内存速度的好方法。

1.调整高速缓存区域的大小。

所谓高速缓存,是指系统在读取磁盘、光盘上的数据时,采取“预读取”技术,也就是将估计即将要读取的数据预先读取到内存的高速缓冲存储器中,这样CPU在高速缓冲存储器中读取数据时就较快,从而进步运行速度。

在内存中设置高速缓冲存储器,可以明显地加快读取数据的速度。

Windows可以根据内存的大小自动地设置高速缓存的大小,当然用户也可以根据自己使用内存的情况,在内存中设置高速缓存的大小,以优化内存的使用。

方法如下:在桌面上用鼠标右击“我的电脑”;在弹出的菜单中单击“属性”;在弹出的窗口中单击“性能”标签;单击下面的“文件系统”按钮;单击“硬盘”标签;拖动“预读式优化”调节杆,设置预读取条件;在“计算机的主要用处”栏设置系统利用高速缓存的比例;假如系统的内存较多,可选择“网络效劳器”,这样系统将用较多的内存作为高速缓存;在CD-ROM标签中,可以直接调节系统用多少内存作为CD-xviii) ROM光盘读写的高速缓存,注意要在“最正确访问方式”中选择“四倍速或更高速”,这样系统将根据情况设置缓存的大小;也可以调节“追加的高速缓存大小”栏中的调节杆,xxii) 追加高速缓存。

2.监视内存。

系统的内存不管有多大,总是会用完的,虽然有虚拟内存,但由于硬盘的读写速度无法与内存的速度相比,大量、频繁地使用虚拟内存将使计算机操作变得无法忍受,所以在使用内存时,就要时刻监视内存的使用情况。

Windows操作系统中提供了一个系统监视器,可以监视内存的使用情况。

另外还有一个简单方法,就是在任何一个文件窗口中,选择“帮助/关于Windows”菜单,在翻开的窗口中就可以看到目前内存使用的情况,一般假如只有60%的内存资可用,这时你就要注意调整内存了,不然就会严重影响你的运行速度和系统性能。

Internal Use Only 戴尔高速缓存解决方案

戴尔缓存分布服务器群*

缓存客户端服务器**

1 安装Fluid Cache 软件

缓存池

2 插入PCIe SSD Express Flash 缓存

私有网络 (10/40 GbE)

3 配置低延迟网络

存储网络(FC or iSCSI)

4 映射卷到缓存池

Dell Compellent SC 8000存储阵列

*至少需要3台经过验证的戴尔服务器用于构建缓存池。 **缓存客户端服务器可以是运行有支持的操作系统、戴尔缓存软件和可用的PCIe插槽的戴尔或者其他品牌服务器

• 测试系统

• Dell PowerEdge R730xd (13G beta), Xeon E5-2690 @ 2.6GHz, 2 sockets w/ 12 cores, 64GB RAM

从Dell Fluid Cache for SAN解决方案获益的其他应用程序

SAP HANA 解决 方案架构增 强

考虑作为 ExaData的替代 方案

云

桌面虚拟 化

经过探讨您可以发现现有环境中更多Fluid Cache for SAN适用的用例和工作负载

8

经过验证的硬件

组件 集群节点

设备描述

最少3台经过认证的戴尔服务器-每个服务器必须包括至少一款缓存介质 经过验证支持多达8台服务器

操作系统

缓存分布服务器

缓存介质 (每台服务器可以安装最大 1.6TB的缓存) 缓存网络交换机

缓存网络接口卡 (NIC)

Compellent 软件 存储

Red Hat Enterprise Linux 6.3 , 6.4 (RHEL) and 6.5* SUSE Linux Enterprise Server 11, Service Pack 3 VMware 5.5**

如何解决超级计算系统中的存储和传输问题

如何解决超级计算系统中的存储和传输问题超级计算系统是一个高性能计算平台,用于处理大规模、复杂的计算任务。

在这样的系统中,存储和传输问题是一个常见而重要的挑战。

本文将探讨一些解决超级计算系统中存储和传输问题的方法和策略。

首先,为了解决存储问题,我们可以采取以下几种方法:1. 分布式文件系统:超级计算系统中的存储问题可以通过使用分布式文件系统来解决。

分布式文件系统将数据分散存储在多个存储节点上,提供了高可用性和容错能力。

这种方法还允许并行访问和多节点数据传输,从而能够提高存储性能。

2. 高速缓存:使用高速缓存可以改善超级计算系统中的存储性能。

高速缓存是一种快速存储设备,通常位于计算节点和存储设备之间,用于暂时存储数据。

通过将频繁访问的数据存储在高速缓存中,系统可以更快地访问和处理数据。

3. 快速存储设备:选择高速的存储设备也有助于解决存储问题。

传统的磁盘驱动器通常具有较低的读写速度,而SSD(固态硬盘)和NVMe(非易失性内存快速存储设备)等快速存储设备可以显著提高存储性能。

接下来,我们将讨论如何解决超级计算系统中的传输问题:1. 高速网络:超级计算系统中的传输问题可以通过使用高速网络来解决。

传统的千兆以太网可能无法满足超级计算系统对高速数据传输的需求。

使用更高带宽的网络技术,如以太网千兆和百兆以太网,可以提高数据传输的速度和效率。

2. 数据压缩和优化:在数据传输过程中,使用数据压缩和优化技术可以减少传输的数据量,提高传输速度。

这些技术可以通过减少数据的冗余和使用更高效的传输协议来实现。

例如,使用压缩算法可以有效地减少数据的大小,从而减少数据传输所需的时间和带宽。

3. 并行传输:在超级计算系统中,使用并行传输技术可以同时传输多个数据流,从而提高传输速度。

这种方法可以通过分割数据流,并使用多个网络接口或多个路径来实现。

并行传输技术可以充分利用系统中的资源,并增加数据传输的吞吐量。

总结起来,超级计算系统中的存储和传输问题可以通过使用分布式文件系统、高速缓存、高速存储设备、高速网络、数据压缩和优化以及并行传输等方法来解决。

高速缓存系统的设计与优化方法研究

高速缓存系统的设计与优化方法研究高速缓存系统是计算机体系结构中的重要组成部分,它的设计和优化对于提高计算机系统的性能至关重要。

本文将探讨高速缓存系统的设计原理、优化方法以及相关研究进展。

一、高速缓存系统的设计原理高速缓存是位于CPU和主内存之间的一个小型、容量有限但访问速度较快的存储器。

其设计原理主要包括以下几个方面:1. 考虑访问局部性:高速缓存系统利用程序的访问局部性原理,将频繁访问的数据块存储到缓存中,以提高访问速度。

常见的局部性包括时间局部性和空间局部性。

2. 采用替换策略:当缓存空间不足时,需要替换掉一部分数据,以便为新的数据腾出空间。

常用的替换策略有最近最少使用(LRU)、随机替换等。

3. 设置缓存块大小:缓存块大小的选择对性能有着重要影响。

如果缓存块太小,可能会导致较高的访问延迟;而缓存块太大则会浪费宝贵的缓存空间。

4. 考虑一致性问题:当高速缓存与主内存之间的数据发生改变时,需要保证缓存中的数据与主内存中的数据保持一致。

常见的解决方案有写直达(write through)和写回(write back)等。

二、高速缓存系统的优化方法1. 提高命中率:命中率是衡量高速缓存性能的重要指标,可以通过以下方法进行优化:- 提高空间局部性:空间局部性是指在程序中多次访问相邻的数据。

通过优化程序的数据结构和内存访问模式,可以提高空间局部性,从而提高命中率。

- 提高时间局部性:时间局部性是指程序在一段时间内多次访问同一数据。

通过合理调整缓存块大小和替换策略,可以提高时间局部性,从而提高命中率。

- 使用关联性较高的缓存映射方式:常见的缓存映射方式包括直接映射、全关联映射和组关联映射。

通过选择关联性较高的缓存映射方式,可以提高命中率。

2. 减少替换开销:替换开销是指由于缓存空间不足,需要替换部分数据造成的开销。

可以通过以下方法进行优化:- 采用更精细的替换策略:传统的替换策略如LRU只考虑最近使用的情况,而并不关心数据的重要性。

嵌入式系统高速缓存一致性优化解决方案

关

键

词 : 缓存 ; 高速 嵌入式系统 ; 性 ; 一致 优化 文献标识码 : A 文章编号 : 7 一 942o )1 00 —0 1 1 o2(o61 — 01 3 6

中图分类号 : 362 ' 1. I P

S l t n t h t z t n o t n itn y ou i o t e Op mia i fDa a Co sse c o i o

p o lm ,a d i lme t i w t y t s f a e rb e s n mp e n i s s m ot r . s t h e w Ke r s A HE:e e d d s se ;c n i e c ;o t z t n y wo d :C C mb d e y t m o ss n y pi ai t mi o

i m b d e y tm t nE e d d S se wi CACHE h

WANG S i o g HA in I h- n ,Z NG Ja ,LAN Yu l

(col f o wr E g erg C ogi n e i , hnq g 00 4 Cf a Sho o f ae n i ei , hnq gU i r t C ogi 0 4 , ln) St n n n v sy n4 i

T i p p r e p t ts o r b e b u a h aa c n it c s fe e d d s s ms n l z s te h s a e x ai e n po lm a o t c e d t o s e y i mo t mb d e y t ,a ay e h a s C sn n o e

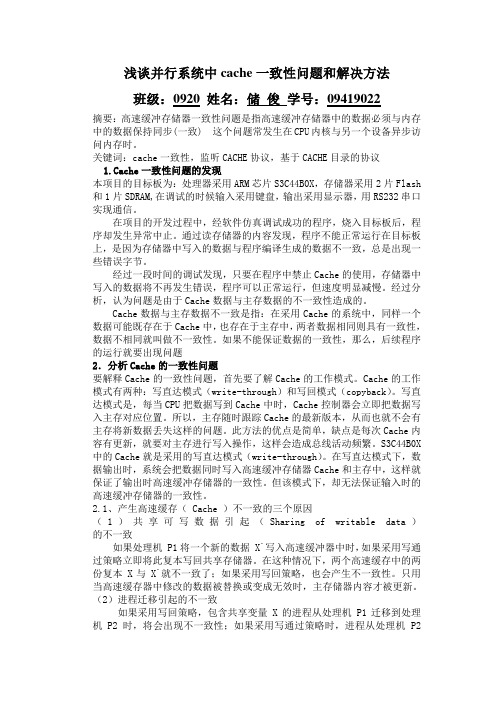

浅谈并行系统中cache一致性问题和解决方法

浅谈并行系统中cache一致性问题和解决方法班级:0920 姓名:储俊学号:09419022摘要:高速缓冲存储器一致性问题是指高速缓冲存储器中的数据必须与内存中的数据保持同步(一致) 这个问题常发生在CPU内核与另一个设备异步访问内存时。

关键词:cache一致性,监听CACHE协议,基于CACHE目录的协议1.Cache一致性问题的发现本项目的目标板为:处理器采用ARM芯片S3C44B0X,存储器采用2片Flash 和1片SDRAM,在调试的时候输入采用键盘,输出采用显示器,用RS232串口实现通信。

在项目的开发过程中,经软件仿真调试成功的程序,烧入目标板后,程序却发生异常中止。

通过读存储器的内容发现,程序不能正常运行在目标板上,是因为存储器中写入的数据与程序编译生成的数据不一致,总是出现一些错误字节。

经过一段时间的调试发现,只要在程序中禁止Cache的使用,存储器中写入的数据将不再发生错误,程序可以正常运行,但速度明显减慢。

经过分析,认为问题是由于Cache数据与主存数据的不一致性造成的。

Cache数据与主存数据不一致是指:在采用Cache的系统中,同样一个数据可能既存在于Cache中,也存在于主存中,两者数据相同则具有一致性,数据不相同就叫做不一致性。

如果不能保证数据的一致性,那么,后续程序的运行就要出现问题2.分析Cache的一致性问题要解释Cache的一致性问题,首先要了解Cache的工作模式。

Cache的工作模式有两种:写直达模式(write-through)和写回模式(copyback)。

写直达模式是,每当CPU把数据写到Cache中时,Cache控制器会立即把数据写入主存对应位置。

所以,主存随时跟踪Cache的最新版本,从而也就不会有主存将新数据丢失这样的问题。

此方法的优点是简单,缺点是每次Cache内容有更新,就要对主存进行写入操作,这样会造成总线活动频繁。

S3C44B0X 中的Cache就是采用的写直达模式(write-through)。

高速缓冲存储器一致性

感谢观看

I(Invalid):这行数据无效。

在该协议的作用下,虽然各cache控制器随时都在监听系统总线,但能监听到的只有读未命中、写未命中以 及共享行写命中三种情况。读监听命中的有效行都要进入S态并发出监听命中指示,但M态行要抢先写回主存;写 监听命中的有效行都要进入I态,但收到RWITM时的M态行要抢先写回主存。总之监控逻辑并不复杂,增添的系统 总线传输开销也不大,但MESI协议却有力地保证了主存块脏拷贝在多cache中的一致性,并能及时写回,保证 cache主存存取的正确性 。

在MESI协议中,每个Cache line有4个状态,可用2个bit表示,它们分别是:

M(Modified):这行数据有效,数据被修改了,和内存中的数据不一致,数据只存在于本Cache中。

E(Exclusive):这行数据有效,数据和内存中的数据一致,数据只存在于本Cache中。

S(Shared):这行数据有效,数据和内存中的数据一致,数据存在于很多Cache中。

一个完整的一致性模型包括高速缓存一致性及存储同一性两个方面,且这两个是互补的:高速缓存一致性定 义了对同一个存储进行的读写操作行为,而存储同一性模型定义了访问所有存储的读写行为。在共享存储空间中, 多个进程对存储的不同单元做并发的读写操作,每个进程都会看到一个这些操作被完成的序。

数据库缓存技术的原理与应用解决方法

数据库缓存技术的原理与应用解决方法数据库缓存技术是一种用于提升数据库性能和响应速度的重要技术手段。

通过将频繁访问的数据缓存到高速存储介质中,可以有效减少数据库的访问次数,提高系统的性能。

本文将深入探讨数据库缓存技术的原理,并介绍几种常用的应用解决方法。

一、数据库缓存技术的原理数据库缓存技术的原理是将数据库中频繁访问的数据存储于高速缓存中,以减少对底层数据库的访问,从而提高系统性能。

其基本原理包括以下几个方面:1. 数据访问模式分析:通过对用户的数据访问模式进行分析,识别出经常被访问或者具有预测性访问的数据,这些数据被认为是热数据。

2. 缓存数据存储:将热数据存储于高速缓存中,常见的缓存介质有内存、SSD(固态硬盘)等。

这些缓存介质具有较低的访问延迟和较高的吞吐量,可以更快速地响应用户请求。

3. 缓存管理机制:当用户请求数据时,首先查询缓存,如果缓存中存在所需数据,则直接返回;若缓存中不存在,则会从数据库中提取数据,并将这些数据缓存到缓存介质中,以便下次使用。

4. 数据一致性维护:由于缓存中数据的更新速度较慢,为了保证数据的一致性,在更新数据库时需要更新同时更新缓存中的数据,或者采用合适的缓存失效策略,及时使缓存中的数据与数据库中的一致。

二、应用解决方法1. 查询结果缓存:对于一些查询操作,可以将查询结果缓存起来,以便下次相同的查询能够从缓存中获取。

这种方法对于查询结果不经常更新的场景非常有效,可以显著提升查询效率。

2. 数据库会话缓存:数据库会话缓存指的是将数据库连接的会话信息缓存起来,以减少数据库连接的开销。

在高并发的系统中,数据库连接的开销是很大的,通过缓存会话信息,可以大幅度降低数据库的连接次数。

3. 数据段缓存:数据段缓存是指将数据库中的常用数据缓存起来。

比如,存储用户信息的数据表、热门商品的数据表等。

通过预先加载这些数据表的数据,并将其缓存到内存中,可以减少数据库的查询次数,提高系统性能。

cache

Cache一致性[摘要]高速缓存(Cache)的设计是为了解决cpu与主存之间速度差距太大的矛盾,Cache技术的发明和使用是计算机科学发展史的重大发展,对于提高计算机系统性能起到了重要的作用。

一般Cache采用高速的SRAM制作。

高速缓冲(Cache)的工作原理就是在程序访问的局部性的基础上。

对于有些有多个处理器的系统,其各自都有其独立的Cache,且都共享主存,那么,这样又出现了新问题,即Cache的一致性问题。

即当其中的一个缓存中数据被修改了的时候,不仅是主存中相对应的字无效,就连同其他缓存中相对应的字也无效(当然恰好其他缓存也有相应的字)。

即使通过写直达法改变了主存的相应字,而其他缓存中数据仍然无效。

显然,解决系统中Cache一致性的问题很重要。

在具有多个处理器的系统中,由于多个处理器有可能对同个一数据块进行读写操作,当其中某个处理器对共享的数据块进行写操作时,其它处理器的高速缓冲cache中这个数据块的副本就将会成为无时效性的数据。

如果不及时地通知相应的处理器去处理,将会导致运行结果的出错。

此论文主要是在分析高速缓冲Cache的一致性问题的造成原因以及解决cache一致性这个问题的监听协议和基于目录的协议两种协议等。

[关键字]高速缓存、Cache、Cache一致性、监听cache协议、基于cache目录的协议一、高速缓存(Cache)的定义依据局部性的原理,发现,其实可以在主存与 CPU之间设置一个高速的、容量相对较小的存储器,若当前正在执行的程序和数据正存放在这个高速的、相对容量较小的存储器中,在程序运行时,不必再去从主存储器取指令以及取数据,只要能够访问这个高速的,容量相对较小的高速存储器即可,所以此举动大大提高了程序运行的速度,这个存储器称作高速缓存存储器(Cache:英文原意为“藏东西的地方”)。

高速缓存存储器介于 CPU和主存之间,它的工作速度数倍于主存,另外,对于此高速缓存器,其全部功能是由计算机硬件来实现的,并且对程序员而言是透明的。

cpu cache无效的方法

cpu cache无效的方法CPU缓存是一种用于加速处理器数据访问的高速存储器。

它位于处理器内部,用于暂时存储频繁访问的数据。

缓存可以提供快速的读写速度,以降低从主内存中读取数据的时间延迟。

然而,有时候CPU缓存可能会失效,导致程序运行速度变慢。

以下是一些导致CPU缓存无效的常见原因和解决方法:1.数据局部性不佳:CPU缓存的设计原则之一是基于局部性原理。

如果程序中的数据分布不具有良好的局部性,那么缓存的效果将会下降。

解决这个问题的方法之一是对代码进行重新排列,使得相关的数据能够紧凑地存储在一起,从而可以最大程度地利用缓存。

2.缓存行冲突:CPU缓存通常以缓存行的形式进行读写。

如果多个变量存储在同一个缓存行上,并且同时被不同的处理器核心访问,就会发生缓存行冲突。

为了解决这个问题,可以将相关的变量分散到不同的缓存行上,从而避免多个核心同时访问同一个缓存行。

3.高速缓存亲和性不佳:在多核处理器上运行的程序可能会出现高速缓存亲和性不佳的问题。

高速缓存亲和性指的是在处理器核心切换时,缓存内容的重新加载问题。

如果缓存内容与新的核心不匹配,那么就会出现缓存失效的情况。

为了解决这个问题,可以使用CPU亲和性调度策略,将特定的线程固定在特定的核心上运行,从而减少缓存失效。

4.内存访问模式不佳:程序中对内存的访问模式也会影响CPU缓存的有效性。

例如,如果程序频繁地访问随机的内存地址,那么缓存的效果将会下降。

相反,如果程序具有良好的访问模式,例如按照局部性原理来访问内存,那么缓存的效果将会提高。

为了改善内存访问模式,可以通过优化算法或数据结构来提高数据局部性。

5.数据竞争:在多线程程序中,如果多个线程同时访问共享数据,就可能导致数据竞争。

数据竞争可能会导致缓存一致性问题,从而使得缓存无效。

为了避免数据竞争,可以使用同步机制,例如互斥锁或原子操作,来保证共享数据的一致性。

总之,CPU缓存的无效问题可能由多种原因引起,包括数据局部性不佳、缓存行冲突、高速缓存亲和性不佳、内存访问模式不佳以及数据竞争。

Web高速缓存服务器网络I/O操作性能存在的问题及改善途径

另外 , u 作为免费的 we 缓存服务器程序 , S i qd 1 ) 它本身支持的并发连接数最多只有 1 2 个 , 4 这对商用的 0 wb e l 高速缓存来说 , 肯定是不够 的. 因此 , 我们的目标就是要提高 Su 处理网络 I qi d / 0的能力和效率 , 让它支 持几千个并发的连接请求 , 但性能不会因此而大幅下降 , 由此来解决 Su 处理网络 I qi d / 0操作 的瓶颈问题 .

述符集合搜索一遍 , 以找出已经准备好的文件描述符 , 而这一搜索过程会 随着集合 中文件描述符个数的增

加而变得越来越低效 . )内核在将准备好 的文件描述符集合通知用户时 , ( 3 又要进行一次从 内核空间到用户

空 间 的复 制 .

当应用程序在处理大量并发的连接时 , 这些开销将随着连接数 目的增多呈线性增长 , 从接的处理 .

服务器通常采用两种操作网络 I / 0的方式来处理多个并发的连接, 一种方式是基于线程的 , 另一种方式 是基于事件驱动的 . 基于线程的方式是用独立的线程来处理每一个新的连接 , 基于事件方式是在一个进程

中使用非阻塞的 I / 0来处理多个连接 .

中图分类号 :P 1 T 31 文献标识码 : A 文章编 号 :07 3820 )9 0 4 4 10 —54 (06 0 —03 —0

1 We 高速缓存服务器存在网络 I b / O瓶颈

很多 W b e 服务器和代理服务器程序都使用事件驱动的单进程架构来实现 . 使用这种方法 的依据是事件

形式把一个文件描述符集合传送给 s e 系统调用 . l t ec lt ec s e 调用将返 回可以进行操作 ( 可读或可写) 的文件描

述符集合 . () l ) 2 p ( 系统调用 : l o o p 在功能上与 s e 系统调用相似 , e c lt 只是使用了一个稍微不同的接 口. 应用程序使

高速缓存中数据阻塞的预防机制

高速缓存中数据阻塞的预防机制一、高速缓存概述高速缓存技术是计算机系统中用于提高数据访问速度的关键技术之一。

它通过将频繁访问的数据存储在快速的存储介质中,减少了对主存的访问次数,从而提高了系统的整体性能。

高速缓存的工作原理是将数据预取到缓存中,当处理器需要访问数据时,首先检查缓存中是否存在所需数据。

如果存在,即缓存命中,处理器可以直接从缓存中读取数据;如果不存在,即缓存未命中,处理器则需要从主存中读取数据,并将其加载到缓存中以供后续访问。

1.1 高速缓存的基本原理高速缓存的基本原理包括数据预取、缓存替换策略和一致性维护。

数据预取是指在处理器访问数据之前,缓存系统预测处理器可能需要的数据,并将其加载到缓存中。

缓存替换策略是指当缓存满时,决定哪些数据需要被替换出缓存的规则。

常见的缓存替换策略有最近最少使用(LRU)、先进先出(FIFO)和最不常用(LFU)等。

一致性维护是指在多处理器系统中,确保所有处理器看到的缓存数据是一致的。

1.2 高速缓存的类型高速缓存根据其存储位置和作用范围,可以分为几种类型。

首先是一级缓存(L1 Cache),它通常集成在处理器芯片内部,具有最快的访问速度。

其次是二级缓存(L2 Cache),它通常位于处理器和主存之间,访问速度次于一级缓存。

最后是三级缓存(L3 Cache),它通常位于多个处理器之间,用于共享数据。

此外,还有辅助缓存,如磁盘缓存和网络缓存,它们用于提高磁盘和网络数据的访问速度。

二、数据阻塞现象数据阻塞是指在高速缓存中,由于某些数据访问模式或缓存策略导致的缓存性能下降的现象。

这种现象通常是由于缓存中的数据访问不均衡,导致某些数据频繁被访问,而其他数据则很少被访问,从而使得缓存的命中率降低,增加了处理器访问主存的次数。

2.1 数据阻塞的原因数据阻塞的原因主要包括以下几个方面:首先是数据访问模式的局部性问题,即某些数据被频繁访问,而其他数据则很少被访问。

其次是缓存替换策略的选择,不同的替换策略可能导致不同的数据访问模式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、问题描述假设有n个页面驻留在内存中,且有一个能容纳k个页面的高速缓存。

现有依次访问内存中m个页面的请求序列I=I1,I2,…,I i,…,I m,其中m>k。

我们必须确定任何时刻哪k个页面放在高速缓存中。

对某个访问请求I i,若该页面在高速缓存中,则可很快完成访问。

否则发生一次缺页,必须将其调入高速缓存。

这时,若高速缓存未满,则直接将其调入,否则必须确定将高速缓存中哪个页面置换出来以便为I i腾出空间。

高速缓存调度问题是指如何调度页面使得缺页的总数尽可能少。

二、算法分析LRU算法:LRU策略淘汰上次使用距离当前最远的页。

LRU实现耗费较高,由于LUR淘汰的是上次使用距时刻t最远的页,故须记录这个距离。

记录方法可使用计数器,给每个页帧增设一个计数器,每访问一页,就把对应的页帧的计数器清零,其余页帧加一,因此,计数器最大的页就是上次访问距今最远的页。

Opt算法:虽然OPT策略被誉为驻留集固定策略中的最优策略,但是由于控制页面调度时需预先知道整个访问串,而在大多数情况下,访问串是不可知的,故难以付诸实用。

在现实情况下并不能完全知晓整个请求序列,但假设我们事先已经知道,这样采取OPT就是最优的。

缓存调度采用OPT策略,OPT策略是驻留集大小固定策略中的最优策略。

它淘汰下次访问距当前最远的那些页中序号最小的一页。

称OPT为驻留集固定类策略中的最优策略理由是,OPT策略对任意一个访问串的控制均有最小的时空积(所占空间与时间的乘积)。

就驻留集固定这类策略而言,由于所占空间为一常数,因此评判策略的性能时只需比较处理同一访问串各自所花费的时间量,即也故障的次数。

设计的关键点:首先在缓存中遍历寻找是否有相应的页面,如果有责结束。

否则,如果缓存内还有空间,则无条件调入内存。

当缓存已满,则进行淘汰,用times记录最远的距离,Index记录最远者的下标。

然后用当前页替换被淘汰页三、时空效率分析OPT时空分析:数据结构中最多只用到一维数组,故而空间复杂度为()。

O n k由关键函数()attemper中复杂度最大的是嵌套的两层for循环可知,时间复杂度的数量级为O(m*k)LRU策略时空分析:空间消耗为一维数组和页的计数器,故而空间复杂度为O (n+k);时间分析:时间最大消耗为每次匹配k个页块,匹配m次,故时间复杂度为O(m*k)四、运行结果OPT策略:访问串:7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1驻留集大小:3LRU策略:访问串:7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,3驻留集大小:3五、分析输出结果OPT策略过程:LRU策略:lru算法:#include<iostream.h>//定义全局变量typedef struct{int state; //块状态true满,false为空int value; //块内的页面号int count; //块计数器标志块据现在的时间}type;type cach[]={{false,-1,0}, //初始化块信息{false,-1,0},{false,-1,0},{false,-1,0}}; //type中有四块int walk_sort[]={7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,3}; //页面访问序列int m=3; //type 块的个数int n=18,count=0; //访问序列的长度void delay(); //声明void up_type(type type[],int walk_sort[]){int i=0; //i为访问序列数组的下标int x;int k;int kk;while(i<n){int j=0; //j为type块的下标//满?while(j<m) //当块没有装满情况{if((type[j].state==false)&&(walk_sort[i]!=type[j].value)) //装入一块{type[j].value=walk_sort[i++];type[j].state=true;type[j].count=0;count++;int kk=0;for (x=0;x<m;x++)if(type[x].value!=-1)cout<<type[x].value<<" ";cout<<"miss"<<endl;//更新其它while(kk<m){if(kk!=j&&type[kk].value!=(-1))type[kk].count++;kk++;}delay();break;}if(type[j].value==walk_sort[i]) //命中{for (x=0;x<m;x++)if(type[x].value!=-1)cout<<type[x].value<<" ";cout<<"hit"<<endl;int kk=0;i++;type[j].count=0;while(kk<m){if(kk!=j&&type[kk].value!=(-1))type[kk].count++;kk++;}}j++; //块下标加一}if(j==m) //考虑type块已经满的情况{int k=0; //块下标while(k<m) //遍历块看其中是否有和访问序列相同的页号,有相同的则命中{if(type[k].value==walk_sort[i]){cout<<endl;for (x=0;x<m;x++)cout<<type[x].value<<" ";cout<<"hit"<<endl;i++;type[k].count=0;int kk=0;//更新其它type块没使用时间while(kk<m){if(kk!=k)type[kk].count++;kk++;}break;}k++;}if(k==m)//type满且没有命中的情况,考虑置换那一块. {int ii=0;count++;int t=0;//要替换的type块号.int max=type[ii].count;ii++;while(ii<m) //lru{if(type[ii].count>max){max=type[ii].count;t=ii;}ii++;}//置换type[t].value=walk_sort[i++];type[t].count=0;for (x=0;x<m;x++)cout<<type[x].value<<" ";cout<<"miss"<<endl;int kk=0;//更新其它type块没使用时间while(kk<m){if(kk!=t)type[kk].count++;kk++;}delay();}}}}void delay(){int i;for(i=0;i<100;i++);}void main(int argc, char* argv[]){cout<<"LRU策略动态变化过程"<<endl;up_type(cach,walk_sort);int i;cout<<"miss的次数"<<count<<endl;cin>>i;}Opt算法://///////////////////////////////////高速缓存调度问题--OPT算法///////////////////////////////#include <iostream>using namespace std;#define MAX 256int n,k,m;//n个页面驻留集,k个页面的高速缓存,m长度的请求队列int I[MAX];int cur_resident;//当前驻留集的个数int cache[MAX],cur_cache;//当前在高速缓存中的页面信息int page_miss;//缺页中断的次数void attemper(){cache[0] = I[0];cur_cache = 1;page_miss = 1;cout<<"缓存内的页面的动态变化过程为:\n"<<I[0]<<endl;for(int i=1; i<m; i++){int j;for( j=0; j<cur_cache; j++){if(I[i] == cache[j])break;}if(j == cur_cache){page_miss++;if(cur_cache < k){cache[cur_cache++] = I[i];}else{//cur_cache==k //淘汰最远的页面int times = 0;int index = 0;for(int q=0; q<k; q++)//cache的下标{int p;for( p=i+1; p<m; p++){if(I[p] == cache[q]){if(times< p-i){times = p-i;index = q;}break;}}if(p == m){index = q;break;}}cache[index] = I[i];//attemper}}else{}for(int m=0;m<cur_cache;m++)cout<<cache[m]<<" ";cout<<endl;}}int main(){page_miss = 0;cur_cache = 0;memset(cache,0,sizeof(cache));cout<<"输入内存驻留的页面号n: ";cin>>n;cout<<"输入请求序列页面的个数m: ";cin>>m;cout<<"输入高速缓存最多容纳的页面数k: ";cin>>k;int i = 0;cout<<"输入请求序列:"<<endl;while(i<m){cin>>I[i];if(I[i] <= n)i++;else cout<<"\nError!\nInput again:";}attemper();cout<<"总共的缺页次数为: "<<page_miss<<endl<<endl;system("pause");return 0;}。