路由器的硬件体系结构

001-华为NE80NE40路由器介绍

NE80、NE40路由器硬件系统

主讲:张建东

主要内容

路由器体系结构

华为技术

NE80、NE40产品简介 NE80、NE40各单板及模块

硬件维护及故障处理

华为技术

路由器体系结构

第五代体系结构

CPU

基于NP的交换式路由器 接口 基于ASIC的交换式路由器 接口 NP NP 交换网 NP NP 接口 接口

基于分布式CPU转发 总线式路由器 接口 ASIC ASIC

CPU

CPU

模块化集中 固定接口集中 转发路由器 转发路由器

CPU CPU

交换网

ASIC ASIC

接口 接口

接口

NE40-8外观

NE40-8结构设计

风 扇 L L L L S S LL L L P P P P R RPP P P U U U U U U UU U U 名称、公司标志 风道 风扇

单板 电源进线

电源 电 源 电 源 侧视

正面

NE40-4主要模块组成

满配制NE40-4由以下模块组成:

一体化机箱,高8U 600W电源模块(1+1备份,交流或直流) 风扇框 2块SRU板(1+1冗余设计) 4块LPU(可配FE、GE、ATM、POS、RPR、CPOS、cE1等业务接口板)

通用交换式路由器(Universal Switching Router,简称USR) 包括3个产品形态,统称NE40系列: Quidway NetEngine 40-8 路由器(简称NE40-8) Quidway NetEngine 40-4 路由器(简称NE40-4) Quidway NetEngine 40-2 路由器(简称NE40-2)

Cisco12000路由器硬件体系产品介绍

风扇、卡位的卡盖

中盈优创资讯科技有限公司 010-58552488

空气过滤器的卡盖

12:36 tt

21

来自中国电信 “用户至上 用心服务”

12816硬件体系结构

GSR System Architecture: Hardware

MBUS

GRP

GRP

SWITCH FABRIC AND SCHEDULER CARDS

中盈优创资讯科技有限公司 010-58552488

12:36 tt

14

来自中国电信 “用户至上 用心服务”

LC的内存

线卡包括以下两种内存:

路由内存:DRAM 包转发内存:SDRAM且包含一系列收(RX)或者发(TX)的缓存,帮助管理出入

线卡的数据包

线卡的内型号和位置和线卡的引擎型号有关,以engine 4为例:

可以和外部扩展的告警系统连接(声音告警、可视告警等) 显示告警卡、CSC卡和SFC卡的状态

告警卡

中盈优创资讯科技有限公司 010-58552488

12:36 tt

16

来自中国电信 “用户至上 用心服务”

面板指示灯含义

CISCO路由器面板指示灯(尤其是告警灯)的含义及简单应对步 骤: GSR设备,其板卡上有允许指示面板,其正常的显示如下: 板卡―― RUN IOS GRP卡- RP ACTV

供冗余的电源,模块A2和B2为下半部分机框(矩阵、下半卡位和下风扇) 提供冗余的电源 支持热插拔,可以拔出A1/B1中的一个或者A2/B2中的一个电源

DC电源

中盈优创资讯科技有限公司 010-58552488

12:36 tt

18

来自中国电信 “用户至上 用心服务”

新一代高端路由器体系结构

维普资讯

服务提供商所面临的挑 战是 :传统 的路由器结 本 却 降 低 了很 多 。如果要 求更 高 的可 靠性 ,可 将 构在故障条件下不能够提供性能保障,从而无法为 的数 量相 应增 多 。

系统 提供极 为坚实 的可靠 性 。 MP R的体 系 结 构 固有 的特性 就是 在 可靠 运 营 S

6 平 滑 下降 .

在发生故障时 ,M S P R技术使流量可以以一种 方面具有极大的潜力。一个随机分配流量 的平行体 均衡 的方 式 重分 布到 同样 可 以到 达 目的地 的预 留 的 系结 构造 就 了一个 精 力充 沛 的交换 网络 。在一 个 交 资源上 。失 去一块 板 卡并 不影 响服 务质量 。但 是 一 换板 中,有许多平行等价的链路单元 ,M S P R技术 旦 发生多点故障 ,M S P R技术可以采用一种更加先 利用适 当而完整的手段 ,监测每个链路单元模块是 进 的策 略 ,在最坏 的情 况 下尽 量实 现 性能 的平 滑 下 否正常运行且能与其他模块正常互通 ,如果发现某 降 ,保证剩余资源 的安全 ,使 网络其他资源有采取 个链路单元模块发生 了故障 ,将把它 与 流量 隔离 , 必要的恢复或保护措施 的余地 ,而不至于崩溃。这 通过这种手段实现故障本地化 ,保证可靠运营。 更 是 MP R智 能 化的体 现 S MS P R故 障监 测基 于实 际流 量 中的不规 则检 7 软件结构 . 测 ,而不用依靠人工测试流量 ,因为人工测试不仅 77 C 70R P的独 有 特 性 之 一 是 具 有 高度 模 块 化 会增加} 额外的负载 ,而 且不可能覆盖 全部的错 误事件 。 的软 件体 系结 构 ,实现 了路 由转 发 和管 理功 能模 块 旦发生故障 ,多路保护将被激活。最基本的 的分离 措施是在平行架构 中提供最小等级的冗余 以补充故 为了减小故障的影响面,增加系统整体可靠性

路由器与网桥的区别

路由器与网桥的区别1.工作层次不同2.端口配置不同网桥俩个局域网端口超过俩个端口的网桥叫交换机。

路由器:局域网和广域网端口3.用途不同网桥唯一的作用是把被许多正在共享的物理网络分割成多个小部分,一次来减少广播风暴,而路由器是在拆分不同子网后,通过网络协议又可进行互相通信,即便是不同网络4.适用范围不同网桥:同一局域网不同子网路由器:不同局域网子网,不同网络5.智能化程度不同网桥共作在数据链路层,不能理解任何网络协议一条链路路由器多个路由,支持各协议6.可管理性不同网桥纯物理硬件,不具有可管理性路由器:软件和硬件路由器的分类:1.按性能档次分:背板交换能力>40Gb/s 高档路由器25到40的为中档小于25为低档2.按结构划分:模块化(较好的扩展能力,吞吐性好,趋势)非模块化3.按功能级别划分:核心层路由器企业级路由器介入级路由器(常见的为宽带路由器)4.从功能上划分; 通用路由器(通常所说的都是)专用路由器5.按所处网络位置划分:边界路由器(连接不同网络)和中间节点路由器(连接不通不过局域网)6.按性能上划分:线速路由器和非线速路由器7.按网络类型上划分:有线和无线路由器主要硬件技术和最新发展1.硬件体系结构2.ASIC技术在高端不复合核心路由器产品开发周期需求,但是在中低档仍有优势可编程ASIC是其趋势3.分布式处理技术现代的路由器采取对报文转发采用分布式处理,可以插多个线路处理板,每个线路板独立完成转发处理工作,即做到每个接口都有一个独立CPU,专门单独负责接收和发送本接口数据包,管理接收发送队列,查询路由表并作出转发决定4.交换式结构和调度算法交换结构有交叉矩阵(速度由调度器决定),共享存储器(存储器的读取速度决定)和共享总线(由总线的容量和仲裁的开销决定)TP0:实现分段和重组,TP1:执行数据分段,重组和差错恢复功能TP2:实现数据的分段和重组,以及单一虚拟电路上的数据流多路复用技术和解除复用技术。

Part 3 路由器的硬件结构(4学时)

天津工业大 HUAWEI 学 TECHNOLOGIES 电子与信息工CO., 程学院 LTD.

HUAWEI IP路由器原理与技术 Confidential

TJPU

实用管理程序

Fast Step——安装软件。使非技术用户可以非常轻松地迅速安装一

个Cisco路由器。

Cisco ConfigMaker——路由器配置工具。用ConfigMaker可以创建

所有Cisco路由器的配置,做好配置后通过网络传到路由器中。如 果网络尚未开通运行,可以从运行ConfigMaker的计算机通过控制 端口和路由器相连,并将配置导入到路由器。

总线结构(适于单个网络接口) 、Cross-bar(交叉开关)结构(适于多个 网络接口) 影响路由器吞吐量的关键因素

路由计算部分——根据网络拓扑选择路由协议,计算出路由表

天津工业大 HUAWEI 学 TECHNOLOGIES 电子与信息工CO., 程学院 LTD.

HUAWEI IP路由器原理与技术 Confidential

TJPU

路由器的硬件组成

只读存储器(Read Only Memory,ROM)

ROM中包括开机自检程序(Power On Self Test,POST)、系统引导程序以及 路由器操作系统(IOS)的精简版本。

随机存储器(Random Access Memory,RAM)

RAM用来存储用户的数据包队列以及路由器在运行过程中产生的中间数据,如 路由表、ARP缓冲区等。 RAM还用来存储路由器的运行配置文件。

路由器的配置及应用技术要点

毕业论文(设计) 题目路由器的配置及应用技术学生姓名学号院系专业指导教师二O一二年五月日路由器的配置及应用技术摘要随着计算机网络技术的快速发展,IP网络的建设与应用也逐渐的多样化,路由器作为IP网络中基本而核心的网络设备,其技术,特别是高性能路由器技术已经成为当前网络领域研究的热点和重点,提高它的配置要求,广泛其应用范围以及传输过程中的安全问题已经成为研究下一代路由器的根本途径。

关键词:路由器配置应用目录第一章路由器的基础1.1路由器的基本概念1.2路由器的工作原理1.3路由器主要技术1.4 路由器的特点和功能第二章路由器的配置2.1 路由器的基本配置2.1.1基本命令模式2.1.2口令配置2.1.3接口配置2. 2 路由器(家庭)安装配置(步骤)2.3企业级路由器的配置方法第三章路由器的应用3.1路由器应用于局域网3.2路由器用于VLAN间的通信3.3路由器作为局域网出口3.4路由器的安全防御功能3. 5路由器的网络管理功能实验:两台路由器互联配置路由器NAT技术在企业网络中的应用前言通信网络是由一些系统和节点组成的集合,这些系统和节点负责传输连接在通信网络上的用户之间信息。

在一个网络中主要定义两种系统:端系统和中间系统。

端系统是支持端用户应用或者服务的设备,中间系统是连接多个网络并允许这些网络的端系统相互之间进行的通信设备。

那么路由器就扮演着把网络相互连接起来的重要角色。

第一章路由器的基础1.1路由器的基本概念:路由器(Router)是连接因特网中各种局域网、广域网的设备,它会根据信道的情况自动选择和设定路由,以最佳路径,按前后顺序发送信号的设备。

路由器所谓路由器,就是一个中间系统,它主要是用来连接两个或多个网络,这些网路可能是同构的也可能是异构的。

路由器工作在OSI参考模型的网络层,在两个不同网络的网络层之间传输报文数据时,需要改变两个不同类型网络报文中的第二层地址,即决定在网络之间数据传输时的路由方向,完成不同网络之间的数据存储、分组和转发。

路由器的体系结构

路由器的体系结构欢迎来到店铺,本文为大家讲解路由器的体系结构,欢迎大家阅读学习。

路由器的体系结构从体系结构上看,路由器可以分为第一代单总线单CPU结构路由器、第二代单总线主从CPU结构路由器、第三代单总线对称式多CPU 结构路由器;第四代多总线多CPU结构路由器、第五代共享内存式结构路由器、第六代交叉开关体系结构路由器和基于机群系统的路由器等多类。

路由器的构成路由器具有四个要素:输入端口、输出端口、交换开关和路由处理器。

输入端口是物理链路和输入包的进口处。

端口通常由线卡提供,一块线卡一般支持4、8或16个端口,一个输入端口具有许多功能。

第一个功能是进行数据链路层的封装和解封装。

第二个功能是在转发表中查找输入包目的地址从而决定目的端口(称为路由查找),路由查找可以使用一般的硬件来实现,或者通过在每块线卡上嵌入一个微处理器来完成。

第三,为了提供QoS(服务质量),端口要对收到的包分成几个预定义的服务级别。

第四,端口可能需要运行诸如SLIP(串行线网际协议)和PPP(点对点协议)这样的数据链路级协议或者诸如PPTP(点对点隧道协议)这样的网络级协议。

一旦路由查找完成,必须用交换开关将包送到其输出端口。

如果路由器是输入端加队列的,则有几个输入端共享同一个交换开关。

这样输入端口的最后一项功能是参加对公共资源(如交换开关)的仲裁协议。

交换开关可以使用多种不同的技术来实现。

迄今为止使用最多的交换开关技术是总线、交叉开关和共享存贮器。

最简单的开关使用一条总线来连接所有输入和输出端口,总线开关的缺点是其交换容量受限于总线的容量以及为共享总线仲裁所带来的额外开销。

交叉开关通过开关提供多条数据通路,具有N×N个交叉点的交叉开关可以被认为具有2N条总线。

如果一个交叉是闭合,输入总线上的数据在输出总线上可用,否则不可用。

交叉点的闭合与打开由调度器来控制,因此,调度器限制了交换开关的速度。

在共享存贮器路由器中,进来的包被存贮在共享存贮器中,所交换的仅是包的指针,这提高了交换容量,但是,开关的速度受限于存贮器的存取速度。

路由器基础知识讲座ppt课件

路由器的主要作用是根据网络层 的信息,选择最佳路径,将数据 包从一个网络转发到另一个网络 ,实现网络互联和通信。

路由器发展历程

第一代路由器

最初的路由器采用软件方式进行路由 计算,性能较低,主要应用于小型网 络。

第二代路由器

第三代路由器

现代路由器已经发展成为高度集成化 、智能化的设备,支持多种路由协议 和网络安全功能,广泛应用于各种规 模的网络。

针对路由功能优化,高效 稳定,如Cisco IOS、 Juniper JUNOS等。

通用操作系统

基于Linux、Unix等系统 ,可定制性强,但需要额 外配置和优化。

实时操作系统

适用于对时间要求严格的 场景,如工业控制、航空 航天等。

路由协议实现原理

静态路由

手动配置路由表,适用于简单网 络环境。

动态路由

Wi-Fi联盟认证

负责无线技术的认证和推广,确保不同厂商的设备 能够互相兼容。

无线网络安全标准

包括WPA/WPA2等加密认证技术,保障无 线网络的安全性。

无线接入点(AP)和桥接器(Bridge)

无线接入点(AP)

01

用于建立无线网络的设备,提供无线客户端的接入和数据传输

功能。

无线桥接器(Bridge)

01

VPN基本概念

VPN(Virtual Private Network)即虚拟专用网络,是利用公共网络

架设的私人网络,通过加密技术保障数据传输的安全性。

02 03

VPN技术原理

VPN采用了隧道技术、加解密技术、密钥管理技术和使用者与设备身份 认证技术,通过在公共网络上建立虚拟专用通道来保障数据传输的安全 性和私密性。

ACL技术原理

NE5000E产品硬件介绍

路漫漫其悠远

NE5000E单机 系统容量 接口容量1.28Tbps,交换容量 (双向计算 2.56Tbps

) 转发性能 1600Mpps 端口密度 16 slots × (4 × 10Gbps) 系统结构 标准机箱,带LCD状态显示

双主控热备份;网板3+1备份;电源 、风扇1+1热备份 系统可靠性 99.999%

NP

NP

接口

基于分布式 CPU转发总线

式路由器 接口

固定接口集中 转发路由器

模块化集中 转发路由器

CPU

CPU

CPU CPU

接口 CPU

接口 接口 接口

CPU

CPU

ASIC 交换网 ASIC

ASIC

ASIC

接口 接口

“性能与业务并重”成为了当代IP 网络基本需求,也是第五代路由器 应运而生的时代使命

路漫漫其悠远

中央框CCC (Cluster Central Chassis)

MPU板: 2块,1:1冗余

ECU板: 8块, Cluster Electric Cross Unit 电交叉板, 每板上支持4块灵活插板光子卡OFC

转发性能 端口密度

系统结构

1600Mpps 64 × 10Gbps 标准机箱,带LCD状态显示 双主控热备份;交换网3+1备份;电源、风扇1+1热备份

系统设计可靠性 99.999%

路漫漫其悠远

NE5000E多框集群基本规格

2.56T级联 5T级联 系统容量 NE5000E*2 NE5000E*4

10T级联 NE5000E*8

IP骨干设备要求

大容量Gbps-Tbps 接口类型丰富 接口密度高

网络配置基础知识

1、Internet内2个站点是如何通信的?2、如何使用VLSM规划IP地址。

根据主机数目不同,划分子网掩码,这样可以节省ip。

3、路由器的基本功能是什么?路由器的硬件主要由哪些部分组成?答:路由选择和交换;网络分段;流量控制;隔离广播;广域网连接。

For personal use only in study and research; not for commercial use路由器的硬件主要由CPU、内存、接口等组成。

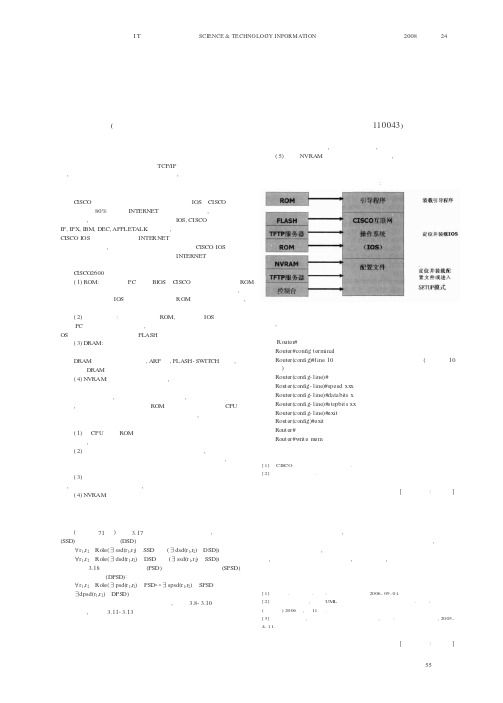

4、简述CISCO路由器的内存体系结构(1)ROM 相当于PC 机的BIOS,Cisco 路由器运行时首先运行ROM 中的程序。

该程序主要进行加电自检,对路由器的硬件进行检测。

(2)FLASH 是一种可擦写、可编程的ROM,FLASH 包含IOS 及微代码。

可以把它想象和PC 机的硬盘功能一样,但其速度快得多。

(3)DRAM:动态内存。

该内存中的内容在系统掉电时会完全丢失。

DRAM 中主要包含路由表,ARP 缓存,fast-switch 缓存,数据包缓存等。

DRAM 中也包含有正在执行的路由器配置文件。

(4)NVRAM:NVRAM 中包含有路由器配置文件,NVRAM 中的内容在系统掉电时不会丢失。

一般地,路由器启动时,首先运行ROM 中的程序,进行系统自检及引导,然后运行FLASH 中的IOS,并在NVRAM 中寻找路由器的配置,并将装入DRAM 中。

5、路由器的配置模式有哪些?进入各种配置模式的命令是什么?(1) router>路由器处于用户命令状态,这时用户可以看路由器的连接状态,访问其它网络和主机,但不能看到和更改路由器的设置内容。

(2) router#在router>提示符下键入enable,路由器进入特权命令状态router#,这时不但可以执行所有的用户命令,还可以看到和更改路由器的设置内容。

(3) router(config)#在router#提示符下键入configure terminal,出现提示符router(config)#,此时路由器处于全局设置状态,这时可以设置路由器的全局参数。

NE5000E核心路由器体系架构

Quidway® NetEngine 5000E核心路由器体系架构概述Quidway® NetEngine 5000E核心路由器(以下简称NE5000E)是华为公司面向互联网骨干节点、城域网核心节点以及数据互联中心节点推出的顶级核心路由器产品。

NE5000E秉承第五代路由器理念,基于先进的网络处理器技术、ASIC技术、IPv6技术和光背板互连技术,采用分布式和可扩展性设计,具备海量交换容量和超高转发性能,全面满足新一代互联网对带宽性能、服务质量、业务提供能力的需要。

NE5000E交换容量为2.56Tbps,接口容量为1.28Tbps,支持高密度10G/40G接口,转发性能高达1600Mpps。

NE5000E可通过光背板互连方式实现容量扩展,支持多机框级联,能极大地提高接口容量和系统性能。

NE5000E共有22个插槽,其中2个主控插槽(1:1备份),4个交换网板插槽(1+3备份)和16个业务插槽。

体系架构NE5000E基于全分布式的硬件转发和无阻塞CROSSBAR交换技术,内置三套总线:监控总线,管理总线和高速数据总线。

接口板采用先进的ASIC和网络处理器技术,来实现业务的高速处理。

NE5000E硬件体系结构NE5000E的单板主要包括:主控板MPU(Main Processing Unit)、交换网板SFU (Switching Fabric Unit)和多种接口板LPU(Line Processing Unit)。

其中关键部件如主控板、交换网板、风扇、电源等都采用冗余设计,提高了整个系统的可靠性。

接口板LPU 的类型包括GE、10GE、10G POS、2.5G POS等。

NE5000E的逻辑架构分为三个平面:数据平面、控制管理平面和监控平面。

三个模块的功能描述如下:NE5000E体系结构逻辑框图z数据平面完成数据报文的高速处理和内部无阻塞交换。

包括报文的封装与解封装、IPv4/MPLS转发处理、QoS与调度处理、内部高速交换以及各种统计。

J基础篇_第4章路由器硬件结构及工作原理cll

第四章路由器硬件结构及工作原理4.1路由器的硬件构成路由器主要由以下几个部分组成:输入/输出接口部分、包转发或交换结构部分(switching fabric)、路由计算或处理部分。

如图4-1所示。

图4-1 路由器的基本组成输入端口是物理链路和输入包的进口处。

端口通常由线卡提供,一块线卡一般支持4、8或16个端口,一个输入端口具有许多功能。

第一个功能是进行数据链路层的封装和解封装。

第二个功能是在转发表中查找输入包目的地址从而决定目的端口(称为路由查找),路由查找可以使用一般的硬件来实现,或者通过在每块线卡上嵌入一个微处理器来完成。

第三,为了提供QoS(服务质量),端口要对收到的数据包进行业务分类,分成几个预定义的服务级别。

第四,端口可能需要运行诸如SLIP(串行线网际协议)和PPP(点对点协议)这样的数据链路级协议或者诸如PPTP(点对点隧道协议)这样的网络级协议。

一旦路由查找完成,必须用交换开关将包送到其输出端口。

如果路由器是输入端加队列的,则有几个输入端共享同一个交换开关。

这样输入端口的最后一项功能是参加对公共资源(如交换开关)的仲裁协议。

普通路由器中该部分的功能完全由路由器的中央处理器来执行,制约了数据包的转发速率(每秒几千到几万个数据包)。

高端路由器中普遍实现了分布式硬件处理,接口部分有强大的CPU处理器和大容量的高速缓存,使接口数据速率达到10Gbps,满足了高速骨干网络的传输要求。

路由器的转发机制对路由器的性能影响很大,常见的转发方式有:进程转发、快速转发、优化转发、分布式快速转发。

进程转发将数据包从接口缓存拷贝到处理器的缓存中进行处理,先查看路由表再查看ARP 表,重新封装数据包后将数据包拷贝到接口缓存中准备传送出去,两次查表和拷贝数据极大的占用CPU的处理时间,所以这是最慢的交换方式,只在低档路由器中使用。

快速交换将两次查表的结果作了缓存,无需拷贝数据,所以CPU处理数据包的时间缩短了。

NetEngine_5000E、NE80E核心路由器介绍

R1603/1604

R2501E/2509E/ 2511E/4001E

R1760

R3680E/3640E

华为机密, 华为机密,未经许可不得扩散

文档密级: 文档密级:内部公开

NE5000E/NE80E系列 系列 核心路由器网络定位

IP骨干网 IP骨干网 城域网核心路由器 大型行业企业网核心路由器 大型IDC出口路由器 大型IDC出口路由器 IDC 下一代互联网、 G/NGN承载网核心路由器 下一代互联网、3G/NGN承载网核心路由器 NE80E主要应用于10G NE80E主要应用于10G网络环境 80 10 NE5000E主要应用于40G和高密度10G NE5000E主要应用于40G和高密度10G网络环境 5000 40 10

IP网络发展趋势 网络发展趋势

大客户专线

•用户量持续增多,每个用户的接入带宽 用户量持续增多, 用户量持续增多 也逐步提升,使得IP网络规模更广, 也逐步提升,使得IP网络规模更广,流 IP网络规模更广 量更大 •大客户/商务客户业务也转向由IP网络 大客户/商务客户业务也转向由IP网络 大客户 IP 承载,要求IP网络具备电信级服务品质 承载,要求IP网络具备电信级服务品质 IP •网络不断发展,新业务不断增加;IPv6 网络不断发展,新业务不断增加; 网络不断发展 下一代互联网技术正在走向成熟和应用 •网络设备需要不断提升以适应业务发展 网络设备需要不断提升以适应业务发展

100Gbps

IP MPLS

•大容量 大容量

Gbps~Tbps ~

•接口类型丰富 接口类型丰富 •接口密度高 接口密度高

1Gbps

IP

更大的容量

华为机密, 华为机密,未经许可不得扩散 文档密级: 文档密级:内部公开

路由器基本知识

KingNet 5

应用层 表示层 会话层 传输层 网络层 数据链路层 物理层

应用层 表示层 会话层 传输层 网络层 数据链路层 物理层

资源子网 通信子网

ห้องสมุดไป่ตู้

KingNet

6

物理层

建立、维护和拆除物理链路的机械、 电气和功能的特征,把实体连接起来 ,在物理介质上传输无特征的比特流 网卡、RS-232C、V24、X.21、V35 都属于物理层范围

KingNet 49

路由协议配置

Router(config)# router igrp 100 Router(config-router)# Router(config-router)#network 200.61.16.0 Router(config-router)#exit

KingNet

50

查看路由器状态

输出速度跟不上输入速度,路由器 的缓存可能被淹没。 采用源抑制,发现拥塞时,向源主 机发送源抑制的ICMP报文,源主机 收到报文后,降速发送。

KingNet

26

冗余和容错

负载分流(Load Sharing) 负载均衡(Load Balancing) 双路由热备份(Hot-Stand-By)

KingNet

KingNet

46

帮助 HELP!!!

在任何模式、任何情况下均可键入 “ ?”来得到帮助。 Router > ? Router# ? Router(config)# ?

KingNet

47

配置局域口

Router(config)# int e0 Router(config-if)# Router(config-if)# ip address 200.61.17.253 255.255.255.0 Router(config-if)#no shutdown Router(config-if)# exit

NE16、08路由器硬件系统概述

NE08/16路由器硬件系统概述交换接入技术支持部北京分部主讲人华为技术NE08/16路由器培训议程路由器基本原理中低端路由器概览NE08/16路由器硬件系统华为技术数据包转发路由表建立和维护安全控制发送传输接收路由器工作流程华为技术NE08/16路由器培训路由器的工作原理包含以下两个关键因素路由协议华为技术NE08/16路由器培训系统处理能力更强 系统可靠性更高系统维护更方便接口配置更灵活分布式处理的优点最少两个业务接口局域网接口、广域网接口配置管理接口局域网接口:10M、100M、1000M接口广域网接口:串口、CE1口、POS接口、 ATM接口配置管理接口:C o n s o l e、A U X接口华为技术NE08/16路由器培训至少两个业务接口协议至少实现到网络层支持异种网络互联支持一组路由协议不同接口的速率适配路由器的特征华为技术器培训议程路由器基本原理中低端路由器概览NE08/16路由器硬件系统华为技术器培训低端——25系列、16系列固定接口分支机构中端——26系列、36系列 模块化接口集中式处理分支机构一个10-BASET 口两个同异步串口一个10-BASET 口一个同异步串口一个ISDN BRI 口16021603160425014001一个10-BASET口两个同异步串口一个10-BASET口一个同异步串口一个CE1/PRI口2509一个10-BASET口两个同异步串口八个异步串口2511一个10-BASET口两个同异步串口十六个异步串口26302631一个固定10-BASET口三个模块插槽两个固定10-BASET口三个模块插槽36403680四个模块插槽八个模块插槽华为技术器培训1FE ——1口10/100M 以太网2FE ——2口10/100M 以太网2SA ——2同异步串口4SA ——4同异步串口1E1——1 CE1/PRI口2E1——2 CE1/PRI口4E1——4 CE1/PRI口4BRI ——4 ISDN BRI S/T口8AS ——8异步串口语音模块中端接口模块华为技术器培训议程路由器基本原理中低端路由器概览NE08/16路由器硬件系统华为技术NE08/16路由器培训NetEngine 16E总共8槽,7个可用插槽总共16槽,12个可用插槽NetEngine 08高端路由器产品华为技术NE08/16路由器培训硬件模块概览路由交换单元:RSU 、RSK 通用接口单元:VIU 、BAK 高可靠控制单元:HAU NE08系统告警单元:ALU各种接口模块:ATM 、POS 、4E1、4SA 、ETH华为技术NE08/16路由器培训Quidway NE 路由器系统组成系统组成包括RSUHAUVIU0槽15槽R S UH A U H A U R S U 主控槽位NE16背面接口板示意图VI U 插槽VI U 插槽系统组成Q u i d w a y N e t E n g i n e16Eè双主控双总线12个通用I/O槽è通用分布式处理板(VI U)Quidway NetEngine 08è单主控双电源è8个Sl ot s双接口卡/板C P C I桥片互联VIU插槽VIU插槽V I U插槽V I U插槽华为技术器培训NE08路由器总线系统告警总线VIU 插槽华为技术器培训路由交换单元•由前处理板和后转接板组成转发表的生成•分布式处理协调中心•全局S N M PACL 等上层应用路由交换单元—RSU器培训RSU板结构华为技术器培训RSU前处理板华为技术华为技术器培训CON :配置口(CONSOLE ),用于系统本地配置AUX :辅助口 ,用于系统远程监控和维护RSU 后转接板(RSK )华为技术器培训通用接口单元•前后插板结构N E08有7个VI U 插槽•CPU128M•Fl ash 可由RSU 装载VRP •Boot r om 系统启动程序VI U 板的作用•根据全局RT/TT ÓµÈû¹ÜÀíµÈQ os 策略•加密VLAN 交换等低层处理•处理I P 多播ACL等局部应用通用接口单元—VIU通用接口单元前处通用接口单元后转接板-B AK接口模块前处理卡接口模块转接卡器培VIU前处理板训华为技术ArrayC P U:P o w e r P C750366M H z/480M I P SD R A M:64~128MF L A S H:8M,装载分布式出来V R PB o o t r o m:1M,系统启动程序接口模块:2个插卡槽位华为技术器培训1个固定快速以太网接口 2个接口模块后转接卡槽位VIU 后转接板(BAK )华为技术器培训高可靠控制单元(HAU)后插板结构NE08没有两条总线之间的桥梁华为技术器培训高密度:4个端口支持通道化,共128通道支持2.048Mbps 透明传输4CE1前处理卡(CEPA )华为技术器培训支持75/120Ω电缆提供DB68插座,配置一转四专用电缆提供接口带电插拔、防雷等保护设计4CE1后转接卡(QEKA )器培训4SA前处理卡(SAPA)华为技术器培训4SA后转接卡(SAKA)华为技术器培训ATM前处理卡(ATPA)华为技术华为技术器培训A T K A 对应单模中距离(30公里)A T K B 对应多模(1公里)A T K C 对应单模长距离(50公里)ATM 后转接卡器培训POS前处理卡(POPA)华为技术器培POS后转接卡训华为技术ArrayP O K A对应单模中距离(30公里)P O K B对应多模(1公里)P O K C对应单模长距离(50公里)器培训以太网前处理卡(ETPA)华为技术华为技术器培训以太网后转接卡(一)ETKA (以太网双绞线)。

路由器的存储结构分析及常见故障处理

配置命令启动路由进程, 为接口提供地址, 设置介质特性等等。 ( 5) 如果 NVRAM 中没有有效 的配置文 件, 操பைடு நூலகம் 系统将执 行一个

称 作 系 统 配 置 对 话 的 由 问 题 驱 动 的 初始 配 置 程 序 。这 种 特 殊 的 模 式 也 称配置对话。

路 由 器 开 电 自 检 后 初 始 启 动 过 程如 下 :

[ 责任编辑: 翟成梁]

●

( 上接第 71 页) 规约 3.17 对 于任意的两个角 色, 静态职责 分离 (SSD) 和 动态 职 责 分 离 (DSD)是 互 斥 的 。

!r1,r2∈R ole(#ssd(r1,r2)∈SSD→┐(#dsd(r1,r2)∈DSD)) !r1,r2∈R ole(#dsd(r1,r2)∈DSD→┐(#ssd(r1,r2)∈SSD)) 规约 3.18 权限职 责分离(PSD)有静 态权限职责 分离(SPSD)和 动 态 权 限 职 责 分 离( DPSD) : !r1,r2∈R ole(#psd(r1,r2)∈PSD’#spsd(r1,r2)∈SPSD∨ #dpsd( r1,r 2)∈DP SD) 本节描述了角色之间的关系的规约, 规约 3.8- 3.10 表 示了角色继 承的性质, 规约 3.11- 3.13 表示了职责分离的性质以及角 色继承和职 责 分 离 中 角 色 之 间 的 关系 。 四 、结 束 语 通过数理代 数和集合论的方 法都系统进行 形式化的描述形 式化

科技信息

○I T 技术论坛○

SCIE NCE & TE CHNO LO GY INFORM ATION

2008 年 第 24 期

路由器的存储结构分析及常见故障处理

张 宏伟 ( 民航 东北地 区空 中交 通管 理局 沈阳 运行 中心 气象 中心 辽 宁 沈阳 110043)

计算机网络原理 路由器的结构

计算机网络原理路由器的结构

从体系结构上看,路由器可以分为:第一代单总线单CPU结构路由路。

第二代单总线主从CPU结构路由器。

第三代单总线对称式多CPU结构路器。

第四代多总线多CPU结构路由器。

第五代共享内存式结构路由器。

第六代交叉开关体系结构路由器和基于机群系统的路由器等多类。

路由器的基本结构由输入端口、输出端口、交换开关和路由处理器组成。

下面我们将分别对这四个组成部分进行具体介绍。

●输入端口。

输入端口是物理链路和输入包的进口处。

端口通常由线卡提供,一块线

卡一般支持4、8或16个端口,一个输入端口具有许多功能。

如:进行数据链路层

的封装和解封装;在转发表中查找输入包目的地址,从而决定目的端口;为了提供

Qos,端口要对收到的包分成几个预定义的服务级别等。

●交换开关。

实现交换开关的功能有多种不同的技术。

目前使用最多的交换开关技术

是总线、交叉开关和共享存储器。

●输出端口。

输出端口在包被发送到输出链路之前存储,可以实现复杂的调度算法以

支持优先级等要求。

与输入端口一样,输出端口同样要能支持数据链路层的封装和

解封装,以及许多较高级协议。

●路由处理器。

路由处理器计算转发表实现路由协议,并运行对路由器进行配置和管

理的软件。

同时,它还处理那些目的地址不在线的转发表中包。

路由器的体系结构

路由器的体系结构在现代网络通信中,路由器扮演着重要的角色,它是将数据包从一个网络转发到另一个网络的关键设备。

路由器的体系结构是如何设计的呢?本文将从硬件和软件两个方面来探讨路由器的体系结构。

一、硬件体系结构1. 中央处理器(CPU)路由器的CPU是整个系统的核心,它负责处理各种控制和转发任务。

CPU的性能决定了路由器的整体性能。

目前,大多数路由器采用多核CPU,以提高系统的并发处理能力。

2. 存储器系统路由器的存储器系统包括主存储器和缓存。

主存储器用于保存路由器的操作系统、路由表等重要数据,而缓存则用于存储临时数据,以提高数据包的处理速度。

3. 接口卡路由器的接口卡是连接路由器与外部网络的接口,它可以是以太网、光纤、串行等不同类型的接口。

接口卡可以根据需要进行灵活的配置和升级。

4. 总线系统总线系统是连接CPU、存储器和接口卡的重要组成部分,它起到数据传输和控制信号传递的作用。

总线的带宽越大,路由器的数据处理能力就越强。

5. 时钟系统时钟系统为路由器提供稳定的时钟信号,以保证整个系统的同步和协调。

二、软件体系结构1. 操作系统路由器的操作系统负责管理和控制路由器的各种功能和资源,如路由表的维护、数据包的转发等。

常见的路由器操作系统有Cisco IOS、Juniper JUNOS等。

2. 路由协议路由协议是路由器之间进行通信和交换路由信息的规则和标准。

常见的路由协议有OSPF、BGP、RIP等,它们能够自动计算最佳路径,并将路由信息传播给其他路由器。

3. 数据转发引擎数据转发引擎是路由器的核心模块,它负责根据路由表的信息,将数据包从输入接口转发到输出接口。

数据转发引擎通常包括数据包接收、查找路由、转发数据包等功能。

4. 管理界面路由器的管理界面提供了用户与路由器进行互动的方式,通过管理界面可以配置路由器的各项参数、监控路由器的状态等。

总结:路由器的体系结构由硬件和软件两个方面构成。

在硬件方面,CPU、存储器系统、接口卡、总线系统和时钟系统共同组成了路由器的基本硬件架构。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

特点

完全的可编程能力 系统灵活性 强大处理能力 高度功能集成 开放式编程接口

应用前景

网络处理器在因特网的核心层、 网络处理器在因特网的核心层、边沿层和局域 企业网中都能有广泛的应用。 网/企业网中都能有广泛的应用。 企业网中都能有广泛的应用 已有的网络设备如骨干网路由器、 已有的网络设备如骨干网路由器、ISP接入设 接入设 备和负载平衡设备, 备和负载平衡设备,通过采用网络处理器可以 升级到更高的速度,提供对新型协议的支持。 升级到更高的速度,提供对新型协议的支持。 可以预测, 可以预测,采用网络处理器的网络设备将是今 后网络设备市场上的主流产品。 后网络设备市场上的主流产品。

StrongARM Core

PCI单元 单元

SRAM单元 单元

SDRAM单元 单元

IX Bus 接口单元

微引擎(六个) 微引擎(六个)

IXP1200 的外部结构

应用CPU 应用 (可选 可选) 可选

PCI 总线

SRAM 8MB Max

IXP1200 网络处理器

SDRAM 256MB Max IX 总线

StrongARM

8KB 数据缓存 512B 从 数据缓存 写缓冲器

数据包

UART 4 定时器

GPIO

PCI 单元

RTC

Intel 16KB StrongARM 指令缓存 SA-1 Core

读缓冲器

SDRAM 单元

存储区 HDR PDU

发送队列

Pkt desc 包描述符 Pkt desc

SDRAM

路由信息

Flash 8MB Max

千兆以太网 MAC 设备

用户或第三方的 IX 总线设备

“Rosetta”

IXP1200 接收

StrongARM

8KB 数据缓存 512B 从 数据缓存 写缓冲器 读缓冲器

UART

4 定时器

GPIO

PCI 单元

RTC

Intel StrongARM SA-1 Core

16KB 指令缓存

编程模式

微代码引擎编程。执行效率高,但工作量大, 微代码引擎编程。执行效率高,但工作量大,代码移植性和 重用性较差。 重用性较差。

编程较为简单,通用性强,执行效率较高。 标准语言编程 。编程较为简单,通用性强,执行效率较高。

4GL编程 。在数据解析及分类方面有优势,但其他方面的功 编程 在数据解析及分类方面有优势, 能较差。 能较差。

路由表

SRAM 单元 微引擎 1

中间结果暂存器 哈希单元

存储器

HDR PDU

微引擎 2

Pkt desc

微引擎 3Hale Waihona Puke SRAMIX BUS

HDR PDU

MAC 设备

IX 总线 接口

微引擎 4

微引擎 5

微引擎 6

微代码开发环境 项目文件 源代码文件

脚本文件 寄存器的符号 名字

软件) 执行处理器 (软件 仿真和调试 软件 微引擎指令在不同的执行状态下 可以很容易的返回源文件, 可以很容易的返回源文件, 进行修改并继续执行

智能协处理器单元, 智能协处理器单元 , 负责整个网络处理器的控 制、管理等。 管理等。

主要功能

位于数据通路物理接口处理器和背板之间, 位于数据通路物理接口处理器和背板之间 , 主要 完成数据通路任务,典型功能包括: 完成数据通路任务,典型功能包括: 分段和重组 协议识别和分类 排队和存取控制 流量整形和流量工程

SDRAM 单元

数据包 存储区 HDR PDU

发送队列

包描述符 包描述符

SDRAM

路由信息

路由表

SRAM 单元

处理包头 微引擎 Info 1

HDR

微引擎 2

微引擎 3

SRAM

IX 总线 MAC

HDR

中间结果暂存器 哈希单元

存储器

HDR

设备

PDU

PDU

IX 总线 接口

微引擎 4

微引擎 5

微引擎 6

IXP1200 发送

网络处理器简介

基本概念

一种专门用来执行包处理、 一种专门用来执行包处理、 转发的高速可编程 处理器。 处理器。其设计充分结合了网络环境中数据流的特 同时具有ASIC高速处理性能和高度灵活的可 点 , 同时具有 高速处理性能和高度灵活的可 编程特性,适用于设计支持业务管理、 编程特性,适用于设计支持业务管理、安全与网络 监控、 等网络功能的高速网络设备。 监控、QoS等网络功能的高速网络设备。 等网络功能的高速网络设备

微引擎 和线程 单个线程

可以显示访问存储器时的 可以同时观察 执行情况 24个线程的情 个线程的情 线程历史 况 命令行界面 运行控制 窗口

数据查看 窗口

Intel IXP 系列网络处理器简介

产品系列

第一代: 第一代:IXP 12XX 第二代: 第二代:IXP 2XXX 其他: 其他:IXP 425等 等

IXP 1200的内部结构 的内部结构

StrongARM Core (232 MHz) 控制和管理任务 • 地 址学习 • 建立并保持路由表 • 网络管理 微引擎 (每个都是 每个都是232 MHz) 每个都是 支持: 支持 • IP, ATM, POS • 帧中继 DSL 帧中继, • QoS • 安全 • Layer 2,3,4 etc.

路由器的硬件体系结构

北京交通大学IP 北京交通大学 网络实验室 苏伟

发展历程

六个阶段(见教材) 六个阶段(见教材) 共享总线→ 共享总线→ 交换结构 路由计算与转发分离 线卡采用网络处理器(NP,Network Processor )等技 , 线卡采用网络处理器 等技 术

研究热点

交换结构 路由转发查询 线卡设计

产生背景

传统通用处理器难以满足对网络性能越来越高 的要求; 的要求;

专用ASIC设备虽然处理速度很高,但灵活性和 设备虽然处理速度很高, 专用 设备虽然处理速度很高 可扩展性较差。 可扩展性较差。

硬件结构组成

网络处理器单元, 主要负责高速的数据处理, 网络处理器单元 , 主要负责高速的数据处理 , 如数据解析、分类和转发等; 如数据解析、分类和转发等;