Microntroller

EC3-1816CLD2NA-中英文说明书-C00-2413-023681

EVOC产品 请注意下列说明:

警告 EVOC产品只允许用于目录和相关技术文件中规定的使用情况。如果要使用其他 公司的产品和组件,必须得到EVOC推荐和允许。正确的运输、储存、组装、装 配、安装、调试、操作和维护是产品安全、正常运行的前提。必须保证允许的环 境条件。必须注意相关文件中的提示。

危险 表示如果不采取相应的小心措施,将会导致死亡或者严重的人身伤害。

警告 表示如果不采取相应的小心措施,可能导致死亡或者严重的人身伤害。

小心 带有警告三角,表示如果不采取相应的小心措施,可能导致轻微的人身伤害。

注意 表示如果不注意相应的提示,可能会出现不希望的结果或状态。

合格的专业人员 本文件所属的产品/系统只允许由符合各项工作要求的合格人员进行操作。

约定 在本文档中,术语“本板”或“产品”有时特指EVOC EC3-1816CLD2NA产品。

说明 安全相关注意事项 为避免财产损失以及出于个人安全方面的原因,请注意本入门指南中关于安 全方面的信息。 文中使用警告三角来指示这些安全信息,警告三角的出现 取决于潜在危险的程度。

目录 1. 产品介绍 .................................................................................................................1

1.1 简介 .................................................................................................... 1

美光科技是哪个国家的

美光科技是哪个国家的Crucial(中文品牌名称:英睿达)美光科技(Micron Technology, Inc.)旗下的一个品牌,总部位于美国Idaho 州Meridian 市。

Crucial 产品包括固态硬盘(SSD)和内存,迄今已被超过5 万台台式电脑、笔记本、服务器、工作站和其他系统所使用。

产品线介绍固态硬盘:Crucial固态硬盘基于自定义固件和其独有的前沿闪存技术而制造。

产品:M5502.5英寸规格容量:128GB,256GB,512GB,1TBmSATA规格容量:128GB,256GB,512GBM.2类型2280规格容量:128GB,256GB,512GB产品:M5002.5英寸规格容量:120GB,240GB,480GB,960GBmSATA规格容量:120GB,240GB,480GB内存:Crucial已为超过5万台系统设计内存产品,从节能型DDR3L 模组到较久远的DDR模组,Crucial能提供业内几乎最为全面的产品组合。

自主制造内存产品,并伴以深度质量测试、30余年的制造经验,和终身有限质保。

产品:·Crucial基本内存适用于:台式机、笔记本、工作站模组类型:UDIMM,SODIMM,UnbufferedECC·Crucial服务器内存适用于:服务器和数据中心模组类型:RDIMM,LRDIMM,FBDIMM,VLPRDIMM,UnbufferedECC ·CrucialMac适用内存适用于:iMac,Macmini,MacBook,MacBookPro模组类型:SODIMM·CrucialBallistix铂胜高性能内存Crucial下的高性能内存产品线,具备更快的速度和更低的延迟,产品特色包括用户可操控的LED灯光、内部温度监测、窄版或宽版模组等多种配置,从新手玩家到超频达人,均能在此找到合适的内存选择。

适用于:游戏玩家、高性能发烧友、超频玩家、机箱改装玩家模组类型:UDIMM。

单片机芯片 80C52

2

MATRA MHS

Rev. G (14 Jan. 97)

Figure 2. Pin Configuration

80C32/80C52

P1.4 P1.3 P1.2 P1.1/T2EX P1.0/T2 NC VCC P0.0/A0 P0.1/A1 P0.2/A2 P0.3/A3

P1.5 P1.6 P1.7 RST RxD/P3.0

TEMIC’s 80C52 and 80C32 are also available at 16 MHz with 2.7 V < VCC < 5.5 V.

D 80C32 : Romless version of the 80C52 D 80C32/80C52-L16 : Low power version

LCC

80C32/80C52

P04 /A4 P05 /A5 P06 /A6 P07 /A7 EA NC ALE PSEN P27 /A15 P26 /A14 P25 /A13

WR/P36 RD/P37 XTAL2 XTAL1

V SS NC P20 /A8 P21 /A9 P22/A10 P23 /A11 P24/A12

Port 2

Port 2 is an 8 bit bi-directional I/O port with internal pullups. Port 2 pins that have 1’s written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (ILL, on the data sheet) because of the internal pullups. Port 2 emits the high-order address byte during fetches from external Program Memory and during accesses to external Data

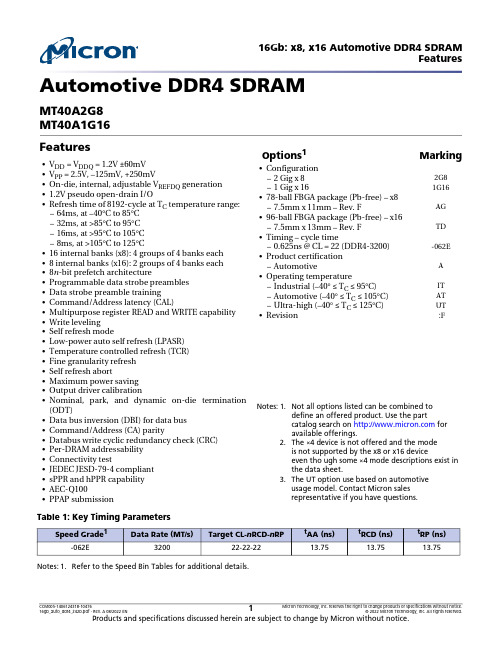

Micron 16Gb x8, x16 汽车级 DDR4 SDRAM 数据手册说明书

Automotive DDR4 SDRAM MT40A2G8MT40A1G16FeaturesNotes:1.Not all options listed can be combined to define an offered product. Use the part catalog search on for available offerings.2.The ×4 device is not offered and the mode is not supported by the x8 or x16 device even tho ugh some ×4 mode descriptions exist in the data sheet.3.The UT option use based on automotive usage model. Contact Micron sales representative if you have questions.Notes:1.Refer to the Speed Bin Tables for additional details.•V DD = V DDQ = 1.2V ±60mV •V PP = 2.5V, –125mV, +250mV •On-die, internal, adjustable V REFDQ generation •1.2V pseudo open-drain I/O •Refresh time of 8192-cycle at T C temperature range:–64ms, at –40°C to 85°C–32ms, at >85°C to 95°C–16ms, at >95°C to 105°C–8ms, at >105°C to 125°C•16 internal banks (x8): 4 groups of 4 banks each•8 internal banks (x16): 2 groups of 4 banks each•8n -bit prefetch architecture•Programmable data strobe preambles•Data strobe preamble training•Command/Address latency (CAL)•Multipurpose register READ and WRITE capability•Write leveling•Self refresh mode•Low-power auto self refresh (LPASR)•Temperature controlled refresh (TCR)•Fine granularity refresh•Self refresh abort•Maximum power saving•Output driver calibration•Nominal, park, and dynamic on-die termination(ODT)•Data bus inversion (DBI) for data bus•Command/Address (CA) parity•Databus write cyclic redundancy check (CRC)•Per-DRAM addressability•Connectivity test•JEDEC JESD-79-4 compliant•sPPR and hPPR capability•AEC-Q100•PPAP submission Options 1Marking •Configuration –2 Gig x 82G8–1 Gig x 161G16•78-ball FBGA package (Pb-free) – x8–7.5mm x 11mm – Rev. F AG •96-ball FBGA package (Pb-free) – x16–7.5mm x 13mm – Rev. F TD •Timing – cycle time –0.625ns @ CL = 22 (DDR4-3200)-062E •Product certification –Automotive A •Operating temperature –Industrial (–40° ≤ T C ≤ 95°C)IT –Automotive (–40° ≤ T C ≤ 105°C)AT –Ultra-high (–40° ≤ T C ≤ 125°C)UT •Revision :F Table 1: Key Timing Parameters Speed Grade 1Data Rate (MT/s)Target CL-n RCD-n RP t AA (ns)t RCD (ns)t RP (ns)-062E 320022-22-2213.7513.7513.75Table 2: AddressingParameter2048 Meg x 81024 Meg x 16 Number of bank groups42Bank group address BG[1:0]BG0Bank count per group44Bank address in bank group BA[1:0]BA[1:0]Row addressing 128K (A[16:0])128K (A[16:0])Column addressing 1K (A[9:0]) 1K (A[9:0])Page size11KB2KBNotes:1.Page size is per bank, calculated as follows:Page size = 2COLBITS× ORG/8, where COLBIT = the number of column address bits and ORG = the number of DQ bits. Figure 1: Order Part Number ExampleExample Part Number: MT40A1G16KH-062E AAT:EContentsImportant Notes and Warnings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 General Notes and Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Industrial Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Automotive Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Ultra-high Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 General Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Definitions of the Device-Pin Signal Level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Definitions of the Bus Signal Level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Functional Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Ball Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Ball Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 RESET and Initialization Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Power-Up and Initialization Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 RESET Initialization with Stable Power Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Uncontrolled Power-Down Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Programming Mode Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Mode Register 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Burst Length, Type, and Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 CAS Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 Write Recovery (WR)/READ-to-PRECHARGE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 DLL RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 Mode Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 DLL Enable/DLL Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 Output Driver Impedance Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 ODT R TT(NOM) Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Additive Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Rx CTLE Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Write Leveling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Output Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Termination Data Strobe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 Mode Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 CAS WRITE Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Low-Power Auto Self Refresh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Dynamic ODT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 Write Cyclic Redundancy Check Data Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 Mode Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 Multipurpose Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 WRITE Command Latency When CRC/DM is Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 Fine Granularity Refresh Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 Temperature Sensor Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 Per-DRAM Addressability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 Gear-Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 Mode Register 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 Hard Post Package Repair Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 Soft Post Package Repair Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 WRITE Preamble . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55READ Preamble . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 READ Preamble Training . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 Temperature-Controlled Refresh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 Command Address Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 Internal V REF Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 Maximum Power Savings Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 Mode Register 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 Data Bus Inversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57 Data Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57 CA Parity Persistent Error Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 ODT Input Buffer for Power-Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 CA Parity Error Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 CRC Error Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 CA Parity Latency Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 Mode Register 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59 Data Rate Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 V REFDQ Calibration Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 V REFDQ Calibration Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 V REFDQ Calibration Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 Truth Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61 NOP Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66 DESELECT Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66 DLL-Off Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66 DLL-On/Off Switching Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68 DLL Switch Sequence from DLL-On to DLL-Off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68 DLL-Off to DLL-On Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 Input Clock Frequency Change . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 Write Leveling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 DRAM Setting for Write Leveling and DRAM TERMINATION Function in that Mode . . . . . . . . . . . . . . . . . . . . . . . 73 Procedure Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73 Write Leveling Mode Exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75 Command Address Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 Low-Power Auto Self Refresh Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80 Manual Self Refresh Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80 Multipurpose Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 MPR Reads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 MPR Readout Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85 MPR Readout Serial Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85 MPR Readout Parallel Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 MPR Readout Staggered Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 MPR READ Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 MPR Writes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90 MPR WRITE Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90 MPR REFRESH Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92 Gear-Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94 Maximum Power-Saving Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97 Maximum Power-Saving Mode Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97 Maximum Power-Saving Mode Entry in PDA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98 CKE Transition During Maximum Power-Saving Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98 Maximum Power-Saving Mode Exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98 Command/Address Parity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100 Per-DRAM Addressability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107V REFDQ Range and Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111V REFDQ Step Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111V REFDQ Increment and Decrement Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112V REFDQ Target Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116Connectivity Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118Minimum Terms Definition for Logic Equations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119Logic Equations for a x4 Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119Logic Equations for a x8 Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120Logic Equations for a x16 Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120CT Input Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120Excessive Row Activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122Post Package Repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123Post Package Repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123Hard Post Package Repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123hPPR Row Repair - Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124hPPR Row Repair – WRA Initiated (REF Commands Allowed) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124hPPR Row Repair – WR Initiated (REF Commands NOT Allowed) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126sPPR Row Repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127hPPR/sPPR/MBIST-PPR Support Identifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130ACTIVATE Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130PRECHARGE Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131REFRESH Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132Temperature-Controlled Refresh Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134Normal Temperature Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134Extended Temperature Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134Fine Granularity Refresh Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136Mode Register and Command Truth Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136 t REFI and t RFC Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136 Changing Refresh Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139Usage with TCR Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139Self Refresh Entry and Exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139SELF REFRESH Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141Self Refresh Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143Self Refresh Exit with NOP Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144Power-Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146Power-Down Clarifications – Case 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151Power-Down Entry, Exit Timing with CAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152ODT Input Buffer Disable Mode for Power-Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154CRC Write Data Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156CRC Write Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156WRITE CRC DATA Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156DBI_n and CRC Both Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157DM_n and CRC Both Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157DM_n and DBI_n Conflict During Writes with CRC Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157CRC and Write Preamble Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157CRC Simultaneous Operation Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157CRC Polynomial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157CRC Combinatorial Logic Equations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158Burst Ordering for BL8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159CRC Data Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159CRC Enabled With BC4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .160。

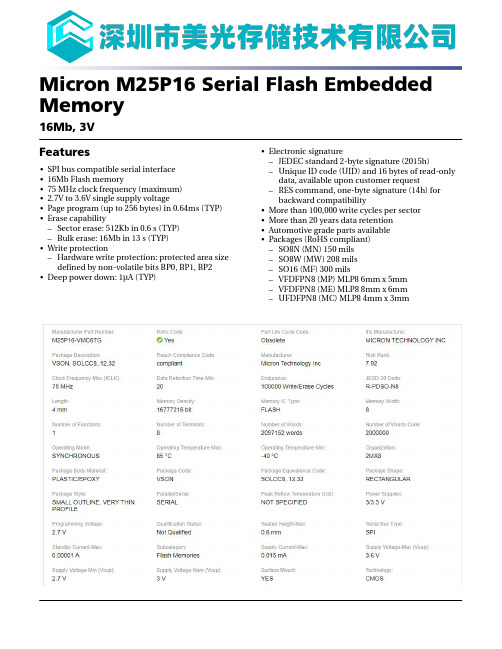

MEMORY存储芯片M25P16-VMC6TG中文规格书

Micron M25P16 Serial Flash Embedded Memory16Mb, 3V Features•SPI bus compatible serial interface •16Mb Flash memory•75 MHz clock frequency (maximum)•2.7V to 3.6V single supply voltage•Page program (up to 256 bytes) in 0.64ms (TYP)•Erase capability–Sector erase: 512Kb in 0.6 s (TYP)–Bulk erase: 16Mb in 13 s (TYP)•Write protection–Hardware write protection: protected area size defined by non-volatile bits BP0, BP1, BP2•Deep power down: 1µA (TYP)•Electronic signature–JEDEC standard 2-byte signature (2015h)–Unique ID code (UID) and 16 bytes of read-only data, available upon customer request–RES command, one-byte signature (14h) for backward compatibility•More than 100,000 write cycles per sector •More than 20 years data retention •Automotive grade parts available •Packages (RoHS compliant)–SO8N (MN) 150 mils –SO8W (MW) 208 mils –SO16 (MF) 300 mils–VFDFPN8 (MP) MLP8 6mm x 5mm –VFDFPN8 (ME) MLP8 8mm x 6mm –UFDFPN8 (MC) MLP8 4mm x 3mmMicron M25P16 Serial Flash Embedded MemoryImportant Notes and WarningsFunctional DescriptionThe M25P16 is an 16Mb (2Mb x 8) serial Flash memory device with advanced write pro-tection mechanisms accessed by a high speed SPI-compatible bus. The device supports high-performance commands for clock frequency up to 75MHz.The memory can be programmed 1 to 256 bytes at a time using the PAGE PROGRAM command. It is organized as 32 sectors, each containing 256 pages. Each page is 256bytes wide. Memory can be viewed either as 8,192 pages or as 2,097,152 bytes. The en-tire memory can be erased using the BULK ERASE command, or it can be erased one sector at a time using the SECTOR ERASE command.This datasheet details the functionality of the M25P16 device based on 110nm process.Figure 1: Logic DiagramS#V CCHOLD#V SSDQ1C DQ0W#Table 1: Signal NamesMicron M25P16 Serial Flash Embedded MemoryFunctional DescriptionFigure 5: Bus Master and Memory Devices on the SPI BusSS2.Resistors (R) ensure that the memory device is not selected if the bus master leaves theS# line High-Z.3.The bus master may enter a state where all I/O are High-Z at the same time; for exam-ple, when the bus master is reset. Therefore, C must be connected to an external pull-down resistor so that when all I/O are High-Z, S# is pulled HIGH while C is pulled LOW.This ensures that S# and C do not go HIGH at the same time and that the t SHCH require-ment is met.4.The typical value of R is 100kΩ, assuming that the time constant R × C p (C p = parasiticcapacitance of the bus line) is shorter than the time during which the bus master leavesthe SPI bus High-Z.5.Example: Given that C p = 50pF (R × C p= 5μs), the application must ensure that the busmaster never leaves the SPI bus High-Z for a time period shorter than 5μs.质量等级领域:宇航级IC、特军级IC、超军级IC、普军级IC、禁运IC、工业级IC,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以深圳市美光存储技术有限公司提供的参数为例,以下为M25P16-VMC6TG的详细参数,仅供参考。

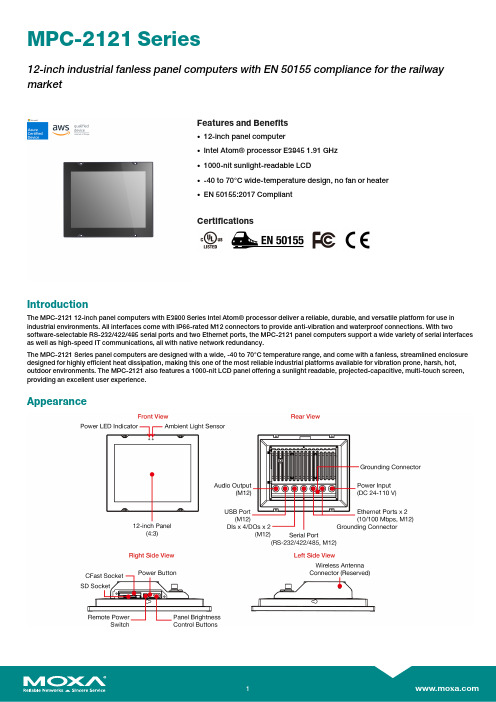

莫加 MPC-2121 系列 12英寸无风扇车辆面板计算机商品介绍说明书

MPC-2121Series12-inch industrial fanless panel computers with EN50155compliance for the railway marketFeatures and Benefits•12-inch panel computer•Intel Atom®processor E38451.91GHz•1000-nit sunlight-readable LCD•-40to70°C wide-temperature design,no fan or heater•EN50155:2017CompliantCertificationsIntroductionThe MPC-212112-inch panel computers with E3800Series Intel Atom®processor deliver a reliable,durable,and versatile platform for use in industrial environments.All interfaces come with IP66-rated M12connectors to provide anti-vibration and waterproof connections.With two software-selectable RS-232/422/485serial ports and two Ethernet ports,the MPC-2121panel computers support a wide variety of serial interfaces as well as high-speed IT communications,all with native network redundancy.The MPC-2121Series panel computers are designed with a wide,-40to70°C temperature range,and come with a fanless,streamlined enclosure designed for highly efficient heat dissipation,making this one of the most reliable industrial platforms available for vibration prone,harsh,hot, outdoor environments.The MPC-2121also features a1000-nit LCD panel offering a sunlight readable,projected-capacitive,multi-touch screen, providing an excellent user experience.AppearanceSpecificationsComputerCPU Intel Atom®Processor E3845(2M Cache,1.91GHz)Graphics Controller Intel®HD GraphicsSystem Memory Pre-installed4(8GB Max.)GB DDR3LSystem Memory Slot SODIMM DDR3/DDR3L slot x1Pre-installed OS MPC-2121-E4-LB-CT-T-W7E/MPC-2101-E4-CT-T-W7E:Windows Embedded Standard7(WS7P)64-bit pre-installedMPC-2121-E4-LB-CT-T-LX/MPC-2121-E4-CT-T-LX:Linux9pre-installedSupported OS Windows10Pro64-bitWindows10Embedded IoT Ent2019LTSC64-bitWindows10Embedded IoT Ent2016LTSBWindows7Pro for Embedded SystemsWindows Embedded Standard7(WS7P)64-bitLinux Debian9Expansion Slots Mini PCIeStorage Slot CFast slot x1SD slots x1,SD3.0(SDHC/SDXC)socketStorage Pre-installed MPC-2121-E4-LB-CT-T-W7E/MPC-2121-E4-CT-T-W7E:32GB CFast CardMPC-2121-E4-LB-CT-T-LX/MPC-2121-E4-CT-T-LX:32GB CFast CardComputer InterfaceEthernet Ports Auto-sensing10/100Mbps ports(M12D-coded4P)x2Serial Ports RS-232/422/485ports x1(M12A-code12P)USB2.0USB2.0hosts x1(M12A-coded5P)Digital Input DIs x4(M12A-code)Digital Output DOs x2(M12A-code)LED IndicatorsSystem Power x1DisplayActive Display Area245.76(H)x184.32(V)mmAspect Ratio4:3Contrast Ratio1000:1Light Intensity(Brightness)500/1000cd/m2Max.No.of Colors16.2M(8-bit/color)Panel Size12-inch viewable imagePixel Pitch(RGB)0.240(H)x0.240(V)mmPixels1024x768Response Time5ms(gray to gray)Viewing Angles176°/176°Touch FunctionTouch Type Capacitive Touch(PCAP)Touch Support Points4pointsGlove Support YesSerial InterfaceBaudrate50bps to115.2kbpsData Bits5,6,7,8Flow Control RTS/CTS,XON/XOFFParity None,Even,Odd,Space,MarkStop Bits1,1.5,2Serial SignalsRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GND RS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDRS-485-4w Tx+,Tx-,Rx+,Rx-,GNDPower ParametersInput Voltage24to110VDCPhysical CharacteristicsHousing MetalIP Rating IP66Dimensions297x238x59mm(11.69x9.37x2.32in) Weight2850g(6.28lb)Environmental LimitsOperating Temperature-40to70°C(-40to158°F)Storage Temperature(package included)-40to70°C(-40to158°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsEMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:6kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:20V/mIEC61000-4-4EFT:Power:2kV;Signal:2kVIEC61000-4-5Surge:Power:2kV;Signal:1kVIEC61000-4-6CS:10VIEC61000-4-8PFMFMechanical Protection Rating IEC60529,IP codeShock EN50155standardVibration EN50155standardEMC EN55032/35Safety IEC60950-1,IEC62368-1,UL62368-1 DeclarationGreen Product RoHS,CRoHS,WEEEWarrantyWarranty Period LCD:1yearSystem:3yearsDetails See /warrantyPackage ContentsDevice1x MPC-2121Series computerInstallation Kit6x screw,for panel-mounting1x M12-Phone jack power cable1x M12-Type A USB cable1x terminal block,2-pin(for remote power input) Documentation1x quick installation guide1x warranty cardDimensionsOrdering Information2.0MPC-2121-E4-LB-CT-T-W7E 12"(4:3)500nitsE3845Quadcore4GBW7E(64-bit)2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T-W7E12"(4:3)1,000nitsE3845Quadcore4GBW7E(64-bit)2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-LB-CT-T-LX 12"(4:3)500nitsE3845Quadcore4GB Debian92(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T-LX12"(4:3)1,000nitsE3845Quadcore4GB Debian92(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-LB-CT-T 12"(4:3)500nitsE3845Quadcore4GB–2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T12"(4:3)1,000nitsE3845Quadcore4GB–2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°C©Moxa Inc.All rights reserved.Updated Jun28,2021.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

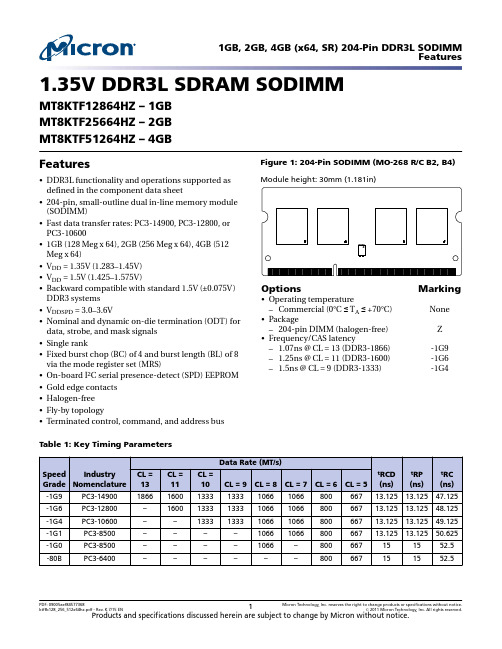

MT8KTF51264HZ-1G6E1

1.35V DDR3L SDRAM SODIMMMT8KTF12864HZ – 1GB MT8KTF25664HZ – 2GB MT8KTF51264HZ – 4GB Features•DDR3L functionality and operations supported as defined in the component data sheet•204-pin, small-outline dual in-line memory module (SODIMM)•Fast data transfer rates: PC3-14900, PC3-12800, or PC3-10600•1GB (128 Meg x 64), 2GB (256 Meg x 64), 4GB (512Meg x 64)•V DD = 1.35V (1.283–1.45V)•V DD = 1.5V (1.425–1.575V)•Backward compatible with standard 1.5V (±0.075V)DDR3 systems •V DDSPD = 3.0–3.6V•Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals •Single rank•Fixed burst chop (BC) of 4 and burst length (BL) of 8via the mode register set (MRS)•On-board I 2C serial presence-detect (SPD) EEPROM •Gold edge contacts •Halogen-free •Fly-by topology•Terminated control, command, and address bus Figure 1: 204-Pin SODIMM (MO-268 R/C B2, B4)Module height: 30mm (1.181in)OptionsMarking•Operating temperature–Commercial (0°C ≤ T A ≤ +70°C)None •Package–204-pin DIMM (halogen-free)Z •Frequency/CAS latency– 1.07ns @ CL = 13 (DDR3-1866)-1G9– 1.25ns @ CL = 11 (DDR3-1600)-1G6– 1.5ns @ CL = 9 (DDR3-1333)-1G4Table 1: Key Timing ParametersTable 2: AddressingTable 3: Part Numbers and Timing Parameters – 1GB Modules1Table 4: Part Numbers and Timing Parameters – 2GB Modules1Table 5: Part Numbers and Timing Parameters – 4GB Modules1Notes: 1.The data sheet for the base device can be found on Micron’s web site.2.All part numbers end with a two-place code (not shown) that designates component and PCB revisions.Consult factory for current revision codes. Example: MT8KSF51264HZ-1G9P1.Pin AssignmentsTable 6: Pin AssignmentsNotes: 1.Pin 78 is NF for 1GB and 2GB; A15 for 4GB.2.Pin 80 is NF for 1GB; A14 for 2GB and 4GB.Pin DescriptionsThe pin description table below is a comprehensive list of all possible pins for all DDR3modules. All pins listed may not be supported on this module. See Pin Assignments forinformation specific to this module.Table 7: Pin DescriptionsTable 7: Pin Descriptions (Continued)DQ MapsTable 8: Component-to-Module DQ Map, R/C B2 (PCB 1092)Table 9: Component-to-Module DQ Map, R/C B4 (PCB 1348)Functional Block Diagram Figure 2: Functional Block DiagramS0#A[15/14/13:0]RAS#WE#CKE0A[15/14/13:0]: DDR3 SDRAMWE#: DDR3 SDRAMCKE0: DDR3 SDRAMRESET#: DDR3 SDRAMCK0CK0#CK1CK1#V REFCAV SSV DDControl, command,and address terminationV DDSPDV TTV REFDQClock, control, command, and address line terminations:TTV DDNote: 1.The ZQ ball on each DDR3 component is connected to an external 240Ω ±1% resistorthat is tied to ground. It is used for the calibration of the component’s ODT and outputdriver.1GB, 2GB, 4GB (x64, SR) 204-Pin DDR3L SODIMMFunctional Block DiagramGeneral DescriptionDDR3 SDRAM modules are high-speed, CMOS dynamic random access memory mod-ules that use internally configured 8-bank DDR3 SDRAM devices. DDR3 SDRAM mod-ules use DDR architecture to achieve high-speed operation. DDR3 architecture is essen-tially an 8n-prefetch architecture with an interface designed to transfer two data wordsper clock cycle at the I/O pins. A single read or write access for the DDR3 SDRAM mod-ule effectively consists of a single 8n-bit-wide, one-clock-cycle data transfer at the inter-nal DRAM core and eight corresponding n-bit-wide, one-half-clock-cycle data transfersat the I/O pins.DDR3 modules use two sets of differential signals: DQS, DQS# to capture data and CKand CK# to capture commands, addresses, and control signals. Differential clocks anddata strobes ensure exceptional noise immunity for these signals and provide precisecrossing points to capture input signals.Fly-By TopologyDDR3 modules use faster clock speeds than earlier DDR technologies, making signalquality more important than ever. For improved signal quality, the clock, control, com-mand, and address buses have been routed in a fly-by topology, where each clock, con-trol, command, and address pin on each DRAM is connected to a single trace and ter-minated (rather than a tree structure, where the termination is off the module near theconnector). Inherent to fly-by topology, the timing skew between the clock and DQS sig-nals can be easily accounted for by using the write-leveling feature of DDR3.Serial Presence-Detect EEPROM OperationDDR3 SDRAM modules incorporate serial presence-detect. The SPD data is stored in a256-byte EEPROM. The first 128 bytes are programmed by Micron to comply withJEDEC standard JC-45, "Appendix X: Serial Presence Detect (SPD) for DDR3 SDRAMModules." These bytes identify module-specific timing parameters, configuration infor-mation, and physical attributes. The remaining 128 bytes of storage are available for useby the customer. System READ/WRITE operations between the master (system logic)and the slave EEPROM device occur via a standard I2C bus using the DIMM’s SCL(clock) SDA (data), and SA (address) pins. Write protect (WP) is connected to V SS, per-manently disabling hardware write protection. For further information refer to Microntechnical note TN-04-42, "Memory Module Serial Presence-Detect."Electrical SpecificationsStresses greater than those listed may cause permanent damage to the module. This is astress rating only, and functional operation of the module at these or any other condi-tions outside those indicated in each device's data sheet is not implied. Exposure to ab-solute maximum rating conditions for extended periods may adversely affect reliability. Table 10: Absolute Maximum RatingsTable 11: Operating ConditionsNotes: 1.Module is backward-compatible with 1.5V operation. Refer to device specification fordetails and operation guidance.2.V TT termination voltage in excess of the stated limit will adversely affect the commandand address signals’ voltage margin and will reduce timing margins.3.T A and T C are simultaneous requirements.4.For further information, refer to technical note TN-00-08: “Thermal Applications,”available on Micron’s web site.5.The refresh rate is required to double when 85°C < T C≤ 95°C.DRAM Operating ConditionsRecommended AC operating conditions are given in the DDR3 component data sheets.Component specifications are available at . Module speed grades correlatewith component speed grades, as shown below.Table 12: Module and Component Speed GradesDesign ConsiderationsSimulationsMicron memory modules are designed to optimize signal integrity through carefully de-signed terminations, controlled board impedances, routing topologies, trace lengthmatching, and decoupling. However, good signal integrity starts at the system level.Micron encourages designers to simulate the signal characteristics of the system'smemory bus to ensure adequate signal integrity of the entire memory system.PowerOperating voltages are specified at the DRAM, not at the edge connector of the module.Designers must account for any system voltage drops at anticipated power levels to en-sure the required supply voltage is maintained.I DD SpecificationsTable 13: DDR3 I DD Specifications and Conditions – 1GB (Die Revision J)Values are for the MT41K128M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 1GbTable 14: DDR3 I DD Specifications and Conditions – 2GB (Die Revision K)Values are for the MT41K256M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 2GbTable 15: DDR3 I DD Specifications and Conditions – 4GB (Die Revision E)Values are for the MT41K512M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 4GbTable 16: DDR3 I DD Specifications and Conditions – 4GB (Die Revision N)Values are for the MT41K512M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 4GbTable 17: DDR3 I DD Specifications and Conditions – 4GB (Die Revision P)Values are for the MT41K512M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 4GbSerial Presence-Detect EEPROMFor the latest SPD data, refer to Micron's SPD page: /spd .Table 18: Serial Presence-Detect EEPROM DC Operating ConditionsTable 19: Serial Presence-Detect EEPROM AC Operating ConditionsNotes:1.Guaranteed by design and characterization, not necessarily tested.2.To avoid spurious start and stop conditions, a minimum delay is placed between the fall-ing edge of SCL and the falling or rising edge of SDA.3.For a restart condition, or following a WRITE cycle.1GB, 2GB, 4GB (x64, SR) 204-Pin DDR3L SODIMMSerial Presence-Detect EEPROMModule DimensionsFigure 3: 204-Pin DDR3 SODIMM3.8 (0.150)1.8 (0.071)(2X)2.0 (0.079) RFront viewTYP45° 4XNotes:1.All dimensions are in millimeters (inches); MAX/MIN or typical (TYP) where noted.2.The dimensional diagram is for reference only.8000 S. Federal Way, P .O. Box 6, Boise, ID 83707-0006, Tel: 208-368-4000/products/support Sales inquiries: 800-932-4992Micron and the Micron logo are trademarks of Micron Technology, Inc.All other trademarks are the property of their respective owners.This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein.Although considered final, these specifications are subject to change, as further product development and data characterization some-times occur.1GB, 2GB, 4GB (x64, SR) 204-Pin DDR3L SODIMMModule DimensionsMouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:M icron Technology:MT8KTF25664HZ-1G6K1MT8KTF51264HZ-1G6P1MT8KTF51264HZ-1G9P1MT8KTF51264HZ-1G6N1。

1.常用元器件厂商商标及网址

AMLogic,Inc.VCD/DVD MPEG-1及MPEG-2视频/音频解码器制造商。

商标

厂商介绍

厂商网址

8X8 Inc.(8x8公司),位于美国加洲,以生产视频传输处理电路为主的专业厂商。

台灣類比科技股份公司,创立于1999年3月25日。拥有由具备10年以上IC相关产业经验。专长是电源管理IC设计及研发。产品內容包括了DC-DC PWM IC,DC-AC PWM IC,Battery Protector & Management IC,LDO,Switching Power Supervisor IC,and Buffer……等等。

Harris Semiconductor(哈利斯公司)以通信产业为主,但半导体涉及的门类越来越多,有多媒体电路、视像电路、各类通信电路、线性电路、数字逻辑电路、功率半导体、MOSFET、微处理机等等,并号称是CMOS器件的鼻祖。

Hewlett Packard Asia Pacific Ltd(惠普半导体)有“专”、“精”的特点,主产品有红外光电器件、光电耦合器件、微波射频器件、控制器件等,基本围绕HP的仪器仪表和打印机及成像产品。

Burr Brown CorporationBB(布尔-布朗公司),公司的各类转换电路、高精度模拟电路及各类专用处理电路模块等等一直在国际上享有盛名。(并入TI)

BROADCOM(美国博通)是提供用于语音、视频及数据的宽频数字传输的高集成度芯片方案的主要提供商。利用其专有技术和先进的设计方法,美国博通公司设计,开发,提供宽带通信市场的单芯片系统的解决方案。美国博通公司产品应用于电缆机顶盒,电缆调制解调器,高速局域网,城域网,广域网和光纤网,家庭网,VoIP,电信服务,住宅宽带网关,直播卫星和地面数字广播,xDSL,无线通信,系统I/O服务器方案以及网络处理。

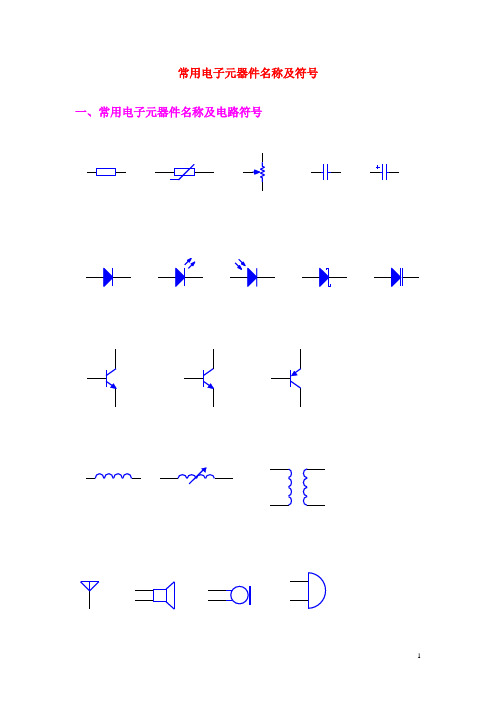

04-常用元器件名称符号和举例

常用电子元器件名称及符号一、常用电子元器件名称及电路符号

二、电路原理图设计--举例

例1 LED发光灯电路

图1 LED发光灯电路

例2三极管放大电路

图2 三极管放大电路

如图3所示,是由OP07组成的同相型放大器。

输出电压与输入电压的关系为

i 1P O 1U R R U ⋅⎪⎪⎭⎫ ⎝

⎛+= 式3-1

其增益为

1

p u 1R R A +

=, 或 )1

l g (20)dB (1

p u R R A += 式3-2

图3 由OP07组成的放大器

如图4所示,是由A741组成的反相型放大器。

输出电压与输入电压的关系为

i U R R U 1

p O =

式4-1

其增益为

1

p u R R A =

, 或 )l g (20)dB (1

p u R R A = 式4-2

图4 由A741组成的放大器

UA741CN ST Microelectronics \ST Operational Amplifier. .lntLib 意法半导体公司

例5 音频功率放大器电路

图5 音频功率放大器电路原理图

例6电源电路

图6 多路输出电源电路原理图

例7 流水灯电路

图7 流水灯电路原理图注:多种画法,如网络标号、总线等。

美光多款产品被禁 国内厂商受牵连

美光多款产品被禁国内厂商受牵连

本月初,因侵犯福州晋华专利,美国存储大厂美光多款相关产品在国内被禁。

虽说,此次禁售保护了福州晋华的利益,同时在贸易战的背景下,禁售美光也引起了国内网友的一片叫好。

实际上,在贸易全球化、各国之间专业化分工越来越细的当下,早已是你中有我,我中有你。

就像是之前中兴事件一样,虽然中兴损失惨重,但是一些美国供应商也因中兴禁令损失不小。

同样,此次美光被禁,不少国内的厂商也受到了波及,损失惨重。

7月3 日,福州晋华官方发布消息,因美光自有品牌产品涉嫌侵害晋华专利,福州市中级人民法院对美国芯片巨头美光发出“诉中禁令”,法院裁定美光半导体销售(上海)有限公司立即停止销售、进口十余款Crucial英睿达固态硬盘、内存条及相关芯片,并删除其网站中关于上述产品的宣传广告、购买链接等信息。

同时裁定美光半导体(西安)有限责任公司立即停止制造、销售、进口数款内存条产品。

根据资料显示,美光自有品牌Crucial英睿达MX300 2.5-inch SSD 525GB 固态硬盘、MX500系列的2TB、1TB、500GB、250GB 2.5英寸的固态硬盘以及包括Crucial DDR4 2133 8G笔记本内存条在内的数款DDR4笔记本与台式机内存条,及相关侵权芯片均遭到了禁售。

而随着美光的众多存储产品在国内被禁止生产和销售,美光在国内的一些。

arm架构_详谈ARM架构与ARM内核发展史

arm架构_详谈ARM架构与ARM内核发展史1、ARM架构与ARM内核1.1 ARM架构与内核简述⽬前为⽌,ARM总共发布8种架构:ARMv1、ARMv2、ARMv3、ARMv4、ARMv5、ARMv6、ARMv7 、ARMv8,这是ARM架构指令集的多个v版本。

基于不同的ARM架构可以设计出不同特点的内核处理器。

⽐如基于ARMv3架构设计出的处理器ARM6、ARM7,这两款处理器适⽤于不同的场景,硬件可能不同,但是架构指令集是⼀样的。

好⽐盖房⼦,刚开始因为⽔平低流⾏盖平房,这就是⼀种架构(ARMv5),然后这种平房架构你可以设计出⼀款独⽴卫⽣间的款式, 这叫ARM7内核。

然后其他⼈(芯⽚设计公司)想盖房⼦的就买你这个图纸去盖,接着过⼀段时间,有⼈觉得光独⽴卫⽣间还不够啊, 我还想有个⼩院⼦! 好吧,那ARM就满⾜你们的要求,出个带⼩院⼦的款式(ARM9)。

即ARMv1/2/3等是指令集的架构,ARM7/9等是基于架构设计出的内核处理器。

ARM的架构都是基于RISC指令集⽽设计的,内核是实现这⼀指令集的硬件架构的基础。

1.2 ARM各架构之间区别1.2.1 ARM版本Ⅰ:V1版架构该版架构只在原型机ARM1出现过,只有26位的寻址空间,没有⽤于商业产品。

其基本性能有:基本的数据处理指令(⽆乘法);基于字节、半字和字的Load/Store指令;转移指令,包括⼦程序调⽤及链接指令;供操作系统使⽤的软件中断指令SWI;寻址空间:64MB(226)。

1.2.2 ARM版本Ⅱ:V2版架构该版架构对V1版进⾏了扩展,例如ARM2和ARM3(V2a)架构。

包含了对32位乘法指令和协处理器指令的⽀持。

版本2a是版本2的变种,ARM3芯⽚采⽤了版本2a,是第⼀⽚采⽤⽚上Cache的ARM处理器。

同样为26位寻址空间,现在已经废弃不再使⽤。

V2版架构与版本V1相⽐,增加了以下功能:乘法和乘加指令;⽀持协处理器操作指令;快速中断模式;SWP/SWPB的最基本存储器与寄存器交换指令;寻址空间:64MB。

美光科技推出第三代低延时内存

美光科技推出第三代低延时内存

美光科技(Micron Technology, Inc)今天推出了第三代低延时DRAM (RLDRAM○R 3 内存)一种高带宽内存技术,能更有效的传输网络信息。

视频内容、移动应用和云计算的蓬勃发展,对网络基础设施提出了更高效的要求,

以便在线传输大量数据。

与前几代产品相比,美光新的RLDRAM 3 内存进一步提高了存储密度和速度,同时最大限度地减少了延迟,降低了功耗,在网络

应用中性能更好。

美光的DRAM 营销副总裁Robert Feurle 说:随着互联网内容消费的不断增长,人们日益需要有一种能支持网络流量增长的技术,美光的RLDRAM 3 内存满足了这种需求。

对于现有的RLDRAM 2,美光将继续提供最高水平的技术支持,并计划长期生产该产品。

此外,美光正将其RLDRAM 2 产品组合转入更先进的50nm 工艺,提高系统性能,降低功耗。

RLDRAM 3 内存产品特点

美光新的RLDRAM 3 内存的主要特点及优点有:

低延时:tRC 不足10 纳秒,是业界最低的随机存取延时

高密度:576Mb-1Gb,灵活性高,可用于多种设计

高速率:达2133Mb/s,数据存取速度更快

高能效:1.2V IO 和1.35V 内核电压,更省电

构建RLDRAM 合作伙伴网络

美光维持着庞大的合作伙伴网络,使其RLDRAM 存储解决方案能更方便地

与网络设备集成。

美光与其合作伙伴展开了广泛合作,为客户提供量身定制的

解决方案,优化网络系统性能。

作为这个价值生态系统的一部分,美光目前合。

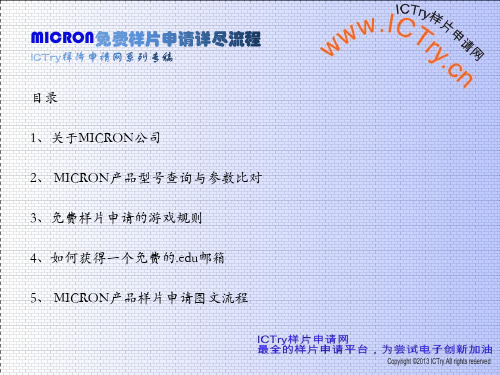

MICRON(美光)样片申请与经验(ICTry样片申请网独家系列)

产品信息确认页面出来 了,点击add后点击submit request,进入下一步。 笔者已经豁出去了,只 要不填银行卡信息就一路走 到黑。 对micron产品型号及参 数不清楚的童鞋,可以先登 陆ICTry样片申请网查询。

这里是您所进行的项目 调研以及地址和联系方式等 填写页面。 虽然我们到现在还不知 道自己在做什么,总之先往 下做吧。 这里需要注意的是 customer po和CR NUMBER 两个字段,分别是对应的海 关和10位数的海关编号,不 知道如何填写的童鞋可以加 ICTry群( 100565231 ), 群内有提供海关编号查询。

MICRON

目录 1、关于MICRON公司 2、 MICRON产品型号查询与参数比对 3、免费样片申请的游戏规则

4、如何获得一个免费的.edu邮箱

5、 MICRON产品样片申请图文流程

镁光科技有限公司(Micron Technology, Inc.)是高级半 导体解决方案的全球领先供应商之一。Micron通过全球化 的运营,制造并向市场推出DRAM、NAND闪存、CMOS 图像传感器、其它半导体组件以及存储器模块,用于前沿 计算、消费品、网络和移动便携产品。 镁光(Micron)身为世界第二大内存颗粒制造商,产品在 国内极少现身。这是因为镁光很少将自己的优质颗粒卖给 其他内存品牌,其极品颗粒供自家DIY品牌Crucial使用及 品牌机OEM市场,在IBM、HP、Dell等国际知名品牌都可 以看到其内存颗粒的产品,可知其稳定性及超频性好。 要问现在的内存超频颗粒哪种最火,答案毫无疑问是镁 光的小D9颗粒,优越的超频性能和相对低廉的售价让镁光 小D9颗粒的内存成为市场中的抢手货。

Hale Waihona Puke 1、适当适当的样片申请是指在选择芯片的时候,不要 贪大图贵,一切从实际情况出发,确保您申请 的样片和您所提供的用途一致。这样会使您的 申请理由充分,从而提高您申请的成功率。我 们的建议是只申请您当前需要的芯片,和您所 提供用途不相关的样片不要放入此次申请。 2、适量 适量的样片申请是指您申请样片时贴近您的实 际用量。这涉及到可申请样片的种类,也涉及 到每种样片可申请的数目。总之,在满足您需 求的前提下,适当的数量能使您申请成功的可 能性就会越大。 3、邮箱 我们刚才提到了免费样片只派发给两类人,所 以我们样片申请者注定了只有两类邮箱可用, 那就是公司邮箱()和教育 机构邮箱(),千万不要去 用第三种,或者第四种。

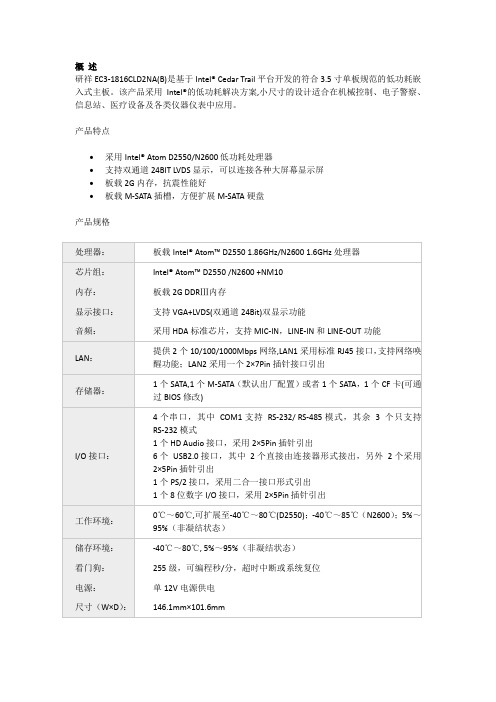

研祥3.5”第三代凌动系列单板电脑EC3-1816CLD2NA(B)

1个SATA,1个M-SATA(默认出厂配置)或者1个SATA,1个CF卡(可通过BIOS修改)

I/O接口:

4个串口,其中COM1支持RS-232/ RS-485模式,其余3个只支持RS-232模式

1个HD Audio接口,采用2×5Pin插针引出

6个USB2.0接口,其中2个直接由连接器形式接出,另外2个采用2×5Pin插针引出

支持双通道24BIT LVDS显示,可以连接各种大屏幕显示屏

板载2G内存,抗震性能好

板载M-SATA插槽,方便扩展M-SATA硬盘

产品规格

处理器:

板载Int 1.6GHz处理器

芯片组:

Intel® Atom™ D2550 /N2600 +NM10

电源:

单12V电源供电

尺寸(W×D):

146.1mm×101.6mm

概述

研祥EC3-1816CLD2NA(B)是基于Intel® Cedar Trail平台开发的符合3.5寸单板规范的低功耗嵌入式主板。该产品采用Intel®的低功耗解决方案,小尺寸的设计适合在机械控制、电子警察、信息站、医疗设备及各类仪器仪表中应用。

产品特点

采用Intel® Atom D2550/N2600低功耗处理器

1个PS/2接口,采用二合一接口形式引出

1个8位数字I/O接口,采用2×5Pin插针引出

工作环境:

0℃~60℃,可扩展至-40℃~80℃(D2550);-40℃~85℃(N2600);5%~95%(非凝结状态)

储存环境:

-40℃~80℃, 5%~95%(非凝结状态)

看门狗:

255级,可编程秒/分,超时中断或系统复位

内存:

板载2G DDRⅢ内存

Micron SEDs安装指南说明书

Technical NoteInstalling Micron SEDs in Windows 8 and 10IntroductionSelf-encrypting drives (SEDs) can provide an effective way of protecting sensitive datafrom falling into the wrong hands. This technical note describes the proper installationand operation of Windows BitLocker in hardware encryption mode. In some configura-tions it is possible for BitLocker to run in software encryption mode, but this can slowthe performance of the SED and the overall system. Proper installation will help maxi-mize the performance and data security of Micron's SEDs, which are designed for desk-top computing.Beginning with the M500 and continuing with the latest SED generations, Micron hasprovided AES-256-bit hardware encryption as a standard option on our SEDs. AES-256is state-of-the-art data encryption and is generally considered unbreakable by knowndecryption techniques (within reasonable time scales).Micron's SEDs conform to both the Trusted Computing Group (TCG) Security Subsys-tem Class (SSC) Opal Specification 2.0 and the IEEE-1667 specification, "Standard Pro-tocol for Authentication in Host Attachments of Transient Storage Devices." In satisfy-ing both of these specifications, Micron's SEDs conform to Microsoft's specification for"eDrive" under Windows 8 and Windows 10. The eDrive functionality enables the man-agement of hardware-encrypted storage devices under the versions of BitLocker foundin the Windows8 and 10 Enterprise and Professional editions.Note: For simplicity, references to "Windows 8" should be understood to apply to eitherWindows 8 or Windows 8.1. This document describes Windows 8 or 10 installation frommedia (DVD or USB thumb drive) or via disk duplication. Deployment from a networkor server is not discussed; that information can be found at , usingthe keyword search "encrypted hard drives."Micron SSD ModelsSome Micron SSD models do not include encryption at all, in which case BitLocker will implement software en-cryption. Other Micron SEDs comply only with the TCG Opal 2.0 protocol. If this is the case, then there are encryp-tion management solutions from Independent Software Vendors (ISV) which can address your data security con-cerns in place of BitLocker. If BitLocker is used, these Opal-only SEDs will be software encrypted because they do not fully comply with the eDrive protocol.Micron C400 SEDs are not compatible with the eDrive protocol, but are TCG Opal 1.0 compatible.Micron SSDs, which are included as original equipment in a computer system, may meet specific design require-ments by the PC manufacturers. Such SSDs or SEDs may not be covered by this technical note.Micron data center and enterprise-class SSDs follow a different encryption protocol, and are not discussed here. Figure 1: Part Marking for Encryption Devices (Example)MT FD D AK128M BF -1AN1ESMicron Technology Product Family Drive Interface Drive Form Factor Drive Density NAND Flash Type Product FamilyProduction StatusCustomer DesignatorFeature SetExtended Firmware FeaturesZ = Non-Encrypted1 = Contact factory2 = SED (eDrive capable)5 = SED (TCG Opal 2.0 only)Sector SizeNAND Flash ComponentBOM Revision2AB YYThe Role of Hardware Encryption in Data SecurityHardware encryption of data on a storage device is only part of an overall data security regime. Hardware encryption can protect "data at rest" on a storage device, especially when the device is lost or stolen and in a powered-off or hibernate mode. However,when the host computer is operating, all data are "in the clear" and vulnerable to intru-sion. Consequently, hardware encryption at the drive level is a complement to, rather than a substitute for, firewalls, virus protection software, and other methods of protect-ing against data intrusion.Security ModesMicron's SEDs support either the TCG Opal 2.0 specification or the ATA SECURITY FEA-TURE SET. The ATA security modes are generally initiated by system BIOS or by some universal extensible firmware interface (UEFI)-based systems in legacy mode. By speci-fication from the associated industry standards organizations, TCG Opal and ATA secur-ity are mutually exclusive. In other words, if one is enabled, the other is disabled. Thus,if the ATA SECURITY FEATURE SET is enabled by BIOS, then Windows will not be able to properly engage Micron's SED as a hardware-encrypted device. Instead, in this mode, software encryption may be engaged by BitLocker.For many systems, the ATA SECURITY FEATURE SET is an effective means of managing encryption without having to acquire an encryption management software package.Note: In the case of Micron's legacy C400 SED, TCG Opal 1.0 is supported, but the ATA security encryption functions are not.TCG Hardware Encryption in Windows 7Micron's SEDs can be effectively deployed in Windows 7. Note that Windows 7 BitLock-er does not support hardware-encrypted devices. However, Micron has worked with several independent software vendors to ensure compatibility, including Wave Systems ( ) and WinMagic ( ).Physical Security IDAll form factors of the M500 and newer SEDs provide what is known as a physical secur-ity ID (PSID) code on the serial number label of every SED. The PSID is a 32-character code which can be used to initiate an operation known as PSID REVERT. PSID REVERT may be used to recover the use of an SED when a password or authentication key is lost;however, PSID REVERT cannot be used to recover data from such a drive. PSID REVERT will initiate a cryptographic erase on the target SED, which changes the 256-bit encryp-tion key resident in hardware on the drive. This renders all of the user data on the drive unreadable. The process will then reset the drive to a factory new state, from which a new OS can be installed.Micron's Storage Executive software package includes a PSID REVERT function. Please see the User Guide for Storage Executive for more specific instructions. Additionally,several third-party tools are available which perform PSID REVERT, including tools from Wave Systems and WinMagic. The PSID, as printed on the Micron serial number label, includes several hyphens (-) for human readability. Do not include these hyphens when entering the PSID code into the revert tool.When doing an OS reinstall on a drive which had a previous installation of Window 8 or Windows 10, it may be necessary to execute a PSID REVERT command on the drive be-TN-FD-28: Installing Micron SEDs in Windows 8 and 10The Role of Hardware Encryption in Data Securityfore proceeding to the following steps, in order to reinitialize the SED to a state wherethe new OS can be successfully installed.Windows 8 or 10 InstallationRequirementsThe setup and installation steps are the same for Windows 8 and Windows 10.Micron's SEDs meet the device requirements for implementing a hardware encryptionsystem, but there are also requirements at the host computer. When the SED is config-ured as an operating system drive, the following preconditions must be met:•The host computer should be at a minimum of UEFI 2.3.1 and should have theEFI_STORAGE_SECURITY_COMMAND_PROTOCOL defined. This enables securityprotocol commands to be sent to and from the SED. Please contact the manufacturerof your host computer to ensure that this requirement is met.•Secure Boot must be enabled.•The host computer must always boot from UEFI. Any “compatibility” or “legacy” bootmode must be disabled. We recommend putting the system in UEFI-only mode be-fore installing the Micron SED.•The compatibility support module (CSM) must be disabled, if it is available.•The drive must be in an uninitialized state with all security modes inactive. (This re-fers to the security state of the SED under the TCG and ATA protocols.) If the drive hasbeen previously initialized, you may need to refer to instructions from the BIOS mak-er or any previous encryption software which may have been used in order to returnthe SED to an uninitialized state. The PSID REVERT function may also be needed toreinitialize the SED.•Windows 8 and 10 cannot manage encryption on SEDs that are attached to the hostcomputer via a RAID controller.•A trusted platform module (TPM) on the host computer is not required in order torun hardware encryption. However, a TPM can provide additional data security func-tions, such as mating the SED to the host system so it cannot be operated in any otherhost computer. Instructions for using a TPM should be obtained from the manufac-turer of the host computer. Installation on a host computer without a TPM may re-quire using a USB thumb drive as a key. (See Microsoft's Windows documentation formore details.)Configuring the Host SystemIt is recommended that the host system UEFI be configured to properly accept the SEDbefore physically installing it, as outlined in the example below. Details of the systemsetup will vary from system to system, as will the names of various functions. However,they are similar enough that a single example should be sufficient. For details on specif-ic UEFI setups, contact your computer's manufacturer.Enabling Secure BootMicrosoft Secure Boot is a requirement to run any Windows 8 or 10 system. Any com-puter that has been configured from the factory for Windows 8 or 10 will already haveSecure Boot enabled. If the host system was originally configured for Windows 7 or aprevious operating system, check to ensure that Secure Boot is enabled, as shown be-low.UEFI Boot Mode/CSM SupportThe host computer system must be in UEFI-only mode, as shown below. Typically, theCSM will be automatically disabled in UEFI-only mode; however, this should be verifiedand the CSM should be disabled if necessary.Installing Windows 8 or 10The most straightforward method of implementing hardware encryption is to perform aclean, new installation of the operating system. BitLocker versions in the Enterprise andProfessional editions of Windows 8 or 10 support hardware encryption on SEDs. Nospecial steps are needed for this function; simply follow the normal OS installationprocess described by Microsoft.After the OS is installed, proceed to the Enable BitLocker section.System CloningBecause Micron SEDs support eDrive, activating BitLocker creates special partitions,which are required to put the eDrive features in effect. When an eDrive-activated SSD iscloned, these special partitions may not be properly copied to the target drive. The tar-get drive may function, but this is not considered a valid process and it may cause latentperformance problems.If the source disk has been encrypted using software encryption in Bitlocker, first en-sure that BitLocker is turned off before initiating the image clone to a Micron SED. Ifusing BitLocker in software encryption mode on the source system, a decryption proc-ess will be required to turn off BitLocker. This can take several hours, depending on theamount of user and OS data on the drive.Enable BitLockerFollow the steps below to enable BitLocker.•Press the Windows key (usually between <Ctrl> and <Alt>); then type This PC andpress Enter.•Right-click on the icon for the system drive and select Turn on BitLocker from thepop-up menu. (Note that Windows 10 displays will look slightly different, but arefunctionally the same.)•Next, a status box confirming that BitLocker is configuring will display, along with a status bar. This will complete momentarily.•Select one of Microsoft's options for saving your recovery key. While Micron has no preferred option here, do not neglect this step. In some circumstances, this may be the only way to recover data from your SSD. Micron has no factory backdoor methods by which to recover data if an authentication key or password is lost. Once the key is saved, select Next to continue.•BitLocker will ask, "Are you ready to encrypt this drive?" After you click Continue, a system restart will be required to complete the process.•After the reboot is complete, you will see from the BitLocker padlock icon on your sys-tem drive that BitLocker is enabled.WARNING: After this first reboot, if a status window with a progress bar indicating thatencryption is underway displays, then the system is most likely in software encryptionmode, which means one of the preceding steps was not correctly completed. In particu-lar, double-check that the pre-boot settings for Secure Boot and UEFI-Only Boot are en-abled and that the CSM is disabled.Recommended SettingsMicron recommends that the system be placed in hibernate mode when the system isnot in use, in particular, when the notebook computer's lid is closed. This ensures thatthe SED fully enters the locked mode. To do so, follow these steps:•Press the Windows key and then type Change what the power buttons do; then pressEnter.•Select the power-down options as shown below.•Hibernate is preferred over sleep mode for both security and power consumptionpurposes. Recovery time may be compromised a bit, but SSDs can recover from hi-bernate significantly faster than HDDs. In fact, after a clean shutdown, a Micron drivewill typically recover from hibernate and be ready to compute in under 0.2 seconds.ConclusionWhen installed properly and operated in hardware encryption mode, Windows 8 and 10BitLocker enables nearly seamless and transparent management of Micron's M500 andnewer SEDs.Revision HistoryRev. A – 08/15•Updated to include Windows 10 informationRev. A – 07/14•Initial release8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-4000/products/support Sales inquiries: 800-932-4992Micron and the Micron logo are trademarks of Micron Technology, Inc.All other trademarks are the property of their respective owners.。

Micron内存颗粒

Micron内存颗粒Micron(美光)内存颗粒的容量辨识相对于三星来说简单许多。

下面就以MT48LC 16M8A2TG-75这个编号来说明美光内存的编码规则。

含义:MT——Micron的厂商名称。

48——内存的类型。

48代表SDRAM;46 代表DDR。

LC——供电电压。

LC代表3V;C 代表5V;V 代表2.5V。

16M8——内存颗粒容量为128Mbits,计算方法是:16M(地址)×8位数据宽度。

A2——内存内核版本号。

TG——封装方式,TG即TSOP封装。

-75——内存工作速率,-75即133MHz;-65即150MHz。

实例:一条Micron DDR内存条,采用18片编号为MT46V32M4-75的颗粒制造。

该内存支持ECC功能。

所以每个Bank是奇数片内存颗粒。

其容量计算为:容量32M ×4bit ×16 片/ 8=256MB(兆字节)。

内存条的型号识别知识内存条一般都有标注大小,如果没有就要看颗粒的编号了,给个你看看:samsung内存例:samsungk4h280838b-tcb0第1位——芯片功能k,代表是内存芯片。

第2位——芯片类型4,代表dram。

第3位——芯片的更进一步的类型说明,s代表sdram、h代表ddr、g代表sgram。

第4、5位——容量和刷新速率,容量相同的内存采用不同的刷新速率,也会使用不同的编号。

64、62、63、65、66、67、6a代表64mbit的容量;28、27、2a代表128mbit的容量;56、55、57、5a代表256mbit的容量;51代表512mbit的容量。

第6、7位——数据线引脚个数,08代表8位数据;16代表16位数据;32代表32位数据;64代表64位数据。

第11位——连线“-”。

第14、15位——芯片的速率,如60为6ns;70为7ns;7b为7.5ns(cl=3);7c为7.5ns(cl=2);80为8ns;10为10ns(66mhz)。

实验三 键盘扫描

实验三键盘扫描&8位7段码管显示实验一实验目的1.进一步熟悉用Quartus II开发SOPC的基本流程。

2.进一步掌握PIO外设的使用方法。

3.熟悉对PIO的更复杂的操作过程。

4.掌握驱动8位七段码管的方法。

二硬件需求1.EDA/SOPC实验箱一台。

三实验原理实验中要用到4×4键盘,系统需要完成4×4键盘的扫描,确定有键按下后需要获取其键值,根据预先存放的键值表,逐个进行对比,从而进行按键的识别,并将相应的按键值进行显示。

键盘扫描的实现过程如下:对于4×4键盘,通常连接为4行、4列,因此要识别按键,只需要知道是哪一行和哪一列即可,为了完成这一识别过程,首先输出4列中的第一列为低电平,其它列为高电平,然后读取行值;然后再输出4列中的第二列为低电平,读取行值,依此类推,不断循环。

系统在读取行值的时候会自动判断,如果读进来的行值全部为高电平,则说明没有按键按下,否则如果读进来的行值发现不全为高电平,则说明键盘整列中必定有至少一个按键按下,读取此时的行值和当前的列值,即可判断到当前的按键位置。

获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管显示。

8位七段码管的显示是在程序中定时扫描显示的,为了使显示的过程简化,可以在程序中开辟8个存储区,用于存放8个七段码管对应值,然后每按下按键一次,则相应的值出现在最右边的七段码管上,原先的显示的值依次左移。

为了完成键盘的扫描和七段码管的正确显示,必须在原来CPU模块的基础上再加入一个定时器模块,用以产生周期性中断,在中断服务程序中完成键盘的扫描以及七段码管的扫描。

四实验内容本实验要完成的内容是设计一个CPU模块,该CPU需要加入一个定时器模块,用以产生周期性中断进行键盘扫描和七段码管的扫描显示。

实验要求能够在按下按键时获取其键值,然后在8个七段码管上正确显示按下的键值,每按键一次,原先显示的值整体左移,新的键值出现在8个七段码管的最右边。

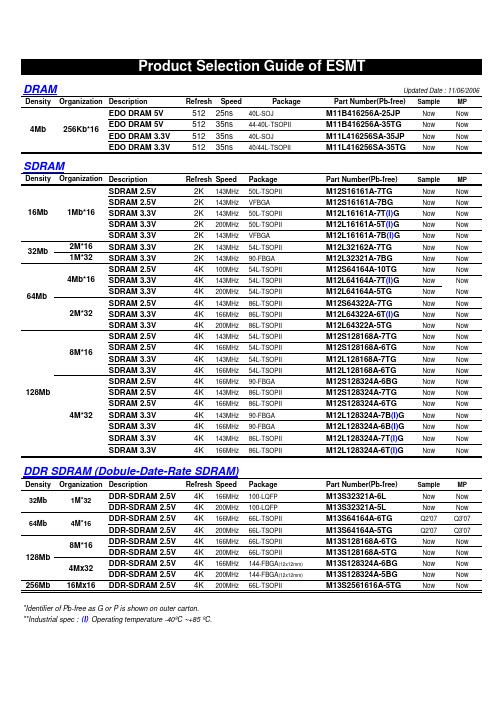

Micron 产品数据手册说明书

DRAMUpdated Date : 11/06/2006DensityOrganization DescriptionRefreshSpeedPackagePart Number(Pb-free)Sample MP EDO DRAM 5V 51225ns 40L-SOJ M11B416256A-25JP Now Now EDO DRAM 5V 51235ns 44-40L-TSOPII M11B416256A-35TG Now Now EDO DRAM 3.3V 51235ns 40L-SOJ M11L416256SA-35JP Now Now EDO DRAM 3.3V 51235ns 40/44L-TSOPIIM11L416256SA-35TGNowNowSDRAMDensityOrganization DescriptionRefresh SpeedPackagePart Number(Pb-free)Sample MP SDRAM 2.5V 2K 143MHz 50L-TSOPII M12S16161A-7TG Now Now SDRAM 2.5V 2K 143MHz VFBGA M12S16161A-7BG Now Now SDRAM 3.3V 2K 143MHz 50L-TSOPII M12L16161A-7T (I)G Now Now SDRAM 3.3V 2K 200MHz 50L-TSOPII M12L16161A-5T (I)G Now Now SDRAM 3.3V 2K 143MHz VFBGA M12L16161A-7B (I)G Now Now 2M*16SDRAM 3.3V 2K 143MHz 54L-TSOPII M12L32162A-7TG Now Now 1M*32SDRAM 3.3V 2K 143MHz 90-FBGA M12L32321A-7BG Now Now SDRAM 2.5V 4K 100MHz 54L-TSOPII M12S64164A-10TG Now Now SDRAM 3.3V 4K 143MHz 54L-TSOPII M12L64164A-7T (I)G Now Now SDRAM 3.3V 4K 200MHz 54L-TSOPII M12L64164A-5TG Now Now SDRAM 2.5V 4K 143MHz 86L-TSOPII M12S64322A-7TG Now Now SDRAM 3.3V 4K 166MHz 86L-TSOPII M12L64322A-6T (I)G Now Now SDRAM 3.3V 4K 200MHz 86L-TSOPII M12L64322A-5TG Now Now SDRAM 2.5V 4K 143MHz 54L-TSOPII M12S128168A-7TG Now Now SDRAM 2.5V 4K 166MHz 54L-TSOPII M12S128168A-6TG Now Now SDRAM 3.3V 4K 143MHz 54L-TSOPII M12L128168A-7TG Now Now SDRAM 3.3V 4K 166MHz 54L-TSOPII M12L128168A-6TG Now Now SDRAM 2.5V 4K 166MHz 90-FBGA M12S128324A-6BG Now Now SDRAM 2.5V 4K 143MHz 86L-TSOPII M12S128324A-7TG Now Now SDRAM 2.5V 4K 166MHz 86L-TSOPII M12S128324A-6TG Now Now SDRAM 3.3V 4K 143MHz 90-FBGA M12L128324A-7B (I)G Now Now SDRAM 3.3V 4K 166MHz 90-FBGA M12L128324A-6B (I)G Now Now SDRAM 3.3V 4K 143MHz 86L-TSOPII M12L128324A-7T (I)G Now Now SDRAM 3.3V4K166MHz86L-TSOPIIM12L128324A-6T (I)GNowNowDDR SDRAM (Dobule-Date-Rate SDRAM)Density Organization DescriptionRefresh SpeedPackagePart Number(Pb-free)Sample MP DDR-SDRAM 2.5V 4K 166MHz 100-LQFP M13S32321A-6L Now Now DDR-SDRAM 2.5V 4K 200MHz 100-LQFP M13S32321A-5L Now Now DDR-SDRAM 2.5V 4K 166MHz 66L-TSOPII M13S64164A-6TG Q2'07Q3'07DDR-SDRAM 2.5V 4K 200MHz 66L-TSOPII M13S64164A-5TG Q2'07Q3'07DDR-SDRAM 2.5V 4K 166MHz 66L-TSOPII M13S128168A-6TG Now Now DDR-SDRAM 2.5V 4K 200MHz 66L-TSOPII M13S128168A-5TG Now Now DDR-SDRAM 2.5V 4K 166MHz 144-FBGA (12x12mm)M13S128324A-6BG Now Now DDR-SDRAM 2.5V 4K 200MHz 144-FBGA (12x12mm)M13S128324A-5BG Now Now 256Mb16Mx16DDR-SDRAM 2.5V 4K200MHz66L-TSOPIIM13S2561616A-5TGNowNow*Identifier of Pb-free as G or P is shown on outer carton.**Industrial spec : (I) Operating temperature -40ºC ~+85 ºC.2M*3264Mb4Mb*1632Mb4Mb 256Kb*161Mb*1616Mb 128Mb8M*164Mx324M*32128Mb8M*1632Mb 64Mb1M*324M*16Mobile SDRAMDensityOrganizationDescriptionRefresh Speed Package & MCPPart Number(Pb-free)Sample MP Mobile SDRAM 2.5V4K 100MHz 50L-TSOPII M52S16161A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 125MHz 50L-TSOPII M52S16161A-8T (I)G Now Now Mobile SDRAM 1.8V4K 100MHz50L-TSOPIIM52D16161A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54L-TSOPII M52S32162A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54-FBGA M52S32162A-10B (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 54L-TSOPII M52S32162A-7.5T (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 54-FBGA M52S32162A-7.5B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D32162A-10T (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54-FBGA M52D32162A-10B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D32162A-7.5T (I)G Now Now Mobile SDRAM 1.8V 4K 133MHz 54-FBGA M52D32162A-7.5B (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 90-FBGA M52S32321A-10B (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 90-FBGA M52S32321A-7.5B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 90-FBGA M52D32321A-10B (I)G Now Now Mobile SDRAM 1.8V 4K 133MHz 90-FBGA M52D32321A-7.5B (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54L-TSOPII M52S64164A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 54-FBGA M52S64164A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 54L-TSOPII M52S64164A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 54-FBGA M52S64164A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D64164A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54-FBGA M52D64164A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D64164A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 133MHz 54-FBGA M52D64164A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 86L-TSOPII M52S64322A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 90-FBGA M52S64322A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 86L-TSOPII M52S64322A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 90-FBGA M52S64322A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 86L-TSOPII M52D64322A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 90-FBGA M52D64322A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 86L-TSOPII M52D64322A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V4K133MHz 90-FBGAM52D64322A-7.5B (I)GQ2 '07Q3 '07*Identifier of Pb-free as G or P is shown on outer carton.**Industrial spec : (I) Operating temperature -40ºC ~+85 ºC.64Mb4Mx162Mx32(1)All Mobile functions are included : PASR,TCSR,DS,Deep power down mode.(2)Max. Icc6 : Self-refresh current with full bank in 70 ºC .1Mx16Max. Icc6= 75uA (1.8V)16Mb32Mb2Mx161Mx32。

镁光 3800频率内存时序电压

一. 镁光(Micron)3800频率内存简介镁光(Micron)3800频率内存是一种高性能内存,采用了先进的技术和工艺,具有较高的时序电压和频率性能。

3800频率内存在计算机硬件领域中具有重要意义,可以提高计算机系统的运行速度和稳定性,因此受到了广泛的关注和应用。

二. 内存时序电压的重要性内存的时序电压是指内存芯片在特定时序下所需的工作电压。

时序电压的大小直接影响着内存芯片的性能和稳定性。

合理的时序电压可以保证内存芯片的正常工作,提高其稳定性和耐受性。

而高频率内存通常需要更高的时序电压来保证其正常工作和性能发挥。

三. 镁光3800频率内存的时序电压特点1. 高时序电压镁光3800频率内存采用了较高的时序电压,以保证其在高频率下的正常工作和稳定性。

3800频率内存的时序电压通常在1.35V至1.5V之间,略高于普通内存的时序电压要求。

这种高时序电压可以有效提升内存芯片的运行速度和性能表现。

2. 高频率性能3800频率内存具有较高的频率性能,可以在较高的频率下工作。

高频率内存可以提高计算机的数据读写速度,加快数据传输和处理的速度,从而提升计算机的整体性能。

而高时序电压可以保证高频率内存的正常工作,为其性能发挥提供保障。

四. 高时序电压的影响1. 提升性能高时序电压可以提升内存芯片的性能和工作速度,加快数据的读写和传输速度,提高计算机系统的响应速度和处理效率。

这对于需要处理大量数据和复杂计算任务的应用和场景具有重要意义,如科学计算、大数据分析等。

2. 稳定性保障高时序电压能够保证内存芯片在高频率下的稳定工作。

对于需要长时间运行和高负载运算的场景,如服务器和工作站等,内存的稳定性至关重要。

高时序电压可以有效提高内存的稳定性和耐受性,降低故障和错误率,保证系统的可靠性和稳定运行。

五. 高时序电压的适用场景1. 游戏电竞对于要求高性能的游戏电竞玩家来说,高时序电压的内存可以提供更快的数据读写速度和稳定的运行性能,提高游戏画面流畅度和响应速度,带来更好的游戏体验。

镁光和三星内存哪个好

镁光和三星内存哪个好镁光和三星内存哪个好镁光和三星内存哪个好呢?小编来像你介绍!下面由店铺给你做出详细的镁光和三星内存介绍!希望对你有帮助!镁光和三星内存介绍三三星 (samsung) 内存工艺整体上要领先其他内存颗粒制造厂。

三星的半导体晶片在存储行业内名声显赫,他们不仅有最先进的半导体技术,在存储晶片方面也走在世界的前端。

从全球的市场份额来看,三星也绝对称的上是大哥级别的!金士顿、威刚、海盗船等一线内存品牌都普遍使用三星的原厂颗粒以保证产品的性能。

三星金条依靠自家生产的内存颗粒一直保持着高品质内存的形象,价格比同规格其他品牌的产品也要略高。

镁光(micron) 曾经被叫做美凯龙,是世界第二大内存颗粒制造商,但其产品在国内却不多见镁光和三星内存介绍三这两个品牌的内存条,一样好,随便选哪个都可以。

如有特殊需求,可考虑如下特点:1、三星和金士顿,都以稳定性好和兼容性好而著称。

都是好内存。

2、金士顿更偏重于兼容性。

所以,不惜损失性能去最大程度的提高兼容性。

因此,速度稍慢,但兼容性最好。

3、三星的内存,属于兼顾。

在保持比较好的兼容性的同时,稍微兼顾一下性能。

超频性能多数情况下要比金士顿好。

镁光和三星内存介绍三:2个厂商看谁的产品好,不光是从质量上来说的。

还看谁的售后好。

当然内存都是3年之内不会坏的,但是你们知道吗3年后这东西很容易报销。

5年以上的很少。

所以,我认为还是金士顿的好,虽然金士顿使用的是三星的颗粒,但是在高端市场上金士顿的研发组还是最强的。

最早看见金士顿的生产了16GB单条的内存条。

售价2000美元。

三星就不行。

但是,说实话,买内存,金士顿的假的比真的还多,也不能说是假的,只能说水货多。

很多。

所以这个问题,楼主问的让大家都不知所云。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。