LD7126中文资料

W681512S中文资料

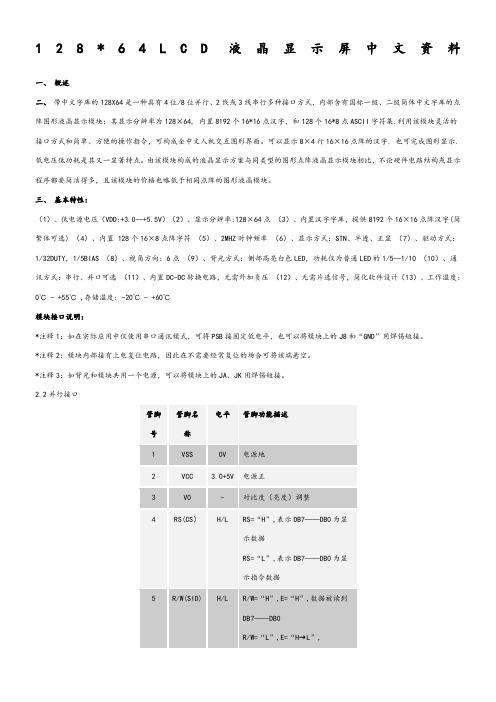

4. TABLE OF CONTENTS

1. GENERAL DESCRIPTION.................................................................................................................. 2 2. FEATURES ......................................................................................................................................... 2 3. BLOCK DIAGRAM .............................................................................................................................. 3 4. TABLE OF CONTENTS ...................................................................................................................... 4 5. PIN CONFIGURATION ....................................................................................................................... 6 6. PIN DESCRIPTION ............................................................................................................................. 7 7. FUNCTIONAL DESCRIPTION............................................................................................................ 8

ICL7129CPL中文资料

ICL7129

August 1997

41/2 Digit LCD, Single-Chip A/D Converter

Features

• ±19,999 Count A/D Converter Accurate to ±4 Count • 10µV Resolution on 200mV Scale • 110dB CMRR • Direct LCD Display Drive • True Differential Input and Reference • Low Power Consumption • Decimal Point Drive Outputs • Overrange and Underrange Outputs • Low Battery Detection and Indication • 10:1 Range Change Input

LOW BATTERY CONTINUITY

OR UR DP2 DP1 DP3 DP3

V+ 5pF (MICA)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

ICL7129ຫໍສະໝຸດ 120kHz4039

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

560pF

1.2kΩ

144 43 42 41 40

39

38

37 36

AD5689R AD5687R AD5689 AD5687 AD5697R nanoDAC+双通道数

Document FeedbackTechnical Support One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Information furnished by Analog Devices is believed to be accurate and reliable. However , noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.ADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最新英文版数据手册。

R ev. 0Tel: 781.329.4700 ©2013Analog Devices, Inc. All rights reserved.功能框图图1.表1. 双通道nanoDAC+器件接口基准电压源 16位 12位 SPI 内部 AD5689R AD5687R 外部 AD5689AD5687I 2C 内部 AD5697R外部SCLV LOGICSDAA1A0INPUT REGISTER DAC REGISTER STRING DAC ABUFFERV OUT AINPUT REGISTER DAC REGISTER STRING DAC BBUFFERV OUT BV REFGNDV DDPOWER-DOWN LOGICPOWER-ON RESET GAIN =×1/×2I N T E R F A C E L O G I CRSTSEL GAINLDAC RESET AD5697R2.5VREFERENCE11253-001产品特性低漂移2.5 V 基准电压源:2 ppm/°C(典型值) 小型封装:3 mm × 3 mm 、16引脚LFCSP 总不可调整误差(TUE):±0.1% FSR(最大值)偏置误差:±1.5 mV(最大值) 增益误差:±0.1% FSR(最大值)高驱动能力:20 mA ,0.5 V(供电轨)用户可选增益:1或2(GAIN 引脚)复位到零电平或中间电平(RSTSEL 引脚)1.8 V 逻辑兼容低毛刺:0.5 nV-sec400 kHz I2C 兼容型串行接口鲁棒的HBM(额定值为3.5 kV)和FICDM ESD(额定值为1.5 kV)性能低功耗:3.3 mW(3 V)2.7 V 至5.5 V 电源温度范围:−40°C 至+105°C应用基站功率放大器过程控制(可编程逻辑控制器[PLC] I/O 卡)工业自动化数据采集系统概述AD5697R 属于nano DAC+™系列,是一款低功耗、双通道、12位缓冲电压输出数模转换器(DAC)。

关于LM7806详细中文资料

关于LM7806详细中文资料目录1.lm7806介绍2.实际应用3.引脚序号、引脚功能4.lm7806应用电路5.7806电参数三端稳压集成电路lm7806。

电子产品中,常见的三端稳压集成电路有正电压输出的lm78 ×× 系列和负电压输出的lm79××系列。

顾名思义,三端IC是指这种稳压用的集成电路,只有三条引脚输出,分别是输入端、接地端和输出端。

它的样子象是普通的三极管,TO- 220 的标准封装,也有lm9013样子的TO-92封装。

1.lm7806介绍用lm78/lm79系列三端稳压I C来组成稳压电源所需的外围元件极少,电路内部还有过流、过热及调整管的保护电路,使用起来可靠、方便,而且价格便宜。

该系列集成稳压IC型号中的lm78或lm79后面的数字代表该三端集成稳压电路的输出电压,如lm7806表示输出电压为正6V,lm7909表示输出电压为负9V。

因为三端固定集成稳压电路的使用方便,电子制作中经常采用。

最大输出电流1.5A,LM78XX系列输出电压分别为5V;6V;8V;9V;10V;12V;15V;18V;24V。

2.实际应用在实际应用中,应在三端集成稳压电路上安装足够大的散热器(当然小功率7806IC内部电路图.的条件下不用)。

当稳压管温度过高时,稳压性能将变差,甚至损坏。

当制作中需要一个能输出1.5A以上电流的稳压电源,通常采用几块三端稳压电路并联起来,使其最大输出电流为N个1.5A,但应用时需注意:并联使用的集成稳压电路应采用同一厂家、同一批号的产品,以保证参数的一致。

另外在输出电流上留有一定的余量,以避免个别集成稳压电路失效时导致其他电路的连锁烧毁。

在lm78** 、lm79 ** 系列三端稳压器中最常应用的是TO-220 和TO-202 两种封装。

LD7552芯片内部结构及工作原理

一、LD7552芯片内部结构及工作原理图1是LD7552的内部结构图。

主要由欠压锁定电路(UVLO)、工作振荡器和绿色模式振荡器、前沿消隐电路、斜率补偿电路、末级驱动电路等组成。

欠压锁定电路也叫低压关断模式,芯片内部的电压检测器对供电电压进行监测,以确保电压当供电电压低于IC的开启门限电压时进行保护。

欠压关断模式可保证IC在供电电压不足时不至于被损坏。

也保证后级电路不至于因为激励不足而出问题。

对于LD7552来讲,供电电压低于11.4V时,欠压保护模式启动,只有当供电电压再次恢复到16V以上时,芯片才重新开始输出激励信号。

LD7552内部有两个振荡器,一个是正常工作振荡器,一个是绿色模式振荡器。

在正常工作时绿色模式振荡器不启动,确保输出频率和波形的稳定。

在待机或者空载情况下,绿色模式振荡器启动,降低开关频率,有效减少功耗,降低温度,能够确保在待机状态系统功耗小于0.3W以下,符合欧洲节能标准要求。

前沿消隐电路是对反馈电流信号和电压信号的峰值进行监测,在250ns内不予通过,防止控制电路误触发造成输出大幅度波动。

+ b4 B/ t$ ~) B5 _# M由于电流控制模式的固有缺陷,在占空比达到50%时,斜率补偿是必要的,因此芯片内置了斜坡振荡器,进行斜率补偿,简化了外围电路设计。

引脚功能介绍:3 i+ [( @6 Q" D①接地。

内部电路公共接地端。

②比较电压反馈引脚。

(补偿过程类似uc384x 芯片),由连接的光电耦合器反馈电压信号,实现控制。

同时该脚还兼任开关机控制功能,当反馈电压低于 1.2V 时,系统处于待机模式。

, {7 H& O; F, X! l7 J2 G5 p. h7 K③电源供电。

LD7552的典型供电电压是36V。

外接高压启动电阻和高频变压器的反馈供电。

在启动瞬间,由于供电电压低于UVLO 的门槛电压,所以没有激励脉冲产生,通过高压启动电阻为LD7552提供必要的启动电流(25μA),直到高频变压器的辅助绕组产生反馈供电。

ADC12062CIVF中文资料

TL H 11490ADC12062 12-Bit1 MHz 75 mW A D Converter with Input Multiplexer and Sample HoldDecember1994 ADC1206212-Bit 1MHz 75mW A D Converterwith Input Multiplexer and Sample HoldGeneral DescriptionUsing an innovative multistep conversion technique the12-bit ADC12062CMOS analog-to-digital converter digitizessignals at a1MHz sampling rate while consuming a maxi-mum of only75mW on a single a5V supply TheADC12062performs a12-bit conversion in three lower-res-olution‘‘flash’’conversions yielding a fast A D without thecost and power dissipation associated with true flash ap-proachesThe analog input voltage to the ADC12062is tracked andheld by an internal sampling circuit allowing high frequencyinput signals to be accurately digitized without the need foran external sample-and-hold circuit The multiplexer outputis available to the user in order to perform additional exter-nal signal processing before the signal is digitizedWhen the converter is not digitizing signals it can be placedin the Standby mode typical power consumption in thismode is100m WFeaturesY Built-in sample-and-holdY Single a5V supplyY Single channel or2channel multiplexer operationY Low Power Standby modeKey SpecificationsY Sampling rate1MHz(min)Y Conversion time740ns(typ)Y Signal-to-Noise Ratio f IN e100kHz69 5dB(min)Y Power dissipation(f s e1MHz)75mW(max)Y No missing codes over temperature GuaranteedApplicationsY Digital signal processor front endsY InstrumentationY Disk drivesY Mobile telecommunicationsY Waveform digitizersBlock DiagramTL H 11490–1 Ordering InformationIndustrial(b40 C s T A s a85 )PackageADC12062BIV V44Plastic Leaded Chip CarrierADC12062BIVF VGZ44A Plastic Quad Flat PackageADC12062CIV V44Plastic Leaded Chip CarrierADC12062CIVF VGZ44A Plastic Quad Flat PackageADC12062EVAL Evaluation BoardTRI-STATE is a registered trademark of National Semiconductor CorporationC1995National Semiconductor Corporation RRD-B30M75 Printed in U S AAbsolute Maximum Ratings(Notes1 2)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage(V CC e DV CC e AV CC)b0 3V to a6V Voltage at Any Input or Output b0 3V to V CC a0 3V Input Current at Any Pin(Note3)25mA Package Input Current(Note3)50mA Power Dissipation(Note4)875mW ESD Susceptibility(Note5)2000V Soldering Information(Note6)V Package Infrared 15seconds a300 C VF PackageVapor Phase(60seconds)a215 C Infrared(15seconds)a220 C Storage Temperature Range b65 C to a150 C Maximum Junction Temperature(T JMAX)150 C Operating Ratings(Notes1 2)Temperature Range T MIN s T A s T MAX ADC12062BIV ADC12062CIVADC12062BIVF ADC12062CIVF b40 C s T A s a85 C Supply Voltage Range(DV CC e AV CC)4 5V to5 5VConverter Characteristics The following specifications apply for DV CC e AV CC e a5V V REF a(SENSE)e a4 096V V REF b(SENSE)e AGND and f s e1MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX all other limits T A e T J e a25 CSymbol Parameter ConditionsTyp Limit Units (Note7)(Note8)(Limit)Resolution12BitsDifferential Linearity Error T A e25 C g0 4g0 8LSB(max)T MIN to T MAX g0 95LSB(max)Integral Linearity Error T MIN to T MAX(BIV Suffix)g0 4g1 0LSB(max) (Note9)TA e a25 C(CIV Suffix)g0 4g1 0LSB(max)T MIN to T MAX(CIV Suffix)g1 5LSB(max) Offset Error T MIN to T MAX(BIV Suffix)g0 3g1 25LSB(max)T A e a25 C(CIV Suffix)g0 3g1 25LSB(max)T MIN to T MAX(CIV Suffix)g2 0LSB(max) Full Scale Error T MIN to T MAX(BIV Suffix)g0 2g1 0LSB(max)T A e a25 C(CIV Suffix)g0 2g1 0LSB(max)T MIN to T MAX(CIV Suffix)g1 5LSB(max) Power Supply Sensitivity DV CC e AV CC e5V g10%g1 0LSB(max) (Note15)R REF Reference Resistance750500X(min) 1000X(max)V REF(a)V REF a(SENSE)Input Voltage AV CC V(max)V REF(b)V REF b(SENSE)Input Voltage AGND V(min)V IN Input Voltage Range To V IN1 V IN2 or ADC IN AV CC a0 05V V(max)AGND b0 05V V(min) ADC IN Input Leakage AGND to AV CC b0 3V0 13m A(max) C ADC ADC IN Input Capacitance25pFMUX On-Channel Leakage AGND to AV CC b0 3V0 13m A(max)MUX Off-Channel Leakage AGND to AV CC b0 3V0 13m A(max) C MUX Multiplexer Input Cap7pFMUX Off Isolation f IN e100kHz92dB2Dynamic Characteristics(Note10)The following specifications apply for DV CC e AV CC e a5V V REF a(SENSE)e a4 096V V REF b(SENSE)e AGND R S e25X f IN e100kHz 0dB from fullscale and f s e1MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX all other limits T A e T J e a25 CSymbol Parameter ConditionsTyp Limit Units (Note7)(Note8)(Limit)SINAD Signal-to-Noise Plus T MIN to T MAX7168 0dB(min) Distortion RatioSNR Signal-to-Noise Ratio T MIN to T MAX7269 5dB(min) (Note11)THD Total Harmonic Distortion T A e a25 C b82b74dBc(max) (Note12)T MIN to T MAX b70dBc(max) ENOB Effective Number of Bits T MIN to T MAX11 511 0Bits(min) (Note13)IMD Intermodulation Distortion f IN e102 3kHz 102 7kHz b80dBc DC Electrical Characteristics The following specifications apply for DV CC e AV CC e a5V V REF a(SENSE)e a4 096V V REF b(SENSE)e AGND and f s e1MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX all other limits T A e T J e a25 CSymbol Parameter ConditionsTyp Limit Units (Note7)(Note8)(Limit)V IN(1)Logical‘‘1’’Input Voltage DV CC e AV CC e a5 5V2 0V(min)V IN(0)Logical‘‘0’’Input Voltage DV CC e AV CC e a4 5V0 8V(max) I IN(1)Logical‘‘1’’Input Current0 11 0m A(max) I IN(0)Logical‘‘0’’Input Current0 11 0m A(max)V OUT(1)Logical‘‘1’’Output Voltage DV CC e AV CC e a4 5VI OUT e b360m A2 4V(min)I OUT e b100m A4 25V(min) V OUT(0)Logical‘‘0’’Output Voltage DV CC e AV CC e a4 5V0 4V(max)I OUT e1 6mAI OUT TRI-STATE Output Pins DB0–DB110 13m A(max)Leakage CurrentC OUT TRI-STATE Output Capacitance Pins DB0–DB115pFC IN Digital Input Capacitance4pFDI CC DV CC Supply Current23mA(max) AI CC AV CC Supply Current1012mA(max) I STANDBY Standby Current(DI CC a AI CC)PD e0V20m A3AC Electrical Characteristics The following specifications apply for DV CC e AV CC e a5V V REF a(SENSE)e a4 096V V REF b(SENSE)e AGND and f s e1MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX all other limits T A e T J e a25 CSymbol Parameter ConditionsTyp Limit Units (Note7)(Note8)(Limits)f s Maximum Sampling Rate1MHz(min)(1 t THROUGHPUT)t CONV Conversion Time740600ns(min) (S H Low to EOC High)980ns(max)t AD Aperture Delay20ns (S H Low to Input Voltage Held)t S H S H Pulse Width5ns(min)550ns(max)t EOC S H Low to EOC Low9560ns(min) 125ns(max)t ACC Access Time C L e100pF1020ns(max) (RD Low or OE High to Data Valid)t1H t0H TRI-STATE ControlR L e1k C L e10pF2540ns(max) (RD High or OE Low to Databus TRI-STATE)t INTH Delay from RD Low to INT High C L e100pF3560ns(max)t INTL Delay from EOC High to INT Low C L e100pFb25b35ns(min) b10ns(max)t UPDATE EOC High to New Data Valid515ns(max)t MS Multiplexer Address Setup Time50ns(min) (MUX Address Valid to EOC Low)t MH Multiplexer Address Hold Time50ns(min) (EOC Low to MUX Address Invalid)t CSS CS Setup Time20ns(min) (CS Low to RD Low S H Low or OE High)t CSH CS Hold Time20ns(min) (CS High after RD High S H High or OE Low)t WU Wake-Up Time1m s (PD High to First S H Low)Note1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occur Operating Ratings indicate conditions for which the device is functional These ratings do not guarantee specific performance limits however For guaranteed specifications and test conditions see the Electrical Characteris-tics The guaranteed specifications apply only for the test conditions listed Some performance characteristics may degrade when the device is not operated under the listed test conditionsNote2 All voltages are measured with respect to GND(GND e AGND e DGND) unless otherwise specifiedNote3 When the input voltage(V IN)at any pin exceeds the power supply rails(V IN k GND or V IN l V CC)the absolute value of current at that pin should be limited to25mA or less The50mA package input current limits the number of pins that can safely exceed the power supplies with an input current of25mA to twoNote4 The maximum power dissipation must be derated at elevated temperatures and is dictated by T JMAX i JA and the ambient temperature T A The maximum allowable power dissipation at any temperature is P D e(T JMAX b T A) i JA or the number given in the Absolute Maximum Ratings whichever is lower i JA for the V (PLCC)package is55 C W i JA for the VF(PQFP)package is62 C W In most cases the maximum derated power dissipation will be reached only during fault conditions4Note5 Human body model 100pF discharged through a1 5k X resistor Machine model ESD rating is200VNote6 See AN-450‘‘Surface Mounting Methods and Their Effect on Product Reliability’’or the section titled‘‘Surface Mount’’found in a current National Semiconductor Linear Data Book for other methods of soldering surface mount devicesNote7 Typicals are at a25 C and represent most likely parametric normNote8 Tested limits are guaranteed to National’s AOQL(Average Outgoing Quality Level)Note9 Integral Linearity Error is the maximum deviation from a straight line between the measured offset and full scale endpointsNote10 Dynamic testing of the ADC12062is done using the ADC IN input The input multiplexer adds harmonic distortion at high frequencies See the graph in the Typical Performance Characteristics section for a typical graph of THD performance vs input frequency with and without the input multiplexerNote11 The signal-to-noise ratio is the ratio of the signal amplitude to the background noise level Harmonics of the input signal are not included in its calculation Note12 The contributions from the first nine harmonics are used in the calculation of the THDNote13 Effective Number of Bits(ENOB)is calculated from the measured signal-to-noise plus distortion ratio(SINAD)using the equation ENOB e(SINAD b 1 76) 6 02Note14 The digital power supply current takes up to10seconds to decay to its final value after PD is pulled low This prohibits production testing of the standby current Some parts may exhibit significantly higher standby currents than the20m A typicalNote15 Power Supply Sensitivity is defined as the change in the Offset Error or the Full Scale Error due to a change in the supply voltageTRI-STATE Test Circuit and WaveformsTL H 11490–2TL H 11490–3TL H 11490–4TL H 11490–55Typical Performance CharacteristicsReference VoltageError Change vs Offset and Fullscale vs Reference VoltageLinearity Error Change Input VoltageMux ON Resistance vs vs Temperature Digital Supply Current vs TemperatureAnalog Supply Current on Digital Input PinsStandby Mode vs Voltage Current Consumption in vs Temperature Conversion Time (t CONV )vs TemperatureEOC Delay Time (t EOC )Spectral Response(ADC IN)SINAD vs Input Frequency (ADC IN)SNR vs Input Frequency (ADC IN)THD vs Input Frequency TL H 11490–276Typical Performance Characteristics(Continued)(Through Mux)SINAD vs Input Frequency (Through Mux)SNR vs Input Frequency (Through Mux)THD vs Input Frequency Impedance SNR and THD vs Source Reference VoltageSNR and THD vs TL H 11490–28Timing DiagramsTL H 11490–9FIGURE 1 Interrupt Interface Timing (MODE e 1 OE e 1)7Timing Diagrams (Continued)TL H 11490–10FIGURE 2 High Speed Interface Timing (MODE e 1 OE e 1 CS e 0 RD e 0)TL H 11490–11FIGURE 3 CS Setup and Hold Timing for S H RD and OEConnection DiagramsTL H 11490–13Top ViewTL H 11490–29Top View8Pin DescriptionsAV CC These are the two positive analog supplyinputs They should always be connectedto the same voltage source but arebrought out separately to allow for sepa-rate bypass capacitors Each supply pinshould be bypassed to AGND with a0 1m F ceramic capacitor in parallel with a10m F tantalum capacitorDV CC This is the positive digital supply input Itshould always be connected to the samevoltage as the analog supply AV CC Itshould be bypassed to DGND2with a0 1m F ceramic capacitor in parallel with a10m F tantalum capacitorAGND These are the power supply ground pins DGND1 There are separate analog and digital DGND2ground pins for separate bypassing of theanalog and digital supplies The groundpins should be connected to a stablenoise-free system ground All of theground pins should be returned to thesame potential AGND is the analogground for the converter DGND1is theground pin for the digital control linesDGND2is the ground return for the outputdatabus See Section6 0LAYOUT ANDGROUNDING for more informationDB0–DB11These are the TRI-STATE output pins en-abled by RD CS and OEV IN1 V IN2These are the analog input pins to the mul-tiplexer For accurate conversions no in-put pin(even one that is not selected)should be driven more than50mV belowground or50mV above V CCMUX OUT This is the output of the on-board analoginput multiplexerADC IN This is the direct input to the12-bit sam-pling A D converter For accurate conver-sions this pin should not be driven morethan50mV below AGND or50mV aboveAV CCS0This pin selects the analog input that willbe connected to the ADC12062during theconversion The input is selected based onthe state of S0when EOC makes its high-to-low transition Low selects V IN1 highselects V IN2MODE This pin should be tied to DV CCCS This is the active low Chip Select controlinput When low this pin enables the RDS H and OE inputs This pin can be tiedlowINT This is the active low Interrupt outputWhen using the Interrupt Interface Mode(Figure1) this output goes low when aconversion has been completed and indi-cates that the conversion result is avail-able in the output latches This output isalways high when RD is held low(Figure2)EOC This is the End-of-Conversion control out-put This output is low during a conversion RD This is the active low Read control inputWhen RD is low(and CS is low) the INToutput is reset and(if OE is high)data ap-pears on the data bus This pin can be tiedlowOE This is the active high Output Enable con-trol input This pin can be thought of as aninverted version of the RD input(see Fig-ure6) Data output pins DB0–DB11areTRI-STATE when OE is low Data appearson DB0–DB11only when OE is high andCS and RD are both low This pin can betied highS H This is the Sample Hold control input Theanalog input signal is held and a new con-version is initiated by the falling edge ofthis control input(when CS is low) PD This is the Power Down control input Thispin should be held high for normal opera-tion When this pin is pulled low the devicegoes into a low power standby mode V REF a(FORCE) These are the positive and negative volt-V REF b(FORCE)age reference force inputs respectivelySee Section4 REFERENCE INPUTS formore informationV REF a(SENSE) These are the positive and negative volt-V REF b(SENSE)age reference sense pins respectivelySee Section4 REFERENCE INPUTS formore informationV REF 16This pin should be bypassed to AGND witha0 1m F ceramic capacitorTEST This pin should be tied to DV CC9Functional DescriptionThe ADC12062performs a12-bit analog-to-digital conver-sion using a3step flash technique The first flash deter-mines the six most significant bits the second flash gener-ates four more bits and the final flash resolves the two least significant bits Figure4shows the major functional blocks of the converter It consists of a2 -bit Voltage Estimator a resistor ladder with two different resolution voltage spans a sample hold capacitor a4-bit flash converter with front end multiplexer a digitally corrected DAC and a capacitive volt-age dividerThe resistor string near the center of the block diagram in Figure4generates the6-bit and10-bit reference voltages for the first two conversions Each of the16resistors at the bottom of the string is equal to of the total string resist-ance These resistors form the LSB Ladder and have a voltage drop of of the total reference voltage(V REF a b V REF b)across each of them The remaining resistors form the MSB Ladder It is comprised of eight groups of eight resistors each connected in series(the lowest MSB ladder resistor is actually the entire LSB ladder) Each MSB Ladder section has of the total reference voltage across it Within a given MSB ladder section each of the eight MSB resistors has of the total reference voltage across it Tap points are found between all of the resistors in both the MSB and LSB ladders The Comparator MultipIexer can connect any of these tap points in two adjacent groups of eight to the sixteen comparators shown at the right of Figure4 This function provides the necessary reference voltages to the comparators during the first two flash con-versionsThe six comparators seven-resistor string(Estimator DAC ladder) and Estimator Decoder at the left of Figure4form Note The weight of each resistor on the LSB ladder is actually equivalent to four12-bit LSBs It is called the LSB ladder because it has thehighest resolution of all the ladders in the converter the Voltage Estimator The Estimator DAC connected be-tween V REF a and V REF b generates the reference volt-ages for the six Voltage Estimator comparators The com-parators perform a very low resoIution A D conversion to obtain an‘‘estimate’’of the input voltage This estimate is used to control the placement of the Comparator Multiplex-er connecting the appropriate MSB ladder section to the sixteen flash comparators A total of only22comparators(6 in the Voltage Estimator and16in the flash converter)is required to quantize the input to6bits instead of the64that would be required using a traditional6-bit flashPrior to a conversion the Sample Hold switch is closed allowing the voltage on the S H capacitor to track the input voItage Switch1is in position1 A conversion begins by opening the Sample Hold switch and latching the output of the Voltage Estimator The estimator decoder then selects two adjacent banks of tap points aIong the MSB ladder These sixteen tap points are then connected to the sixteen flash converters For exampIe if the input voltage is be-tween and of V REF(V REF e V REF a b V REF b) the estimator decoder instructs the comparator multiplexer to select the sixteen tap points between and ( and )of V REF and connects them to the sixteen comparators The first flash conversion is now performed producing the first6MSBs of dataAt this point Voltage Estimator errors as large as of V REF will be corrected since the comparators are connect-ed to ladder voltages that extend beyond the range speci-fied by the Voltage Estimator For example if( )V REF k V IN k( )V REF the Voltage Estimator’s comparators tied to the tap points below( )V REF will output‘‘1’’s (000111) This is decoded by the estimator decoder to‘‘10’’ The16comparators will be placed on the MSB ladderTL H 11490–14FIGURE4 Functional Block Diagram10Functional Description(Continued)tap points between( )V REF and( )V REF This overlap of ( )V REF will automatically cancel a Voltage Estimator er-ror of up to256LSBs If the first flash conversion deter-mines that the input voltage is between( )V REF and (( )V REF b LSB 2) the Voltage Estimator’s output code will be corrected by subtracting‘‘1’’ resulting in a corrected value of‘‘01’’for the first two MSBs If the first flash conver-sion determines that the input voltage is between( )V REF b LSB 2)and( )V REF the voltage estimator’s output code is unchangedThe results of the first flash and the Voltage Estimator’s output are given to the factory-programmed on-chip EEPROM which returns a correction code corresponding to the error of the MSB ladder at that tap This code is convert-ed to a voltage by the Correction DAC To generate the next four bits SW1is moved to position2 so the ladder voltage and the correction voltage are subtracted from the input voltage The remainder is applied to the sixteen flash con-verters and compared with the16tap points from the LSB ladderThe result of this second conversion is accurate to10bits and describes the input remainder as a voltage between two tap points(V H and V L)on the LSB ladder To resolve the last two bits the voltage across the ladder resistor(between V H and V L)is divided up into4equal parts by the capacitive voltage divider shown in Figure5 The divider also creates 6LSBs below V L and6LSBs above V H to provide overlap used by the digital error correction SW1is moved to posi-tion3 and the remainder is compared with these16new voltages The output is combined with the results of the Voltage Estimator first flash and second flash to yield the final12-bit resultBy using the same sixteen comparators for all three flash conversions the number of comparators needed by the multi-step converter is significantly reduced when compared to standard multi-step techniquesApplications Information1 0MODES OF OPERATIONThe ADC12062has two interface modes An interrupt read mode and a high speed mode Figures1and2show the timing diagrams for these interfacesIn order to clearly show the relationship between S H CS RD and OE the control logic decoding section of the ADC12062is shown in Figure6Interrupt InterfaceAs shown in Figure1 the falling edge of S H holds the input voltage and initiates a conversion At the end of the conver-sion the EOC output goes high and the INT output goes low indicating that the conversion results are latched and may be read by pulling RD low The falling edge of RD re-sets the INT line Note that CS must be low to enable S H or RDHigh Speed InterfaceThis is the fastest interface shown in Figure2 Here the output data is always present on the databus and the INT to RD delay is eliminatedTL H 11490–15FIGURE5 The Capacitive Voltage Divider11Applications Information (Continued)TL H 11490–16FIGURE 6 ADC Control Logic2 0THE ANALOG INPUTThe analog input of the ADC12062can be modeled as two small resistances in series with the capacitance of the input hold capacitor (C IN ) as shown in Figure 7 The S H switch is closed during the Sample period and open during Hold The source has to charge C IN to the input voltage within the sample period Note that the source impedance of the input voltage (R SOURCE )has a direct effect on the time it takes to charge C IN If R SOURCE is too large the voltage across C IN will not settle to within 0 5LSBs of V SOURCE before the conversion begins and the conversion results will be incor-rect From a dynamic performance viewpoint the combina-tion of R SOURCE R MUX R SW and C IN form a low pass filter Minimizing R SOURCE will increase the frequency re-sponse of the input stage of the converterTypical values for the components shown in Figure 7are R MUX e 100X R SW e 100X and C IN e 25pF The set-tling time to n bits ist SETTLE e (R SOURCE a R MUX a R SW ) C IN n ln (2) The bandwidth of the input circuit isf b 3dB e 1 (2 3 14 (R SOURCE a R MUX a R SW ) C IN )For maximum performance the impedance of the source driving the ADC12062should be made as small as possible A source impedance of 100X or less is recommended A plot of dynamic performance vs source impedance is given in the Typical Performance Characteristics sectionIf the signal source has a high output impedance its output should be buffered with an operational amplifier capable of driving a switched 25pF 100X load Any ringing or instabili-ties at the op amp’s output during the sampling period can result in conversion errors The LM6361high speed op amp is a good choice for this application due to its speed and its ability to drive large capacitive loads Figure 8shows the LM6361driving the ADC IN input of an ADC12062 The 100pF capacitor at the input of the converter absorbs some of the high frequency transients generated by the S H switching reducing the op amp transient response require-ments The 100pF capacitor should only be used with high speed op amps that are unconditionally stable driving ca-pacitive loadsTL H 11490–17FIGURE 7 Simplified ADC12062Input Stage12Applications Information (Continued)TL H 11490–18FIGURE 8 Buffering the Input with an LM6361High Speed Op AmpAnother benefit of using a high speed buffer is improved THD performance when using the multiplexer of the ADC12062 The MUX on-resistance is somewhat non-linear over input voltage causing the RC time constant formed by C IN R MUX and R SW to vary depending on the input voltage This results in increasing THD with increasing frequency Inserting the buffer between the MUX OUT and the ADC IN terminals as shown in Figure 8will eliminate the loading on R MUX significantly reducing the THD of the multiplexed sys-temCorrect converter operation will be obtained for input volt-ages greater than AGND b 50mV and less than AV CC a50mV Avoid driving the signal source more than 300mV higher than AV CC or more than 300mV below AGND If an analog input pin is forced beyond these voltages the cur-rent flowing through that pin should be limited to 25mA or less to avoid permanent damage to the IC The sum of all the overdrive currents into all pins must be less than 50mA When the input signal is expected to extend more than 300mV beyond the power supply limits for any reason (un-known uncontrollable input voltage range power-on tran-sients fault conditions etc )some form of input protection such as that shown in Figure 9 should be usedTL H 11490–19FIGURE 9 Input Protection13Applications Information(Continued)3 0ANALOG MULTIPLEXERThe ADC12062has an input multiplexer that is controlled by the logic level on pin S0when EOC goes low as shown in Figures1and2 Multiplexer setup and hold times with re-spect to the S H input can be determined by these two equationst MS(wrt S H)e t MS b t EOC(min)e50b60e b10ns t MH(wrt S H)e t MH a t EOC(max)e50a125e175ns Note that t MS(wrt S H)is a negative number this indicates that the data on S0must become valid within10ns after S H goes low in order to meet the setup time requirements S0must be valid for a length of(t MH a t EOC(max))b(t MS b t EOC(min))e185ns Table I shows how the input channels are assignedTABLE I ADC12062InputMultiplexer ProgrammingS0Channel0V IN11V IN2The output of the multiplexer is available to the user via the MUX OUT pin This output allows the user to perform addi-tional signal processing such as filtering or gain before the signal is returned to the ADC IN input and digitized If no additional signal processing is required the MUX OUT pin should be tied directly to the ADC IN pinSee Section9 0(APPLICATIONS)for a simple circuit that will alternate between the two inputs while converting at full speed4 0REFERENCE INPUTSIn addition to the fully differential V REF a and V REF b refer-ence inputs used on most National Semiconductor ADCs the ADC12062has two sense outputs for precision control of the ladder voltage These sense inputs compensate for errors due to IR drops between the reference source and the ladder itself The resistance of the reference ladder is typically750X The parasitic resistance(R P)of the package leads bond wires PCB traces etc can easily be0 5X to 1 0X or more This may not be significant at8-bit or10-bit resolutions but at12bits it can introduce voltage drops causing offset and gain errors as large as6LSBsThe ADC12062provides a means to eliminate this error by bringing out two additional pins that sense the exact voltage at the top and bottom of the ladder With the addition of two op amps the voltages on these internal nodes can be forced to the exact value desired as shown in Figure10TL H 11490–20FIGURE10 Reference Ladder Force and Sense Inputs14。

oppo A127播放器 说明书

干扰 所有的无线设备都可能受到干扰,从而 影响性能。

在爆破地点附近应关机 请遵守任何相关的限制规定。请勿在进 行爆破操作的地方使用本设备。

合理的使用

仅在正常位置故用手触摸天线区域。

OPPO A127支持多种音频格式的专用音乐播放器,让您轻松玩转音乐;200万像素数码拍照功能,助您将每个美好瞬间变 成永恒;图片处理随时随地;QQ、QQ游戏、飞信让运动、旅途中的您能随时随地和好友聊天或其它娱乐,尽享沟通乐趣; 还有Java游戏、蓝牙2.1+EDR、变换主题更让您乐不停……

使用产品前请仔细阅读本使用说明书。 网址

本文档的内容按产品制造时的状况提供。除非适用的法律另有规定,否则不对文档的准确性、可靠性和内容作出任何类型 的明确或默许的保证。

1 请务必为您产品中存储的所有重要内容和数据制作备份或保存书面记录,因为该内容和数据在产品的使用、维修、电池更换

或 其 他 原 因 都 有 可 能 造 成 资 料 丢 失 或 损 坏 。在 适 用 法 律 允 许 的 最 大 限 度 内 ,在任何情 况 下,O P P O或 其 任 何 许 可 证 持 有 方 均 不对任何数据或收入方面的损失,或任何特殊、偶然、附带或间接损失承担责任,无论该损失由何种原因引起。

本产品经过杜比实验室的许可而制造。杜比和双D符号是杜比实验室的注册商标。

产品的供货情况和相关的应用软件和配件,可能因地区而异。有关详情,请向OPPO指定的经销商查询。

本产品可能包含受中国和其他国家或地区的出口法律和法规控制的商品、技术或软件,严禁任何违反法律的转移行为。

安全事项

请阅读以下简明的规则,如未遵守这些规则可能会导致危险 或触犯法律。本说明书提供了有关安全事项的更详细信息。

MH8S72DALD-6资料

DESCRIPTIONThe MH8S72DALD is 8388608 - word by 72-bit Synchronous DRAM module. This consists of nine industry standard 8Mx8 Synchronous DRAMs in TSOP and one industory standard EEPROM in TSSOP.The mounting of TSOP on a card edge Dual Inline package provides any application where high densities and large quantities of memory are required.This is a socket type - memory modules, suitable for easy interchange or addition of modules.FEATURESMax. Clock frequency -6:133MHz,-7,8:100MHzsingle 3.3V±0.3V power supplyBurst length- 1/2/4/8/Full Page(programmable)10pin 11pinPIN NO.PIN NAME PIN NO.PIN NAME PIN NO.PIN NAME PIN NO.PIN NAME 1VSS43VSS85VSS127VSS 2DQ044NC86DQ32128CKE0 3DQ145/S287DQ33129NC 4DQ246DQMB288DQ34130DQMB6 5DQ347DQMB389DQ35131DQMB7 6VDD48NC90VDD132NC 7DQ449VDD91DQ36133VDD 8DQ550NC92DQ37134NC 9DQ651NC93DQ38135NC 10DQ752CB294DQ39136CB6 11DQ853CB395DQ40137CB7 12VSS54VSS96VSS138VSS 13DQ955DQ1697DQ41139DQ48 14DQ1056DQ1798DQ42140DQ49 15DQ1157DQ1899DQ43141DQ50 16DQ1258DQ19100DQ44142DQ51 17DQ1359VDD101DQ45143VDD 18VDD60DQ20102VDD144DQ52 19DQ1461NC103DQ46145NC 20DQ1562NC104DQ47146NC 21CB063NC105CB4147NC CB12264VSS106CB5148VSS 23VSS65DQ21107VSS149DQ53 24NC66DQ22108NC150DQ54 25NC67DQ23109NC151DQ55 26VDD68VSS110VDD152VSS 27/WE069DQ24111/CAS153DQ56 28DQMB070DQ25112DQMB4154DQ57 29DQMB171DQ26113DQMB5155DQ58 30/S072DQ27114NC156DQ59 31NC73VDD115/RAS157VDD 32VSS74DQ28116VSS158DQ60 33A075DQ29117A1159DQ61 34A276DQ30118A3160DQ62 35A477DQ31119A5161DQ63 36A678VSS120A7162VSS 37A879CK2121A9163CK3 38A1080NC122BA0164NC 39BA181WP123A11165SA0 40VDD82SDA124VDD166SA1 41VDD83SCL125CK1167SA2 42CK084VDD126NC168VDD NC = No ConnectionVccVssD0 - D8D0 - D8/S0/S2CKE0D0 - D8D0 - D8D0 - D8/WE D0 - D8D0 - D85SDRAMs4SDRAMs+3.3pF cap.SCLWPCK3Serial Presence Detect Table IByte Function describedSPD enrty dataSPD DATA(hex)0Defines # bytes written into serial memory at module mfgr128801Total # bytes of SPD memory device256 Bytes 082Fundamental memory type SDRAM 043# Row Addresses on this assembly A0-A110C 4# Column Addresses on this assembly A0-A8095# Module Banks on this assembly 1BANK 016Data Width of this assembly...x72487... Data Width continuation0008Voltage interface standard of this assemblyLVTTL 019SDRAM Cycletime at Max. Supported CAS Latency (CL).A0Cy cle time for CL=310SDRAM Access from Clock6ns60tAC for CL=311DIMM Configuration type (Non-parity,Parity,ECC)ECC0212Refresh Rate/Type self refresh(15.625uS)8013SDRAM width,Primary DRAM x 80814Error Checking SDRAM data widthx 80815M inimum Clock Delay,Back to Back Random Column Addresses10116Burst Lengths Supported 1/2/4/8/Full page8F 17# Banks on Each SDRAM device4bank0418CAS# Latency 30419CS# Latency 00120Write Latency 00121SDRAM Module Attributes non-buffered,non-registered 0022SDRAM Dev ice Attributes:General Precharge All,Auto precharge0E 23SDRAM Cy cle time(2nd highest CAS latency)13ns D0Cy cle time for CL=224SDRAM Access form Clock(2nd highest CAS latency)7ns 70tAC for CL=225SDRAM Cy cle time(3rd highest CAS latency)N/A00N/A 0026SDRAM Access form Clock(3rd highest CAS latency)27Precharge to Active Minimum 20ns 1428Row Active to Row Active Min.15ns 0F 10ns -8-8-710ns A06ns 60-729RAS to CAS Delay Min 22.5ns 1730Active to Precharge Min50ns32-7,-8-6757.5ns -7,-8-6 5.4ns 54-7,-8-62/306-6N/A 00-6N/A 00-7,-8-622.5ns 17-7,-8-6-7,-8-6-7,-8-620ns 1420ns 1445ns 2DSerial Presence Detect Table II31Density of each bank on module64MByte 1036-61Superset Information (may be used in future)option 0062SPD Revision 63Checksum for bytes 0-62Check sum for -85764-71Manufactures Jedec ID code per JEP-108EMITSUBISHI 1CFFFFFFFFFFFFFF72Manufacturing locationMiyoshi,Japan 01Tajima,Japan 02NC,USA 03Germany 0473-90Manufactures Part Number MH8S72DALD-891-92Revision Code PCB revision rrrr 93-94Manufacturing date year/week code yyww 95-98Assembly Serial Number serial numberssssssss99-125Manufacture Specific Data option 00126Intetl specification frequency100MHz 64127Intel specification CAS# Latency support128+Unused storage locationsopen0032Command and Address signal input setup time 2ns 202033Command and Address signal input hold time1ns 1034Data signal input setup time 2ns 35Data signal input hold time1ns 10rev 1.2A 12Check sum for -717MH8S72DALD-64D483853373244414C442D36202020202020-7AF CL=2/3,AP,CK0,2MH8S72DALD-7-6,-8AD CL=3,AP,CK0,2-6-7,-8-6-7,-8-6-7,-8-6-7,-8Check sum for -6A41.5ns 150.8ns 08151.5ns 0.8ns 08-6-7,-8JEDEC2024D483853373244414C442D372020202020204D483853373244414C442D38202020202020PIN FUNCTIONBASIC FUNCTIONS/S Chip Select : L=select, H=deselect /RAS Command /CAS Command /WE CommandCKE Ref resh Option @ref resh commandA10Precharge Option @precharge or read/write commandCK def ine basic commandsThe MH8S72DALD provides basic functions,bank(row)activate,burst read / write, bank(row)precharge,and auto / self refresh.Each command is defined by control signals of /RAS,/CAS and /WE at CK rising edge. In addition to 3 signals,/S,CKE and A10 are used as chip select,refresh option,and precharge option,respectively.To know the detailed definition of commands please see the command truth table.Activate(ACT) [/RAS =L, /CAS = /WE =H]Read(READ) [/RAS =H,/CAS =L, /WE =H]Write(WRITE) [/RAS =H, /CAS = /WE =L]Precharge(PRE) [/RAS =L, /CAS =H,/WE =L]Auto-Refresh(REFA) [/RAS =/CAS =L, /WE =CKE =H]ACT command activates a row in an idle bank indicated by BA. READ command starts burst read from the active bank indicated by BA.First output data appears after /CAS latency. When A10 =H at this command,the bank is deactivated after the burst read(auto-precharge,READA ). WRITE command starts burst write to the active bank indicated by BA. Total datalength to be written is set by burst length. When A10 =H at this command, the bank is deactivated after the burst write(auto-precharge,WRITEA ). PRE command deactivates the active bank indicated by BA. This command also terminates burst read / write operation. When A10 =H at this command, both banks are deactivated(precharge all, PREA ).REFA command starts auto-refresh cycle. Refresh address including bank address are generated internally. After this command, the banks are precharged automatically.COMMAND TRUTH TABLECOMMAND MNEMONIC CKE n-1CKE n /S /RAS /CAS /WE BA0,1A10A0-9Deselect DESEL H X H X X X X X X No Operation NOP H X L H H H X X X Row Adress Entry &Bank Activate ACT H X L L H H V V V Single Bank Precharge PRE H X L L H L V L X Precharge All Bank PREA H X L L H L X H X Column Address Entry& Write WRITEHXLHLLVLVColumn Address Entry & Write with Auto-Precharge WRITEA H X L H L L V H VColumn Address Entry& Read READ H X L H L H V L VColumn Address Entry & Read with AutoPrecharge READA H X L H L H V H V Auto-Refresh REFA H H L L L H X X X Self-Refresh Entry REFS H L L L L H X X X Self-Refresh Exit REFSX L H H X X X X X X L H L H H H X X X Burst Terminate TERM H X L H H L X X X Mode Register SetMRSHXLLLLLLV*1H =High Level, L = Low Level, V = Valid, X = Don't Care, n = CK cycle number NOTE:1.A7-9 = 0, A0-6 = Mode AddressA11X X V X X VV V V X X X X X LCurrent State/S/RAS/CAS/WE Address Command Action IDLE H X X X X DESEL NOPL H H H X NOP NOPL H H L BA TBST ILLEGAL*2L H L X BA,CA,A10READ/WRITE ILLEGAL*2L L H H BA,RA ACT Bank Active,Latch RAL L H L BA,A10PRE/PREA NOP*4L L L H X REFA Auto-Refresh*5L L L L Op-Code,Mode-AddMRS Mode Register Set*5ROW ACTIVE H X X X X DESEL NOP L H H H X NOP NOPL H H L BA TBST NOPL H L H BA,CA,A10READ/READA Begin Read,Latch CA, Determine Auto-PrechargeL H L L BA,CA,A10WRITE/WRITEABegin Write,Latch CA,Determine Auto-PrechargeL L H H BA,RA ACT Bank Active/ILLEGAL*2 L L H L BA,A10PRE/PREA Precharge/Precharge All L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALREAD H X X X X DESEL NOP(Continue Burst to END) L H H H X NOP NOP(Continue Burst to END)L H H L BA TBST Terminate BurstL H L H BA,CA,A10READ/READA Terminate Burst,Latch CA, Begin New Read,Determine Auto-Precharge*3L H L L BA,CA,A10WRITE/WRITEA Terminate Burst,Latch CA, Begin Write,Determine Auto-Precharge*3L L H H BA,RA ACT Bank Active/ILLEGAL*2L L H L BA,A10PRE/PREA Terminate Burst,Precharge L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALFUNCTION TRUTH TABLEFUNCTION TRUTH TABLE(continued)Current State/S/RAS/CAS/WE Address Command Action WRITE H X X X X DESEL NOP(Continue Burst to END) L H H H X NOP NOP(Continue Burst to END)L H H L BA TBST Terminate BurstL H L H BA,CA,A10READ/READA Terminate Burst,Latch CA, Begin Read,Determine Auto-Precharge*3L H L L BA,CA,A10WRITE/WRITEATerminate Burst,Latch CA,Begin Write,Determine Auto-Precharge*3L L H H BA,RA ACT Bank Active/ILLEGAL*2L L H L BA,A10PRE/PREA Terminate Burst,PrechargeL L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALREAD with H X X X X DESEL NOP(Continue Burst to END) AUTO L H H H X NOP NOP(Continue Burst to END) PRECHARGE L H H L BA TBST ILLEGALL H L H BA,CA,A10READ/READA ILLEGALL H L L BA,CA,A10WRITE/WRITEAILLEGALL L H H BA,RA ACT Bank Active/ILLEGAL*2 L L H L BA,A10PRE/PREA ILLEGAL*2L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALWRITE with H X X X X DESEL NOP(Continue Burst to END) AUTO L H H H X NOP NOP(Continue Burst to END) PRECHARGE L H H L BA TBST ILLEGALL H L H BA,CA,A10READ/READA ILLEGALL H L L BA,CA,A10WRITE/WRITEAILLEGALL L H H BA,RA ACT Bank Active/ILLEGAL*2 L L H L BA,A10PRE/PREA ILLEGAL*2L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALFUNCTION TRUTH TABLE(continued)Current State/S/RAS/CAS/WE Address Command Action PRE -H X X X X DESEL NOP(Idle after tRP) CHARGING L H H H X NOP NOP(Idle after tRP) L H H L BA TBST ILLEGAL*2L H L X BA,CA,A10READ/WRITE ILLEGAL*2L L H H BA,RA ACT ILLEGAL*2L L H L BA,A10PRE/PREA NOP*4(Idle after tRP)L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALROW H X X X X DESEL NOP(Row Active after tRCD ACTIVATING L H H H X NOP NOP(Row Active after tRCD L H H L BA TBST ILLEGAL*2L H L X BA,CA,A10READ/WRITE ILLEGAL*2L L H H BA,RA ACT ILLEGAL*2L L H L BA,A10PRE/PREA ILLEGAL*2L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALWRITE RE-H X X X X DESEL NOP COVERING L H H H X NOP NOPL H H L BA TBST ILLEGAL*2L H L X BA,CA,A10READ/WRITE ILLEGAL*2L L H H BA,RA ACT ILLEGAL*2L L H L BA,A10PRE/PREA ILLEGAL*2L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALFUNCTION TRUTH TABLE(continued)Current State/S/RAS/CAS/WE Address Command Action RE-H X X X X DESEL NOP(Idle after tRC) FRESHING L H H H X NOP NOP(Idle after tRC) L H H L BA TBST ILLEGALL H L X BA,CA,A10READ/WRITE ILLEGALL L H H BA,RA ACT ILLEGALL L H L BA,A10PRE/PREA ILLEGALL L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALMODE H X X X X DESEL NOP(Idle after tRSC) REGISTER L H H H X NOP NOP(Idle after tRSC) SETTING L H H L BA TBST ILLEGALL H L X BA,CA,A10READ/WRITE ILLEGALL L H H BA,RA ACT ILLEGALL L H L BA,A10PRE/PREA ILLEGALL L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALABBREVIATIONS:H = Hige Level, L = Low Level, X = Don't CareBA = Bank Address, RA = Row Address, CA = Column Address, NOP = No Operation NOTES:1. All entries assume that CKE was High during the preceding clock cycle and the current clock cycle.2. ILLEGAL to bank in specified state; function may be legal in the bank indicated by BA,depending on the state of that bank.3. Must satisfy bus contention, bus turn around, write recovery requirements.4. NOP to bank precharging or in idle state.May precharge bank indicated by BA.5. ILLEGAL if any bank is not idle.ILLEGAL = Device operation and / or date-integrity are not guaranteed.FUNCTION TRUTH TABLE FOR CKECurrent State CKEn-1CKEn/S/RAS/CAS/WE Add ActionSELF - H X X X X X X INVALIDREFRESH*1L H H X X X X Exit Self-Refresh(Idle after tRC) L H L H H H X Exit Self-Refresh(Idle after tRC)L H L H H L X ILLEGALL H L H L X X ILLEGALL H L L X X X ILLEGALL L X X X X X NOP(Maintain Self-Refresh) POWER H X X X X X X INVALIDDOWN L H X X X X X Exit Power Down to IdleL L X X X X X NOP(Maintain Self-Refresh) ALL BANKS H H X X X X X Refer to Function Truth Table IDLE*2H L L L L H X Enter Self-RefreshH L H X X X X Enter Power DownH L L H H H X Enter Power DownH L L H H L X ILLEGALH L L H L X X ILLEGALH L L L X X X ILLEGALL X X X X X X Refer to Current State = Power Down ANY STATE H H X X X X X Refer to Function Truth Tableother than H L X X X X X Begin CK0 Suspend at Next Cycle*3 listed above L H X X X X X Exit CK0 Suspend at Next Cycle*3 L L X X X X X Maintain CK0 SuspendABBREVIATIONS:H = High Level, L = Low Level, X = Don't CareNOTES:1. CKE Low to High transition will re-enable CK and other inputs asynchronously.A minimum setup time must be satisfied before any command other than EXIT.2. Power-Down and Self-Refresh can be entered only from the All banks idle State.3. Must be legal command.SIMPLIFIED STATE DIAGRAMIDLEPRE CHARGEAUTO REFRESHSELF MODE REGISTERSETPOWER DOWNREADREADAWRITEWRITEAREAD SUSPENDREADA SUSPENDWRITE SUSPENDWRITEA SUSPENDPOWER ONCLK SUSPENDCKELCKEHCKEHCKEHACTCKEHCKELCKEHWRITEAREADAPREPOWER APPLIEDAutomatic Sequence TBST(for Full Page)TBST(for Full Page)POWER ON SEQUENCEBefore starting normal operation, the following power on sequence is necessary to prevent a SDRAM from damaged or malfunctioning.1. Apply power and start clock. Attempt to maintain CKE high, DQMB0-7 high and NOP condition at the inputs.2. Maintain stable power, stable clock, and NOP input conditions for a minimum of 200us.3. Issue precharge commands for all banks. (PRE or PREA)4. After all banks become idle state (after tRP), issue 8 or more auto-refresh commands.5. Issue a mode register set command to initialize the mode register.After these sequence, the SDRAM is idle state and ready for normal operation.MODE REGISTERCK Burst Length, Burst Type and /CAS Latency can be programmed by setting the mode register(MRS). The mode register stores these date until the next MRS command, which may be issue when both banks are in idle state. After tRSC from a MRS command, the SDRAM is ready for new command.Command AddressCKDQBurst TypeA2A1A0Initial Address BL Sequential InterleavedColumn Addressing000001010011100101110111-00-01-10-11--0012345670123456712345670103254762345670123016745345671232107654456701234567012356701234547610326701234567452301701201231232301300176540123103223013201--11210345632111842CK A0-9,11A10DQOPERATION DESCRIPTIONBANK ACTIVATEOne of four banks is activated by an ACT command.An bank is selected by BA0-1. A row is selected by A0-11.Multiple banks can be active state concurrently by issuing multiple ACT commands.Minimum activation interval between one bank and another bank is tRRD.PRECHARGEAn open bank is deactivated by a PRE command.A bank to be deactivated is designated by BA0-1.When multiple banks are active, a precharge all command (PREA, PRE + A10=H) deactivates all of open banks at the same time. BA0-1 are "Don't Care" in this case.Minimum delay time of an ACT command after a PRE command to the same bank is tRP.READA READ command can be issued to any active bank. The start address is specified by A0-8 (x8) . 1st output data is available after the /CAS Latency from the READ. The consecutive data length is defined by the Burst Length. The address sequence of the burst data is defined by the Burst Type. Minimum delay time of a READ command after an ACT command to the same bank is tRCD.When A10 is high at a READ command, auto-precharge (READA) is performed. Anycommand (READ, WRITE, PRE, ACT, TBST) to the same bank is inhibited till the internal precharge is complete. The internal precharge starts at the BL after READA. The next ACT command can be issued after (BL + tRP) from the previous READA. In any case, tRCD+BL > tRASmin must be met.CK CommandA0-9, 11A10DQCKA10DQCKCL=3 CL=2CK Command A10DQCK Command A10DQWRITE with Auto-Precharge (BL=4)WRITEA WRITE command can be issued to any active bank. The start address is specified by A0-8 (x8). 1st input data is set at the same cycle as the WRITE. The consecutive data length to be written is defined by the Burst Length. The address sequence of burst data is defined by the Burst Type. Minimum delay time of a WRITE command after an ACT command to the same bank is tRCD. From the last input data to the PRE command, the write recovery time (tWR) is required. When A10 is high at a WRITE command, auto-precharge (WRITEA) is performed. Any command (READ, WRITE, PRE, ACT, TBST) to the same bank is inhibited till the internal precharge is complete. The internal precharge starts at tWR after the last input data cycle. The next ACT command can be issued after (BL + tWR -1 + tRP) from the previous WRITEA. In any case, tRCD + BL + tWR -1 > tRASmin must be met.A0-9, 11BA0,1A0-9, 11BA0,1BURST INTERRUPTION[ Read Interrupted by Read ]Burst read oparation can be interrupted by new read of the same or the other bank. Random column access is allowed READ to READ interval is minimum 1 CKCK A10DQ[ Read Interrupted by Write ]Burst read operation can be interrupted by write of any active bank. Random column access is allowed. In this case, the DQ should be controlled adequately by using the DQMB0-7 to prevent the bus contention. The output is disabled automatically 1 cycle after WRITE assertion.CK A10DQA0-9,11BA0,1A0-9,11BA0,1Output disableby DQM by WRITE[ Read Interrupted by Precharge ]A burst read operation can be interrupted by precharge of the same bank . Read to PRE interval is minimum 1 CK. A PRE command output disable latency is equivalent to the /CAS Latency.Read Interrupted by Precharge (BL=4)CKDQDQ CommandDQCommandDQ CL=3CL=2DQCommandDQ[ Read Interrupted by Burst Terminate ]Similarly to the precharge, burst terminate command can interrupt burst read operation and disable the data output. The terminated bank remains active,READ to TBST interval is minimum of 1 CK. A TBSTcommand to output disable latency is equivalent to the /CAS Latency.Read Interrupted by Terminate (BL=4)CKDQCL=3DQDQDQCL=2DQDQ[ Write Interrupted by Write ]Burst write operation can be interrupted by new write of any active bank. Random column access is allowed. WRITE to WRITE interval is minimum 1 CK.Write Interrupted by Write (BL=4)CK Command A10DQWrite Ya 000Write Yb 000Da0Da1Da2Db0Dc0Dc1Write Yc 010Dc2Dc3[ Write Interrupted by Read ]Burst write operation can be interrupted by read of any active bank. Random column access is allowed. WRITE to READ interval is minimum 1 CK. The input data on DQ at the interrupting READ cycle is "don't care".Write Interrupted by Read (BL=4, CL=2)CKA10DQA0-9, 11BA0,1A0-9,11BA0,1don't care[ Write Interrupted by Precharge ]Burst write operation can be interrupted by precharge of the same bank. Write recovery time(tWR) is required from the last data to PRE command. During write recovery, data inputs must be masked by DQM.CKA10DQ[ Write Interrupted by Burst Terminate ]Burst terminate command can terminate burst write operation. In this case, the write recovery time is not required and the bank remains active.The WRITE to TBST minimum interval is 1CK.Write Interrupted by Burst Terminate (BL=4)CKCommandA10DQ ACTX a00TBSTDa0Da1A0-9,11 BA0,1A0-9,11 BA0,1WriteYa00WriteYb00Db0Db1Db2Db3[ Write with Auto-Precharge interrupted by Write or Read to anotehr Bank ]Burst write with auto-precharge can be interrupted by write or read to another bank . Next ACT command can be issued after (BL+tWR-1+tRP) from the WRITEA. Auto-precharge interrrupted by a command to the same bank is inhibited.CK A10DQCK A10DQA0-9,11BA0,1A0-9,11BA0,1[ Read with Auto-Precharge interrupted by Read to anotehr Bank ]Burst read with auto-precharge can be interrupted by read to another bank . Next ACT command can be issued after (BL+tRP) from the READA. Auto-precharge interrrupted by a command to the same bank is inhibited.CK A10DQA0-9,11BA0,1Full Page BurstFull page burst length is available for only the sequential burst type. Full page burst read or write is repeated untill aPrecharge or a Burst Terminate command isissued. In case of the full page burst , a read or write with auto-precharge command is illegal.Single WriteWhen single write mode is set, burst length for write is always one, independently of Burst Length defined by (A2-0).AUTO REFRESHSingle cycle of auto-refresh is initiated with a REFA(/CS=/RAS=/CAS=L,/WE=/CKE=H) command. The refresh address is generated internally. 4096 REFA cycle within 64ms refresh 64Mbit memory cells. The auto-refresh is performed on 4banks concurrently. Before performing an auto-refresh, all banks must be in the idle state. Auto-refresh to auto-refresh interval is minimum tRFC. Any command must not be issued before tRFC from the REFA command.CK/S/RAS/CAS/WECKEA0-11BA0,1Auto Refresh on All Banks Auto Refresh on All BanksSELF REFRESHSelf-refresh mode is entered by issuing a REFS command (/CS=/RAS=/CAS=L,/WE=H, CKE=L). Once the self-refresh is initiated, it is maintained as log as CKE is kept low.During the self-refresh mode, CKE is asynchronous and the only enabled input , all other inputs including CK are disabled and ignored, so that power consumption due to synchronous inputs is saved. To exit the self-refresh, supplying stable CK inputs, asserting DESEL or NOP command and then asserting CKE=H. After tRFC from the 1st CK edge follwing CKE=H, all banks are in the idle state and a new command can be issued after, but DESEL or NOP commands must be asserted till then.CK/S/RAS/CAS/WECKEA0-11BA0,1minimum tRFCfor recoveryCLK SUSPEND and POWER DOWNCKE controls the internal CLK at the following cycle. Figure below shows how CKE works. By negating CKE, the next internal CLK is suspended. The purpose of CLK suspend is power down, output suspend or input suspend. CKE is a synchronous input except during the self-refresh mode. CLK suspend can be performed either when the banks are active or idle. A command at the suspended cycle is ignored.CK(ext.CLK)CKEint.CLKCK CKE CKECK DQCKEDQM CONTROLDQMB0-7 is a dual function signal defined as the data mask for writes and the output disable for reads. During writes, DQMB0-7 masks input data word by word. DQMB0-7 to Data In latency is 0.During reads, DQMB0-7 forces output to Hi-Z word by word. DQMB0-7 to output Hi-ZCKCommandDQdisabled by DQMB=HABSOLUTE MAXIMUM RATINGSRECOMMENDED OPERATING CONDITION (Ta=0 ~ 70°C, unless otherwise noted)1:VIH(max)=5.5V f or pulse width less than 10ns.2.VIL(min)=-1.0 f or pulse width less than 10ns. CAPACITANCEAVERAGE SUPPLY CURRENT from Vdd(Ta=0 ~70°C, Vdd = 3.3 ± 0.3V, Vss = 0V, unless otherwise noted)AC OPERATING CONDITIONS AND CHARACTERISTICS(Ta=0 ~ 70°C, Vdd = 3.3 ± 0.3V, Vss = 0V, unless otherwise noted)Symbol Parameter Test Condition LimitsUnit Min.Max.VOH(DC)High-Level Output Voltage(DC)IOH=-2mA 2.4V VOL(DC)Low-Level Output Voltage(DC)IOL=2mA 0.4VVOH(AC)High-Level Output Voltage(AC)CL=50pF, IOH=-2mA 2V VOL(AC)Low-Level Output Voltage(AC)CL=50pF, IOL=2mA 0.8VIOZ Off-stare Output Current Q floating VO=0 ~ Vdd -55uA Ii Input Current VIH=0 ~ Vdd+0.3V -4545uA Note)1:Icc(max) is specif ied at the output open condition.2.Input signals are changed one time during 30ns.6301891806309909135270225-7, -8Test ConditionLimits (max)Unit tRC=min.tCLK=min, BL=1,CL=3mA CKE=L,tCLK=15ns, /CS>Vcc-0.2V mA CKE=CLK=L, /CS>Vcc-0.2VmA mA tCLK=min, BL=4, CL=3,all banks activ e(discerte)mA tRC=min, tCLK=min mA CKE <0.2VmACKE=H,tCLK=15ns,VIH>Vcc-0.2V,VIL<0.2V Symbol Icc1Icc2P Icc2PS Icc2NSIcc4Icc5Icc6Icc2N Parameteroperating currentone bank activ e (discrete)precharge stanby currentin power-down mode burst currentauto-refresh current self-refresh currentCKE=H,CLK=L,VIH>Vcc-0.2V,VIL<0.2V(f ixed)mA precharge stanby current in non power-down mode mA CKE=H,tCLK=15nsIcc3NS Icc3N CKE=H,CLK=LmA active stanby currentin non power-down modeone bank activ e (discrete)67518918081011709135270225-6AC TIMING REQUIREMENTS (SDRAM Component)(Ta=0 ~ 70°C, Vdd = 3.3 ± 0.3V, Vss = 0V, unless otherwise noted)Input Pulse Levels: 0.8V to 2.0V Input Timing Measurement Level: 1.4VCKSignal1.4V1.4VAny AC timing is referenced to the inputsignal crossing through 1.4V.Note:1 The timing requirements are assumed tT=1ns.If tT is longer than 1ns,(tT-1)ns should be added to the parameter.Limits Symbol Parameter -7Unit Min.Max.tCLK CK cycle timenstCH CK High pulse width 310ns tCL CK Low pilse width 3ns tT Transition time of CK 110nstIS Input Setup time(all inputs)2ns tIH Input Hold time(all inputs)1ns tRC Row cycle time 70ns tRCD Row to Column Delay 20nstRAS Row Active time 50100KnstRP Row Precharge time 20ns tWR Write Recovery time 20ns tRRD Act to Act Deley time20ns tRSC Mode Register Set Cycle time 10ns tSRX Self Refresh Exit time 10ns tREFRefresh Interval time64ms-8Min.Max.313311021702050100K 202020101064CL=2CL=31010ns -6Min.Max.2.5102.51101.50.867.52045100K 201515107.5647.5tRFC Refresh cycle time 80ns 8075tPDE Power Down Exit time 10ns 107.51.4V1.4VDQCKtACtOHtOHZSWITCHING CHARACTERISTICS (SDRAM Component)(Ta=0 ~ 70°C, Vdd = 3.3 ± 0.3V, Vss = 0V, unless otherwise note3)Output Load ConditionV OUTFor -63ns32.7CL=3Burst Write (single bank) @BL=4/CS/RAS/CAS /WECKE BA0,1DQACT#0WRITE#0PRE#0ACT#0WRITE#0CLKItalic parameter indicates minimum caseA0-8A10DQM A9,11Burst Write (multi bank) @BL=4/CS /RAS/CAS /WECKE BA0,1DQXX X 0Y01D0D0D0D0X X 0YD0D0D0D0ACT#0WRITE#0PRE#0ACT#0WRITE#001234567891011121314151617tRCDtRAS tWRtRPtRCtRCDD1D1D1D1XX X 1tRRD YtWR0X1XXX2tRRDACT#1WRITE#1PRE#1ACT#2CLKItalic parameter indicates minimum caseA0-8A10DQM A9,11。

IDT723612资料