AMR2803R3S中文资料

M-System远程I O R3系列通信模块规格书(型号:R3-NM1)说明书

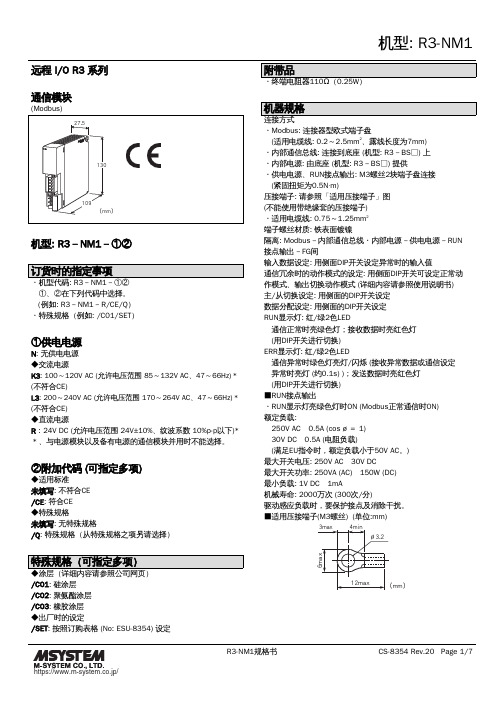

远程 I/O R3 系列通信模块机型: R3-NM1-①② ①、②在下列代码中选择。

(例如: R3-NM1-R/CE/Q)・特殊规格(例如: /C01/SET)①供电电源N: 无供电电源◆交流电源K3: 100~120V AC (允许电压范围 85~132V AC、47~66Hz)*(不符合CE)L3: 200~240V AC (允许电压范围 170~264V AC、47~66Hz)*(不符合CE)◆直流电源R:24V DC (允许电压范围 24V±10%、纹波系数 10%p-p以下)**、与电源模块以及备有电源的通信模块并用时不能选择。

②附加代码 (可指定多项)◆适用标准未填写: 不符合CE/CE: 符合CE◆特殊规格未填写: 无特殊规格/Q: 特殊规格(从特殊规格之项另请选择)/C01: 硅涂层/C02: 聚氨酯涂层/C03: 橡胶涂层◆出厂时的设定/SET: 按照订购表格 (No: ESU-8354) 设定・Modbus: 连接器型欧式端子盘 (适用电缆线: 0.2~2.5mm2、露线长度为7mm)・内部通信总线: 连接到底座 (机型: R3-BS□) 上・内部电源: 由底座 (机型: R3-BS□) 提供・供电电源、RUN接点输出: M3螺丝2块端子盘连接 (紧固扭矩为0.5N·m)压接端子: 请参照「适用压接端子」图(不能使用带绝缘套的压接端子)・适用电缆线: 0.75~1.25mm2端子螺丝材质: 铁表面镀镍隔离: Modbus-内部通信总线・内部电源-供电电源-RUN接点输出-FG间输入数据设定: 用侧面DIP开关设定异常时的输入值通信冗余时的动作模式的设定: 用侧面DIP开关可设定正常动作模式、输出切换动作模式 (详细内容请参照使用说明书)主/从切换设定: 用侧面的DIP开关设定数据分配设定: 用侧面的DIP开关设定RUN显示灯: 红/绿2色LED 通信正常时亮绿色灯;接收数据时亮红色灯 (用DIP开关进行切换)ERR显示灯: 红/绿2色LED 通信异常时绿色灯亮灯/闪烁 (接收异常数据或通信设定 异常时亮灯 (约0.1s) );发送数据时亮红色灯 (用DIP开关进行切换)■RUN接点输出・RUN显示灯亮绿色灯时ON (Modbus正常通信时ON)额定负载: 250V AC 0.5A (cos ø = 1) 30V DC 0.5A (电阻负载) (满足EU指令时,额定负载小于50V AC。

MEMORY存储芯片TMS320F28035PNS中文规格书

6TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Revision History Copyright ©2008–2014,Texas Instruments Incorporated2Revision HistoryNOTE:Page numbers for previous revisions may differ from page numbers in the current version.This data manual revision history highlights the changes made to the SPRS377E device-specific data manual to make it an SPRS377F revision.Scope:Applicable updates to the TMS320C6747/C6745Fixed-and Floating-Point Digital Signal Processor device family,specifically relating to the TMS320C6747and TMS320C6745devices,which are all now in the production data (PD)stage of development,have been incorporated.Revision HistorySEEADDITIONS/MODIFICATIONS/DELETIONS Global•Turned on Navigation Icons on top of first page.•Updated Features,Applications,and Description for consistency and translation.•Moved Trademarks information from first page to within Section 7,Device and Documentation Support.•Moved ESDS Warning to within Section 7,Device and Documentation Support.Section 1.1FeaturesDeleted Highlights rmation was duplicated elsewhere in Features.Section 1.2ApplicationsAdded NEW section.Section 1.3DescriptionAdded NEW Device Information Table.Section 3.3.2.3C674x CPUTable 3-2,C674x Cache Registers:•Updated/Changed REGISTER DESCRIPTION for BYTE ADDRESSES 0000,0020,and 0040from "...See the System reference Guide..."to "See the Technical Reference Manual..."Section 3.6Terminal Functions Table 3-21,Universal Serial Bus (USB)Terminal Functions:•Updated/Changed USB0_VDDA12DESCRIPTION from "...must always be connected via a 1μFcapacitor..."to "...is recommended to be connected via a 0.22-μF capacitor..."Section 3.6.11Universal Asynchronous Receiver/Transmitter s (UART0,UART1,UART2)Table 3-16,Universal Asynchronous Receiver/Transmitter (UART)Terminal Functions:•Updated/Changed footnote from "...DSP Reference Guide -Literature Number SPRUFK4..."to "...DSP Technical Reference Manual (SPRUH91)..."Section 3.6.21Reserved and NoConnectTable 3-26,Reserved and No Connect Terminal Functions:•Updated/Changed RSV4DESCRIPTION from "...This pin may be tied high or low."to "...For proper device operation,this pin must be tied low or to CVDD."Section 3.6.23Unused USB0(USB2.0)and USB1(USB1.1)PinConfigurationsMoved to within Section 3.6,Terminal Functions Table 3-28,Unused USB0and USB1Pin Configurations:•Updated/Changed USB0_VDDA12Configuration by combining both Configuration columns and changing text to "Internal USB0PHY output connected to an external..."Section 5Device OperatingConditionsSection 5.2,Handling Ratings:•Split handling,ratings,and certifications from the Abs Max table and placed in NEW Handling Ratings table.Section 5.4Notes onRecommendedPower-On Hours(POH)Table 5-1,Recommended Power-On Hours:•Added Silicon Revision column.Section 6.10.6EMIFA ElectricalData/Timing Table 6-22,EMIFA Asynchronous Memory Switching Characteristics:•Updated/Changed the MIN,NOM,and MAX equations for NO.3,10,15,and 24from "...(EWC*16)..."to "...EWC..."Section 5.3,Recommended Operating Conditions:•Added "Unless specifically indicated"to "These I/O specifications apply to ..."footnote8TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments Incorporated3Device Overview3.1Device CharacteristicsTable 3-1provides an overview of the C6745/6747low power digital signal processor.The table shows significant features of the device,including the capacity of on-chip RAM,peripherals,and the package type with pin count.Table 3-1.Characteristics of the C6745/C6747ProcessorHARDWARE FEATURESC6745C6747PeripheralsNot all peripherals pinsare available at the same time (for moredetail,see the Device Configurations section).EMIFB16bit,up to 128MB SDRAM 16/32bit,up to 256MB SDRAM EMIFAAsynchronous (8-bit bus width)RAM,Flash,NOR,NAND Asynchronous (8/16-bit bus width)RAM,Flash,16bit up to 128MB SDRAM,NOR,NAND Flash Card InterfaceMMC and SD cards supported.EDMA332independent channels,8QDMA channels,2Transfer controllers Timers264-Bit General Purpose (each configurable as 2separate 32-bit timers,1configurable as Watch Dog)UART3(one with RTS and CTS flow control)SPI2(each with one hardware chip select)I 2C2(both Master/Slave)Multichannel AudioSerial Port [McASP]2(each with transmit/receive,FIFO buffer,16/9serializers)3(each with transmit/receive,FIFO buffer,16/9serializers)10/100Ethernet MAC with Management Data I/O 1(RMII Interface)eHRPWM 6Single Edge,6Dual Edge Symmetric,or 3Dual Edge Asymmetric Outputs eCAP 332-bit capture inputs or 332-bit auxiliary PWM outputs eQEP232-bit QEP channels with 4inputs/channel UHPI-1(16-bit multiplexed address/data)USB 2.0(USB0)Full Speed Host Or Device with On-Chip PHY High-Speed OTG Controller with on-chip OTG PHY USB 1.1(USB1)-Full-Speed OHCI (as host)with on-chip PHY General-PurposeInput/Output Port8banks of 16-bit LCD Controller-1RTC-1(32KHz oscillator and seperate power trail.Provides time and date tracking and alarm capability.)PRU Subsystem(PRUSS)2Programmable PRU Cores On-Chip Memory Size (Bytes)320KB RAM 448KB RAMOrganization DSP 32KB L1Program (L1P)/Cache (up to 32KB)32KB L1Data (L1D)/Cache (up to 32KB)256KB Unified Mapped RAM/Cache (L2)DSP Memories can be made accessible to EDMA3,and other peripherals.-ADDITIONAL MEMORY128KB RAMC674x CPU ID +CPU Rev ID Control Status Register (CSR.[31:16])0x1400C674x MegamoduleRevision Revision ID Register (MM_REVID[15:0])0x0000。

MEMORY存储芯片TMS320F28032PNT中文规格书

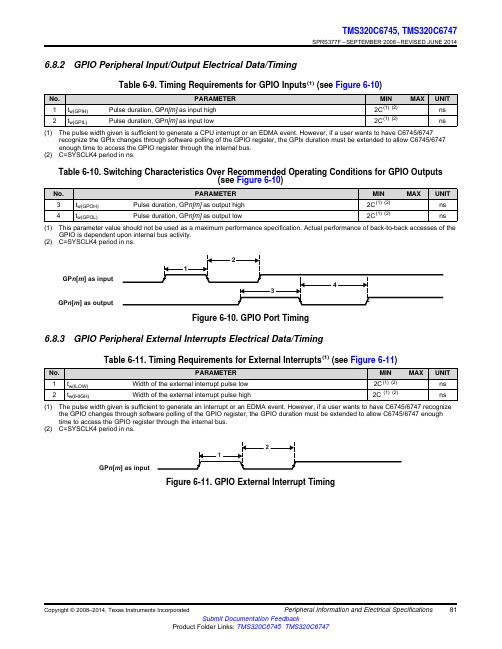

GP [] as inputn m GP [] as inputn mGP [] as output n m 81TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated 6.8.2GPIO Peripheral Input/Output Electrical Data/Timing(1)The pulse width given is sufficient to generate a CPU interrupt or an EDMA event.However,if a user wants to have C6745/6747recognize the GPIx changes through software polling of the GPIO register,the GPIx duration must be extended to allow C6745/6747enough time to access the GPIO register through the internal bus.(2)C=SYSCLK4period in ns.Table 6-9.Timing Requirements for GPIO Inputs (1)(see Figure 6-10)No.PARAMETER MIN MAX UNIT 1t w(GPIH)Pulse duration,GP n[m]as input high 2C (1)(2)ns 2t w(GPIL)Pulse duration,GP n[m]as input low 2C (1)(2)ns (1)This parameter value should not be used as a maximum performance specification.Actual performance of back-to-back accesses of the GPIO is dependent upon internal bus activity.(2)C=SYSCLK4period in ns.Table 6-10.Switching Characteristics Over Recommended Operating Conditions for GPIO Outputs (see Figure 6-10)No.PARAMETER MIN MAX UNIT 3t w(GPOH)Pulse duration,GP n[m]as output high 2C (1)(2)ns 4t w(GPOL)Pulse duration,GP n[m]as output low 2C (1)(2)ns Figure 6-10.GPIO Port Timing6.8.3GPIO Peripheral External Interrupts Electrical Data/Timing(1)The pulse width given is sufficient to generate an interrupt or an EDMA event.However,if a user wants to have C6745/6747recognize the GPIO changes through software polling of the GPIO register,the GPIO duration must be extended to allow C6745/6747enough time to access the GPIO register through the internal bus.(2)C=SYSCLK4period in ns.Table 6-11.Timing Requirements for External Interrupts (1)(see Figure 6-11)No.PARAMETER MIN MAX UNIT 1t w(ILOW)Width of the external interrupt pulse low 2C (1)(2)ns 2t w(IHIGH)Width of the external interrupt pulse high 2C (1)(2)ns Figure 6-11.GPIO External Interrupt Timing82TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical Specifications Copyright ©2008–2014,Texas Instruments Incorporated(1)On previous architectures,the EDMA3TC priority was controlled by the queue priority register (QUEPRI)in the EDMA3CC memory-map.However for this device,the priority control for the transfer controllers is controlled by the chip-level registers in the System Configuration Module.You should use the chip-level registers and not QUEPRI to configure the TC priority.6.9EDMATable 6-12is the list of EDMA3Channel Contoller Registers and Table 6-13is the list of EDMA3Transfer Controller registers.Table 6-12.EDMA3Channel Controller (EDMA3CC)RegistersBYTE ADDRESSACRONYM REGISTER DESCRIPTION 0x01C00000PID Peripheral Identification Register 0x01C00004CCCFG EDMA3CC Configuration Register GLOBAL REGISTERS 0x01C00200QCHMAP0QDMA Channel 0Mapping Register 0x01C00204QCHMAP1QDMA Channel 1Mapping Register 0x01C00208QCHMAP2QDMA Channel 2Mapping Register 0x01C0020CQCHMAP3QDMA Channel 3Mapping Register 0x01C00210QCHMAP4QDMA Channel 4Mapping Register 0x01C00214QCHMAP5QDMA Channel 5Mapping Register 0x01C00218QCHMAP6QDMA Channel 6Mapping Register 0x01C0021CQCHMAP7QDMA Channel 7Mapping Register 0x01C00240DMAQNUM0DMA Channel Queue Number Register 00x01C00244DMAQNUM1DMA Channel Queue Number Register 10x01C00248DMAQNUM2DMA Channel Queue Number Register 20x01C0024CDMAQNUM3DMA Channel Queue Number Register 30x01C00260QDMAQNUM QDMA Channel Queue Number Register 0x01C00284QUEPRI Queue Priority Register (1)0x01C00300EMR Event Missed Register 0x01C00308EMCR Event Missed Clear Register 0x01C00310QEMR QDMA Event Missed Register 0x01C00314QEMCR QDMA Event Missed Clear Register 0x01C00318CCERR EDMA3CC Error Register 0x01C0031CCCERRCLR EDMA3CC Error Clear Register 0x01C00320EEVAL Error Evaluate Register 0x01C00340DRAE0DMA Region Access Enable Register for Region 00x01C00348DRAE1DMA Region Access Enable Register for Region 10x01C00350DRAE2DMA Region Access Enable Register for Region 20x01C00358DRAE3DMA Region Access Enable Register for Region 30x01C00380QRAE0QDMA Region Access Enable Register for Region 00x01C00384QRAE1QDMA Region Access Enable Register for Region 10x01C00388QRAE2QDMA Region Access Enable Register for Region 20x01C0038C QRAE3QDMA Region Access Enable Register for Region 30x01C00400-0x01C0043C Q0E0-Q0E15Event Queue Entry Registers Q0E0-Q0E150x01C00440-0x01C0047C Q1E0-Q1E15Event Queue Entry Registers Q1E0-Q1E150x01C00600QSTAT0Queue 0Status Register 0x01C00604QSTAT1Queue 1Status Register 0x01C00620QWMTHRAQueue Watermark Threshold A Register 0x01C00640CCSTATEDMA3CC Status Register GLOBAL CHANNEL REGISTERS 0x01C01000EREvent Register 0x01C01008ECR Event Clear Register。

A2803中文资料

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.Recommended Substitutions:High Voltage High Current Darlington ArraysA2803Date of status change: May 2, 2005Deadline for receipt of LAST TIME BUY orders: October 28, 2005These parts are in production but have been determined to be LAST TIME BUY . This classification indicates that the product is obsolete and notice has been given. Sale of this device is currently restricted to existing customer applications. The device should not be purchased for new design applications because of obsolescence in the near future. Samples are no longer st Time Buy2803 THRU 2824HIGH-VOLTAGE,HIGH-CURRENTDARLINGTON ARRAYS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50002Copyright © 1977, 2001 Allegro MicroSystems, Inc.*Also available for operation between -40°C and +85°C. To order, change prefix from ‘ULN’ to ‘ULQ’.DEVICE PART NUMBER DESIGNATION5075100125150AMBIENT TEMPERATURE IN °C25Dwg. GP-018BA L L O W AB L E P AC K A G E P O W E RD I S S I P A T I O N I N W A T T Sx = Character to identify specific device. Specification shown applies to family of devices with remaining digits as shown. See matrix above.The ULx2804, ULx2823, & ULx2824 are discontinued.Shown for reference only.2803 THRU 2824HIGH-VOLTAGE,HIGH-CURRENT DARLINGTON ARRAYS3Complete part number includes prefix to operating temperature range: ULN = -20°C to +85°C, ULQ = -40°C to +85°C and a suffix to identify package style: A = DIP, LW = SOIC.Types ULx2803A, ULx2803LW, ULx2804A, and ULx2804LWELECTRICAL CHARACTERISTICS at +25°C (unless otherwise noted).The ULx2804 is discontinued.Shown for reference only.2803 THRU 2824HIGH-VOLTAGE,HIGH-CURRENTDARLINGTON ARRAYS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50004Complete part number includes prefix to operating temperature range: ULN = -20°C to +85°C, ULQ = -40°C to +85°Cand a suffix to identify package style: A = DIP, LW = SOIC. Note that the ULQ2823LW and ULQ2824LW are not presently available.Types ULx2823A, ULN2823LW, ULx2824A, and ULN2824LWELECTRICAL CHARACTERISTICS at +25°C (unless otherwise noted).The ULx2823 & ULx2824 are discontinued.Shown for reference only.2803 THRU 2824HIGH-VOLTAGE,HIGH-CURRENTDARLINGTON ARRAYS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000620Dwg. GP-070-44010080DUTY CYCLE IN PER CENT0600400O U T P U T C U R R E N T I N m A /C H A N N E L2006020Dwg. GP-070-34010080DUTY CYCLE IN PER CENT0600400O U T P U T C U R R E N T I N m A /C H A N N E L20060ALLOWABLE COLLECTOR CURRENT AS A FUNCTION OF DUTY CYCLEULx28xxLW20Dwg. GP-070-24010080DUTY CYCLE IN PER CENT 0600400O U T P U T C U R R E N T I N m A /C H A N N E L2006020Dwg. GP-070-14010080DUTY CYCLE IN PER CENT 0600400O U T P U T C U R R E N T I N m A /C H A N N E L20060ALLOWABLE COLLECTOR CURRENT AS A FUNCTION OF DUTY CYCLEULx28xxAx = Characters to identify specific device. Specification shown applies to family of devices with remaining digits as shown.2803 THRU 2824HIGH-VOLTAGE,HIGH-CURRENT DARLINGTON ARRAYS7INPUT CURRENT AS AFUNCTION OF INPUT VOLTAGEULx28x3xDwg. GP-069INPUT VOLTAGE2.52.0I N P U T C U R R E N T I N m A — II N1.00.51.50.5Dwg. GP-0671.01.5COLLECTOR-EMITTER SATURATION VOLTAGE0600400C O L L E C T O R C U R R E N T I N m A200COLLECTOR CURRENT AS A FUNCTION OF INPUT CURRENT200Dwg. GP-068400INPUT CURRENT IN µA0600400C O L L E C T O R C U R R E N T I N m A200ULx28x4x6Dwg. GP-069-11012INPUT VOLTAGE52.0I N P U T C U R R E N T I N m A — II N1.00.51.587911SATURATION VOLTAGE AS A FUNCTION OFCOLLECTOR CURRENTx = Characters to identify specific device. Characteristic shown applies to family of devices with remaining digits as shown.2803 THRU 2824HIGH-VOLTAGE,HIGH-CURRENTDARLINGTON ARRAYS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50008PACKAGE DESIGNATOR “A” DIMENSIONSDimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)NOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.Dwg. MA-001-18A in19Dwg. MA-001-18A mm192803 THRU 2824HIGH-VOLTAGE,HIGH-CURRENT DARLINGTON ARRAYS9PACKAGE DESIGNATOR “LW” DIMENSIONSDimensions in Inches (for reference only)Dimensions in Millimeters (controlling dimensions)Dwg. MA-008-18A mm1.27BSCwg. MA-008-18A inBSCNOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.2803 THRU 2824HIGH-VOLTAGE,HIGH-CURRENT DARLINGTON ARRAYS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-500010The products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, ormanufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.元器件交易网。

HSMS-2803中文资料

Technical Data

HSMS-28XX Series

Features

• Surface Mount SOT-23/SOT143 Package

• Low Turn-On Voltage (As Low as 0.34 V at 1 mA)

HSMS-286X

7.0 0.18 0.69 10E-5 5.0 x 10E -8 1.08 5.0 0.65

2 0.5

4

IF - FORWARD CURRENT (mA)

∆VF - FORWARD VOLTAGE DIFFERENCE (mV)

IF - FORWARD CURRENT (mA)

Typical Parameters at TA = 25°C (unless otherwise noted), Single Diode

HSMS-2820 series of diodes is the best all-around choice for most applications, featuring low series resistance, low forward voltage at all current levels and good RF characteristics. The HSMS-2860 series is a high performance diode offering superior Vf and ultra-low capacitance.

CDIAGONAL = _C_1_x__C_2_ + _C_3__x_C__4 C1 + C2 C3 + C4

Kramer AV SL-280 快速启动指南说明书

SL-280 Quick Start (P/N: 2900-300567QS REV 2)P/N: 2900-300567Q S Rev: 2Scan for full manualSL-280 Quick Start GuideThis guide helps you install and use your SL-280 for the first time.Go to /downloads/SL-280 to download the latest user manual and check if firmware upgrades are available. Step 1: Check what’s in the boxSL-280Master / Room Controller 1 Set of rack ears1 Quick start guide1 Power cord4 Rubber feetStep 2: Get to know your SL-280#Feature Function 1POWER LED Lights green when powered on. 2SERVICE Mini USB Connector Connect to a PC to perform a firmware upgrade. 3IR Receiver and LED Detects IR signals for IR learning and indicates an active signal by lighting blue. 4 LINK LED Indicates Ethernet activity:Blue LED on – good connection.Blue LED flashing – no connection.Blue LED off – not ready.5 CONTROL LED Indicates control states:Green – the control application (brain) is ready and working.Blue – the control application (brain) is synchronizing.Red – indicates an error in the control application (brain).6 SERIAL LEDs (from 1 to 8) White Tx LEDs and blue Rx LEDs flash to indicate activity on each channel.7 IR LEDs (from 1 to 8) Blue LEDs indicating IR activity on each channel (the associated LED lights when therelevant IR port transmits data).8 I/O LEDs (from 1 to 8) Blue LEDs indicating I/O activity on each channel (the associated LED lights onDigital Out HIGH, and when Digital In is triggered).9 RELAY LEDs (from 1 to 8)Blue LEDs indicating relay activity on each channel (the associated LED lights whenthe relay is closed).# Feature Function10 SERIAL Ports (1-8) Terminal Block Connect to up to 8 serial controlled devices, for Ethernet-to-RS232bidirectional tunneling.11 IR Ports (1-8) Terminal Block Connect to up to 8 IR emitters or blasters.12 I/O Ports (1-8) Terminal Block Connect to up to 8 sensors or devices to be controlled, (for example, amotion sensor). Port may be configured as a digital input, digital output, oranalog input.13 RELAY Ports (1-8) Terminal Block 6 NO relays and 2 NC relays.Connect to up to 8 devices to be controlled by relay (for example, amotorized projection screen).14 USB Connector N/A – For future use.15 ID Button For self-identification over the network.Press the button to send (broadcast) the Beacon P3K command.Reply includes: IP address, UDP port number, TCP port number, MACaddress, and Model Name.16 RESET Button For performing a factory default reset.17 LAN RJ-45 Connector Connects to a local area network. Indications:LINK LED lights amber – 1000/100/10MB connection.DATA LED flashes green – Ethernet data link activity.18 Power Socket with Fuse and Power Switch Connects to mains electricity, powers on and off the device.Step 3: Install the SL-280To rack mount the machine attach both ear brackets to the machine (by removing the threescrews from each side of the machine and replacing those screws through the ear brackets)or place the machine on a table.Step 4: Connect the inputs and outputsAlways switch OFF the power on each device before connecting it to your SL-280. For best results, we recommend that you always use Kramer high-performance cables to connect AV equipment to the SL-280.Step 5: Connect the powerConnect AC power to the rear of the SL-280, switch on its power and then switch on the power on each device.Safety InstructionsCaution: There are no operator serviceable parts inside the unit.Warning: Use only the power cord that is supplied with the unit.Warning: Do not open the unit. High voltages can cause electrical shock! Servicing by qualified personnel only.Warning: Disconnect the power and unplug the unit from the wall before installing.See for updated safety information.。

datasheet-pam2803

FeaturesLED Power Efficiency:up to 90%Current Accuracy:5%(V =3.6V to 1.8V@V =3.7V)1MHz Switching FrequencyUses small,Low Profile External Components Low RDS(ON):100mΩ(TYP.)Open LED ProtectionOver Temperature Protection Low Profile SOT-23-6Package Pb-Free Package±IN F Low Start-Up Voltage:0.9V(I =270mA)Low Hold Voltage:0.75V(I =200mA)White LED Torch (Flashlight)White LED Camera FlashDSC(Digital Still Camera)Flash Cellular Camera Phone Flash PDA Camera FlashCamcorder Torch(Flashlight)LampThe PAM2803is a set-up DC-DC converter that delivers a regulated output current.The device switches at a 1.0MHz constant frequency,allowing for the use of small value external inductor and ceramic capacitors.The PAM2803is targeted to be used for driving loads up to 1A from a two-cell alkaline battery.The LED current can be programmed by the external current sense resistor,Rs,connected between the feedback pin (FB)and ground.A low 95mV feedback voltage reduces the power loss in the Rs for better efficiency.With its internal 2A,100device can provide high efficiency even at heavy load.During the shutdown mode,the feedback resistor Rs and the load are completely disconnected and the current consumption is reduced to less than 1uA.The PAM2803is available in the 6-lead SOT-23-6package.LED LED ApplicationsGeneral Descriptio nmΩNMOS switch,the n n n n n n n n n n n n n n n n nTypical ApplicationBlock DiagramC OLED SPin Configuration&Marking InformationTop View SOT 236--123654Pin NumberName Function 1SW Switch 2GND Ground 3FB Feedback 4SHDN Shut Down 5VOUT Output 6VINInputAbsolute Maximum RatingsThese are stress ratings only and functional operation is not implied Exposure to absolute maximum ratings for prolonged time periods may affect device reliability All voltages are with respect to ground ...Input Pin Voltage ...............................–0.3V to 6V SW Pin Voltage..................................–0.3V to 6V SHDN,FB Pin Voltage.........................–0.3V to 6VOperating Temperature Range .........-40C to 85C Storage Temperature Range.........–65C to 125C Lead Temperature (Soldering,5sec)...........300C°°°°°Recommended Operating ConditionsJunction Temperature 40to 125-...............C C..................C C°°°°Ambient Temperature 40to 85-Thermal InformationXX:Product Code V:Voltage Code Y:Year W:WeeklyElectrical CharacteristicT =25,V =2.4V,I =750mA,V =V ,L=2.2uH,C =10uF,C =10uF,unless otherwise noted.A IN LED SHDN IN ΙΝO ℃Note1:V -LED Forward VoltageF ParameterSymbol ConditionsMin TypMax Unit Input Voltage Range V IN 0.9VF-0.2(note 1)V Feedback Voltage V FB 9095100mV Start-up Voltage V START V IN :0V →3V I LED =270mA 0.9V Hold Voltage V HOLD V IN :3V →0V I LED :750mA →200mA0.75V Oscillator Frequency F OSC 0.85 1.01.15MHz SHDN Input High V SH V IN =1.8V 1.0V SHDN Input LowV SL V IN =1.8V0.4V Over Temperature Shutdown OTS 150℃Over Temperature Hysteresis OTH 15℃Maximum Output Current RangeI O(MAX)750mA Quiescent Current I Q I LED =0mA,V O =3.4V,Device Switching at 1MHz 13mA Shutdown Current I SD Shutdown mode 1uA Switch on Resistance R DSON V O =3.4V 0.1ΩCurrent Limit I LIM V O =3.4V 2A EfficiencyηI LED =750mA90%Typical Performance CharacteristicsT =25,L=2.2uH ,C =10uF,C =10uF,unless otherwise noted.A ΙΝΟ℃400450500550600650700750800Input Voltage(V)L E D C u r r e n t (m A )50556065707580859095100 1.21.51.82.12.42.733.33.6Input Voltage(V)F e e d b a c k V o l t a g e (m V )5007009001100130015001700190021002300 1.21.51.82.12.42.733.33.6Input Voltage(V)D C I n p u t C u r r e n t (m A )1.LED Power Efficiency vs Input Voltage2.LED Current vs Input Voltage4.Feedback Voltage vs Input Voltage (I =750mA@V =3.7V)LED F 4050607080901001.21.51.82.12.42.733.33.6Input Voltage(V)L E D P o w e r E f f i c i e n c y (%)Typical Performance Characteristics (continued )7.Overvoltage ProtectionSW V AC CouplingO IL5.Switching Waveform6.Start-Up WaveformSHDNI LV OInductor SelectionCapacitor SelectionDiode SelectionLED Current SettingThe PAM2803can use small value inductors due to its switching frequency of 1MHz.The value of inductor will focus in the range of 2.2uH to 4.7uH for most PAM2803applications.In typical high c u r r e n t w h i t e L E D a p p l i c a t i o n s ,i t i s recommended to use a 4.7uH inductor.The inductor should have low DCR (DC resistance)to minimize the I R power loss,and it requires a current rating of 2A to handle the peak inductor current without saturating.An input capacitor is required to reduce the input ripple and noise for proper operation of the PAM2803.For good input decoupling,Low ESR (equivalent series resistance)capacitors should be used at the input.At least 2.2uF input capacitor is recommended for most applications.A minimum output capacitor value of 6.8uF is r e c o m m e n d e d u n d e r n o r m a l o p e r a t i n g conditions,while a 10uF-22uF capacitor may be required for higher power LED current.A reasonable value of the output capacitor depends on the LED current.The ESR of the output capacitor is the important parameter to determine the output voltage ripple of the converter,so low ESR capacitors should be used at the output to reduce the output voltage ripple.The small size of ceramic capacitors is an excellent choice for PAM2803applications.The X5R and X7R types are preferred because they maintain capacitance over wide voltage and temperature ranges.It's indispensable to use a Schottky diode rated at 2A with the ing a Schottky diode with a lower forward voltage drop is better to improve the power LED efficiency,and its voltage rating should be greater than the output voltage.I n a p p l i c a t i o n ,t h e O N S e m i c o n d u c t o r MBRA210LT3G is recommended.The LED current is set by the single external Rs resistor connected to the FB pin as shown in the typical application circuit on page 1.The typical FB reference is internally regulated to 95mV.The LED current is 95mV/Rs.It's recommended to use a 1%or better precision resistor for the better LED current accuracy.The formula and table 1for Rs selection are shown as follows:Rs=95mV/I Table 1.Rs Resistor Value Selection 2LEDPCB Layout GuidelinesAs for all switching power supplies,the layout and components placement of the PAM2803is an important step in the design;especially at h i g h p e a k c u r r e n t s a n d h i g h s w i t c h i n g frequencies.The input capacitor and output capacitor should be placed respectively as close as possible to the input pin and output pin of the IC;the inductor and schottky diode should be placed as close as possible to the switch pin by using wide and short traces for the main current path;the current sense resistor should be placed as close as possible between the ground pin and feedback pin.Application InformationStandard Value(Ω)I LED (mA)0.185280.156330.127920.10950Ordering InformationPlease consult PAM sales office or authorized Rep Distributor for detailed ordering information../FB Voltageof Pins Type PAM2803Pin Configuration Package Type Number of PinsFB Voltage A Type1.SW2.GND3.FB4.SHDN5.VOUT6.VINA:SOT-23-6F:6095:95mVPart Number Marking Package Type Standard Package PAM2803AAF095CFAYWSOT-23-63,000Units/Tape&ReelOutline DimensionSOT 236--GAUGE PLANE SEATING PLANEBASESECTION A-ASEE VIEWSSymbol AA1A2b c D E Spec 1.20±0.250.10±0.05 1.10±0.20.40±0.10.15±0.0.7 2.90±0.12.80±0.2Symbol E11e e 1LL1θSpec1.60±0.10.95BSC1.90BSC 0.55±0.250.60REF4°±4°。

芯片2803资料

PIN CONNECTION (top view)

April 1993

1/8

ULQ2801A - ULQ2802A - ULQ2803A - ULQ2804A - ULQ2805A

SCHEMATIC DIAGRAM AND ORDER CODES For ULQ2801A (each driver for PMOS-CMOS) For ULQ2802A (each driver for 14-15 V PMOS)

Ci Input Capacitance

tPLH Turn-on Delay Time tPHL Turn-off Delay Time

IR Clamp Diode Leakage Current

VF Clamp Diode Forward Voltage

Test Conditions

VCE = 50V TJ = 105°C, VCE = 50V TJ = 105°C for ULQ2802A VCE = 50V, Vi = 6V

Symbol Vo Vi

IC IB Ptot

Tamb Tstg

Parameter

Output Voltage Input Voltage for ULQ2802A, 2803A, 2804A

for ULQ2805A Continuous Collector Current Continuous Base Current

500 µA 1b 500 µA 1b

0.9 1.1 V 1.1 1.3 V 2 1.3 1.6 V

0.82 1.25 mA 0.93 1.35 mA 0.35 0.5 mA 3

1 1.45 mA

1.5 2.4 mA

2803芯片

2803芯片2803芯片(HT2803)是一种面向电子产品设计和嵌入式系统开发的低功耗、高性能单片机芯片。

它由Hangzhou Silan Microelectronics Co., Ltd生产,适用于家电、智能终端、工业控制和汽车电子等领域。

HT2803芯片采用先进的技术和设计,具有以下主要特点:1. 高性能:采用高速、低功耗的ARM Cortex-M3内核,频率可达80MHz,可以处理复杂的嵌入式应用程序。

此外,它还配备了丰富的外设接口,如UART、I2C、SPI等,方便与外部设备进行通信和数据交换。

2. 低功耗:HT2803芯片在设计上注重了功耗的优化。

它通过合理的功耗管理策略和低功耗模式的支持,可以将功耗降到最低,延长电池寿命,适合那些对长时间运行的电池供电设备。

3. 强大的时钟和计时功能:HT2803芯片集成了多种时钟和计时功能,包括实时时钟(RTC)、定时器(Timer)和看门狗定时器(Watchdog Timer),可以满足各种实时需求,如精确时间戳、定时中断等。

4. 多种存储和扩展能力:HT2803芯片内部集成了不同容量的Flash存储器和SRAM,可以存储大量程序代码和数据。

此外,它还拥有多个外部扩展存储接口,如SD卡接口和SPI Flash接口,方便用户根据需求扩展存储空间。

5. 强大的通信接口:HT2803芯片支持多种通信接口,包括UART、I2C、SPI和USB等。

这些通信接口可以与其他外设设备进行数据交换和通信,方便实现设备之间的互联互通。

6. 安全性保护:HT2803芯片具有丰富的安全特性,如时钟和数据加密、防篡改保护和独立的安全存储区域。

这些安全特性可以有效保护设备的安全性和数据的机密性。

综合来说,HT2803芯片是一款高性能、低功耗的嵌入式单片机芯片,适用于多种领域的电子产品设计和开发。

它的强大的功能和丰富的外设接口,可以满足各种应用需求,并保证设备的可靠性和安全性。

DSC2803X 数字信号控制器 数据手册说明书

Haawking DSC2803X数字信号控制器数据手册编号:北京中科昊芯科技有限公司2022年03月V1.3历史版本记录目录1.器件概述 (5)1.1产品特性 (5)1.2应用 (6)2.DSC28034简介 (7)2.1器件特性 (7)2.2产品编码 (8)2.3引脚分配 (9)2.4信号说明 (10)3.功能概述 (19)3.1系统架构 (19)3.2内存映射 (19)3.3简要说明 (21)3.3.1HXS320F2803x DSC (21)3.3.2内存总线 (21)3.3.3外设总线 (21)3.3.4实时JTAG和分析 (22)3.3.5闪存 (22)3.3.6M0、M1、L0、L1SARAM (22)3.3.7引导ROM (23)3.3.8.1JTAG引导模式 (23)3.3.8.2GetMode获取模式 (24)3.3.8.3引导加载器使用的外设引脚 (24)3.3.8安全性 (24)3.3.9外设中断扩展(PIE)模块 (25)3.3.10外部中断(XINT1-XINT3) (26)3.3.11内部振荡器、外部振荡器和PLL (26)3.3.12看门狗 (26)3.3.13外设时钟 (26)3.3.14低功耗模式 (27)3.3.15通用输入/输出(GPIO)复用器 (27)3.3.1632位CPU定时器(0,1,2) (28)3.3.18控制外设 (28)3.3.19串行端口外设 (29)3.4寄存器映射 (29)3.5器件仿真寄存器 (30)3.7LDO/VREG/BOR/POR (34)3.7.1VREG (34)3.7.1.1使用片上VREG (35)3.7.1.2不使用片上VREG (35)3.7.2片上上电复位(POR)和掉电复位(BOR)电路 (35)3.8系统控制 (36)3.8.1内部零引脚振荡器 (39)3.8.2晶体振荡器选项 (40)3.8.3基于PLL的时钟模块 (41)3.9低功耗模块 (41)4.外设 (43)4.1模拟器件 (43)4.1.1特性 (43)4.1.2ADC MUX多路复选 (47)4.1.3比较器模块 (47)4.2同步串行通信接口(SPI)模块 (48)4.3异步串行通信接口(SCI)模块 (51)4.4本地互联网络(Lin)模块 (53)4.5增强型控制器局域网络(eCAN)模块 (55)4.6内部集成电路接口(I2C)模块 (58)4.7增强型PWM模块(ePWM1/2/3/4/5/6/7) (61)4.8高分辨率PWM模块(HRPWM) (63)4.9增强型脉冲捕获模块(eCAP) (64)4.10高分辨率脉冲捕获模块(HRCAP) (66)4.11增强型正交编码器模块(eQEP) (67)4.12JTAG端口 (72)4.13GPIO控制寄存器 (74)4.14直接存储访问存储单元(DMA) (78)5.开发支持 (83)5.1集成开发环境Haawking IDE (83)5.2仿真器 (84)5.2.1简介 (84)5.2.2概览 (84)5.2.2.1特性 (85)5.3串口下载器 (86)5.4JTag下载工具 (87)6.1绝对最大额定值 (88)6.2推荐工作条件 (88)6.3ESD额定值 (89)6.4电气特性 (89)6.5功耗 (91)6.6散热设计考虑 (92)7.热特性/机械数据 (93)7.1LQFP80 (93)7.2TQFP64 (94)8.参考文献 (95)1.器件概述1.1产品特性高能效32位处理器(H28x内核)✓主频120MHz(周期8.33ns)✓哈佛(Harvard)总线架构✓硬件乘法/除法单元✓4/6通道高速DMA✓快速中断响应和处理✓统一存储器编程模型✓高效代码(使用C/C++和汇编语言)增强型控制外设✓增强型脉宽调制器(ePWM)✓高分辨率PWM(HRPWM)✓增强型捕获(eCAP)✓高分辨率输入捕获(HRCAP)✓增强型正交编码器脉冲(eQEP)✓模数转换器(ADC)✓片载温度传感器✓比较器芯片及系统开销✓3.3V单电源供电✓无上电顺序要求✓集成上电和掉电复位✓代码安全模块✓无模拟支持引脚时钟和系统控制✓两个内部12MHz零引脚振荡器✓片载振荡器/外部时钟输入✓看门狗定时器模组功能✓支持锁相环路(PLL)倍频系数动态调整多达45个具有输入滤波功能、可单独编程的多路复用GPIO✓可支持所有外设中断的外设中断扩展(PIE)模块✓三个32位CPU定时器✓每个ePWM模块中包含独立的32位定时器✓片载存储器✓闪存,SRAM,OTP,引导ROM可用128位安全密钥/锁✓保护安全内存块✓防止固件逆向工程✓串行端口外设✓一个SCI(UART)模块✓两个SPI模块✓一个内部集成电路(I2C)总线✓一个本地互连网络(LIN)总线✓一个增强型控制器局域网络(eCAN)总线高级仿真特性✓分析和断点功能✓封装选项✓80引脚薄型四方扁平(LQFP)封装✓64引脚TQFP封装✓温度选项✓工作温度:-40°至105°1.2应用●电器●医疗、保健与健身●楼宇自动化●电机驱动器●电动汽车、混合动力电动汽车(EV/HEV)动力传动●电力传送●工厂自动化●电信基础设施●电网基础设施●2.DSC28034简介2.1器件特性表2-1DSC2803x产品特性(1):ADC主频=30MHz时,转换速率是1.56Msps,由于可以同时采样转换两个通道,故最高速率为3.12Msps。

2803芯片

支持免费上传,创造良好化境。

Edited by Foxit Reader特征● 18位恒定电流输出。

℃除非有另外规定电气特性(VCC=5V, TA= 25,典型内部框图图1. WS2803内部模块框图芯片引脚设置图2.a SOP-28 图2.b DIP-28引脚功能描述到地的电阻就可以将WS2803的恒定电流输出设定在22mA 。

R EXT =1.5K 时,I OUT =18.6mAWS2803芯片的消耗功率 (PD)WS2803芯片所消耗的最大功率由PD(max)=(Tj-Ta)/Rth(j-a)决定,当所有18个输出通道均开启的时候,芯片中实际消耗的功率为。

因此,为了保证PD(act )≤PD(MAX),最大驱动电流与占空比的关系为)×××(+)×(=)(18DS OUT DD DD D V Duty I V I act P 18///)×(=)(Duty V V I R T T IDS CC CC a jth a j OUT。

当使用环境温度上升时,芯片消耗的最大功率为PD(MAX)=(Tj-Ta)/Rth(j-a),当使用环境温度上升时,芯片所允许消耗的最大功率将降低。

负载供电电压 (V LED )WS2803所设计的VDS 操作范围为0.8~5V ,考虑到芯片封装的散热效率的显示,VDS 可以升高,但是必须要保证PD(ACT)>PD(MAX),,当V LED =24V 时 and V DS =V LED -V F ,,V LED 为负载供电电压,在实际应用中最好将VLED 设定在满足输出驱动要求的最低电压。

在有必要时,需要在芯片的外部添加一个分压器,产生一个压降V DROP 来避免过多的功率消耗在芯片上,该分压器应该满足V DS =(V LED -V F )-V DROP如下图所示,电阻和齐纳二极管都可以用来降低WS2803的功耗。

DVSA2805S中文资料

VPT Inc.2801 Commerce StreetBlacksburg, VA 24060Sales Info: (425) 337-2482 FAX: (603) 297-1160WEB: E-mail: mbosmann@DescriptionThe DVSA series of hybrid DC to DC conve r ters is able to operate at the full military (-55 °C to +125 °C) temperature range with no power derating. Unique to the DVSA series is a PATENTED magnetic feedback circuit that is fault tolerant and radiation immune. Operating at a nominal fixed frequ ency of 450kHz the regulated, isolated units utilize well controlled undervoltage lock out circuitry to eliminate slow start-up problems.Block DiagramDVSA2800S SeriesSpecificationsAbsolute Maximum RatingsInput Voltage (Continuous) 50 Vdc Input Voltage (Transient) 80 V (1sec) Output Power 16 Watts Power Dissipation, Full Load, T CASE = +125°C 2.5 Watts Junction Temperature rise to case +10°C Storage Temperature-65°C to +150°C Lead Solder Temperature for 10 seconds 270°C Weight15 gramsTcase = -55°C to +125°C, Vin = +28V ±5%, Full Load unless otherwise specifiedDVSA283R3S DVSA2805SDVSA2812SParameterConditions-55°C ≤TC ≤125°C,VIN = 28 VDC ±5%, Full LoadUnless otherwise specifiedMin Typ MaxMin Typ MaxMin Typ MaxUnitsStaticINPUTVoltage15 28 50 15 28 50 15 28 50 V Current 3Inhibited No Load3.5 40 5 60 3.5 40 5 60 3.5 40 5 60 mA mA Ripple Current Full Load, 20Hz to 10MHz 15 30 15 30 15 30 mA P-P Inhibit Pin Input 0 1.5 0 1.5 0 1.5 V Inhibit Pin Open Circuit Voltage 9.0 11.0 13.0 9.0 11.0 13.0 9.0 11.0 13.0 V UVLO Turn On 11.5 15.0 11.5 15.0 11.5 15.0 V UVLO Turn Off 11.0 14.5 11.0 14.5 11.0 14.5 V OUTPUTVoltage V OUTV OUTTcase = 25°C -55°C ≤ Tcase ≤ +125°C 3.27 3.20 3.30 3.30 3.33 3.40 4.95 4.85 5.00 5.00 5.05 5.15 11.88 11.64 12.0 12.0 12.12 12.36 V V Power 0 4 0 5 0 6 W Current V OUT0 1.21 0 1.0 0 0.50 A Ripple Voltage V OUT Full Load, 20Hz to 10MHz 10 30 10 30 15 40 mV p-p Line Regulation V OUT Vin = 15V to 50V 10 20 10 20 10 20 mV Load Regulation V OUT No Load to Full Load 20 40 20 40 20 40 mV EFFICIENCY64 68 68 72 73 77 % LOAD FAULT POWER DISSIPATIONOverload Short Circuit 3.0 2.5 3.0 2.5 3.0 2.5 W W CAPACITIVE LOAD 1000 1000 500 µF SWITCHING FREQUENCY400 450 525 400 450 525 400 450 525 kHz ISOLATION 500Vdc100 100 100 M Ω THERMAL RESISTANCE Case to Ambient (θCA) 28 28 28 °C/W MTBFMIL-HDBK-217F, AIF @ Tc = 55°C 457 457 457 kHrs DynamicLOAD STEPOutput Transient Recovery 2 V OUT Half Load to Full Load200 200 400 400200 200 400 400300 200 500 400mV PK µSec LINE STEPOutput Transient Recovery 2 V OUT V IN = 15V to 50V 200 200 400 400 200 200 400 400300 200 500 400mV PK µSecTURN ON DelayOvershoot 2V OUTV IN = 0V to 28V10 015 3310 015 5010 015 120mSec mV PKNOTES: 1. Dependent on output voltage. 2. Time for output voltage to settle within 1% of its nominal value 3. Derate linearly to 0 at 135°C.DVSA2800S SeriesSpecificationsAbsolute Maximum RatingsInput Voltage (Continuous) 50 Vdc Input Voltage (Transient) 80 V (1sec) Output Power 16 Watts Power Dissipation, Full, TCASE = +125°C 2.5 Watts Junction Temperature rise to case +10°C Storage Temperature-65°C to +150°C Lead Solder Temperature for 10 seconds 270°C Weight15 gramsTcase = -55°C to +125°C, Vin = +28V ±5%, Full Load unless otherwise specifiedDVSA2815SParameterConditions-55°C ≤TC ≤125°C,VIN = 28 VDC ±5%, Full LoadUnless otherwise specifiedMin Typ Max UnitsStaticINPUTVoltage15 28 50 V Current 3Inhibited No Load3.5 40 5 60 mA mA Ripple Current Full Load, 20Hz to 10MHz 15 30 mA P-P Inhibit Pin Input 0 1.5 V Inhibit Pin Open Circuit Voltage 9.0 11.0 13.0 V UVLO Turn On 11.5 15.0 V UVLO Turn Off 11.0 14.5 V OUTPUTVoltage V OUTV OUTTcase = 25°C -55°C ≤ Tcase ≤ +125°C 14.85 14.55 15.00 15.00 15.15 15.45 V V Power 0 6 W Current V OUT0 0.4 A Ripple Voltage V OUT Full Load, 20Hz to 10MHz 15 40 mV P-P Line Regulation V OUT Vin = 15V to 50V 10 20 mV Load Regulation V OUT No Load to Full Load 20 40 mV EFFICIENCY74 78 % LOAD FAULT POWER DISSIPATIONOverload Short Circuit 3.0 2.5 W W CAPACITIVE LOAD 500 µF SWITCHING FREQUENCY 400 450 525 kHz ISOLATION100 M Ω THERMAL RESISTANCE Case to Ambient (θCA) 28 °C/W MTBFMIL-HDBK-217F, AIF @ Tc = 55°C 457 kHrs DynamicLOAD STEPOutput Transient Recovery2 V OUT Half Load to Full Load300 200 500 400 mV PK µSecLINE STEPOutput Transient Recovery2 V OUT V IN = 15V to 50V 300 200 500 400 mV PK µSecTURN ON DelayOvershoot2V OUTV IN = 0V to 28V10 015 150mSec mV PKNOTES: 1. Dependent on output voltage. 2. Time for output voltage to settle within 1% of its nominal value. 3. Derate linearly to 0 at 135°C.DVSA2800S Without EMI filterFigure 1DVSA2800S With EMI filterFigure 2DVSA2800S SeriesOrdering InformationExample Part Number: DVSA2805DR/ESDVSA 28 05 S R /ESProduct Series Nominal Input Voltage Output Voltage No. Outputs Rad Hard Opt. Screening DVSA 28 28 Volts 03R3 3.3 Volts S Single None Std. None Standard05 5 Volts R 100kRad /ES Extended12 12 Volts /HB HB Screening15 15 VoltsLast Revised 6/26/00。

AMR特性需求分析

只供内部使用AMR特性需求分析报告标准类型TD-SCDMA文档编号XDTM 4.390.117 FRS版本号V1.0状态作者尉宁所属部门系统部提交日期2003-7-16I.文档控制1)2)3)文档发行范围目录1引言 (5)1.1 编写目的 (5)1.2 预期读者和阅读建议 (5)1.3 文档约定 (5)1.4 参考资料 (5)1.5 缩写术语 (6)1.6 定义 (8)2特性需求原由 (9)3功能性描述 (9)3.1 框架结构 (9)3.2 AMR语音编解码器概述 (9)3.3. AMR语音编解码器源控制速率操作 (11)3.3.1 AMR SCR概述 (11)3.3.2 AMR SCR操作 (12)3.3.2.1 TX侧的AMR SCR操作 (12)3.3.2.2 RX侧的AMR SCR操作 (13)3.3.2.3 语音激励检测器 (14)3.3.2.4 舒适噪声 (15)3.4 AMR语音编解码器差错隐藏 (15)3.5 AMR语音编解码器的编/解码 (17)3.5.1 编码器的功能性描述 (17)3.5.1.1 预处理 (17)3.5.1.2 线性预测分析和量化 (17)3.5.1.3 自适应码本 (18)3.5.1.4 代数码本 (18)3.5.1.5 增益量化 (19)3.5.2 解码器的功能性描述 (19)3.5.2.1 解码和语音合成 (19)3.5.2.2 后处理 (20)3.6 AMR语音编解码器的帧结构 (20)3.6.1 AMR 帧头和AMR 辅助信息 (20)3.6.2 AMR核心帧 (22)3.6.2.1 具有语音比特的AMR核心帧 (22)3.6.2.2具有舒适噪声比特的AMR核心帧 (22)3.6.3 AMR帧的组成 (23)3.7 AMR语音编解码器的接口实现 (25)3.7.1 Iu接口用户面(RAN) (25)3.7.1.1 Iu UP传输协议上的帧结构 (25)3.7.1.1.1 初始化 (25)3.7.1.1.2 时间对准 (27)3.7.1.2 比特映射 (28)3.7.1.3 帧处理 (29)3.7.1.3.1从TC到Iu接口的帧处理(下行) (29)3.7.1.3.2从Iu接口到TC的帧处理(上行) (30)3.7.2 Nb接口用户面(CN) (30)3.7.2.1 Nb UP传输协议上的帧结构 (30)3.7.2.1.1 初始化 (31)3.7.2.1.2 时间对准 (31)3.7.2.2 比特映射 (31)3.7.2.3 帧处理 (32)4附录 (32)A: AMR IF2帧格式 (32)B: 语音编码器比特顺序 (32)1引言1.1编写目的本特性需求分析报告对移动通信系统中AMR语音编解码器(声码器)组成、功能及作用进行了详细的分析。

SAM3S微控制器系列应用说明书

SAM3S Microcontroller Series Array Schematic Check List1.IntroductionThis Application Note is a schematic review check list for systems embedding Atmel’s SAM3S series of ARM® Cortex™-M3, Thumb®2-based microcontrollers.It gives requirements concerning the different pin connections that must be consid-ered before starting any new board design and describes the minimum hardware resources required to quickly develop an application with the SAM3S Series. It does not consider PCB layout constraints.It also gives advice regarding low-power design constraints to minimize power consumption.This Application Note is not intended to be exhaustive. Its objective is to cover as many configurations of use as possible.The Check List table has a column reserved for reviewing designers to verify that theline item has been checked.211061A–ATARM–28-Jul-10Application Note2.Associated DocumentationBefore going further into this Application Note, it is strongly recommended to check the latest documents for the SAM3S Series Microcontrollers on Atmel’s Web site.Table 2-1 gives the associated documentation needed to support full understanding of this appli-cation note.Table 2-1.Associated DocumentationInformationDocument TitleUser ManualElectrical/Mechanical CharacteristicsOrdering InformationErrata SAM3S Series Product DatasheetInternal architecture of processorThumb2 instruction sets Embedded in-circuit-emulatorThis part is integrated and formated according to the core integration in the SAM3S series. This information is fully detailed in the SAM3S Series ProductDatasheet.Cortex-M3 Technical Reference Manual (available from ARM Ltd.)Evaluation Kit User GuideSAM3S-EK Evaluation Board User Guide311061A–ATARM–28-Jul-10Application Note3.Schematic Check List;Signal Name Recommended Pin Connection DescriptionVDDIN1.8V to 3.6VDecoupling/Filtering capacitor (10μF or higher ceramic capacitor)(1)(2)Powers the voltage regulator, ADC, DAC and Analogcomparator power supply.VDDIO1.62V to 3.6VDecoupling/Filtering capacitors(100 nF and 2.2µF)(1)(2)Powers the peripheral I/Os, USB transceiver, Backuppart, 32kHz crystal oscillator and oscillator pads .Decoupling/Filtering capacitors must be added to improvestartup stability and reduce source voltage drop.Warning: At power-up VDDIO needs to reach 0.6Vbefore VDDIN reaches 1.0VVDDOUTDecoupling/Filtering capacitors(100 nF and 2.2µF)(1)(2)1.8V Output of the main voltage regulator.Decoupling/Filtering capacitors must be added toguarantee stability.411061A–ATARM–28-Jul-10Application NoteNote: RestrictionsWith Main Supply < 2.0 V, USB and ADC/DAC and Analog comparator are not usable.With Main Supply ≥ 2.0V and < 3V, USB is not usable.With Main Supply ≥ 3V, all peripherals are usable.VDDCOREMust be connected directly to VDDOUTpin.1.62V to 1.95VDecoupling capacitor (100 nF)(1)(2)Power the Core, the embedded memories and theperipherals power supply.VDDPLL 1.62V to 1.95VDecoupling capacitor (100 nF)(1)(2)Powers PLLA, PLLB, the Farst RC and the 3-20 MHzoscillator.GNDGroundGround pins GND are common to VDDIO, VDDPLL andVDDCORE;Signal Name Recommended Pin Connection Description511061A–ATARM–28-Jul-10Application Note;Signal Name Recommended Pin Connection DescriptionVDDIN1.8V to 3.6VDecoupling/Filtering capacitor (10μF or higher ceramic capacitor)(1)(2)Powers the voltage regulator, ADC, DAC and Analogcomparator power supply.VDDIO1.62V to 3.6VConnected to Main Supply Decoupling/Filtering capacitors(100 nF and 2.2 µF)(1)(2)Powers the peripheral I/Os.Decoupling/Filtering capacitors must be added to improvestartup stability and reduce source voltage drop.Warning: At power-up VDDIO needs to reach 0.6Vbefore VDDIN reaches 1.0VVDDOUTDecoupling/Filtering capacitors(100 nF and 2.2µF)(1)(2)1.8V Output of the main voltage regulator.Decoupling/Filtering capacitors must be added toguarantee stability.611061A–ATARM–28-Jul-10Application NoteNote: RestrictionsWith Main Supply < 2.0 V, USB and ADC/DAC and Analog comparator are not usable.With Main Supply ≥ 2.0V and < 3V, USB is not usable.With Main Supply ≥ 3V, all peripherals are usable.VDDCORE 1.62V to 1.95VConnected to VDDCORE Supply Decoupling capacitor (100 nF and2.2µF)(1)(2)Core, embedded memories and peripherals power supplyVDDPLL1.62V to 1.95VConnected to VDDCORE Supply Decoupling capacitor (100 nF and2.2µF)(1)(2)Powers PLLA, PLLB, the Farst RC and the 3-20 MHzoscillator.GNDGroundGround pins GND are common to VDDIO, VDDPLL andVDDCORE;Signal Name Recommended Pin Connection Description711061A–ATARM–28-Jul-10Application Note;Signal Name Recommended Pin Connection DescriptionVDDIN1.8V to 3.6VDecoupling/Filtering capacitor (10μF or higher ceramic capacitor)(1)(2)Powers the voltage regulator.VDDIO1.62V to 3.6VDecoupling/Filtering capacitors(100 nF and 2.2 µF)(1)(2)Powers the peripheral I/Os.Decoupling/Filtering capacitors must be added to improvestartup stability and reduce source voltage drop.Warning: At power-up VDDIO needs to reach 0.6Vbefore VDDIN reaches 1.0VVDDOUTDecoupling/Filtering capacitors(100 nF and 2.2µF)(1)(2)1.8V Output of the main voltage regulator.811061A–ATARM–28-Jul-10Application NoteNote: The two diodes provide a "switchover circuit" (for illustration purpose) between the backup battery and the main sup-ply when the system is put in backup mode.VDDCORE1.62V to 1.95VConnected to VDDOUT Supply Decoupling capacitor (100 nF)(1)(2)Core, embedded memories and peripherals power supplyVDDPLL1.62V to 1.95VConnected to VDDOUT Supply Decoupling capacitor (100 nF)(1)(2)Powers PLLA, PLLB, the Farst RC and the 3-20 MHzoscillator.GNDGroundGround pins GND are common to VDDIO, VDDPLL andVDDCORE;Signal Name Recommended Pin Connection Description911061A–ATARM–28-Jul-10Application Note1011061A–ATARM–28-Jul-10Application Note1111061A–ATARM–28-Jul-10Application NoteSerial Wire and JTAG (3)TCK/SWCLK/PB7Application dependantIf debug mode is not required this pin canbe use as GPIOReset State:- SWJ-DP Mode - Internal pull-up disabled - Schmitt Trigger enabled TMS/SWDIO/PB6Application dependantIf debug mode is not required this pin canbe use as GPIOReset State:- SWJ-DP Mode - Internal pull-up disabled - Schmitt Trigger enabled TDI/PB4Application dependantIf debug mode is not required this pin canbe use as GPIOReset State:- SWJ-DP Mode - Internal pull-up disabled - Schmitt Trigger enabled TDO/TRACESWO/PB5Application dependantIf debug mode is not required this pin canbe use as GPIO Reset State:- SWJ-DP Mode - Internal pull-up disabled - Schmitt Trigger enabledJTAGSEL Application dependant.Must be tied to V VDDIO to enter JTAGBoundary Scan.In harsh environments, It is strongly recommended to tie this pin to GND.Permanent Internal pull-down resistor (15 kOhm).Flash MemoryERASE/PB12Application dependant.If hardware erase is not required this pincan be use as GPIOInternal pull-down resistor (100kOhm).Must be tied to V VDDIO to erase the General Purpose NVM bits (GPNVMx), the whole Flash content and the securitybit.Reset state: Erase Input, with a 100 kOhm Internal pulldown and Schmitt trigger enabled Minimum debouncing time is 220 ms.Reset/TestNRSTApplication dependant.Can be connected to a push button forhardware reset.By default, the NRST pin is configured as an inputPermanent internal pull-up resistor to V VDDIO (15 kOhm).TST TST pin can be left unconnected innormal modeTo enter in FFPI mode TST pin must be tiedto V VDDIO.In harsh environments, It is strongly recommended to tie this pin to GND.Permanent internal pull-down resistor (15 kOhm).;Signal NameRecommended Pin ConnectionDescription1211061A–ATARM–28-Jul-10Application NotePIOPAx - PBx-PCxApplication Dependant (Pulled-up on V VDDIO )At reset, all PIOs are in IO or System IO mode with Schmitttrigger inputs and internal pull-up enabled.To reduce power consumption, if not used, the concerned PIO can be configured as an output and driven at ‘0’ withinternal pull-up disabled.Parallel Capture ModePIODC0-PIODC7Application Dependant V VDDIO Parallel Mode capture Data PIODCCLK Application Dependant V VDDIO Parallel Mode capture Clock PIODCEN1-2Application Dependant V VDDIOParallel Mode capture mode enableAnalog ReferenceADVREF2.0V to V DDIO (*)Decoupling capacitor(s).(*)2.0V is used for 10-bit ADC resolution only. In other case the minimum ADVREFvalue is 2.4V.ADVREF is a pure analog input.ADVREF is the voltage reference for the ADC,DAC andAnalog comparator.To reduce power consumption, if analog features are notused, connect ADVREF to GND.12-bit ADCAD0-AD140 to ADVREF.ADC Channels ADTRGV DDIO .ADC External Trigger input10-bit ADC (4)AD0-AD140 to ADVREF.ADC Channels ADTRGV DDIO .ADC External Trigger input12-bit DACDAC0-DAC11/6* ADVREF to 5/6* ADVREFDACTRGV DDIO .DAC External Trigger inputUSB Device (UDP)DDP/PB10Application dependent (3)If USB device support is not required thispin can be use as GPIO Reset State:- USB Mode - Internal Pull-down DDM/PB11Application dependent (3)If USB device support is not required thispin can be use as GPIOIReset State:- USB Mode - Internal Pull-down ;Signal Name Recommended Pin ConnectionDescription1311061A–ATARM–28-Jul-10Application NoteNotes: 1.These values are given only as a typical example.2.Decoupling capacitors must be connected as close as possible to the microcontroller and on each concerned pin.B Device Typical connection: copy of Figure 37-2 of the Datasheet4.Note that the ADC voltages in 10-bit mode resolution (ADC 12-bit in low resolution) can descend to 2.0V. Only one ADC isavailable on the SAM3S series.Static Memory Controller (SMC)D0-D15Application dependent.Data Bus (D0 to D15)Note: Data bus lines are multiplexed with the PIOB controller. Their I/O line reset state isinput with pull-up enabled .A0-A23Application dependent.Address Bus (A0 to A23)Note: Data bus lines are multiplexed withthe PIOB & PIOC controllers. Their I/O line reset state isinput with pull-up enabled .NWAITApplication dependent.NWAIT pin is an active low input.Note: NWAIT is multiplexed with PC18.;Signal NameRecommended Pin ConnectionDescription1411061A–ATARM–28-Jul-10Application Note4.SAM3S Boot Program Hardware ConstraintsSee AT91SAM Boot Program section of the SAM3S Series Datasheet for more details on the boot program.4.1SAM-BA BootThe SAM-BA ® Boot Assistant supports serial communication via the UART or USB device port:•UART0 Hardware Requirements: none.•USB Device Hardware Requirements:External Crystal or External Clock (1) with frequency of:11,289 MHz 12,000 MHz 16,000 MHz 18,432 MHzNote:1.Must be 2500 ppm and 1.8V Square Wave SignalTable 4-1.Pins driven during SAM-BA Boot Program executionPeripheral Pin PIO Line UART0URXD PA9UART0UTXDPA101511061A–ATARM–28-Jul-10Application Note5.Revision HistoryTable 5-1.Revision HistoryDoc. Rev Date Comments ChangeRequest Ref.11061A28-Jul-10First issueHeadquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong RoadKwun Tong, KowloonHong KongTel: (852) 2245-6100Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb Site/AT91SAMTechnical SupportAT91SAM SupportAtmel techincal supportSales Contacts/contacts/Literature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2010 Atmel Corporation. All rights reserved. Atmel®, Atmel logo, SAM-BA® and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM®, the ARMPowered® Logo, Thumb®, Cortex™ and others are the registered trade-marks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.11061A–ATARM–28-Jul-10。

amr机器人控制器技术参数

amr机器人控制器技术参数AMR机器人控制器技术参数随着自动化技术的迅速发展,自动导航机器人(AMR)在物流、仓储和制造等领域得到了广泛应用。

AMR机器人控制器是AMR系统中的核心部件之一,它负责控制机器人运动、导航和任务执行等关键功能。

本文将介绍AMR机器人控制器的一些重要技术参数。

1. 通信接口:AMR机器人控制器通常支持多种通信接口,如以太网、RS232、RS485等。

这些接口用于与其他设备进行数据交换和通信,实现机器人与系统的连接与控制。

2. 处理器性能:AMR机器人控制器的处理器性能直接影响机器人的运行效率和响应速度。

一般来说,控制器采用高性能的多核处理器,以保证机器人能够快速响应各种指令和任务。

3. 内存容量:AMR机器人控制器需要存储大量的地图数据、任务信息和运动规划算法等。

因此,控制器的内存容量需要足够大,以满足机器人运行期间的数据存储和处理需求。

4. 电源要求:AMR机器人控制器通常需要工作在恶劣的环境中,因此对电源的要求也比较高。

控制器需要具备稳定的电源供应,并具备一定的防护措施,以保证机器人在各种工作环境下的可靠性和稳定性。

5. 系统兼容性:AMR机器人控制器需要能够兼容不同类型的机器人和传感器设备。

因此,控制器需要支持多种通信协议和接口标准,以便与其他设备进行无缝集成和协同工作。

6. 安全性能:AMR机器人通常需要在人员密集的环境中工作,因此安全性是一个非常重要的考虑因素。

AMR机器人控制器需要具备安全防护功能,能够实时监测机器人的运动状态,并能够及时响应紧急情况,以保证人员的安全。

7. 软件功能:AMR机器人控制器的软件功能包括运动控制、导航规划、路径优化和任务调度等。

控制器需要具备高效的算法和强大的软件功能,以实现机器人的智能化运行和高效的任务执行。

8. 扩展性:AMR机器人通常需要根据实际应用需求进行功能扩展和定制化开发。

因此,控制器需要具备良好的扩展性,能够支持各种附加模块和传感器的集成,以满足不同应用场景的需求。

AMR系统简介全面的

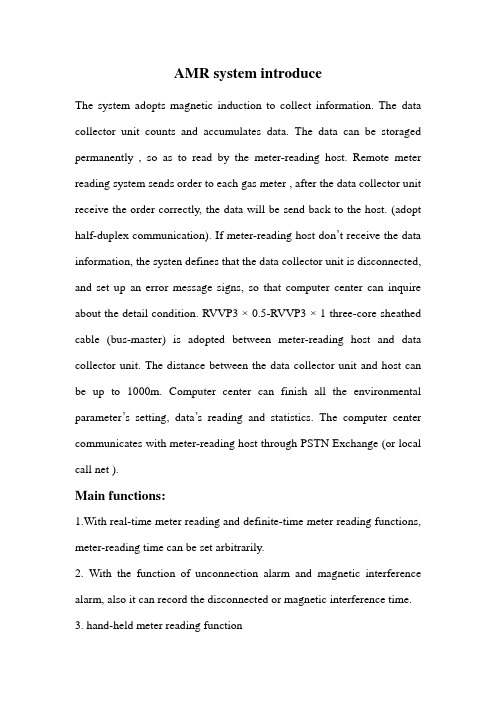

AMR system introduceThe system adopts magnetic induction to collect information. The data collector unit counts and accumulates data. The data can be storaged permanently , so as to read by the meter-reading host. Remote meter reading system sends order to each gas meter , after the data collector unit receive the order correctly, the data will be send back to the host. (adopt half-duplex communication). If meter-reading host don’t receive the data information, the systen defines that the data collector unit is disconnected, and set up an error message signs, so that computer center can inquire about the detail condition. RVVP3 × 0.5-RVVP3 × 1 three-core sheathed cable (bus-master) is adopted between meter-reading host and data collector unit. The distance between the data collector unit and host can be up to 1000m. Computer center can finish all the environmental parameter’s setting, data’s reading and statistics. The computer center communicates with meter-reading host through PSTN Exchange (or local call net ).Main functions:1.With real-time meter reading and definite-time meter reading functions, meter-reading time can be set arbitrarily.2. With the function of unconnection alarm and magnetic interference alarm, also it can record the disconnected or magnetic interference time.3. hand-held meter reading function4. The system has comprehensive functions of gas balance, statistic, analyzing, printing etc5. Realize gas charge’s automatic statistics .Technical indicators:1. Meter-reading host Capacity: ≤510 data collector unit2. Adopt RS485 communication method2.Meter-reading host communication mode: up way MODEM-PSTN interface , RS32 interface . down way half-duplex bus-master interface (bus sheathed three-core wire)3. bus-master power supply: 20VDC4.. Power consumption: static work <5W, when reading <25W5. Host power supply; 220V AC, 50HZ6. Host Dimension: 370 × 250 × 57 (mm)Performance :reading system:1.Remote meter reading system is a more perfect administer system, which can realize the gas meter’s automatic and remote reading. The administer can modify the unit price to meet market changes . The computer center administers the clooector unit on the gas meter., and the collector records the pulses which the signal acquisition card sents from the gas meter, and then translate the signal into data( the gas volume CBM). The other function of collecter unit is to transfer this data to thecomputer center to calculate, the result will be storaged to the databank. The pathway: data collector unit→RS485 →meter reading host→PSTN line→ computer center..2.Remote meter reading system have the advantage of long service life, stability , accurate measurement .3. When the power supply system is power off , the collector still can work in normal condition, and automatically record the number of pulses to ensure data’s accurate and complete . The clock and calendar will be correct all the time after the power is back.4. Collector is installed in the external of gas meter, moisture-proof and seal, doesn’t affect y measurement accuracy.5. "AMR softwares" requirements WINDOWS98 operation system or higher operation system. The software sets different level operation permission for different operater. Each rank has its own passport, which can ensure data ‘s security and reliable, to prevent misoperation. System reliabilityThe reliability is very important in this system. Series measure is taken to ensure the system’s reliability from software and hardware.1. PowerPower is to necessary for the system, there are following two method to supply power.1. 220V AC power supply: 220V AC voltage will be converted into astable 12V DC voltage systems.2. UPS power supply: When there are something wrong with 220V AC power supply , UPS will supply power for the system.3. There are battery inside the data data collector unit .In addition, the system adoptS advanced technology, when all the power cut off suddenly, the data can be stored correctly.Filtering software can ensure the accuracy of the accumulated signal.4. Data CommunicationIt adopts special and intensified RS485 communication ways between computer administer center and data data collector unit . it is 4 times load capacity than the generally 485 communication ways . It has a strong anti-interference ability of the common mode, at the same time, variety of calibration is done to ensure the accuracy of data’ s tranfer. System’s management1. User management: increase, delete, save, modify and statistics the user’s information.2.Gas meter management: A. Increase, delete, save, modify and statistical gas meter’s information. B. Record the gas meter’s calibration and change condition C. Display metr reading and charge condition, and so on.3. Gas using management : The administer can set diffenert charge standard for different using’s purpose and useing time. There \also aredifferent charge way when the gas using is within and beyond the standard volume4. Statistics and analysis: The software has powerful reporting capabilitie, such as statistics and analysis summary statements. At the same time it can generate curves, histograms, pie charts and other statements, besides, all this can be printed.Data collector unit introduce1. Collect gas meter pulse signals, data processing and storage.2. Display date, time, address , the user numbers, data collector unit parameters, gas volume.3. Infrared communication function: Pocket PC users (portable) wireless infrared data collector unit can collet data when necessary4. Wen the city pow cut off, it can automatically switch to a back-up battery power supply. After the city power is recover, back to the city power supply automatically, and charging batteries. Power switch does not affect the normal operation of the system.5. Data collector unit is consist of the mainboard, wiring board, power supply module, bus communication module, LCD modules. If any module fails, it is convenient to maintenance.6. Data storage and protection: the data collector unit collects data every five minutesand storage to the EEPROM, The data don't lose when power off.after power-down7. Anti-lightning function, There are three class anti-lightning design.8. The data collector unit has the function of unconnect, short-circuit fault detection.9. Coupled with the appropriate tools, engineers can easily detect every meter whether it’s correct from the sensor to data collector unit.10. Data collector unit has the function of RS-485 fault detection。

UCC2803QDREP资料

元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. To minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third–party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Mailing Address:Texas InstrumentsPost Office Box 655303Dallas, Texas 75265Copyright 2003, Texas Instruments Incorporated。

MEMORY存储芯片TMS320F28335PTPQ中文规格书

RMII_MHz_50_CLK RMII_TXENRMII_TXD[1:0]RMII_RXD[1:0]RMII_CRS_DVRMII_RXER116TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical Specifications Copyright ©2008–2014,Texas Instruments IncorporatedTable 6-37.EMAC Control Module RAMBYTE ADRESSREGISTER DESCRIPTION 0x01E20000-0x01E21FFF EMAC Local Buffer Descriptor MemoryTable 6-38.RMII Timing RequirementsNo.PARAMETER MIN TYP MAX UNIT 1tc(REFCLK)Cycle Time,RMII_MHZ_50_CLK 20ns 2tw(REFCLKH)Pulse Width,RMII_MHZ_50_CLK High 713ns 3tw(REFCLKL)Pulse Width,RMII_MHZ_50_CLK Low 713ns 6tsu(RXD-REFCLK)Input Setup Time,RXD Valid before RMII_MHZ_50_CLK High 4ns 7th(REFCLK-RXD)Input Hold Time,RXD Valid after RMII_MHZ_50_CLK High 2ns 8tsu(CRSDV-REFCLK)Input Setup Time,CRSDV Valid before RMII_MHZ_50_CLK High 4ns 9th(REFCLK-CRSDV)Input Hold Time,CRSDV Valid after RMII_MHZ_50_CLK High 2ns 10tsu(RXER-REFCLK)Input Setup Time,RXER Valid before RMII_MHZ_50_CLK High 4ns 11th(REFCLKR-RXER)Input Hold Time,RXER Valid after RMII_MHZ_50_CLK High 2nsNote:Per the RMII industry specification,the RMII reference clock (RMII_MHZ_50_CLK)must have jitter tolerance of 50ppm or less.Table 6-39.RMII Switching CharacteristicsNo.PARAMETER MIN TYP MAX UNIT 4td(REFCLK-TXD)Output Delay Time,RMII_MHZ_50_CLK High to TXD Valid 2.513ns 5td(REFCLK-TXEN)Output Delay Time,RMII_MHZ_50_CLK High to TXEN Valid2.513nsFigure 6-30.RMII Timing DiagramAHCLKRx ACLKRx AFSRx AMUTEINx AMUTEx AFSXx ACLKXx AHCLKXx AXRx[0]AXRx[1]AXRx[y]PinsFunction Receive Master Clock Receive Bit Clock Receive Left/Right Clock or Frame Sync Transmit Master Clock Transmit Bit Clock Transmit Left/Right Clock or Frame Sync Transmit/Receive Serial Data Pin Transmit/Receive Serial Data Pin Transmit/Receive Serial Data PinThe McASPs DO NOT have dedicated AMUTEINx pins.119TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated (1)Pins available are the maximum number of pins that may be configured for a particular McASP;not including pin multiplexing.6.16Multichannel Audio Serial Ports (McASP0,McASP1,and McASP2)The McASP serial port is specifically designed for multichannel audio applications.Its key features are:•Flexible clock and frame sync generation logic and on-chip dividers•Up to sixteen transmit or receive data pins and serializers•Large number of serial data format options,including:–TDM Frames with 2to 32time slots per frame (periodic)or 1slot per frame (burst)–Time slots of 8,12,16,20,24,28,and 32bits–First bit delay 0,1,or 2clocks–MSB or LSB first bit order–Left-or right-aligned data words within time slots•DIT Mode (optional)with 384-bit Channel Status and 384-bit User Data registers•Extensive error checking and mute generation logic•All unused pins GPIO-capableAdditionally,while the C674x McASP modules are backward compatible with the McASP on previous devices;the C674x McASP includes the following new features:•Transmit &Receive FIFO Buffers for each McASP.Allows the McASP to operate at a higher sample rate by making it more tolerant to DMA latency.•Dynamic Adjustment of Clock Dividers–Clock Divider Value may be changed without resetting the McASPThe three McASPs on the C6745/6747are configured with the following options:Table 6-43.C6745/6747McASP Configurations (1)ModuleSerializers AFIFO DIT C6745/6747Pins McASP01664Word RX 64Word TX N AXR0[15:0],AHCLKR0,ACLKR0,AFSR0,AHCLKX0,ACLKX0,AFSX0,AMUTE0McASP11264Word RX 64Word TX N AXR1[11:10],AXR1[8:0],AHCLKR1,ACLKR1,AFSR1,AHCLKX1,ACLKX1,AFSX1,AMUTE1McASP2416Word RX 16Word TX Y AXR2[3:0],AHCLKR2,ACLKR2,AFSR2,AHCLKX2,ACLKX2,AFSX2,AMUTE2Figure 6-33.McASP Block Diagram。

ME2803中文资料(2015版)

Units

-VDET -VDET(S)>2.2V VHYS VIN=2V (1.0V-1.5V) VIN =3.5V (1.6V-2.5V)

V

V

Supply Current

ISS

VIN=4.5V (2.6V-3.9V) VIN =6V (4.0V-5.6V) VIN=7V (5.7V-6.5V) -

V02

Page 3 of 11

ME2803

Functional Description:

1、 When input voltage (VIN) rises above detect voltage (–VDET), output voltage (VOUT) will be equal to VIN. 2、 When input voltage (VIN) falls below detect voltage (–VDET), output voltage (VOUT) will be equal to the ground voltage (GND) level. 3、 When input voltage (VIN) falls to a level below that of the minimum operating voltage (VMIN), output will become unstable. In this condition, V IN will equal the pulled-up output (should output be pulled-up.) 4、 When input voltage (VIN) rises above the ground voltage (GND) level, output will be unstable at levels below the minimum operating voltage (VMIN). Between the VMIN and detect release voltage +VDET) levels, the ground voltage (GND) level will be maintained. 5、 When input voltage (VIN) rises above detect release voltage (+VDET), output voltage (VOUT) will be equal to VIN. 6、 The difference between +VDET and –VDET represents the hysteresis range.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

09/15/081Descriptionn 30 Watts Output Powern Available in 3.3, 5, 12 and 15 Volt Outputs n 18 - 40 VDC Input Range (28 VDC Nominal)n Total Ionizing Dose > 25KRads (Si)n SEE Hardened to LET up to 60 MeV .cm 2/mg n -55°C to +125°C Operating Range n Indefinite Short Circuit Protection n External Synchronizationn Shutdown from External Signal n Flexible Mountingn Fully Isolated - Input to Output and to Case n Complimentary EMI Filter Available n Electrical Performance Similar to ATR28XXS Seriesn Standard Microcircuit Drawings AvailableFeaturesThe AMR28XXS series of DC/DC converter modules has been specifically designed for operation in moderate radiation environments supplementing the higher radiation performance available in the International Rectifier ART2815T converter series.Environments presented to space vehicles operating in low earth orbits, launch boosters, orbiting space stations and similar applications requiring a low power,high performance converter with moderate radiation hardness performance will be optimally served by the AMR28XXS Series.The AMR28XXS has been designed for high density using chip and wire hybrid technology that complies with the class H requirements of MIL-PRF-38534.Manufactured in a facility fully qualified to MIL-PRF-38534, these converters are fabricated utilizing DSCC qualified processes. For available screening options,refer to device screening table in the data sheet.Applicable generic lot qualification test data including radiation performance can be made available on request.Consult IR Santa Clara for special requirements.AMR28XXS SERIES28V Input, Single OutputThe physical configuration of the AMR28XXS series permits mounting directly to a heat conduction surface without the necessity of signal leads penetrating the heat sink surface. This package configuration permits greater independence in mounting and more secure mechanical attachment than traditional radially leaded packages. International Rectifier ’s rugged ceramic seal pins are used exclusively in the package thereby assuring long term hermeticity.AMRHYBRID - HIGH RELIABILITY RADIATION TOLERANT DC/DC CONVERTER.PD-94691BAMR28XXS SeriesFor Notes to Specifications, refer to page 4Static Characteristics -55°C ≤ T CASE ≤ +125°C, V IN =28 V DC ±5%, C L =0, unless otherwise specified.ParameterGroup A SubgroupsTest Conditions Min Nom Max UnitInput Voltage16 28 40 V Output VoltageAMR2803R3SAMR2805S AMR2812S AMR2815SAMR2803R3S AMR2805S AMR2812S AMR2815S1 1 1 1 2, 3 2, 3 2, 3 2, 3 Iout=0 3.25 4.95 11.88 14.85 3.20 4.90 11.70 14.60 3.30 5.00 12.00 15.003.35 5.05 12.12 15.15 3.40 5.10 12.30 15.40V Output Current1AMR2803R3SAMR2805S AMR2812S AMR2815S 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 Vin = 18, 28, 40 Volts7500 6000 2500 2000 mA Output PowerAMR2803R3S All Others1, 2, 3 1, 2, 3 100% load25 30 WOutput Ripple Voltage2AMR2803R3SAMR2805S AMR2812S AMR2815S1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 Vin = 18, 28, 40 Volts BW = 20 Hz to 2 MHz60 60 60 75 mV PPOutput Voltage Regulation3 Line AMR2803R3S AMR2805S AMR2812S AMR2815S Load AMR2803R3SAMR2805S AMR2812S AMR2815S1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 31, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 V in = 18, 28, 40 Volts Iout = 0, 50%, and 100% load±10 ±10 ±30 ±40 ±10 ±10 ±50 ±50±30 ±30 ±60 ±75 ±50 ±50 ±120 ±150mV3AMR28XXS SeriesStatic Characteristics (Continued) -55°C ≤ T CASE ≤ +125°C, V IN =28 V DC ±5%, C L =0, unless otherwise specified.For Notes to Specifications, refer to page 4ParameterGroup A SubgroupsTest Conditions Min Nom Max Unit Input CurrentNo Load AMR2803R3S AMR2805S AMR2812S AMR2815SInhibited All 1, 2, 31, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 Iout=0, Inhibit =open Inhibit shorted to input return20 20 20 20 8.0 50 50 75 100 18 mA Input Ripple Current21, 2, 3 Vin = 16, 28, 40 Volts, 100% load, BW = 20 Hz to 2 MHz50 mA PP EfficiencyAMR2803R3S AMR2805S AMR2812S AMR2815S AMR2803R3SAMR2805S AMR2812S AMR2815S 1 1 1 1 2, 3 2, 32, 3 2, 3 100% load 74 76 80 79 70 72 75 75%Isolation1Input to output or any pin to case(except case ground pin) at 500Vdc100 M ΩCapacitive Load4, 54 No effect on dc performance 500 µF Short Circuit Power Dissipation 1, 2, 319 W Switching Frequency 4, 5, 6 100% load 500 550 600 KHz Sync Frequency Range 4, 5, 6100% load500700KHzMTBFMIL-HDBK-217F, N2SF @ Tc = 35°C 940 KhrsWeight68 gAMR28XXS SeriesDynamic Characteristics -55°C ≤ T CASE ≤ +125°C, V IN =28 V DC ±5%, C L =0, unless otherwise specified.ParameterGroup A SubgroupsTest Conditions Min Nom Max Unit Output Response To StepTransient Load Changes7AMR2803R3S AMR2805S AMR2812S AMR2815SAMR2803R3S AMR2805S AMR2812S AMR2815S 4, 5, 6 4, 5, 6 4, 5, 6 4, 5, 6 4, 5, 6 4, 5, 6Load step 50%Ù 100% Load step 8% Ù 50% -500 -500 -800 -1000 -500 -500 -1000 -1000+500 +500 +800 +1000 +500 +500 +1000 +1000mV pkRecovery Time, Step TransientLoad Changes 7, 84, 5, 6Load step 50%Ù 100% or Load step 8% Ù 50%200 µs Output Response Transient StepLine Changes 5, 9AMR2803R3S AMR2805S AMR2812SAMR2815S 4, 5, 64, 5, 64, 5, 6 4, 5, 6 Input step from/to 18 to 40Vdc, 100% load -500 -500 -1200 -1500+500 +500 +1200 +1500mV pkRecovery Time Transient StepLine Changes 5, 8, 94, 5, 6Input step from/to 18 to 40Vdc, 100% load10 ms Turn On OvershootAMR2803R3S AMR2805S AMR2812S AMR2815S 4, 5, 6 4, 5, 6 4, 5, 6 4, 5, 6 0% load to 100% load500 500 800 1000 mV pkTurn On Delay104, 5, 60% load to 100% load 25 ms Short Circuit Recovery 5, 104, 5, 625ms1 Parameter guaranteed by line and load regulation tests.2 Bandwidth guaranteed by design. Tested for 20 KHz to 2.0 MHz.3 Output voltage measured at load with remote sense leads connected across load.4 Capacitive load may be any value from 0 to the maximum limit without compromising dc performance. A capacitive load in excess of the maximum limit will not disturb loop stability but may interfere with the operation of the load fault detection circuitry, appearing as a short circuit during turn on.5 Parameter shall be tested as part of design characterization and after design or process changes. Parameters shall be guaranteed to the limit specified in Electrical Specifications.6 Load step transition time between 2.0 and 10 microseconds.7 Recovery time is measured from the initiation of the transient to where V OUT has returned to within ±1 % of V OUT at 50 percent load.8 Input step transition time between 2.0 and 10 microseconds.9 Turn on delay time measurement is for either a step application of power at the input or the removal of a ground signal from the inhibit pin while power is applied to the input.Notes to Specifications5AMR28XXS SeriesBlock DiagramApplication InformationInhibit Function (Enable)EMI FilterDevice SynchronizationConnecting the inhibit input to input common will cause the converter to shut down. It is recommended that the inhibit pin be driven by an open collector device capable of sinking at least 400 µA of current.The open circuit voltage of the inhibit input is 10 +1.0 V DC .An optional EMI filter is available (AFH461) that will reduce the input ripple current to levels below the limits imposed by MIL-STD-461 CE03.When multiple DC/DC converters are utilized in a single system, significant low frequency noise may be generated due to a small difference in the switching frequency of the converters (beat frequency noise). Because of the low frequency nature of this noise (typically less than 10 KHz), it is difficult to filter out and may interfere with proper operation of sensitive systems (communication,radar or telemetry). International Rectifier provides synchronization of multiple AMR type converters to match switching frequency of the converter to the frequency of the system clock, thus eliminating this type of noise.MTBF vs Case Temperature for AMR2803R3SOutput Return-SenseAMR28XXS SeriesMechanical OutlinePin DesignationRadiation SpecificationInternational Rectifier currently does not have a DSCC certified Radiation Hardness Assurance Program.7AMR28XXS SeriesPart Numbering WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, Tel: (310) 252-7105IR SANTA CLARA: 2270 Martin Av., Santa Clara, California 95050, Tel: (408) 727-0500Visit us at for sales contact information .Data and specifications subject to change without notice. 09/2008Standard Microcircuit Drawing Equivalence Table AMR 28 05 S /EMModel 28 = 28VOutputS = Single D = Dual T = TripleOutput Voltage03R3 = 3.3V, 05 = 5V, 12 = 12V, 15 = 15VScreening Level(Please refer to Screening Table)No Suffix, CH, EMInput VoltageNotes:Best commercial practice.Device with ‘/CH’ suffix is a DSCC class H compliant without radiation performance. No suffix is a radiation rated device but not available as a DSCC qualified SMD per MIL-PRF-38534.International Rectifier currently does not have a DSCC certified Radiation Hardness Assurance Program.。