毛刺信号消除电路的研究与实现

毛刺的消除

毛刺

时序仿真输出波形

引入了D 引入了D触发器的长帧同步时钟的产生

module longframe2(clk,strb); parameter DELAY=8; input clk; output strb; reg[7:0] counter; reg temp,strb; always@(posedge clk) begin if(counter==255) counter<=0; else counter<=counter+1; end always@(posedge clk) begin strb<=temp;end //引入触发器 //引入触发器 always@(counter) begin if(counter<=(DELAY-1)) temp<=1; else temp<=0; if(counter<=(DELAYend endmodule

消除毛刺后的时序仿真输出波形

延时方式去毛刺

延时方式去毛刺

逻辑方式去毛刺

逻辑方式去毛刺

定时方式去毛刺

定时方式去毛刺

跨时钟域设计

module metastable(clka,clkb,ina,outb); input clka,clkb,ina; output outb; reg outb,outa; always @(posedge clka) outa=ina; always @(posedge clkb) outb=outa; outa outb~reg0 endmodule

FPGA设计中毛刺的消除 FPGA设计中毛刺的消除

信号在FPGA器件内部通过连线和逻辑门时, 信号在FPGA器件内部通过连线和逻辑门时, 都有一定的延时。因此多路信号的电平值发生 变化时,在信号变化的瞬间,组合逻辑的输出 有先后顺序,往往会出现一些不正确的“毛刺” 有先后顺序,往往会出现一些不正确的“毛刺” (Glitch),称为“冒险”(Hazard)现象。 Glitch),称为“冒险” Hazard)现象。 这些毛刺在电路板的设计中由于PCB走线时, 这些毛刺在电路板的设计中由于PCB走线时, 存在分布电感和分布电容,所以许多毛刺能够 被自然滤除,而在PLD内部没有分布电感和电 被自然滤除,而在PLD内部没有分布电感和电 容,这些毛刺将被完整地保留并向下一级传递, 所以在FPGA设计中,如何消除毛刺就变得很 所以在FPGA设计中,如何消除毛刺就变得很 重要。

电路中如何消除方波跳变时产生的尖刺

电路中如何消除方波跳变时产生的尖刺?解释一:在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。

产生毛刺叫冒险。

如果布尔式中有相反的信号则可能产生竞争和冒险现象。

解决方法:一是添加布尔式的(冗余)消去项,但是不能避免功能冒险,二是在芯片外部加电容。

三是增加选通电路。

在组合逻辑中,由于多少输入信号变化先后不同、信号传输的路径不同,或是各种器件延迟时间不同(这种现象称为竞争)都有可能造成输出波形产生不应有的尖脉冲(俗称毛刺),这种现象成为冒险。

解释二:竞争与冒险是数字电路中存在的一种现象。

由于元器件质量和设备工艺已达到相当高的水平,因而数字电路的故障往往是竞争与冒险引起的,所以要研究它们。

在一个复杂的数字电路的设计阶段,就完全预料电路中的竞争与冒险是困难的,有一些要通过实验来检查。

下面将说明组合数字电路中竞争与冒险的基本概念和确定消除它的一些基本方法。

竞争:在组合电路中,信号经由不同的途径达到某一会合点的时间有先有后,这种现象称为竞争。

冒险:由于竞争而引起电路输出发生瞬间错误现象称为冒险。

表现为输出端出现了原设计中没有的窄脉冲,常称其为毛刺。

竞争与冒险的关系:有竞争不一定会产生冒险,但有冒险就一定有竞争。

在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。

产生毛刺叫冒险。

如果布尔式中有相反的信号则可能产生竞争和冒险现象。

解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

当组合逻辑电路存在冒险现象时,可以采取修改逻辑设计,增加选通电路,增加输出滤波等多种方法来消除冒险现象。

当一个门的输入有两个或两个以上的变量发生改变时,由于这些变量是经过不同路径产生的,使得它们状态改变的时刻有先有后,这种时差引起的现象称为竞争(Race)。

数字电路毛刺消除问题

数字电路⽑刺消除问题参考博⽂:和1. ⽑刺的产⽣原因:冒险和竞争使⽤分⽴元件设计电路时,由于PCB在⾛线时,存在分布电容和电容,所以在⼏ns内⽑刺被⾃然滤除,⽽在PLD内部没有分布电感和电容,所以在PLD/FPGA设计中,竞争和冒险问题⽐较重要。

信号在FPGA器件内部通过连线和逻辑单元时,都有⼀定的延时。

延时的⼤⼩与连线的长短和逻辑单元的数⽬有关,同时还受器件的制造⼯艺、⼯作电压、温度等条件的影响。

信号的⾼低电平转换也需要⼀定的过渡时间。

由于存在这两⽅⾯因素,多路信号的电平值发⽣变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现⼀些不正确的尖峰信号,这些尖峰信号称为"⽑刺"。

如果⼀个组合逻辑电路中有"⽑刺"出现,就说明该电路存在"冒险"。

可以概括的讲,只要输⼊信号同时变化,(经过内部⾛线)组合逻辑必将产⽣⽑刺。

将它们的输出直接连接到时钟输⼊端、清零或置位端⼝的设计⽅法是错误的,这可能会导致严重的后果。

所以我们必须检查设计中所有时钟、清零和置位等对⽑刺敏感的输⼊端⼝,确保输⼊不会含有任何⽑刺。

存在逻辑冒险的电路:仿真波形:2. 判断是否存在冒险关于冒险的知识,数电书上有详细的说明,当时没有认真学,只了解个⼤概,现在⼜要重新看...还记得当年画卡诺图时的痛苦冒险按照产⽣⽅式分为静态冒险 & 动态冒险两⼤类。

静态冒险指输⼊有变化,⽽输出不应该变化时产⽣的窄脉冲;动态冒险指输⼊变化时,输出也应该变化时产⽣的冒险。

动态冒险是由静态冒险引起的,所以,存在动态冒险的电路也存在静态冒险。

静态冒险根据产⽣条件不同,分为功能冒险和逻辑冒险两种。

当有两个或两个以上的输⼊信号同时变化时,在输出端有⽑刺,称为功能冒险;如果只有⼀个输⼊变量变化时,出现的冒险称为逻辑冒险。

因为动态冒险是由静态冒险引起的,所以消除了静态冒险,也就消除了动态冒险。

毛刺产生和消除

数字逻辑基础LOGO毛刺产生及消除传播延迟不仅限制电路工作的速度,它们也会在输出端引起不期望的多余跳变。

这些多余的跳变,称为“毛刺”。

⏹这将导致当其中一个信号发生改变时,给信号提供了两条或更多的流过电路的路径,并且其中一条路径的延迟时间比其他路径长。

⏹当信号路径在输出门重组时,这个在一条路径上增加的时间延迟会产生毛刺。

毛刺产生及消除当一个输入信号通过两条路径或多条路径驱动的一个输出,其中一条路径有反相器而另外一条没有时,通常会出现非对称的延迟。

包含反相器会产生毛刺的组合逻辑结构毛刺产生及消除毛刺生成逻辑结构和时序分析毛刺产生及消除当一个输入用于两个积项(或者和之积方程式的两个和项),以及反相器在其中一项中有而另一项中没有时,将会产生毛刺。

在该卡诺图中,两个圆圈决定了最小逻辑表达式。

B·C 独立于A 。

当B 变化时,两种不同的积项必须在输出时重组以保持输出为高,这就是引起毛刺的原因。

产生毛刺的电路毛刺该设计保存在\eda_verilog\glitch 目录下毛刺产生及消除电路产生毛刺可以通过它原理图、卡诺图或者是逻辑等式验证。

⏹在原理图中,输入后面有多条到达输出的路径,并且其中一条有反相器而其他路径没有就会产生毛刺。

⏹在卡诺图中,假如画的圈是相邻的但不重叠,那么那些没有被圈圈住的相邻项将有可能产生短时脉冲干扰。

毛刺产生及消除可能的毛刺没有毛刺没有毛刺毛刺产生及消除对于毛刺的产生,一个逻辑电路必须对驱动所有输入到适当的水平的耦合变量“很敏感”,这样就只有耦合变量可以影响输出。

在一个SOP 电路中,这意味着除了耦合输入外的所有的输入必须被驱动到“1”,这样它们对第一级与门的输出就不会产生影响。

这种情况为逻辑电路消除毛刺提供了一个直观的方法:将所有多余的输入信号组合到一个新的第一级的逻辑输入(例如,SOP 电路的与门),并将这个新增加的门添加到电路中。

毛刺产生及消除逻辑表达式:耦合项是A ,多余项可以组合成项的形式,将这项添加到电路组成方程式。

电路中如何消除方波跳变时产生的尖刺.doc

电路中如何消除方波跳变时产生的尖刺?解释一:在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。

产生毛刺叫冒险。

如果布尔式中有相反的信号则可能产生竞争和冒险现象。

解决方法:一是添加布尔式的(冗余)消去项,但是不能避免功能冒险,二是在芯片外部加电容。

三是增加选通电路。

在组合逻辑中,由于多少输入信号变化先后不同、信号传输的路径不同,或是各种器件延迟时间不同(这种现象称为竞争)都有可能造成输出波形产生不应有的尖脉冲(俗称毛刺),这种现象成为冒险。

解释二:竞争与冒险是数字电路中存在的一种现象。

由于元器件质量和设备工艺已达到相当高的水平,因而数字电路的故障往往是竞争与冒险引起的,所以要研究它们。

在一个复杂的数字电路的设计阶段,就完全预料电路中的竞争与冒险是困难的,有一些要通过实验来检查。

下面将说明组合数字电路中竞争与冒险的基本概念和确定消除它的一些基本方法。

竞争:在组合电路中,信号经由不同的途径达到某一会合点的时间有先有后,这种现象称为竞争。

冒险:由于竞争而引起电路输出发生瞬间错误现象称为冒险。

表现为输出端出现了原设计中没有的窄脉冲,常称其为毛刺。

竞争与冒险的关系:有竞争不一定会产生冒险,但有冒险就一定有竞争。

在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。

产生毛刺叫冒险。

如果布尔式中有相反的信号则可能产生竞争和冒险现象。

解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

当组合逻辑电路存在冒险现象时,可以采取修改逻辑设计,增加选通电路,增加输出滤波等多种方法来消除冒险现象。

当一个门的输入有两个或两个以上的变量发生改变时,由于这些变量是经过不同路径产生的,使得它们状态改变的时刻有先有后,这种时差引起的现象称为竞争(Race)。

竞争的结果若导致冒险或险象(Hazard)发生(例如毛刺),并造成错误的后果,那么就称这种竞争为临界竞争。

电路设计中的毛刺问题的研究

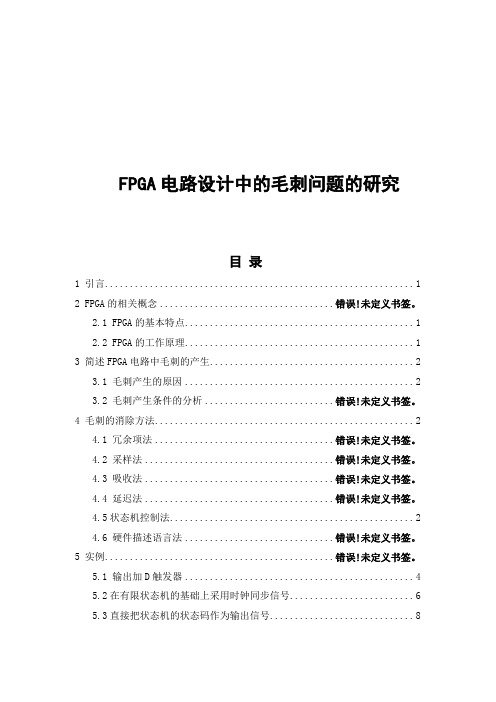

FPGA电路设计中的毛刺问题的研究目录1 引言 (1)2 FPGA的相关概念.................................. 错误!未定义书签。

2.1 FPGA的基本特点 (1)2.2 FPGA的工作原理 (1)3 简述FPGA电路中毛刺的产生 (2)3.1 毛刺产生的原因 (2)3.2 毛刺产生条件的分析......................... 错误!未定义书签。

4 毛刺的消除方法 (2)4.1 冗余项法................................... 错误!未定义书签。

4.2 采样法..................................... 错误!未定义书签。

4.3 吸收法..................................... 错误!未定义书签。

4.4 延迟法..................................... 错误!未定义书签。

4.5状态机控制法 (2)4.6 硬件描述语言法............................. 错误!未定义书签。

5 实例............................................. 错误!未定义书签。

5.1 输出加D触发器 (4)5.2在有限状态机的基础上采用时钟同步信号 (6)5.3直接把状态机的状态码作为输出信号 (8)6 结语 (10)参考文献 (11)致谢 (12)FPGA电路设计中的毛刺问题的研究摘要:目前,FPGA器件已经越来越广泛地应用在数字电路设计等领域,但它的毛刺问题却成为一个影响其可靠性和精确性的重要因素。

本文探讨了毛刺产生的原因及产生的条件,以计数器和乘法器为例对解决方案进行了深入具体地分析,总结了多种不同的解决方法,并且通过仿真说明这几种方法能够有效地消除或在一定程度上减少数字电路设计中出现的毛刺。

消除毛刺的放法【转】

出端 Q=D,当输入的信号有毛刺时,只要不发生在时钟的上升沿时刻,输出就不会有毛

刺。这种方法类似于将异步电路转化为同步电路,实现简单,但同样会涉及到时序问题。

(3)吸收法

由于产生的毛刺实际上是高频窄脉冲,故增加输出滤波,在输出端接上小电容C就

消除毛刺信号的影响,常用的采样方法有两种

:一种使用一定宽度的高电平脉冲与输

出相与,从而避开了毛刺信号,取得输出信号的电平值。这种方法必须保证采样信号在

合适的时间产生,并且只适用于对输出信号时序和脉冲宽度要求不严的情况。另一种更常见的方法叫锁存法,是利用 D 触发器的输入端 D 对毛刺信号不敏感的特点,在输出

新设计延迟线,因而这种方法也是有局限性的。而且采用延迟线的方法产生延迟会由于

环境温度的变化而使系统可靠性变差。

(5)硬件描述语言法

这种方法是从硬件描述语言入手,找出毛刺产生的根本原因,改变语言设计,产生

满足要求的功能模块,来代替原来的逻辑功能块。

以上为五种常用的毛刺消除方法。

诺圆相切,其对应的电路就可能产生险象。因此,修改卡诺图,在卡诺图的两圆相切处

增加一个圆,以增加多余项来消除逻辑冒险。但该法对于计数器型产生的毛刺是无于冒险多出现在信号发生电平跳变的时刻,即在输出信号的建立时间内会产生毛

刺,而在保持时间内不会出现,因此,在输出信号的保持时间内对其进行采样,就可以

消除毛刺的方法

知道了毛刺产生的条件,就可以通过调整设计方案,破坏其条件来阻止毛刺的发生。

还可以对电路进行改进,以消除毛刺对系统的影响

。下面对各种方法做分别介绍:

FPGA设计中毛刺信号解析

FPGA设计中毛刺信号解析

在FPGA(Field-Programmable Gate Array)设计中,毛刺信号是一种不稳定的、短暂的、高频的信号噪声。

这种信号可能是由于电路中的突变或者切换引起的,通常会引起系统性能下降或者功能异常。

因此,解析和处理毛刺信号对于FPGA设计来说非常重要。

下面将介绍如何解析毛刺信号以及常见的解决方法。

一种常见的解决方法是通过信号滤波来降低毛刺的影响。

滤波可以通过数字滤波器实现,常见的滤波器包括低通滤波器、中通滤波器和带通滤波器。

根据毛刺信号的特征,选择适合的滤波器参数,可以有效地去除毛刺信号。

另一种方法是通过信号的去抖动处理来消除毛刺影响。

去抖动是一种通过延迟信号的上升或下降边沿的方法,以消除信号中的瞬时毛刺。

通过添加适当的延迟,我们可以使得毛刺信号在系统中不被处理,从而减少对系统性能的影响。

此外,我们还可以通过时序优化来减少毛刺问题。

时序优化包括调整时钟频率、优化时序路径和消除时序冲突等。

通过优化时序,我们可以使得信号在FPGA中的传输更加平稳和稳定,从而减少毛刺信号的出现。

在一些特殊情况下,信号毛刺可能需要通过硬件逻辑设计来解决。

例如,我们可以使用状态机、锁存器或者计数器等特殊电路来对毛刺信号进行抑制和消除。

综上所述,FPGA设计中毛刺信号解析是一个复杂的问题,需要综合考虑信号源、滤波、去抖动、时序优化和硬件逻辑等方面。

通过合理选择

解决方案,并借助模拟和数字混合仿真工具的帮助,我们可以有效地解析和处理毛刺信号,提高系统性能和功能稳定性。

FPGA消除毛刺的方法

FPGA消除毛刺的方法1. 控制时钟边沿:毛刺往往是由于时钟边沿的不稳定引起的。

为了减少毛刺的发生,可以通过合理控制时钟边沿的稳定性来消除毛刺。

一种常见的方法是使用FPGA的Phase-Locked Loop(PLL)电路来锁定外部输入的时钟信号,并生成一个稳定的内部时钟信号。

通过合理设置PLL的参数,可以消除时钟边沿的抖动,进而减少毛刺现象的发生。

2.去除信号干扰:毛刺往往是由于信号干扰引起的。

为了消除毛刺,可以采取一些方法来去除信号干扰。

首先,可以通过布线的方式将敏感信号和噪声源进行物理隔离,减少信号之间的干扰。

其次,在设计时可以采用差分信号传输技术,利用差分传输的优势来抵消一部分共模干扰,减小信号受到噪声的影响。

还可以利用滤波器来消除高频噪声干扰,提高信号质量。

3.适当增加延时:毛刺往往是由于信号变化过快引起的。

为了减少毛刺的发生,可以适当增加信号的延时。

通过增加延时,可以使信号的变化更加平滑,避免毛刺的产生。

可以使用FPGA内部的延时线来实现增加延时的功能。

在选择延时线时,要根据信号的频率和变化情况来确定延时的大小,以达到最佳的消除毛刺效果。

4.信号滤波:毛刺往往是由于信号不稳定引起的。

为了减少毛刺的发生,可以通过信号滤波来稳定信号。

可以根据信号的特点选择合适的滤波器类型和参数,对信号进行滤波处理。

常用的滤波器包括低通滤波器、带通滤波器和带阻滤波器等。

通过对输入信号进行滤波处理,可以减少信号快速变化引起的毛刺现象。

5.引入缓冲器:毛刺往往是由于信号传输路径中的阻抗不匹配引起的。

为了消除毛刺,可以在信号传输路径中引入合适的缓冲器。

缓冲器可以提供合适的驱动能力,消除驱动能力不足或者驱动能力过强引起的毛刺现象。

在选择缓冲器时,要考虑信号的特点和传输路径的阻抗匹配情况,以达到最佳的消除毛刺效果。

总结起来,FPGA消除毛刺的方法包括控制时钟边沿、去除信号干扰、适当增加延时、信号滤波以及引入缓冲器等。

毛刺的研究现状及去除技术

製造科技導論期中報告製造工程-毛刺的研究現狀及去除技術班級:四技電子四甲學號:99081122姓名:李彤目錄摘要 (2)一、金屬切削毛刺的研究 (3)1.車削加工毛刺 (3)2.鑽削加工毛刺 (3)3.銑削加工毛刺 (4)二、去毛刺技術 (5)1.滾筒研磨去毛刺 (5)2.電化學去毛刺 (6)3.熱能去毛刺 (6)4.磁力研磨去毛刺 (6)5.擠壓研磨去毛刺 (7)6.高科技去毛刺 (7)摘要分析車削、鑽削、銑削毛刺研究的分類及其主要的影響因素。

針對毛刺的危害,介紹幾種生產實際中常用的去毛刺方法。

關鍵字:金屬切削車削毛刺鑽削毛刺銑削毛刺去毛刺技術AbstractDiscusses the studying status,the classify and the main influencing factors of turning,drilling and milling burr research by the numbers.Aiming at burr imperil,it introduce several deburring methods in common use and expatiates that it is necessary to increase burr metrical technology and extend burr researchful fieldsKey words:Metal cutting Turning burr Drilling burr Milling burr Deburring technology一、金屬切削毛刺的研究1.車削加工毛刺車削加工毛刺生成機理的研究比較多。

車削加工中產生的毛刺主要是進給方向毛刺,有兩種具體形態,一種被稱為I型毛刺,這種毛刺的高度隨切削深度的增加而增大,並且毛刺高度與毛刺根部厚度的比值比較大。

由於I型毛刺直接影響了工件的加工精度,因此必須減小或抑制。

电压毛刺无损吸收电路

电压毛刺无损吸收电路电压毛刺无损吸收电路电压毛刺无损吸收电路电压毛刺是高频变换器研制和生产过程中的棘手问题,处理得不好会带来许多的问题,诸如:功率管的耐压必须提高,而且耐压越高,其通态电压越大,功耗越大,这不仅使产品效率降低,而且使电路可靠性降低;另外,高频杂音的增加,对环境造成污染;为了达到指标,必须进一步采取措施,结果不仅使产品体积增大,而且使成本增加。

解决办法通常是:增加主变压器中各线圈的耦合程度,以减少漏感(例如双线并绕等);选用结电容小,恢复时间短的优质开关管;增加吸收电路,最常用的是RC吸收电路,这种电路虽结构简单,但是有损的,而且变换器功率越大,需要的C越大,使R上的功耗也越大,导致R 的体积很大,其结果是产品中常常装有体积大的电阻电容,使运行环境恶化,整机效率降低。

显然这些解决办法不理想,本文将介绍两种无损电压毛刺回收电路。

1 常规RC吸收电路的功耗RC吸收电路如图1所示,设主变压器一次侧为半桥或全桥电路,二次侧为极性交变的脉宽调制方波,并且带有毛刺,如图2所示。

这样在RC串联电路中就有充放电过程,在R上就会有功耗。

为分析方便,先不考虑电压毛刺,uAC的电压波形为极性交变的方波。

图1 高频整流的RC吸收电路图2 高频调制方波设某一时刻t=0时uAC的极性为上正下负,大小为Eo,C上的电压为Eo,极性上负下正,等效电路如图3所示。

由电路方程可得Eo=idt-Eo+iR图3 等效电路由初始条件t=0时,i=2Eo/R,解得i=2Eoe -t/RC/R。

电阻R上的消耗功率WR=i2Rdt=2CEo2即C上的电压从-Eo→+Eo变化过程中,R上的功耗为2CEo2。

充电过程结束最终C上的电压为Eo,极性反转。

一个周期内uAC翻转两次,R上的总功耗为4CEo2。

例如:一个输出为48V的整流器,Eo通常约为150V,频率f取50kHz,电容C取1nF,则R上的功耗WR=4CEo2×f=5W。

高效能FPGA毛刺PUF设计与实现

高效能FPGA毛刺PUF设计与实现毛刺PUF(Physical Unclonable Function)可以利用随机性噪声提供一种额外的安全措施,用于硬件和软件的安全认证。

它是一种数字电路,可以利用毛刺效应(glitches)产生的噪声来生成一系列的随机比特串,来防止攻击者通过复制芯片或读取芯片状态来获取关键信息。

在FPGA(Field Programmable Gate Array)领域,毛刺PUF通常是通过设计和实施算法来利用FPGA的硬件特性实现的。

本文将介绍如何设计和实现一种高效能的毛刺PUF,并将介绍相关的设计和实施步骤。

一、毛刺PUF的设计思路在设计毛刺PUF时,需要将芯片的不同特性和毛刺效应考虑在内。

毛刺效应是由FPGA中的动态电流和电磁干扰引起的,这些电流和电磁干扰有时会导致芯片的输出值产生变化。

因此,如果将芯片的输入值稍稍改变一点,可能会导致芯片的输出值发生相对于输入的不可预测的变化,从而为PUF生成随机的比特串提供可能。

在毛刺PUF的设计中,需要考虑以下几个方面:(1)选择适当的FPGA芯片。

不同的FPGA芯片应该有不同的毛刺效应,因此需要根据所需的毛刺PUF规格选择适当的FPGA芯片。

(2)确定生成随机比特串的算法。

需要确定一个适当的算法,能够通过观察芯片在不同输入下的输出情况来生成一系列的随机比特串。

(3)实现算法。

需要通过编写代码和利用FPGA自适应电路来实现算法。

(4)性能评估。

需要对设计的毛刺PUF进行性能测试和评估,以确保其满足安全认证要求。

二、毛刺PUF的实现步骤2.1 选择合适的FPGA芯片在选择FPGA芯片时,需要考虑毛刺效应的强度和可观测性。

若一种芯片的毛刺效应不是很强,可能不足以产生随机信号,同理,如果输出值变化的规律性过强,不足以保证PUF的安全性,会降低PUF的可靠性,因此需要寻找尽可能具有随机性的毛刺效应强的FPGA,以提高毛刺PUF的可靠性和安全性。

激光去毛刺电子电路板工艺优化研究

激光去毛刺电子电路板工艺优化研究随着电子设备的广泛应用,电路板作为重要的电子组装部件,在生产过程中也逐渐受到了越来越多的关注。

在电路板制作过程中,由于连接电路的板子表面可能会有一些毛刺、划痕或残渣,以致于无法实现电路的正常运行,或者导致电路设备运行不稳定,从而影响电子设备的正常工作。

因此,激光去毛刺技术的引入和研究,对于优化电子电路板的生产质量,提高电子设备的工作性能,具有十分重要的现实意义。

激光去毛刺技术,是一种将强光直接照射到被处理物体表面,将物体表面残渣烧掉的技术。

在工业生产领域,激光去毛刺技术主要被应用在电子电路板、模具、精密机械等领域。

而对于电子电路板来说,使用激光去毛刺技术可以显著地提高电路板表面的平整度和光泽度,从而降低电路板表面的粗糙度,提高电路板的生产精度,同时可以保证电路板的成品率和压力强度,避免电路板因为残留毛刺导致电路断路的情况发生。

虽然激光去毛刺技术内在的优势已经得到了广泛的认可,但其实激光去毛刺技术在生产过程中也存在一些问题和挑战。

例如,激光去毛刺技术如果不慎使用不当,会导致电路板表面被烧毁,而这对于电子电路板的生产精度和产品质量都会造成负面影响。

此外,激光去毛刺技术需要控制的参数较多,如激光功率、扫描速度、光斑直径等,因此需要在实践中不断积累经验并进行不断优化。

对于这些问题,一些生产厂商和学者们进行了深入研究,提出了一些优化措施,以改善激光去毛刺的工艺过程。

其中最重要的措施是优化激光去毛刺参数的选择和调整。

具体来说,需要根据不同的电路板材料,不同的毛刺大小和位置,以及不同的扫描速度和激光功率,选择不同的激光参数进行调整。

这一步需要通过多次试验和实践,不断积累经验,以找到最佳的激光参数组合来完成电路板的去毛刺工作。

除了激光参数的优化外,生产厂商还需要在实际操作中加强对激光处理过程的控制。

在加工电子电路板时,需要保证激光束的质量和稳定性,以确保激光束与电路板的接触质量,并在加工过程中监控扫描速度和激光功率,根据实际情况进行调整和控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第32卷第4期集宁师专学报Vol.32,No.4

2010年12月Journal of JiningTeachers College Dec.2010

收稿日期:2010-06-13

作者简介:聂阳,男,汉族,内蒙古乌兰察布市人,硕士,研究方向:系统级芯片设计、D SP 电路设计。

基金资助:2010年度内蒙古自治区高等学校科学研究项目:《基于FPG A 的数字电路教学方法变革与研究思路》(编号:N )

毛刺信号消除电路的研究与实现

聂阳,赵鹏宇,荆丽丽

(集宁师范学院物理系,内蒙古乌兰察布012000)

摘要:本文分析了毛刺信号的消除电路,以电路实例给出毛刺信号消除的三种电路解决方案,并利用FPG A 和ED A 仿真软件给出了仿真结果,具有一定的工程指导意义。

关键词:毛刺信号;延时电路;定时电路中图分类号:TN 492文献标识码:A 文章编号:1009-7171(2010)04-0011-05

1引言

信号在数字系统内部传输时,都有一定的延时。

延时的大小不仅与连线的长短和逻辑单元的数目有关,还受器件的制造工艺、工作电压、温度等条件的影响;同时信号的高低电平转换也需要一定的过渡时间[]1。

当多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为毛刺。

1.1电路理论分析

根据理论分析,若实现如下电路y=a

b +c

d ,其电路原理图和仿真图如图1、2所

示,从图2中可以看到4

个信号都发生变化时,电路的输出产生毛刺。

图1

电路原理图

图2电路仿真图

J 10212

12集宁师专学报第32卷

2毛刺信号消除电路解决方案

2.1消除毛刺信号—增加冗余项

函数式和真值表所描述的是静态逻辑,而竞争则是从一种稳态到另一种稳态的过程。

因此竞争是动态过程,它发生在输入变量变化时。

此时,若在两个卡诺图圆圈相切处增加一个冗余的卡诺图圈,即卡诺图的两圆相切处增加一个圆,可以消除逻辑冒险。

但该法对于计数器型产生的毛刺是无法消除的。

0001111000001001001011111110

01

表1卡诺图

增加冗余项后y=a

b +c

d +a

b

c

d 的电路原理图和仿真图如图3、4

所示。

图3

添加冗余项后电路原理图

图添加冗余项电路仿真图

其优点是可以消除毛刺信号。

但其缺点为:()增加冗余项电路,资源消耗多。

()

a b

cd 412

第4期

聂阳,赵鹏宇,荆丽丽:毛刺信号消除电路的研究与实现13通用程度差,只适合逻辑比较简单的电路,如计数器型电路毛刺无法解决,不适合复杂的逻辑系统。

2.2消除毛刺信号—延时电路[]2

延时电路就是使用触发器、寄存器等时序元件或对输入、输出或电路通道上的信号进行适当的延时或延时采样,使处理过的信号在输出后能避开毛刺。

如图5、6所示。

图5添加延时电路原理图

图6添加延时电路仿真图

延时量由延时时钟c l k决定,如果cl k的周期小于毛刺信号的宽度,毛刺信号仍然可以被采到,如图7所示。

7cl k

图添加延时电路的周期小于毛刺信号宽度仿真图

14集宁师专学报第32卷

当延时电路c l k 的周期小于毛刺信号宽度时,采用增加延时电路和利用多个延时信号相与的结果做为最终的输出结果。

如图8所示,增加两级延时后,经过与门得输出信号十分干净,已滤除了毛刺信号。

图8增加两级延时后电路原理图

图9增加两级延时后仿真图

此方法的优点是可以滤除毛刺信号,对于小于时钟周期的毛刺信号也可以滤除。

其缺点为:(1)输出信号变窄;(2)需增加延时电路数量,至少3级;(3)时钟频率要求较高。

2.3消除毛刺信号—定时电路

[]3[]

4利用两个计数器对输入信号的高电平和低电平的持续时间(脉宽)进行计数,只有当高电平的计数时间大于某值,则判为遇到正常信号,输出为逻辑“1”,若低电平的计数器大于某值,则输出逻辑“0”。

具体代码如下:

m odul e m aoci (cl k,di n,dout );i nput cl k,di n;//工作时钟信号和输入信号out put dout ;r eg dout ;

[3]_,_;高电平和低电平计数器y @()对低电平脉宽计数

r eg :0h l evel l l evel //a l w a s posedge c l k //begi n

第4期

聂阳,赵鹏宇,荆丽丽:毛刺信号消除电路的研究与实现15

i f(!di n)

l_l e vel<=l_l evel+1;

el se

l_l e vel<=4'b000;

e nd

a l w ays@(posedge cl k)//对高电平脉宽计数

begi n

i f(di n)

h_l e vel<=h_l evel+1;

el se

h_l e vel<=4'b000;

e nd

a l w ays@(posedge cl k)

begi n

i f(h_l eve l>4'b1100)//对高电平脉宽计数一旦大于12,输出1

dout<=1'b1;

el se i f(l_l e vel>4'b0111)//对低电平脉宽计数一旦大于7,输出0

dout<=1'b0;

e nd

e ndm odul e

3、总结语

数字系统设计过程中,毛刺信号的消除是工程师必须面对的棘手问题。

若本级电路的毛刺信号没有得到消除,毛刺信号可能会传输到后几级电路从而导致整个系统不稳定。

本文通过具体实例和方法设计了消除毛刺信号电路。

作为启迪,可据此提出其他的更好的方法。

参考文献:

[1]阎石.《数字电子技术基础》[M].第五版.北京:高等教育出版社,2005:200-203.

[2]楼观涛.《FPG A设计中毛刺信号的产生及消除》[J].电子世界,2004年第7期:32-33.

[3]聂名义.《一种滤除低速时钟信号毛刺干扰的方法》:中国,200410080476[P].2006

[4]潘松.《E D A技术与V eri l og H D L》[M].北京:清华大学出版社,2009:302-305.

The Research and implementation of glitch signal

elimination circuit

Nie yang,Zhao peng yu,Jing li li

(Physics Department of Jining Teachers College,Wulanchabu Inner Mongolia012000) Abstract:This paper analyzes the glitch signal elimination circuit.Circuit example is given to the three circuits to eliminate glitch signal solution,And use FPGA and EDA simulation software simulation results, which has engineering significance.

e words:glitch signal dela circuit timing circuits

K y;y;。