TI系列DSP的I 2C模块配置与应用

I_2C总线技术在DSP系统中的实现

收稿日期:2007-10-30作者简介:柯艳明(1968— ),男,湖北大冶人,讲师,硕士。

文章编号:1008-8245(2008)01-0007-03I 2C 总线技术在DSP 系统中的实现柯艳明(黄石理工学院电气与电子信息工程学院,湖北黄石435003)摘 要:许多嵌入式系统处理器由于不带有I 2C 总线接口而限制了I 2C 总线接口器件在其上的应用。

介绍了I 2C 总线的特点和时序,并以串行E 2PROM 为例,给出了在T MS320F240X DSP 系统中模拟实现I 2C 总线的方法。

实践证明,该方法简单、可靠,对于构建实际的DSP 应用系统来说具有现实的参考价值。

关键词:I 2C 总线;DSP;E 2PROM 中图分类号:TP336 文献标识码:AThe I mple ment ati on of I 2C Bus Technology i n DSP Syste mKE Yan m ing(School of Electrical and Electronic Infor mation Engineering,Huangshi Institute of Technology,Huangshi Hubei 435003)Abstract:Many e mbedded syste m p r ocess or can not use I 2C bus devices because of its lack of I 2C bus interface .This paper intr oduces the character and ti m e sequence of I 2C bus and taking serial E 2PROM as exa mp le and p resents the si m ulating app licati on method of I 2C bus in DSP syste m.The p ractice p r oves that this method is si m p le and reliable and gives p ractical reference value for actual constructi on of DSP app licati on syste m.Key words:I 2C bus;DSP;E 2PROM I 2C (I nter I C BUS )总线是PH I L I PS 公司推出的一种新型串行总线,它可使芯片之间通过简单的双线进行通讯。

TI的DSP开发环境CCS安装配置说明文档

本说明文档包含:1. CCS3.3开发环境与附加驱动的安装顺序2. CCS3.3硬件仿真模式的启动3. 硬件仿真模式启动后,开发环境的配置4. 硬件调试连接顺序5. 硬件调试断开顺序6. 关于gel 文件和cmd 文件的附加说明重要提示:在使用DSP2808最小系统板进行硬件仿真实验时,需时常注意电源芯片和DSP 芯片的温度,尤其是在上电异常或电路板与上位PC 机连接异常时,如果电源芯片或DSP 芯片短时间内突然过热,则代表电路板出现异常,不可再强行通电使用。

CCS3.3开发环境与附加驱动的安装顺序:第一步:安装CCS3.3编译开发环境,选择典型安装选项。

安装完成后,桌面出现两个图标第二步:安装USB 驱动,双击CDM20802_Setup.exe第三步:安装XDS100驱动,双击XDS100_v1_1_RTM.exe第四步:安装2808例子程序,双击TMS320F2808全套例程.rar至此,CCS3.3开发环境与附加驱动的安装完成。

CCS3.3硬件仿真模式的启动:第一步:双击桌面上的Setup CCStudio v3.3图标第二步:在开启的界面中,选择Platform 中的下拉菜单中选择xds100usb emulator第三步:选择F2808 XDS100 USB Emulator,点击Add第四步:此时已将2808添加至左侧的My System中,点击左下角的Save&Quit来启动CCS3.3第五步:在出现的弹出窗口中选择“是”至此,CCS3.3以完成初次启动的配置并正常启动附加说明,完成初次启动配置后,以后再使用时,不需要再点击Setup CCStudio v3.3来进行配置了,只需要点击,来按照原有配置启动即可。

硬件仿真模式启动后,开发环境的配置:第一步:点击Project->new,新建一个空的工程第二步:在左侧的工程管理栏中新建好的工程中,单击右键,选择Build Options第三步:在Advanced 标签页中,在Unified Memory Model(-ml前打钩第四步:在 Preprocessor 标签页中,将C:\tidcs\c28\DSP280x\v160\DSP280x_headers\include 输入至 Include Search Path 中,输入分号(注意此时应保持输入法为英文输入法),再将C:\tidcs\c28\DSP280x\v160\DSP280x_common\include 输入至 Include Search Path 中,以完成 CCS3.3 的编译器对头文件的查找路径的设置。

ti c2000程序工程结构

TI C2000程序工程结构一、简介TI C2000系列是德州仪器公司的数字信号处理器(DSP)系列芯片,主要应用于实时控制和数字信号处理。

在进行C2000程序开发时,良好的程序工程结构是非常重要的,可以提高程序的可维护性和可移植性,同时也有利于团队协作开发。

本文将介绍TI C2000程序工程结构的相关内容。

二、目录结构1. 根目录1.1 程序源码1.2 头文件1.3 驱动程序1.4 运行时库1.5 项目文件1.6 文档2. 程序源码目录2.1 应用程序2.2 算法2.3 通信协议2.4 控制器2.5 硬件接口2.6 中断服务程序2.7 实时操作系统(RTOS)应用3. 头文件目录3.1 DSP库3.2 驱动库3.3 运行时库3.4 外设库3.5 系统配置4. 驱动程序目录4.1 ADC4.2 PWM4.3 SCI4.4 SPI4.5 GPIO5. 运行时库目录5.1 DSP库5.2 系统库5.3 常用函数库6. 项目文件目录6.1 项目配置文件6.2 仿真器配置文件7. 文档目录7.1 产品规格书7.2 数据手册7.3 用户指南三、程序源码模块1. 应用程序模块1.1 m本人n.c1.2 task1.c1.3 task2.c2. 算法模块2.1 FFT.c2.2 PID.c2.3 DSPFilters.c3. 通信协议模块3.1 SPI.c3.2 CAN.c3.3 I2C.c4. 控制器模块4.1 PI_Controller.c4.2 StateMachine.c5. 硬件接口模块5.1 GPIO.c5.2 PWM.c5.3 ADC.c6. 中断服务程序模块6.1 ISR.c6.2 DMA_ISR.c7. 实时操作系统(RTOS)应用模块 7.1 os_task1.c7.2 os_task2.c四、头文件模块1. DSP库头文件1.1 dsplib.h1.2plex.h2. 驱动库头文件2.1 adc.h2.2 pwm.h2.3 sci.h3. 运行时库头文件3.1 c2000_runtime.h3.2 syslib.h4. 外设库头文件4.1 dac.h4.2 spi.h4.3 can.h4.4 i2c.h5. 系统配置头文件5.1 system_config.h 5.2 device.h五、驱动程序模块1. ADC驱动程序1.1 adc.c1.2 adc.h2. PWM驱动程序2.1 pwm.c2.2 pwm.h3. SCI驱动程序3.1 sci.c3.2 sci.h4. SPI驱动程序4.1 spi.c4.2 spi.h5. GPIO驱动程序5.1 gpio.c5.2 gpio.h六、运行时库模块1. DSP库1.1 digitalsignalprocessing.lib1.2 dsplib.lib2. 系统库2.1 system.lib2.2 syslib.lib3. 常用函数库3.1 c2000_runtime.lib3.2mon.lib七、项目文件1. 项目配置文件1.1 project.cfg1.2 project.xml2. 仿真器配置文件2.1 emulator.cfg2.2 emulator.xml八、文档1. 产品规格书1.1 C2000系列技术手册1.2 C2000芯片规格书2. 数据手册2.1 C2000系列用户手册2.2 C2000系列软件手册3. 用户指南3.1 C2000系列开发指南3.2 C2000系列编程指南结论良好的程序工程结构是TI C2000程序开发过程中的重要组成部分。

TI公司 DSP驱动模式 划分层次

TI公司 DSP驱动模式划分层次引言TI(Texas Instruments)公司是全球领先的半导体解决方案供应商之一。

他们提供多种型号的数字信号处理器(DSP)芯片,用于应用于多个领域,如通信、音频、图像处理等。

为了更好地利用DSP芯片的性能和功能,TI公司采用了一种划分层次的DSP驱动模式。

本文将详细介绍TI公司DSP驱动模式的划分层次以及每个层次的功能。

划分层次TI公司将DSP驱动模式划分为以下四个层次:1.应用层2.驱动层3.中间层4.硬件层下面将详细介绍每个层次的功能以及相应的驱动模块。

1. 应用层应用层是DSP驱动模式的最高层,通过应用层可以与DSP 芯片进行交互并执行特定的功能。

应用层提供了各种API接口,可以方便地访问DSP的功能和资源。

应用层的主要功能包括:•初始化DSP芯片•加载运行DSP代码•设置DSP芯片的参数•发送和接收数据2. 驱动层驱动层是位于应用层和中间层之间的中间层。

它负责与底层硬件交互,驱动DSP芯片的各个功能模块。

驱动层的主要功能包括:•控制DSP芯片的电源管理•配置DSP芯片的时钟和中断•提供对DSP芯片寄存器的访问接口•控制DSP芯片的数据流和DMA传输3. 中间层中间层是位于驱动层和硬件层之间的层次。

它主要负责对DSP芯片进行抽象和封装,以提供更高层次的接口和功能。

中间层的主要功能包括:•提供对DSP芯片的基本操作函数,如数学运算、滤波等•实现DSP芯片的算法库,提供更高级别的功能•封装底层驱动模块,提供统一的接口给上层应用层4. 硬件层硬件层是DSP驱动模式的最底层,它直接与硬件设备进行交互。

硬件层的主要功能包括:•与DSP芯片进行物理连接•实现DSP芯片的底层寄存器读写操作•控制DSP芯片的外设(如ADC、DAC等)•处理DSP芯片的中断信号驱动模块示例以下是TI公司DSP驱动模式中常见的驱动模块示例:1.UART驱动模块:用于与DSP芯片进行串行通信,实现数据的发送和接收。

DSP(TMS320C6713)入门之旅五、I2C的理解和使用

一般DSP上面都集成了I2C模块,这样在连接外部器件时可以很方便的控制外部的器件。

I2C 基本上都是用于外部控制的,因为是是串行总线。

在我们的实验板上I2C总线连接到了两个从设备上面,一个是我们的eeprom,另一个是我们的音频芯片AIC23。

通过I2C协议我们写入和读取eeprom数据,控制AIC23的声音一些属性!简介一下I2C协议的规则:一. 技术性能:工作速率有100K和400K两种;支持多机通讯;支持多主控模块,但同一时刻只允许有一个主控;由数据线SDA和时钟SCL构成的串行总线;每个电路和模块都有唯一的地址;每个器件可以使用独立电源二. 基本工作原理:以启动信号START来掌管总线,以停止信号STOP来释放总线;每次通讯以START开始,以STOP结束;启动信号START后紧接着发送一个地址字节,其中7位为被控器件的地址码,一位为读/写控制位R/W,R/W位为0表示由主控向被控器件写数据,R/W为1表示由主控向被控器件读数据;当被控器件检测到收到的地址与自己的地址相同时,在第9个时钟期间反馈应答信号;每个数据字节在传送时都是高位(MSB)在前;写通讯过程:1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线;2. 发送一个地址字节(包括7位地址码和一位R/W);3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK);4. 主控收到ACK后开始发送第一个数据字节;5. 被控器收到数据字节后发送一个ACK表示继续传送数据,发送NACK表示传送数据结束;6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线;读通讯过程:1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线;2. 发送一个地址字节(包括7位地址码和一位R/W);3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK);4. 主控收到ACK后释放数据总线,开始接收第一个数据字节;5. 主控收到数据后发送ACK表示继续传送数据,发送NACK表示传送数据结束;6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线;DSP中IIC模块框图:1. 总线空闲状态SDA和SCL两条信号线都处于高电平,即总线上所有的器件都释放总线,两条信号线各自的上拉电阻把电平拉高;2. 启动信号START时钟信号SCL保持高电平,数据信号SDA的电平被拉低(即负跳变)。

I~2C总线存储器在DSP240平台上应用的软件设计

软件开发与设计

I 2 C总线存储器在 D S P 2 4 0平 台上应 用的软件 设计

曾佳 赞

( 南京机电液压工程研究 中心 , 南京 2 1 0 0 1 6 ) 摘 要 :对 I z c总线协议 进行 了解析 ,并 以 A T 2 4 C 2 5 6芯 片为例 ,设计 了 I 2 C总线存储 器在 D S P 2 4 0平台上 的读 写存

l I 2 C总线 协议

( 1 )I 2 C总线 只有两根信号线 ,一 根是数据线 S D A,另一

根是时钟线 S C L 。

到有 效地 S D A下 跳沿 ,在 S C L的 H有效后 ,S D A的 H 电平

至少保持 0 . 2 5 p . s( t S U。S A T启 动建立时间) ,其后转为 L电平

能确认从器件 的地址数 据接收成功 ,主器件 可以继续 进行片

2 I 2 C总 线的读 写 操作

2 . 1 片 选 地 址

内地 址的数据 发送 ,先 发片内地址 的高位字 节 ,再发 低位字 节 。地址发送 完成后 ,发送 需要存储 的数据 字节 。发 送过程

与片地址数据方式相同。

I 2 C总线数 据存 储器片选地址规则约定: 其 中高 5 位为 固定 设 置 ,所有种类 的 I 2 C总线 存储器通用 。A 0 , A1 为连接在 同一 总线 上的存储器片地址 。R / W 为读 写指令信号 ,1 :读存储器 内部数据 ;0 :向存储器 内部写数据 。

( 4 )起 始信号 :时钟线保 持高 电平期 间数据线 电平从 高

主器件启 动完成后 ,即开始按 字节位发 送片选 地址 ,先 高位后低位 。每位数据的有效数值必须在 S C L为 H稳定有效 ,

I 2C总线技术在DSP系统中的实现

p p ri t d c st e c aa tra d t e u n eo 2 u d t k n e a 2 ROM se a l d p e e t t e a e nr u e h h r ce n me s q e c f1 C b s a a i g s r lE o i n i P a x mp e a rs n s h n

IC(n rI U ) 线 是 P ILS公 司 推 出 It C B S 总 e H LP

有 IC 总 线 接 口 , 而 限 制 了 IC 总 线 接 口 器 件 从

的一 种新 型 串行 总线 , 可使 芯 片之 间通 过 简 单 它

的 双 线 进 行 通 讯 。 IC极 大 简 化 了应 用 系 统 的 硬

了 1C总 线的特点 和时序 , 以串行 E P O 2 并 2R M为 例, 给出 了在 T 3 0 2 0 S MS 2 F4 X D P系统 中模 拟实现 IC总线的 方法。实践证明 , 该方法 简单 、 可靠 , 于构建实 际的 D P应用系统来说具有现实 的参考价值 。 对 S

讯 、 电、 家 智能 仪器 仪表 等场合 。

D P1 即 数 字 信 号 处 理 器 , 当 今 I S[ J 是 T行 业 的

热 点技术 之 一 , 独 特 的硬 件 结 构 设 计 ( 其 哈佛 结

构 、 水 线 技 术 等 ) 多 种 寻 址 方 式 保 证 了 其 具 备 流 和

关键 词 :, 1 2 C总线 ;S ; 2R M D P EP O 中 图分类号 : P 3 T 36 文 献标识 码 : A

Th m p e e t to f I Bu c o o y i P y t m e I l m n a i n o 2C s Te hn l g n DS S se

I2C模块使用教程

前言 (4)第1章 I2C模块规格说明 (5)1.1 综述 (5)1.2 特性 (5)1.3 模块架构 (7)1.4 配套资料说明 (7)1.5 模块原理图 (8)第2章 Arduino 基础 (9)2.1 Arduino硬件 (9)2.2 Arduino软件 (10)2.3 示例程序:LED控制 (12)第3章实时时钟 (17)3.1 DS1307介绍 (17)3.2 接线图 (17)3.3 DS1307的使用 (18)第4章外部存储 (23)4.1 AT24C32介绍 (23)4.2 接线图 (23)4.3 AT24C32的使用 (23)第5章温度侦测 (28)5.1 LM75介绍 (28)5.2 接线图 (28)5.3 LM75的使用 (29)结语 (33)为什么叫I2C模块?和一元硬币差不多大小的一块PCB上放了三个芯片,分管三个功能:时间计算、温度侦测、数据存储。

这三个芯片都是通过I2C总线通信的。

我们知道,I2C理论上可以级联2的7次方即128个设备,该模块级联了三个典型且通用I2C设备(这里为三个独立芯片),并且预留了级联更多I2C设备的接口,所以叫I2C模块。

为什么做这个I2C模块?在淘宝上搜索“I2C模块”,搜索结果中的I2C模块,一般是用一两个芯片实现对应的一两个功能,有的板上还集成非I2C相关的功能,不是纯粹的I2C模块,配套教程则比较杂乱。

于是我们决定做一个纯粹的、功能多一点的I2C模块,和Arduino配套,配上精心书写的“一份”教程。

我们强调教程的“一份”,是因为这份教程针对I2C的使用做了集中且系统的教学,不用再去搜索其他资料。

教程中使用到的Arduino库经过我们的开发,把相关功能都做好了封装,在代码中直接调用即可,无论是用来学习还是做产品开发,都简单和高效。

为了大家更好的学习,模块实行软硬件开源。

By MAKERTIPS2013年7月于广州大学城第1章 I2C模块规格说明1.1 综述I2C模块集成了三个芯片,分别实现三个功能:1、时间计算:DS13072、温度侦测:LM753、数据存储:AT24C32图1.1 I2C模块功能说明3D图1.2 特性1、使用实时时钟芯片DS1307计算时间2、使用温度传感器芯片LM75侦测温度3、使用EEPROM存储芯片AT24C32 存储数据4、通过精简的I2C总线实现以上功能5、使用CR2032锂电池为时钟芯片供电,可使用2年LM75DS1307AT24C326、设计小巧,PCB尺寸28mm*25mm7、引出LM75的OS脚,可作为温度中断输出8、通过排针J1或J2,可以级联其他I2C设备图1.2 小巧的I2C模块1.3 模块架构I2C(Inter-Integrated Circuit)总线是由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。

TI系列DSP的I2C模块配置与应用

p a p e r@m e s n e t.c o m.c n(投稿专用)2006年第4期M i c r o c o n t r o l l e r s&E m b e d d e dS y s t e m s67<’系列()*的’4-模块配置与应用□北京航空航天大学赵世峰张海范耀祖□中国航天时代电子公司吴海涛I2C总线最早是由P h i l i p s公司提出的串行通信接口规范。

标准I2C总线只使用两条线通信,能将多个具有I2C接口的设备连接,进行可靠的通信。

连接到同一总线的I2C器件数量,只受总线最大电容400p F的限制,而且最高通信速率可以达到3.4M b/s。

由于I2C接口简单,使用方便,被很多芯片采用,成为一种广泛应用的接口[1]。

D S P即数字信号处理器,是一种广泛应用的嵌入式处理器,主要应用是实时快速地实现各种数字信号处理算法。

目前,国际主要的D S P供应商是T I公司,其TM S32系列产品占据了D S P市场近一半的份额。

为了用户能方便快捷的进行系统的开发与集成,T I公司在一些型号的D S P中集成了I2C通信模块,本文以TM S320C6713为例,使用T I公司D S P开发工具C C S2.2提供的C S L(C h i p S u p p o r tL i b,片级支持库)配置I2C模块。

图像采集和处理是D S P应用的一个重要领域,本文结合作者开发的基于D S P的图像采集、处理系统,以C MO S图像采集芯片O V7620为例,介绍D S P芯片通过I2C模块对I2C设备进行配置的过程。

1T I公司带I2C接口的D S P在嵌入式系统开发过程中,如果处理器没有I2C接口而系统中又存在I2C器件时,通用的办法是利用处理器的两根引脚分别模拟S D A和S C L信号,并利用程序模拟接口。

这种方法的通用性好,灵活可靠,但是移植性差,不同型号的处理器需要不同的程序。

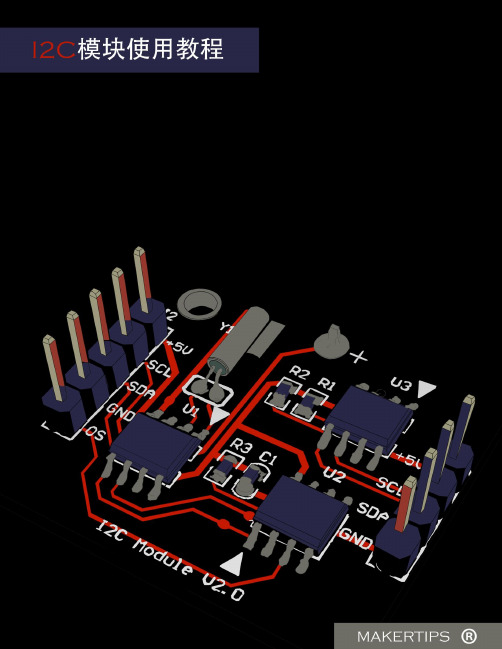

TI TMS320C2000 I2C模块参考指南

图 1 I2C 总线连接图 SDA 和 SCL 都是双向线路,通过一个上拉电阻连接到正的电源电压(如上图),总线特征包 括: a) 当场效应管接通时总线相当于接地,处于低电平状态; b) 当场效应管断开时上拉电阻 Rp 将总线上拉至高电平; c) 只要有设备将总线拉至低电平时,不管其它设备状态怎样,总线都将一直保持低电平; d) 当总线空闲时时钟线和数据线路都处于高电平状态。 2 I2C 模块的时钟 I2C 模块作为一个外设模块受到外设时钟控制寄存器 PCLKCR0 管理,在配置 I2C 模块前应该 确认 I2C 模块的时钟被打开(SysCtrlRegs.PCLKCR0.bit.I2CAENCLK = 1; // I2C)。

不管是七位地址还是十位地址模式,都有相当的数据传送和控制方式,包括重复起始条件、停 止条件、应答等,唯一不同的只是地址位数而已!

I2caRegs.I2CSAR 寄存器用于存储从机的地址。当满足开始发送条件的条件时,在发送完开始 条件后,I2C 模块将 I2caRegs .I2CSAR 中的地址复制到移位寄存器并按位发送出去。 3.2.1 七位地址格式

3.2 I2C 总线地址格式 I2C 总线规范中定义了两种地址格式:七位地址格式和十位地址格式。 I2C 模块中的 I2caRegs.I2CMDR.bit.XA 控制着地址格式,当 XA 为 1 时地址处于 10 位格式模式,

当 XA 为 0 时处于七位地址模式。同时还需要确认自由格式控制位已被关闭 (I2caRegs.I2CMDR.bit.FDF = 0),即七位地址和十位地址模式都不适用于自由模式。

b) 工作在主发模式工作时,有一个非应答(NACK)中断可用于主机对 NACK 位进行处理。

TI公司DSP系列概述解析

下一步可能的应用 ...

互联网相关: 智能电冰箱等

高速, 高密度磁盘驱动 数字视频

Internet 服务器

高精度的加工工艺

高效的 电动汽车

C2000系列DSP

子系列

C2xx子系列:16位定点DSP、20MIPS

➢代表器件:TMS320F206PZ C24x子系列:16位定点DSP、20MIPS

Memory Sub-System

Fast program execution out of both RAM and Flash memory

▪ 110-120 MIPS with Flash Acceleration Technology ▪ 150 MIPS out of RAM for time-critical code CCoonnttrrooll PPoerrtispherals

C6000™ DSP

Personal DSP

TI C55x™ DSP 核心: 世界上最低功耗性能比

mW/MIPS的DSPs

• 以达到0.05mW/MIPs的最低

功耗性能比而具有最长的电池 寿命。

• 最佳的代码密度 • 兼容C54x™ DSP软件

Broadband Infrastructure DSP

MIPS MEMORY

Flash ROM RAM Boot ROM EVENT MGR GP Timers CMP/PWM CAP/QEP 10-BIT ADC Channels Conv. Time COMMS SCI (UART) SPI CAN

GPIO

WATCHDOG

EMIF

VOLTAGE

PACKAGING

PRODUCTION Yr 2000 10Ku Pricing

I2C 模块的操作_16位单片机原理及应用──基于MSP430_[共5页]

![I2C 模块的操作_16位单片机原理及应用──基于MSP430_[共5页]](https://img.taocdn.com/s3/m/278a42ff4b73f242326c5fcb.png)

第6章通用同步/异步收发器USART 1456.3.2 I2C模块的操作I2C模块支持任何从机或主机的I2C兼容设备。

每个I2C设备有唯一的地址,并且可以作为一个发送器或一个接收器进行操作。

在进行数据传输的时候,连接到I2C总线器件可以被视为主机或从机。

时钟信号SCL由主机产生并传输。

I2C数据的传输是通过串行数据引脚(SDA)和串行时钟引脚(SCL)进行的。

两引脚都是双向接口,并且须使用上拉电阻连接到正电压源。

I2C总线连接图如图6.18所示。

图6.18 I2C总线连接图MSP430的SDA和SCL引脚不能被拉高到MSP430的V CC以上。

1.I2C模块初始化I2C模块是外设USART的一部分。

USART0用于I2C模式时,有些位的定义与SPI或UART模式不同。

U0CTL寄存器默认值是UART模式。

要选择I2C模式需对SYNC和I2C位进行置位。

在模块的初始化时,I2C模块准备好发送或接收操作。

置位I2CEN释放I2C模块进行操作。

只有在I2CEN=0时,才可配置或重新配置I2C模块,以避免不可预知行为。

设置I2CEN= 0具有以下效果。

①I2C通信停止。

② SDA和SCL是高阻抗。

③ I2CTCTL中位3~0被清零,位7~4不变。

④ I2CDCTL和I2CDR寄存器清零。

⑤发送和接收移位寄存器被清零。

⑥ U0CTL,I2CNDA T,I2CPSC,I2CSCLL,I2CSCLH寄存器不变。

⑦ I2COA,I2CSA,I2CIE,I2CIFG和I2CIV寄存器不变。

当从I2C模式转到UART或SPI模式时,必须先清零I2C、SYNC、I2CEN位,并置位SWRST,然后进行UART或SPI初始化程序。

不遵守此规程可能会导致不可预知操作发生。

(1)配置USART模块复位后用于I2C操作时,所需的I2C配置过程如下。

①SWRST=1,选择I2C模式(BIS.B #I2C + SYNC,&U0CTL)。

TI公司DSP系列概述解析

8-level hardware stack

Repeat count

2 status registers

Peripheral Bus

WD Timer CAN SCI SPI

A/D Converter

10 bits, 16 channels

C2000™: 参数选择列表

‘F240 ‘C240 ‘F241 ‘C242 ‘F243 ‘LF2402 ‘LC2402 ‘LC2404 ‘LF2406 ‘LC2406 ‘LF2407

Event Managers

Ultra-Fast 12-bit ADC

▪ 16.7 MSPS Conversion Speed ▪ Dual s/h enable simultaneous sampling ▪ Auto Sequencer, up to 16 conversions w/o CPU Communications Ports

PRODUCTION Yr 2000 10Ku Pricing

20 20 20 20 20 30/40 30/40 30/40 30/40

16K 8K 8K

8K

32K

16K 4K

4K

16K

544 544 544 544 544 544

544

1.5K 2.5K

Yes

Yes

3

3

2

2

2

Memory Sub-System

Fast program execution out of both RAM and Flash memory

▪ 110-120 MIPS with Flash Acceleration Technology ▪ 150 MIPS out of RAM for time-critical code CCoonnttrrooll PPoerrtispherals

DSP28335 I2C接口应用

D S P I2C应用说明1.示例程序中几种状态第一次看i2c_eeprom示例程序,对程序中的MsgStatus信息状态切换非常懵懂,为什么要有这几个状态?状态切换顺序如何安排?一大堆的状态,让人有些摸不着头脑。

先把程序中的头文件涉及的7种状态分析一下。

//I2CMessageCommandsforI2CMSGstruct#defineI2C_MSGSTAT_INACTIVE0x0000//未激活状态:一般成功发送数据或者//接受数据后可以设置信息状态为此状态,告诉用户可进行下一次的写数据或读数据。

#defineI2C_MSGSTAT_SEND_WITHSTOP0x0010//发送带停止位数据:这是为写数据而设///的状态,写入地址和数据之后发个停止位告诉存储器数据写入完毕。

#defineI2C_MSGSTAT_WRITE_BUSY0x0011//写数据忙状态:在将待写的数据放入//缓存后,就可以使能IIC传输数据了,然后把信息状态设为该状态,意在告诉用户:数据//已经在传送过程中。

当然是否传送完毕,还需要通过查询SCD位来判断。

#defineI2C_MSGSTAT_SEND_NOSTOP0x0020//发送无停止位数据:这个状态是为了读//取数据而设的,有查阅过AT24C1024EEPROM存储器使用手册的读者知道,在读数据之前//要发送数据的地址,发完地址不能产生停止位,这是存储器硬件设计决定的。

设为这个状//态意在告诉读者,可以发送要读取的数据的地址了。

#defineI2C_MSGSTAT_SEND_NOSTOP_BUSY0x0021//发送无停止位数据忙状态:这个状态是//为了读取数据而设的,似于I2C_MSGSTAT_WRITE_BUSY,说明地址数据已经在传送过程中。

//传送是否成功,还要看ARDY的状态。

#defineI2C_MSGSTAT_RESTART0x0022//重发开始位状态:这个状态也是为读取////数据而设。

TI系列DSP的I2C模块配置与应用

TI系列DSP的I2C模块配置与应用

赵世峰;张海;范耀祖;吴海涛

【期刊名称】《单片机与嵌入式系统应用》

【年(卷),期】2006(000)004

【摘要】I2C总线最早是由Philips公司提出的串行通信接口规范。

标准I2C总线只使用两条线通信,能将多个具有I2C接口的设备连接,进行可靠的通信。

连接到同一总线的I2C器件数量,只受总线最大电容400pF的限制,而且最高通信速率可以达到3.4Mb/s。

由于I2C接口简单,使用方便,被很多芯片采用,成为一种广泛应用的接口。

【总页数】3页(P67-69)

【作者】赵世峰;张海;范耀祖;吴海涛

【作者单位】北京航空航天大学;北京航空航天大学;北京航空航天大学;中国航天时代电子公司

【正文语种】中文

【中图分类】TN43

【相关文献】

1.利用I2C总线实现DSP对SAA7113H的配置 [J], 温贺平;戴青云;刘志鑫

2.利用I2C总线实现DSP对增强型视频输入处理器SAA7111A EVIP的配置 [J], 李立庄;胡方明

3.基于TMS320C6000系列DSPs的驱动模块设计 [J], 张路

4.TMS320系列DSP与I2C总线的接口 [J], 徐婉莹;黄新生

5.TI针对电信基础局端及医疗等新兴应用推出最新DSP产品系列 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

jh1[通信电子]利用I_2C和McBsp接口实现DSP与CODEC芯片的数据传输

![jh1[通信电子]利用I_2C和McBsp接口实现DSP与CODEC芯片的数据传输](https://img.taocdn.com/s3/m/09f9951dba68a98271fe910ef12d2af90242a84c.png)

利用I 2C 和McBsp 接口实现DSP 与CODEC 芯片的数据传输武晓光1,郭天文2(1.南京工业大学信息学院 江苏南京 210009;2.中国矿业大学信电学院 江苏徐州 221008)摘 要:首先介绍TMS320VC5509DSP 芯片I 2C 和McBsp 接口特点及功能,结合音频CODEC 芯片TL V320A IC23B 的工作原理,详细阐述该芯片与DSP 相连的配置和数据接口的设计方法,并给出实现与DSP 数据传输的汇编程序示例。

关键词:DSP ;TL V320A IC23B ;I 2C ;McBsp中图分类号:TN91213 文献标识码:B 文章编号:1004373X (2006)2413703Implementation of Data T ransmission bet w een DSP and Audio Codec by I 2C and McBspWU Xiaoguang ,GUO Tianwen(1.College of Information Science and Engineering ,Nanjing University of Technology ,Nanjing ,210009,China ;2.School of Information and Electrical Engineering ,China University of Mining &Technology ,Xuzhou ,221008,China )Abstract :In this paper ,firstly introduced the feature and function of I 2C and McBs Pinterface on TMS320VC5509chip ,combined with the principle of CODEC TL V320A IC23B ,then the paper expounded in detail the design method of Configura 2tion and data interface that connect TL V320A IC23B with DSP ,At last ,provides a example ASM program that can realize the data Transmission between them.K eywords :DSP ;TL V320A IC23B ;I 2C ;McBsp收稿日期:200608301 引 言在语音信号处理系统中,DSP 要完成信号的采集和运算处理任务,必须有前端语音信号A/D ,D/A 转换接口电路的配合。

DSP原理及应用技术第7.4节 I2C模块

7.4.3 I2C模块中断请求

1. 基本的I2C中断请求

如图7-50所示,I2C模块通过复用一个仲裁器向CPU发送一个 I2C中断请求。每个中断请求在状态寄存器(I2CSTR)中有一个标 志位,在中断使能寄存器(I2CIER)中有一个使能位。当一个指定 的事件发生时,它的标志位被置位。如果相应的使能位为0,则中 断请求被拦截;而如果使能位为1,请求作为I2C中断转发给CPU。

Байду номын сангаас

7.4.1 I2C模块概述

4.I2C模块的主要组成

I2C模块结构框图如图7-39所示

图7-39 I2C模块结构框图

7.4.1 I2C模块概述

4.I2C模块的主要组成 I2C模块主要包含:

➢ 一个串行接口:一个数据引脚(SDA)和一个时钟引脚(SCL) ➢ 数据寄存器和FIFO:暂时保存SDA引脚与CPU之间传递的接收数

7.4.3 I2C模块中断请求

1. 基本的I2C中断请求

I2C总线模块产生的中断请求如表7-50所述。I2C中断是CPU可

屏蔽中断之一。和其它中断请求一样,如果已在CPU内被使能,则

执行相应的中断服务程序(I2CINT1A_ISR)。可以通过读中断源寄

存器I2CISRC的值来确定I2CINT1A_ISR中断源(中断事件),这便

据和发送数据。 ➢ 控制和状态寄存器。 ➢ 外围总线接口:用于CPU访问I2C模块寄存器和FIFOs。 ➢ 时钟同步器:用来使I2C输入时钟(由DSP时钟源产生)和SCL引

脚的时钟同步,并且使数据发送器与不同的主机时钟速度同步 ➢ 对输入到I2C模块的时钟进行分频的预定标器。 ➢ SDA和SCL引脚上的噪声滤波。 ➢ 用来处理I2C模块和其它主器件的仲裁问题的仲裁器。 ➢ 中断产生逻辑,用以向CPU发送中断信号。 ➢ FIFO中断产生逻辑:以便在I2C模块中接收数据或发送数据时能

I^2C总线技术在DSP系统中的实现

I^2C总线技术在DSP系统中的实现

柯艳明

【期刊名称】《黄石理工学院学报》

【年(卷),期】2008(24)1

【摘要】许多嵌入式系统处理器由于不带有I2C总线接口而限制了I2C总线接口

器件在其上的应用。

介绍了I2C总线的特点和时序,并以串行E2PROM为例,给出

了在TMS320F240X DSP系统中模拟实现I2C总线的方法。

实践证明,该方法简单、可靠,对于构建实际的DSP应用系统来说具有现实的参考价值。

【总页数】3页(P7-9)

【关键词】I^2C总线;DSP;E^2PROM

【作者】柯艳明

【作者单位】黄石理工学院电气与电子信息工程学院

【正文语种】中文

【中图分类】TP336

【相关文献】

1.I2C串行总线技术在DSP系统中的虚拟实现 [J], 刘滨;姜广欣;杨占录

2.I2C总线技术在 DSP 系统中的实现 [J], 柯艳明

3.视频解码技术中I^2C总线控制核的实现 [J], 闫霞;方康玲

4.基于MCU和CPLD系统中I^2C总线控制器的设计与实现 [J], 吴繁红

5.I^2C总线在51系列单片机系统中的实现 [J], 孙艳秋;康巍威

因版权原因,仅展示原文概要,查看原文内容请购买。

利用I^2C总线实现DSP对CMOS图像传感器的控制

利用I^2C总线实现DSP对CMOS图像传感器的控制

王金涛;王雨;罗世军

【期刊名称】《国外电子测量技术》

【年(卷),期】2001()4

【摘要】介绍了 I^2C串行总线,TI公司的TMS320C32,OmniVision公司的

OV7100的性能和特点。

提出了一种利用 DSP的多功能口实现 I^2C总线控制方法。

【总页数】3页(P29-30)

【关键词】I^2C总线;CMOS图像传感器;数字信号处理器

【作者】王金涛;王雨;罗世军

【作者单位】天津大学精仪学院;北京大洋公司;四川自贡教育学院

【正文语种】中文

【中图分类】TP212

【相关文献】

1.基于I~2C总线的数字温度传感器与DSP实现温度采集 [J], 闫江周;梁涛;董鹏飞;

2.基于I^2C总线图像传感器配置的FPGA实现 [J], 操亚华

3.基于CMOS技术的I^2C总线接口实现方法 [J], 张涛;郑冬军;王婧

4.基于I^2C总线的CMOS图像传感器接口电路设计 [J], 黄全平;周荣政;席占国;张原;洪志良

5.OmniVision图像传感器的SCCB总线协议在DSP中的实现 [J], 苑玮琦;汤永华

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0 0 H ̄ 0 F H 和 0 0 H ̄0 F H 这 三 个 区域 存 储 同 样 10 1F 20 2F

一

参 考 文 献

1 施 忠 培 .R AM 掉 电 保 护 电路 的 设计 .福 建 电 脑 ,0 3 7 :1 2 0 ( )6

如图 1 示。 所

数 据总线

D P中集 成 了 1c通 信 模 块 , 文 以 T 3 0 6 1 S 本 MS 2 C 7 3为

例, 使用 T 公司 D P开发工具 C S . 提供 的 C L C i I S C 22 S ( hp

S p ot , u p r Ib 片级 支 持 库 ) 置 IC模 块 。 i 配 2

SDA

亟 亟 母.CP源自 S CL 1 T 公司带 1 l 2 C接 口的 D P S

在嵌入式系统开发过程中 , 如果 处理 器 没 有 1C 接 1 2 3

而系统中又存在 IC器件时 , z 通用的办法是利用处理 器的

两 根 引 脚 分 别 模 拟 S A 和 S L信 号 , 利 用 程 序 模 拟 接 D C 并

维普资讯

IC X 2 D R是 发送 缓存 ,2 X R是 发送 移 位 寄 存 器 。 IC S

4 周立.几种实用的单片机抗干扰和掉电保护 电路.煤矿 自动

化 ,O l 4 :8 4 2O ( )4  ̄ 9

( 稿 日期 t 0 5 1 — 8 收 0 — 11 ) 2

Mcc tl s me eS t s 6 i o rl &E b d sm r noe o r ddye 7

维普资讯

_ ll l 。

l l l

T 系列 D I - S P的 2 C横块配置与应用

■ 北 京 航 空 航 天 大 学 ■ 中 国航 天 时代 电子 公 司

赵 世 峰 张 海 范 耀 祖

吴 海 涛

1C总线最 早是 由 P ip 公 司提出 的串行通信 接 口 hl s i

图像采 集和处理 是 DS P应用 的一个 重要领 域 , 文 本 结合 作 者 开 发 的 基 于 D P的 图 像 采 集 、 理 系 统 , S 处 以

C S图像 采集 芯 片 O 6 o为例 , MO V7 2 介绍 D P芯 片通 过 S IC模块对 1c设备进行配置的过程。 z 2

TM S 2 C6 1 、 3 O 7 3 TMS 2 C 4 6 TMS 2 C5 0 3O 61 、 3 0 5 9等 。

使用方便 , 被很 多芯片采用 , 成为一种广泛应用的接 1E 。 2l 1i D P即数字信号处理器 , S 是一种广泛应用的嵌入式处 理器 , 主要应 用 是实 时快 速地 实 现各 种数 字信 号处 理 算

2 王幸之 , 王雷 , .单 片机 应 用 系 统 抗 干 扰 技 术 .北 京 : 京 等 北

航 空 航 天 大 学 出版 社 ,9 9 1 9

组数据 , 当使用这些数据前 , 先对各组进行检查 , 于正 对

3 高东林.单 片机 系统 可靠掉 电保护 的实现.测控技 术 ,02 20

( ): 2 6 1 6~ 3

TMS 2C 7 3 3O 6 1 是一款 高性 能 浮点 D P, S 内部集 成 2

个 1C接 口 : C 1 O和 1C 。其 中 , 1 引 脚 与 Mc S 1 1 1C 的 B P

法 。目前 , 国际主要的 D P供应商是 T 公 司, T 3 S I 其 MS 2

系列产品 占据了 D P市场 近一半 的份额 。为了用户 能方 S

圈 圆 圆 圃

I 件 [ c 事

圈1 1 2 C模 块 结构

EDM A

C U 断 P 中

EDM A

控制 器 同步

口。这种方 法的通 用性好 , 灵活可靠 , 是移植性差 , 同 但 不

生时可保 证数据 的准确无误 。耀

4 采用 软 件 冗 余措 施保 证 数 据 的准 确 性

的 1c器件数量 , 只受总线最 大电容 4 0p 0 F的限制 , 且 而

最 高 通 信 速 率 可 以 达 到 3 4Mb s 由 于 1C接 口简 单 , . /。 2

为 了用户能方 便 快捷地 进行 系统 的开发与 集成 , I T

公 司在 一 些 型 号 的 DS P中集 成 了 1C通 信 模 块 , 如 2 例

确 的数据方可应用 , 同时将错误的数据进行修正。在上 电 与断电过程 中, 总线不 确写性是 随机 的 , 不可将 所有数 据 完全 冲失 。采用硬件对数据进行断电保护 , 同时在软件上 采用 的冗余措施是最常用的数据保护方法 , 在断电突然发

p e msto. ( 稿 用 a r eec c 投 专 ) p @ n.r n n

便 快捷 的进 行 系 统 的 开 发 与 集 成 , I 司 在 一 些 型 号 的 T 公

( h can l ufrdSr l ot , Mu i n e B f e ei r 1 多通 道缓存 串 口 1 h e aP ) 的引脚 复用 , 默认情况 下是激活 Mc S 1 使用 IC BP , 1必须 将 寄存器 D VC G 的最低 位 置 12 E F [ 。1C模块 的结 构 , 2

规范 。标准 IC总线 只使 用 两条 线 通 信 , 将 多个 具有 2 能

型号的处理器需要 不 同的程序 。尽 管在 网上能够 下载到 这类程序 的源代码 , 但是进行程序移植仍会浪费开发人员 大量的时间 , 而且使得程序变得庞 大, 不易维护 。

IC接 口的设备连 接 , 2 进行 可靠 的通信 。连 接到同一总 线