GAL20V8引脚分布

8050-8550三极管引脚图与管脚识别

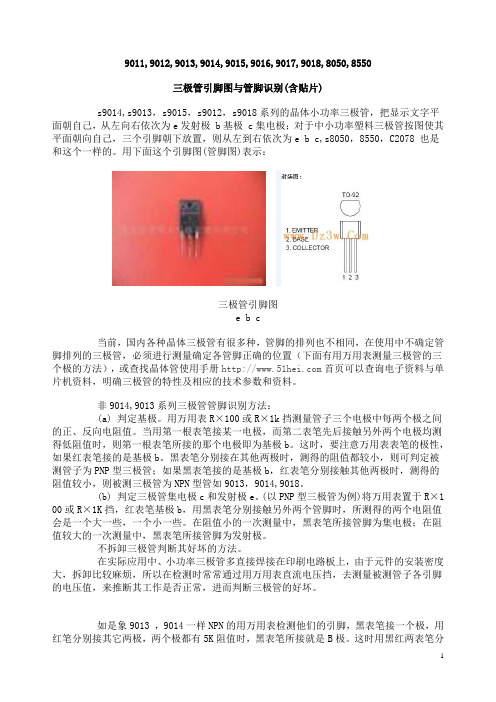

9011,9012,9013,9014,9015,9016,9017,9018,8050,8550三极管引脚图与管脚识别(含贴片)s9014,s9013,s9015,s9012,s9018系列的晶体小功率三极管,把显示文字平面朝自己,从左向右依次为e发射极 b基极 c集电极;对于中小功率塑料三极管按图使其平面朝向自己,三个引脚朝下放置,则从左到右依次为e b c,s8050,8550,C2078 也是和这个一样的。

用下面这个引脚图(管脚图)表示:三极管引脚图e b c当前,国内各种晶体三极管有很多种,管脚的排列也不相同,在使用中不确定管脚排列的三极管,必须进行测量确定各管脚正确的位置(下面有用万用表测量三极管的三个极的方法),或查找晶体管使用手册首页可以查询电子资料与单片机资料,明确三极管的特性及相应的技术参数和资料。

非9014,9013系列三极管管脚识别方法:(a) 判定基极。

用万用表R×100或R×1k挡测量管子三个电极中每两个极之间的正、反向电阻值。

当用第一根表笔接某一电极,而第二表笔先后接触另外两个电极均测得低阻值时,则第一根表笔所接的那个电极即为基极b。

这时,要注意万用表表笔的极性,如果红表笔接的是基极b。

黑表笔分别接在其他两极时,测得的阻值都较小,则可判定被测管子为PNP型三极管;如果黑表笔接的是基极b,红表笔分别接触其他两极时,测得的阻值较小,则被测三极管为NPN型管如9013,9014,9018。

(b) 判定三极管集电极c和发射极e。

(以PNP型三极管为例)将万用表置于R×1 00或R×1K挡,红表笔基极b,用黑表笔分别接触另外两个管脚时,所测得的两个电阻值会是一个大一些,一个小一些。

在阻值小的一次测量中,黑表笔所接管脚为集电极;在阻值较大的一次测量中,黑表笔所接管脚为发射极。

不拆卸三极管判断其好坏的方法。

在实际应用中、小功率三极管多直接焊接在印刷电路板上,由于元件的安装密度大,拆卸比较麻烦,所以在检测时常常通过用万用表直流电压挡,去测量被测管子各引脚的电压值,来推断其工作是否正常,进而判断三极管的好坏。

GAL的工作模式资料

G A L的工作模式GAL16V8有3种工作模式,即寄存器模式、复合模式和简单模式。

适当连接器件的引脚线,由OLMC的输出/输入特性可以决定其工作模式。

GAL16V8寄存器模式在寄存器模式中,宏单元被配置为专用的寄存器输出或者I/O功能。

这种模式中有效的结构配置与普通的16R8和16RP4器件类似,只是在极性,I/O和寄存器布置方面有不同。

所有的宏单元共享共同的时钟和输出使能控制引脚。

任一个宏单元都能够被配置成寄存器或I/O形式,可以多至8个。

专用的输入或输出功能能够被用作I/O功能的子系统。

寄存器形式输出每个输出端有8个乘积项(图A),I/O形式输出端有7个乘积项(图B),在两个图中,引脚1和11总是分别地配置为时钟输入和输出使能,不能被配置为专用输入。

包括用户电子签名(UES)熔丝和乘积项禁止 (PTD) 熔丝,JEDEC熔丝数显示在下页的逻辑图上。

引脚号功能20 V cc10 地2~9 仅作为输入1 时钟输入11 使能(低电平有效)12~19 输入或输出(本引脚反馈),图A和图B图A,寄存器配置,输入或输出,引脚12...19, 8个输出乘积项,本引脚反馈,/OE和CLK公用图B,组合I/O配置,输入或输出,引脚12...19,7个输出乘积项,1 个使能乘积项,本引脚反馈寄存器模式逻辑图输入引脚2-9I/O 引脚12-19,本引脚反馈时钟引脚1输出使能引脚11GAL16V8复合模式在复合模式中,宏单元或者仅仅配置为输出功能或者配置为I/O功能。

这个模式中有效的结构配置类似于普通的16L8和16P8器件,只是在每个宏单元中带有可编程的极性。

这个模式中最多能有6个I/O口,专用的输入或输出功能能够被用作I/O功能的子系统(图A)。

2个最外边的宏单元(引脚 12 和 19)没有输入能力(图B)。

在寄存器模式中能够实现设计需要的8个I/O口。

全部宏单元的每一个输出端有7个乘积项,1个乘积项被用于可编程的输出使能控制(图A和图B)。

GAL芯片

6.1 时序逻辑电路的基本概念 6.2 同步时序逻辑电路的分析 6.3 异步时序逻辑电路的分析 6.4 同步时序逻辑电路的设计 6.5 典型的时序逻辑集成电路 6.6 时序可编程逻辑器件GAL

(Generic Array Logic)

可编程逻辑器件(PLD)分类

PLD

F=A&!B #!A&B;

Q:=!Q; Q.CLK=CP; when (select==0) then out=d0

else out=d1;

when (S < 9) then S:=S.fb+1

Else S:=0;

WHEN-THEN-ELSE 语句

when X==1 then S:=B else 件

〔 *.abl *.sch *.abv

逻辑设计

编写逻辑描述文件 (源文件输入)

编译与仿真

器件适配

*.jed

写入芯片 (编程器)

主要生成文件

*.jed

Isp器件可直接 下载

硬件通电测试(统调)

ispEXPERT 设计方法

1. ABEL-HDL语言基本元素 2. 源文件格式 3. ispEXPERT 设计举例

ABEL-HDL基本元素

寄存器的点后缀表示

.CLK

边沿触发器的时钟输入

. SP

同步置1

.SR

同步置0

.AP

异步置1

.AR

异步置0

.FB

寄存器反馈信号

.OE

输出允许

.Q

寄存器输出

…… 常用:

Q:= ;

Q.CLK=CLK1;

(不用的功能端,其点缀方程可不写)

ABEL-HDL基本元素

附录A-常用芯片引脚功能图-分类-肖琼

《数字逻辑》课程实验芯片汇集惠州学院计算机科学系“数字系统设计”实验室2013年3月目录四2输入正与非门74LS00 (3)四2输入正与非门74LS20 (3)六反向器74LS04 (4)四2输入正或非门74LS28 (4)四2输入异或门74LS86 (5)四2输入与门74LS08 (5)4—2—3—2与或非门74LS64 (6)三态输出的四总线缓冲器74LS125 (7)3线-8线译码器74LS138 (8)10 线-4 线优先编码器(BCD 输出)74LS147 (9)8线-3线优先编码器74LS148 (10)双2:4线译码器/分配器74LS139 (11)8选1数据选择器74LS151 (12)双4:1线数据选择器/多路开关74LS153 (13)双四位十进制计数器74LS390 (14)4位二进制全加器74LS83 (15)四位比较器74LS85 (16)3:8线译码-驱动CD4543 (17)双2线 - 4线译码器74HC139 (18)七段数码管5011AS (18)双下沿J-K触发器74LS114 (19)4位二进制同步加法计数器74LS161 (20)双J-K触发器(带清除端)74LS73A (21)双D正边沿触发器74LS74 (22)同步十进制计数器74LS162 (23)四上升沿 D 触发器74LS175 (24)4位双向移位寄存器74LS194 (25)四位通用移位寄存器74LS195 (26)可编程并行接口逻辑器件8255A (27)可编程与阵列逻辑器件GAL16V8 (27)可编程与阵列逻辑器件GAL20V8 (28)四2输入正与非门74LS001.外引线排列图2.逻辑电路图3.功能表四2输入正与非门74LS201.外引线排列图2.逻辑电路图3.功能表六反向器74LS041.外引线排列图2.逻辑电路图3.功能表四2输入正或非门74LS281.外引线排列图2.逻辑电路图3.功能表四2输入异或门74LS861.外引线排列图2.逻辑电路图3.功能表四2输入与门74LS081.外引线排列图2.逻辑电路图3.功能表4—2—3—2与或非门74LS641.外引线排列图2.逻辑电路图3.功能表三态输出的四总线缓冲器74LS1251.外引线排列图2.逻辑电路图3.功能表3线-8线译码器74LS1381. 外引线排列图2.逻辑电路图3.功能表10 线-4 线优先编码器(BCD 输出)74LS1471.外引线排列图2.逻辑电路图3.功能表8线-3线优先编码器74LS1481.外引线排列图2.逻辑电路图3.功能表双2:4线译码器/分配器74LS1391.外引线排列图2.逻辑电路图3.功能表8选1数据选择器74LS1511.外引线排列图2.逻辑电路图3.功能表双4:1线数据选择器/多路开关74LS1531.外引线排列图2.逻辑电路图3.功能表双四位十进制计数器74LS3901.外引线排列图2.逻辑电路图3.功能表4位二进制全加器74LS831.外引线排列图2.逻辑电路图3.功能表四位比较器74LS851.外引线排列图2.逻辑电路图3.功能表3:8线译码-驱动CD45431.外引线排列图2.逻辑电路图3.功能表双2线- 4线译码器74HC1391.外引线排列图2.功能表七段数码管5011AS1.外引线排列图2.功能表双下沿J-K触发器74LS1141.外引线排列图2.逻辑电路图3.功能表4位二进制同步加法计数器74LS1611.外引线排列图2.逻辑电路图3.功能表双J-K触发器(带清除端)74LS73A1.外引线排列图2.逻辑电路图3.功能表双D正边沿触发器74LS741.外引线排列图2.逻辑电路图3.功能表同步十进制计数器74LS1621.外引线排列图2.逻辑电路图3.功能表四上升沿 D 触发器74LS1751.外引线排列图2.逻辑电路图3.功能表4位双向移位寄存器74LS1942.逻辑电路图1.外引线排列图3.功能表四位通用移位寄存器74LS1951.外引线排列图2.逻辑电路图3.功能表可编程并行接口逻辑器件8255A1.外引线排列图2.逻辑图可编程与阵列逻辑器件GAL16V81.外引线排列图2.功能方框图1.外引线排列图2.功能方框图更多芯片,请查阅:/DataSheet/。

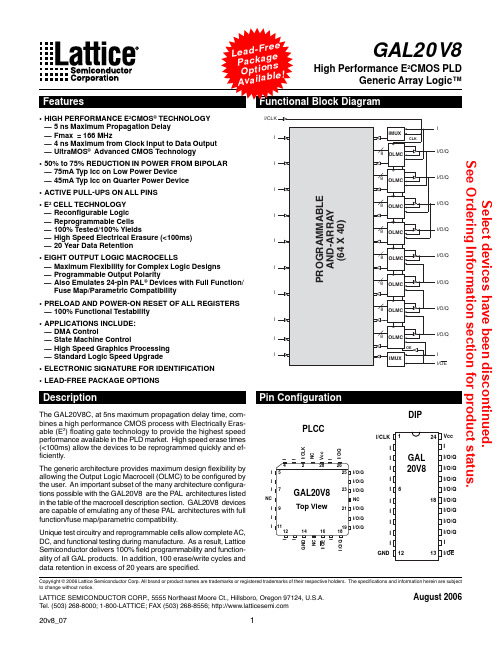

GAL20V8_06资料

GAL20V8 Ordering Information

Conventional Packaging Commercial Grade Specifications

Tpd (ns) Tsu (ns) Tco (ns) Icc (mA)

Ordering #

5

3

4

115 GAL20V8C-5LJ1

7.5

元器件交易网

Select devices have been discontinued. See Ordering Information section for product status.

LePAOaavpdact-kiliFaaorgbneelsee!

GAL20V8

55 GAL20V8B-25QP

55 GAL20V8B-25QJ

90 GAL20V8B-25LP

90 GAL20V8B-25LJ

Industrial Grade Specifications

Package 28-Lead PLCC 28-Lead PLCC 24-Pin Plastic DIP 28-Lead PLCC 24-Pin Plastic DIP 24-Pin Plastic DIP 28-Lead PLCC 24-Pin Plastic DIP 28-Lead PLCC 24-Pin Plastic DIP 28-Lead PLCC 24-Pin Plastic DIP 28-Lead PLCC

2

Select devices have been discontinued. See Ordering Information section for product status.

元器件交易网

VME总线的工作原理简介

VME总线的工作原理简介李慎旭李东方高原山东电视台发射台有4个频道的主机是汤姆逊公司生产的全固态电视发射机,除2频道外其他3个频道的主机都配置了计算机控制系统,且这种计算机控制系统是基于VME总线的。

VME总线出现于1981年,它是由motorola公司推出的,经过二十几年连续不断的开发,是稀有的进入21世纪仍然大规模应用的工控总线,VME总线如此强大的生命力和广阔的应用前景源自VME总线的许多独具的特点。

由于电视发射机属于专用设备,应用规模少,而从国外引进的全固态电视发射机数量更少,因此各种电视技术期刊中对VME总线的介绍更是稀少,本文即是对VME总线的标准及其工作原理的简介,以便给同业人员研究基于VME总线全固态电视发射机的计算机控制系统提供一些帮助。

一、VME总线类属计算机系统中应用的总线可分为外部总线和内部总线两大类。

外部总线如:RS-232-C、RS-485、IEEE-488、USB等总线;而内部总线又可分为系统总线和片级总线,片级总线如:I2C总线、SPI总线、SCI总线等;系统总线如:ISA总线、EISA总线、VESA总线、PCI总线;工业现场总线如:VME,STD、PC-104、compact PCI等。

二、VME总线简介VME总线,Versamodel Eurocard由Motorola公司1981年推出的第一代32位工业开放标准总线,其主要特点是VME总线的信号线模仿Motorola公司生产的68000系列单片机信号线,由于其应用的广泛性被IEEE收为标准,即IEEE 1014-1987,其标准文件为VMEbus specification Rev C.1。

VME总线的插板一般有两种尺寸,一种是3U高度的带一个总线接口J1,高*长为100mm*160mm,另一种是6U高度的带2个总线接口J1、J2,高*长为233mm*160mm。

一般每块VME总线的插板上的接口J1、J2都有96针,每一个接口都是3排,按A、B、C排列,每排32针,J1一般用于直接与VME总线相连,J2的中间列用于扩展地址总线或数据总线,另外两列可由用户定义及I/O、磁盘驱动及其他外设等,(注意:我们应用的全固态电视发射机的I/O板和RC/RI板就扩展了J2口的针脚。

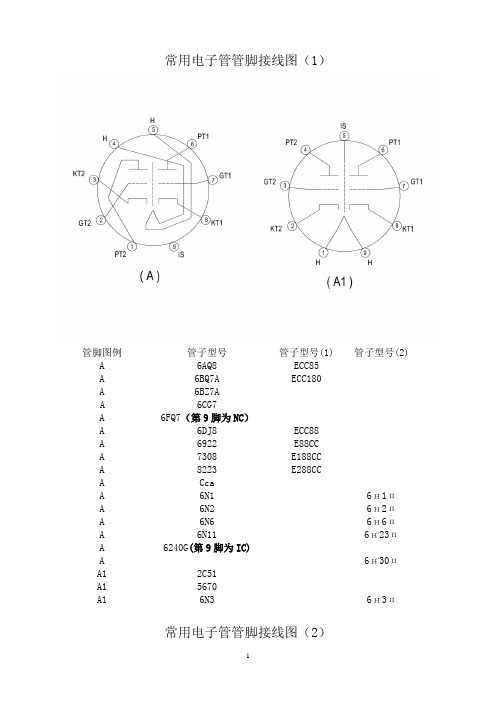

常见电子管管脚接线图

常用电子管管脚接线图(1)管脚图例管子型号管子型号(1) 管子型号(2)A 6AQ8 ECC85A 6BQ7A ECC180A 6BZ7AA 6CG7A 6FQ7(第9脚为NC)A 6DJ8 ECC88A 6922 E88CCA 7308 E188CCA 8223 E288CCA CcaA 6N1 6н1пA 6N2 6н2пA 6N6 6н6пA 6N11 6н23пA 6240G(第9脚为IC)A 6н30пA1 2C51A1 5670A1 6N3 6н3п常用电子管管脚接线图(2)管脚图例管子型号管子型号(1) 管子型号(2)B 12AT7 ECC81B 12AU7 ECC82B 12AX7 ECC83B 12BH7B 5751B 5814AB 6201 E81CCB 6189 E82CCB 6681 E83CCB 7025B 12AY7 6н4пB ECC99B E80CCB 6N4B 6N10B 2025B1 5687B1 7119 E182CC常用电子管管脚接线图(3)管脚图例管子型号管子型号(1) 管子型号(2)C 6SL7GTC 5691C 6SN7GTC 5692C 6N8P 6н8сC 6N9P 6н9сC ECC33C 6AS7GC 6080C 6N5P 6н5сC 6N13P 6н13сC 6BX7GTC 6BL7GTAD 6BQ5 EL84D 7189D 6P14 6п14п常用电子管管脚接线图(4)管脚图例管子型号管子型号(1) 管子型号(2)E 6F6GTE 6L6GE 6L6GCE 6V6GTE 5881E 6550AE KT88(第1脚为BC)E KT66E 1614E 7581AE 6P3P 6п3сE 6P6P 6п6сE 6G-B8F 2A3F 2c4cF 45F 50F 300BF 4300B常用电子管管脚接线图(5)管脚图例管子型号管子型号(1) 管子型号(2)G 211G 845H EL34 6CA7常用电子管管脚接线图(6)管脚图例管子型号管子型号(1) 管子型号(2)I 7027AK 7868常用电子管管脚接线图(7)管脚图例管子型号管子型号(1) 管子型号(2) L 807L FU-7 г-807M 6AU6 EF94M 6BA6 EF93M 6BD6M 6J4 6ж4пM 6J5 6ж5п常用电子管管脚接线图(8)管脚图例管子型号管子型号(1) 管子型号(2) M1 6AG5 EF96M1 6AK5 EF95M1 6BC5M1 6J1 6ж1пM1 6J3 6ж3пN 6267 EF86N 6J8 6ж32п常用电子管管脚接线图(9)管脚图例管子型号管子型号(1) 管子型号(2) N1 6BX6 EF80N1 6EJ7 EF184O 6SJ7GTO 5693O 6J8P 6ж8с常用电子管管脚接线图(10)管脚图例管子型号管子型号(1) 管子型号(2) P 5AR4 GZ34P 5V4GP 5Z4GT GZ30P GZ32P GZ33P GZ37P U54P 5Z4P 5ц4сQ 5U4GQ 5U4GBQ 5Z3P 5ц3с常用电子管管脚接线图(11)管脚图例管子型号管子型号(1) 管子型号(2) R 5R4GYR 5Y3GTR 274BR 5Z2PS 5Z3S 80常用电子管管脚接线图(12)管脚图例管子型号管子型号(1) 管子型号(2) T 6CA4 EZ81T EZ80U 6X4 EZ90常用电子管管脚接线图(13)管脚图例管子型号管子型号(1) 管子型号(2) U1 6Z4 6ц4пV 7591常用电子管管脚接线图(14)管脚图例管子型号管子型号(1) 管子型号(2) W 6AN8X 6BL8 ECF80X 6U8A ECF82常用电子管管脚接线图(15)管脚图例管子型号管子型号(1) 管子型号(2) Y 7199注:F----灯丝 G----栅极 G1----控制栅 G2----帘栅极 G3----抑制栅极或集射屏 H----热丝 K----阴极 P----屏极IC----管内没有电极连接的空脚,但管座上的焊片不能作中继连接端子用。

某型光电雷达系统中 GAL 芯片的解密方法研究

某型光电雷达系统中 GAL 芯片的解密方法研究摘要:介绍了某型光电雷达电子机载系统中常用的GAL系列可编程控制器的源程序破解方法,对实际破解过程中遇到的问题进行总结分析,并给出一个维修测试方法,实验结果表明:采用superpro编程器结合ABEL编译器软件可以实现程序破解和烧录需求,能满足使用要求。

关键词:GAL可编程控制器;光电雷达;ABEL语言;破解1引言通用逻辑可编程器件GAL[1]是在PAL器件基础上发展起来的PLD器件,在结构和工艺上作了很大改进,由于其性能稳定,价格低廉一直被广泛应用于工业生产中,某型光电雷达系统中使用较多的是GAL16V8B和GAL20V8D这两种。

为了提高对某型光电雷达系统相关电路板整体功能的了解和工厂修理能力建设,需要通过对相关芯片源程序的破解以了解其输出与输入的逻辑关系。

本文介绍的对GAL芯片的破解方法以GAL16V8B为例,先通过superpro编程器读取相关芯片熔丝图,获取其jed [2]文件,最后使用ABEL编译器将jed文件进行反编译来获取原始程序,并对反编译后的结果进行验证测试。

2读取GAL芯片的jed文件将需要破解的GAL芯片放入superpro编程器中,直接读取芯片的熔丝图并保存成jed格式文件。

文件格式如下所示:MODULE:SUPERPROTITEL:C:\Documents and Settings\Administrator\桌面\1.jedDD GAL16V8*DM LATTICE*QP20*QF002194*QV0*F0*L000000 0000000000000000000000000000000000000000*……………………………………………………L002160 1111111111111111111111111111111110*C229B*jed文件以ASCII码形式表示出熔丝图、测试、标识和注释信息,是软件编程和器件编程之间一种“中间代码”。

8pin引脚定义

8pin是一种电子元器件/器件的类型,它包含8个引脚。

8pin通常用于集成电路、继电器、变压器、传感器等设备中,以下是一些常见8pin引脚定义:

1. VCC:电源正极,通常是5V 或者3.3V,用于为元器件提供电源。

2. GND:电源负极,用于为元器件提供电源的地。

3. IN(输入):接收信号输入引脚。

4. OUT(输出):输出已处理或转换后的信号引脚。

5. SCLK:时钟信号输入引脚,用于数据同步。

6. EN(使能):使能引脚,用来控制设备的启停,或者切换节能模式。

7. CS(片选):芯片选择引脚,用于选择和确定元器件或IC的操作对象。

8. NC(未连接):未连接引脚,当元器件功能不需要时常被保留为未连接状态。

GAL20V8是通用可编程逻辑器件

GAL20V8是通用可编程逻辑器件GAL20V8是通用阵列逻辑器件,现场可编程器件。

它最多可以有20个输入引脚、最多可以有8个输出引脚。

它既可以实现组合逻辑的逻辑功能,也可以实现时序逻辑的逻辑功能。

通用可编程器件GAL20V8有8个输出引脚,分别标为IO0~IO7,有I1~I10、I12和I13共12个专用输入引脚,另有I0/CLK和I11/OE两个引脚,当被编程的电路需要时钟信号和使用输出允许控制时,时钟脉冲和输出允许控制信号就只能分别从I0/CLK和I11/OE这两个引脚输入;当不需要这两个信号(或一个)时,它们(或一个)可用作数据输入引脚。

IO0~IO7在某些场合,也可用于输入功能,或分时用于输入/输出功能,可由用户决定。

所以说它最多有20个输入、8个输出(至少有2个引脚用于输出)。

GAL20V8内部,包括输入缓冲门、输出反馈缓冲门、与门阵列、输出逻辑宏单元OLMC(内含或阵列)和输出三态门等。

要对通用可编程器件GAL20V8进行编程,需要使用专用的软件工具和能对GAL 器件编程的编程器,才可以向GAL20V8器件内写入所需要的逻辑功能。

设计和操作过程大体如下:1.编辑扩展名为“.PLD” 的源文件,该文件用于描述在GAL20V8内部实现的逻辑功能。

此为文本文件,但格式应符合相应编译软件的要求,也可以用ABEL 语言编辑扩展名为“.ABL”的源文件,只是要有相应的编译软件完成编译才能使用。

2.用相应的软件对已设计的源文件进行编译,以生成GAL20V8的熔丝图文件,扩展名为“.JED”。

3.用编程设备向GAL20V8器件内写入熔丝图文件所规定的内容,即对GAL20V8进行编程。

由于不同厂商提供的编程软件和编程设备有所不同,具体操作细节请阅读有关设备的使用手册。

常用集成块IC引脚功能

常用集成块IC引脚功能#标题#:立体声放音电路TA8105F立体声放音电路TA8105F各脚功能:1前置地,2前置放大器A正相输入,3前置放大器A反相输入,4前置放大器A负反馈,5前置放大器A输出,6反相LED显示,7M/N(金属磁带/普通磁带)转换,8功放A输入,9辐射抑制,10功放A输出,11功放地,12纹波抑制,13电源电压Vcc,14正相/反相转换,15功放B输出,16辐射抑制,17功放B输入,18外接电容,19正相LED显示,20前置放大器B输出,21前置放大器B负反馈,22前置放大器B反相输入,23前置放大器B正相输入,24基准电压.可用其同样封装结构的改进型TA8115N来直接代换.#标题#:驱动电路BA5209驱动电路BA5209各脚功能:1地,2反向驱动电压输出,3旁路,4伺服控制电压,5正向指令输入,6反向指令输入,7电源电压Vcc,8电压,9旁路,10正向驱动电压输出.可用极常用的驱动电路BA6209来直接代换.#标题#:CMOS型D/A转换器VCD用集成电路KDA0316集成电路KDA0316各脚功能:1左声道模拟音频信号输出,2基准高电压A+5V,3基准高电压B,4+5V电压,5字符时钟2输入,6左,右声道分离时钟输入,7字符时钟1输入,8音频串行数据输入,9位时钟输入,10+5V电压输入,11测试电路输出,12测试端1,13测试端2,14选择输出,15地,16低电平参考电压0V,17地,18空,19空,20右声道模拟音频信号输出.可用相同封装结构的LC7881或者CXD1161来直接代换.#标题#:带自动录音电平控制(ALC)的双均衡放大器BA3308集成电路BA3308各脚功能:1负反馈,2输入A,3输出A,4地,5自动电平控制,6电源Vcc,7输出B,8输入B,9负反馈B.可用KA22241来直接代换.#标题#:彩电中放集成电路MC1352P集成电路MC1352P各脚功能:1图像中频输入,2图像中频输入,3地,4地,5键控脉冲输入,6中放AGC输入,7图像中频输出,8图像中频输出,9高放AGC电压输出,10中放AGC调节,11电源Vcc,12高放AGC电压输出,13高放AGC延迟调节,14中放AGC滤波.可用LA1352,M5183来直接代换.#标题#:行,场扫描集成电路KA2133集成电路KA2133各脚功能:1场同步脉冲输入,2外接场振荡电容,3场振荡放电,4场电源电压,5外接升压电容负极,6场反馈,7外接升压电容正极,8场输出,9行激励输出,10行稳压器,11场脉宽消隐调节,12行振荡输入,13AFC输出,14AFC输入,15同步分离输入,16场同步脉冲输出.可用UPC1379来直接代换.#标题#:彩电电源厚膜集成电路STK7310集成电路STK7310各脚功能:1误差检测输入,2误差检测管基极,3反馈信号输入,4误差检测电压输入,5放大管偏置,6激励级输入,7激励级退耦,8保护输入,9限流输入,10电源调整管基极,11电源调整管发射极,12电源调整管集电极.可用IX0308CE/STK7308来直接代换.#标题#:稳速集成电路LA4512集成电路LA4512各脚功能:1电源电压Vcc,2地,3输出,4电压调节.可用LA5511/LA5512/5G5511来直接代换.#标题#:七重达林顿阵列驱动集成电路ULN2003A集成电路ULN2003A各脚功能:1~7脚分别是1~7路输入,16~10分别是1~7路输出,8接地,9接电源正极.可用MC1413P/UPA2003C/TD62003AP直接代换.#标题#:低压直流电机驱动集成电路KIA6901P集成电路KIA6901P各脚功能:1空,2空,3电源,4外接直流电机,5地,6基准电压端,7空,8电机速度调整.可用LA5521D/KA2402直接代换.#标题#:FM立体声解码集成电路AN7421集成电路AN7421各脚功能:1FM立体声复合信号输入,2外接低通滤波器1,3Vcc,4压控振荡器,5接地,6外接立体声指示灯,7接低通滤波器2,8L声道输出,9R声道输出.可用TA7342P/KA2264/D7342P直接代换.#标题#:双电压比较器集成电路HA17393集成电路HA17393各脚功能:1输出1,2反相输入1,3同相输入1,4地,5同相输入2,6反相输入2,7输出2,8电源电压Vcc.可用相同封装的LM393N/LM393P/AN1393/UPC393C等直接代换.#标题#:音频功率放大器集成电路TBA820集成电路TBA820是音频功率放大器,有14脚的TBA820L和8脚的TBA820M,常常将TBA820L称为TBA820.TBA820L的引脚功能是:1自举,2旁路,3空,4补偿1,5负反馈,6空,7输入,8接衬底地,9空,10功放地,11空,12输出,13补偿2,14Vcc,TBA820L可用CD820/D820/ECG1113等直接代换.TBA820M的引脚功能是:1补偿,2负反馈,3输入,4接地,5输出,6电源Vcc,7自举,8滤波.TBA820M可用CD820M/D820M/KA2201直接代换.#标题#:带ALC功能的双前置录放集成电路C1313HA集成电路C1313HA(UPC1313HA)各脚功能:1负反馈1,2输入1,3输出1,4ALC,5接地,6Vcc,7输出2,8输入2,9负反馈2.可用D1313HA直接代换.#标题#:音频功率放大器集成电路TA7209集成电路TA7209各脚功能:1旁路,2频率补偿,3自举,4旁路,5负反馈,6旁路,7功放输入,8空,9空,10地,11空,12功放输出,13空,14电源电压Vcc.可用D7209P/TA7209AP/ECG1222直接代换.#标题#:音频功率放大器集成电路KA386集成电路KA386各脚功能:1增益设定,2反馈输入,3正相输入,4地,5输出,6Vcc,7接旁路电容,8增益设定.可用相同封装的LM386/NJM386直接代换.#标题#:电机稳速集成电路KA2407集成电路KA2407各脚功能:1电源电压Vcc,2控制,3地,4稳压输出.可用UPC1470来直接代换.#标题#:彩电中放集成电路IX0062CE集成电路IX0062CE各脚功能:1噪声检波,2视频输出,3图像缓冲放大输入,4空,5外接去耦电容,6图像中放信号输入,7图像中放信号输入,8外接去耦电容,9外接电容,10高放AGC放大输入,11高放AGC放大输入,12高放AGC输出,13地,14外接4.5MHZ陷波器,15外接4.5MHZ陷波器,16外接图像载频线圈,17外接图像载频线圈,18AFT图像中频输入,19电源Vcc,20图像输出,21外接阻容元件,22AGC检波输出.可用HA11238直接代换.#标题#:SHARP夏普C-1837D型彩色电视机电原理图主要集成块:IX0388CE、IX0365CEZZ、IX0308CEZZ、IX0304CEZZ、IX0238CEZZ #标题#:彩电伴音集成电路M5144P集成电路M5144P各脚功能:1伴音中频输入,2伴音中频输入,3地,4空脚,5电源,6音量控制,7去加重,8检波信号输出,9调频检波变压器,10调频检波变压器,11空脚,12伴音输出,13音质调节,14伴音信号输入.#标题#:彩电图像中频信号处理集成电路M5186P集成电路M5186P各脚功能:1图像中放输入,2图像中放输入,3地,4高频AGC(反向),5高频AGC(正向),6AFT转换信号输入,7AFT输出,8AFT线圈,9图像检波线圈,10图像检波线圈,11AFT线圈,12伴音中频检波器滤波电路,13伴音中频检波器输出,14图像放大器输出,15图像检波器输入,16电源,17图像中放输出,18图像中放输出,19中频AGC控制电压,20中频AGC放大器输入,21AGC滤波电路,22高频AGC控制电压.#标题#:彩电PAL制式彩色电视信号处理和解调集成电路M5194P集成电路M5194P各脚功能:1地,2色饱和度控制,3色同步选通脉冲输入,4APC 滤波电路,5APC滤波电路,6晶体振荡器,7晶体振荡器,8双稳电路激励脉冲输入,9色度副载波输出,10R-Y色副载波输入,11B-Y色副载波输入,12G-Y输出,13R-Y输出,14B-Y输出,15电源,16R-Y色信号输入,17B-Y色信号输入,18色信号输出,19色滤波电路,20ACC滤波电路,21旁路电路,22彩色信号输入.#标题#:彩电图像信号处理和同步分离集成电路M5195P集成电路M5195P各脚功能:1图像信号输入,2同频滤波电路,3同步保持,4同步转换,5同步输出,6电源,7地,8图像信号输出,9消隐输入,10直流箝位调整,11亮度调节,12黑电平调节,13对比度调节,14信号提升电路2,15画质调节,16信号提升电路1.#标题#:彩电PAL制式彩色同步解码电路TBA520集成电路TBA520各脚功能:1识别信号输入,2R-Y参考信号输入,3PAL开关输出,4R-Y输出,5G-Y输出,6电源,7B-Y输出,8B-Y参考信号输入,9B-Y彩色信号输入,10测试点,11G-Y直流电平调节,12R-Y直流电平调节,13R-Y彩色信号输入,14行脉冲输入(正),15行脉冲输入(负),16地.#标题#:彩电彩色矩阵预放大集成电路TBA530集成电路TBA530各脚功能:1B信号输出负载电阻,2-(B-Y)信号输入,3-(G-Y)信号输入,4-(R-Y)信号输入,5亮度信号输入,6地,7电流馈入点,8电源,9R通道反馈,10R信号输出,11R信号输出负载电阻,12G通道反馈,13G信号输出,14G信号输出负载电阻,15B通道反馈,16B信号输出.#标题#:彩电色处理集成电路TBA540集成电路TBA540各脚功能:1振荡器反馈输入,2频率控制反馈,3电源,4参考副载波输出,5色同步脉冲输入,6参考副载波输入,7消色器输出,8PAL双稳电路脉冲输入,9ACC输出,10ACC电平调节,11ACC增益调节,12ACC电平调节,13振荡器相位控制环的直流控制端点,14振荡器相位控制环的直流控制端点,15振荡器反馈,16地#标题#:彩电亮度色度处理及控制集成电路TBA560C集成电路TBA560C各脚功能:1平衡彩色信号输入,2直流对比度控制,3亮度信号输入,4黑电平箝位电容器,5亮度信号输出,6亮度控制,7色同步脉冲输出,8回扫消隐输入,9色信号输出,10色同步脉冲选通和箝位脉冲输入,11电源,12色通道直流反馈,13彩色饱和度控制,14ACC输入,15平衡彩色信号输入,16地#标题#:彩电中频放大集成电路TBA970集成电路TBA970各脚功能:1视频信号输出,2电源,3视频信号输入,4三极管集电极,5三极管基极,6三极管发射极,7对比度控制,8电子束电流反馈输入,9电子束电流控制,10行同步脉冲输入1,11行同步脉冲输入2,12亮度控制,13黑电平记忆,14去耦,15黑电平反馈输入,16地#标题#:彩电彩色解调集成电路TBA990集成电路TBA990各脚功能:1识别信号输入,2R-Y副载波参考信号输入,37.8KHz信号输出,4R-Y信号输出,5G-Y信号输出,6电源,7B-Y信号输出,8B-Y 副载波参考信号输入,9B-Y直流电平调节,10B-Y色信号输入,11G-Y直流电平调节,12R-Y直流电平调节,13R-Y色信号输入,14行脉冲输入(双稳电路同步),15空脚,16地#标题#:彩电色处理集成电路TDA2522集成电路TDA2522各脚功能:1B-Y输出,2G-Y输出,3R-Y输出,4地,5B-Y彩色输入,6R-Y彩色输入,7振荡器环路滤波器,8振荡器环路滤波器,9振荡器反馈,10振荡器反馈,11电源,12ACC输出,13ACC电容,14ACC电容,15色同步选通和消隐脉冲,16消色器延迟电容#标题#:彩电亮度及色度处理集成电路TDA2560集成电路TDA2560各脚功能:1彩色信号输入端1,2彩色信号输入端2,3ACC输入,4彩色饱和度控制,5地,6色信号/色同步脉冲输出,7色同步选通和消隐脉冲,8电源,9回扫消隐,10亮度信号输出(-同步),11亮度控制,12黑电平箝位,13亮度通道增益控制,14亮度信号输入,15亮度信号输出(+同步),16直流对比度控制.#标题#:彩电行振荡集成电路TDA2590集成电路TDA2590各脚功能:1电源,2行扫触发电路,3行报触发电路,4脉冲宽度转换,5相位比较1,6行回扫,7色同步脉冲/消隐,8场同步脉冲,9视频信号输入,10噪声分离电路,11VCR(录相?)开关,12时间常数转换,13相位比较2,14振荡器,15振荡器,16地#标题#:双运算放大器集成电路OP249集成电路OP249各脚功能:1输出1,2负输入1,3正输入1,4地,5正输入2,6负输入2,7输出2,8电源.可用OP215,TL072,AD712直接代换#标题#:音频功率放大集成电路ECG1380集成电路ECG1380各脚功能:1输入,2负反馈,3地,4输出,5电源Vcc.可用TDA2030直接代换#标题#:VCD聚焦伺服电路TA002可用MN662743直接代换#标题#:音频数字处理与D/A轮换集成电路ES3887可用ES3207直接代换#标题#:1W的单声道功放集成电路D2283B集成电路D2283B各脚功能:1去耦,2地,3地,4输出,5电源电压,6地,7地,8输入.可用ULN2283B直接代换#标题#:收录机前置放大集成电路BA3406AL集成电路BA3406AL各脚功能:1输出L-1,2输出L-2,3负反馈L,4金属带L,5输入L,6静噪L,7电源电压,8静音控制,9地,10金属带控制,11输入R,12静噪R,13负反馈R,14金属带R,15输出R-1,16输出R-2.#标题#:三位二/十进制编码计数器集成电路MC14553B可用CD4553B,D4553直接代换#标题#:电话机中振铃集成电路TA31001P集成电路TA31001P各脚功能:1电源电压,2振铃触发输入,3外接超低频振荡电容,4外接超低频振荡电阻,5地,6外接音频振荡电阻,7外接音频振荡电容,8振铃信号输出.可用CSC8204或CSC31001直接代换#标题#:双运算放大器集成电路MCN34082集成电路MCN34082各脚功能:1运放A输出,2运放A反相输入,3运放A同相输入,4接电源负极,5运放B同相输入,6运放B反相输入,7运放B输出,8接电源正极.可用TL072,AD712,LT1057直接代换#标题#:电子频道选台集成电路CN5010可用AN5050或UPC1360直接代换#标题#:新三端+5V稳压器MIC29150集成电路MIC29150各脚功能:1输入,2地,3输出#标题#:音频功放电路DBL1069集成电路DBL1069可用TA8210H直接代换#标题#:调频/调幅中频放大集成电路CIA7078集成电路CIA7078各脚功能:1调幅本振回路,2调频中放输入,3前级地,4第一级调频中放输出,5第二级调频中放输入,6电源VCC1,7调频中放输出,8外接调频旁路电容,9后级地,10外接调幅旁路电容,11调幅中放输出,12电源VCC2,13调频AGC输入,14调幅中放输入,15调幅变频输出,16调幅变频输入.可用UPC1018直接代换.#标题#:五段图示均衡放大器D7796集成电路D7796各脚功能:1,3,5,7,9分别是1~5个谐振电路的基极输入端,2,4,6,8,10分别是1~5五个谐振电路的负反馈端,11缓冲放大器输入端,12缓冲放大器负反馈端,13缓冲放大器输出,14电源电压,15偏置电压,16接地.可用LA3600,M5226,TA7796直接代换.#标题#:双路电压比较集成电路BA10393集成电路BA10393各脚功能:1输出1,2反相输入1,3正相输入1,4单电源供电时为接地端,双电源供电时为负电源电压端,5正向输入2,6反向输入2,7输出2,8正电源电压端.可用相同封装的LM393,NJM2903(1)直接代换.#标题#:三路单刀双掷双向模拟电子开关HD14053BP集成电路HD14053BP可直接用HD4053,MC14053B,CD4053B,C4053B,BU4053B,HEF4053B代换.#标题#:音频振铃集成电路ML4003集成电路ML4003各脚功能:1接电源正极VCC,2振铃触发,3外接超低频振荡电容,4外接超低频振荡电阻,5接地,6外接音频振荡电阻,7外接音频振荡电容,8振铃信号输出.可用CIC8204,CS8204,CSC8204,CD8204,MC8204,TA31001P直接代换.#标题#:双电压比较集成电路NJM2903S集成电路NJM2903S各脚功能:1VCC,2输出1,3反相输入1,4正相输入1,5地,6正向输入2,7反向输入2,8输出2,9VCC.可用相同封装的LM2903S,LA6393S直接代换.#标题#:放音双前置放大电路BA3304集成电路BA3304各脚功能:1L(左声道)输入,2空,3电源VCC,4偏置,5地,6空,7空,8R(右声道)输入,9R负反馈,10R输出,11空,12空,13空,14空,15L输出,16L负反馈#标题#:音响功放集成电路TDA2615音响功放集成电路TDA2615各脚功能:1输入A,2控制,3地,4输出A,5接电源正极,6输出B,7接电源负极,8地,9输入B.可用TDA2616直接代换.#标题#:伴音集成电路LA1363伴音集成电路LA1363各脚功能:1中频输入,2中频输入,3地,4地,5电源VCC,6音量控制,7去加重,8鉴频输出,9外接鉴频调谐回路,10外接鉴频调谐回路,11空,12音频输出,13音量控制,14激励放大输入.可用LA1365或AH1124直接代换.#标题#:彩电亮度控制及信号处理集成电路AN380彩电亮度控制及信号处理集成电路AN380可用UPC1380直接代换.。

TEC-2000G教学计算机系统技术说明_16位机实验指导

; 输入用到的子程序到内存 2100 开始的存储区 ;输出保存在 R0 寄存器中的字符

;将保存在 R0 中的大写字母转换为小写字母 ;写 R0 中的字符到内存,地址同 LDRR 所用的地址 ;测试串行接口是否完成输出过程

;未完成输出过程则循环测试 ;结束子程序执行过程,返回主程序

运行过程中,可以直接看到屏幕上显示的内容,运行过后, 再用 D 20F0 命令看内存的 20F0 区 域中保存的运行结果:

压 START 前

运算

I8-I0 SST SCi SSH A

B ALU CZVS

输出

*D1+0->R0

011000111 001 00 00 不;0->R1

011000111 001 00 00 不用 0001

R0+R1->R0

011000001 001 00 00 0001 0000

压 START 后 ALU CZVS 输出

实验要求

1. 实验之前认真预习,写出预习报告,包括操作步骤,实验过程所用数据和运行结果等,否则实 验效率会很低,所学到的内容也会大受影响;

2. 实验过程当中,要仔细进行,防止损坏设备,分析可能遇到的各种现象,判断结果是否正确, 记录运行结果;

3. 实验之后,认真写出实验报告,包括对遇到的各种现象的分析,实验步骤和实验结果,自己在 这次实验的心得体会与收获。

经设计好并正常运行的各类指令的功能、格式和执行流程,也包括控制器设计与实现中的具体线 路和控制信号的组成。扩展指令的参考设计方案,已在第二章中给出。 5. 要明确自己要实现的指令格式、功能、执行流程设计中必须遵从的约束条件。 为了完成自己设计几条指令的的功能、格式和执行流程,并在教学计算机上实现、调试正确的实 验内容,具体过程包括: 1) 确定指令格式和功能,要受教学机已有硬件的约束,应尽量与已实现指令的格式和分类办法 保持一致; 2) 划分指令执行步骤并设计每一步的执行功能,设计节拍状态的取值,应参照已实现指令的处 理办法来完成,特别要注意的是,读取指令的节拍只能用原来已实现的,其他节拍的节拍状态也应 尽可能地与原用节拍的状态保持一致和相近; 3) 在指令流程表中填写每一个控制信号的状态值,基本上是个查表填数的过程,应该特别仔细, 并有意识地体会这些信号的控制作用; 4) 写出每个控制信号的完整逻辑表达式,可能和必要的话,进行一点逻辑化简; 5) 把这些控制信号,按教学计算机设计中规定的几个 GAL20V8 的引脚分配结果编程到相应的 GAL20V8 芯片中去; 6) 写一个包含你设计的指令的程序,通过运行该程序检查执行结果的正确性,来初步判断你的 设计是否正确;如果有问题,通过几种办法查出错误并改正,继续调试,直到完全正确。

大型游戏机电脑板原理及维修

各种IC的彩色故障,最终都要在彩色6116的地址线和数据线上反映出来,唯一的方法是靠辨认各点上的波形,关键点是要区分是系统SRAM本身,还是地址线不对,这时候要当机立断。如方便的话,可替换SRAM1616,如替换无效,则要对每根地址线,数据线确认、观察。

(2)彩色电路故障的检查方法

图9是电脑板彩色处理部分的电路框图。

电脑板形成的背景I、背景II、背景III及前景的图像信号通过优先权电路,将前景优先权级高、依次最后一层背景优先权级最低,这样使前景人物出现挡住相应背景,这部分电路由PLD器件和锁存器74LS374或74LS373等组成,此部分电路产生故障将使画面层次无序。通过优先权电路输出的信号经过彩色编码电路2×6116处理后送到触发器74LS174。74LS174的输出经过色码加权排阻由公共端输出红、绿、蓝三基色视频信号到I/O口,直接送入显示器。游戏画面的色彩失真,混乱或缺少一种彩色,一种简单的方法是从28插排上找红、绿、蓝三根线(元件面○12线,○13蓝,焊接面○12绿每根线都连接着一个排阻的公共端,另外端连接在集成块上。一般这个集成块是74LS273,74LS367或74LS174等。

确定背景SRAM后,余下的是靠辨认其各点上的波形。

两片62256的○26脚为地址线,电路上采用并联连接,○26脚波形异常,幅度在中态范围。

查到异常,余下的关键工作要区分是SRAM本身故障,还是外围电路故障引起波形畸变。62256采用的是有插座按装方式,将两片62256替换后故障依旧,此地址信号来自U42一片74LS257的第○7脚,74LS257是一枚三态输出四2选1数据选择器,利用公共的"数据选择"端S从两个数据源中选择一个4位数据,所选择的数据由个输出端输出,○7脚为一数据输出端,测IC板发现,○15脚允许端E0低电平,允许数据输出,选择端○1脚S端为高电平,选择○6脚为输入信号,此时IC的○7脚波形应与○6脚基本一致,但○6脚输入信号正常,○7脚输出异常,判断74LS257坏,更换后图像恢复正常。

大型游艺机维修,主板

大型游戏机原理与维修-------操作故障的维修十四、操作故障的维修在电脑板中,操作故障最容易排除。

它主要体现在投币不响应,操作死机,操作失灵等等,主要表现为缺拳少腿等。

操作故障的排除方法首先从28插排上找到控制上、下、左、右动作投币等控制线。

沿着这根线找到与这根线相连的集成块或与这个集成块相连的片子。

一般就是它们出了问题,这些集成声的型号是74LS245、74LS273、74LS244、74LS258、74LS367等。

[例67]板型:通用板故障现象:左右控制失灵检查与修理:操作的实现是开关K控制相应的功能,通过74LS245总线发送接收器,将操作信息送至68000CPU的数据总线。

操作开关处于常开状态,排阻为上拉电阻保持各操作点为高电平。

按下开关,相应的74LS245B侧的某位阶跃为低电平0V。

DR为数据传送方向控制输入端。

DR端高电平数据是从A传送至B,DR低电平数据从B侧传送到A侧,此电路只用于将B侧操作信息送至总线A侧,所以DR端接地。

E端为高电平时数据与总线隔离。

28插元件面的17脚对应1P开始,18上,19下,20左,21右,22、23、24各脚分别对应1P的三个动作开关。

2P的排列与1P相同,对应位置在板的焊接面。

正常状态下,各脚的电平应为+5V,测其为中态偏高电平。

排阻正常,判74LS245坏。

[例68]板型:标准板故障现象:按"开始"键死机检查与修理:按"开始"开关对应17线,连至74LS245,此74LS245内部短路至使按键后出现短路造成CPU总线粘连产生死机。

这种故障还产生于投币及操作其它功能键时产生。

[例69]板型:标准板故障现象:开机演练正常,但不能操作检查与修理:查主1P接在一片74LS245上。

操作开关时,B侧变为低电平,A侧无反应。

查245DR端低电平正常。

其E端为高电平,使数据与总线隔离,该例故障为操作信息不能送至CPU,E端信号来自1#GAL20V8,将其更换后故障排除。

3 通用寄存器单元实验

通用寄存器单元实验一、实验目的1、了解通用寄存器的组成和硬件电路2、利用通用寄存器实现数据的置数、左移、右移等功能二、实验要求按照实验步骤完成实验项目,实现通用寄存器移位操作。

了解通用寄存器单元的工作原理运用。

三、实验说明图2-2-11.寄存器实验构成(如图2-2-1)1、通用寄存器由2片GAL构成8位字长的寄存器单元。

8芯插座RA-IN作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。

GAL:是一种可电擦除、可重复编程、可加密的可编程逻辑器件(PLD)。

目前普遍采用的芯片有两种:GAL16V8(20引脚)和GAL20V8(24引脚),这两种GAL能够按设计者自己的要求构成各种功能的逻辑电路,在研制开发新的电路系统时,极为方便。

2、数据输出由一片74LS244(输出缓冲器)来控制。

用8芯插座RA-OUT作为数据输出端,可通过短8芯扁平电缆,把数据输出端连接到数据总线。

3、判零和进位电路由1片GAL、1片74LS74和一些常规芯片组成,用2个LED(ZD、CY)发光管分别显示其状态。

2.控制信号说明3.通用寄存器单元的工作原理通用寄存器单元的核心部件为2片GAL,它具有锁存、左移、右移、保存等功能。

通过设置X0、X1来指定通用寄存器工作方式。

例如,当置ERA=0、X0=1、X1=1,RACK有上升沿时,把总线上的数据打入通用寄存器。

通用寄存器的输出端Q0~Q7接入判零电路。

LED(ZD)亮时,表示当前通用寄存器内数据为0。

输出缓冲器采用74LS244,当控制信号RA-O为低时,74LS244开通,把通用寄存器内容输出到总线;当RA-O为高时,74LS244的输出为高阻。

4.实验步骤实验1、数据输入通用寄存器●RA-IN 二进制开关单元中的J01插座(H16~H23)RA-OUT DJ6●RACK PLS1●ERA、X0、X1、RA-O、M接入二进制拨动开关。

●二进制开关H16~H23作为数据输入,置42H。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

至相邻 宏单元

OMUX AC0 AC1(n) D Q XOR(n) CLK Q FMUX

11 0× 10

10 11 0×

设计规则: 资源: 使用:

AC1(n) 来自相邻引脚 *AC0 同步时序设计(无异步清零);

状态方程最大与项数为8 1脚--CLK, 13脚--OE(接地)

ABEL-HDL

1. ABEL-HDL时序语言基本元素 2. 设计举例

状态转移描述

状ቤተ መጻሕፍቲ ባይዱ机描述语句 • 格式 State_diagram STATE 状态N:

(状态变量) 方程; 方程 … 转移语句;

• 转移语句 – goto – if then else – case

GOTO

转移语句

state A: Z1=1; Z2=0; goto B

IF-THEN-ELSE

转移语句

state

计数 译码结构

B、 用状态机结构

MODULE ex4s CLK PIN; L3..L0 PIN ISTYPE'REG'; C,X=.C.,.X.; S=[L3..L0]; S1=^B0001; S2=^B0010; S3=^B0100; S4=^B1000; S0=^B1111;//上电状态

状态编码定义

I: I/O:

专用输入 I、O、I/O

时序工作时: 1脚——CLK 13脚——OE(低有 效) 最大8路输出; 最多20路输入

GAL20V8/ZD

时钟信 号输入 输入/输出口

输入口

GAL结构 (16V8)

三态 控制

GAL输出宏单元结构

PTMUX OE VCC TSMUX

11 0× 10

11 10 00 01

EQUATIONS S.CLK=CLK;

时钟方程

STATE_DIAGRAM (S) STATE S0: GOTO S1 ; STATE S1: GOTO S2 ; STATE S2: GOTO S3 ; STATE S3: GOTO S4 ; STATE S4: GOTO S1 ; TEST_VECTORS (CLK->S) @REPEAT 20{C->X;} END

A: if

X==1 then else C

B

注:可使用链接式或嵌套式

条件语句使用的位置

State_diagram (s)

state

A: if X then B else C with Z=1; endwith

out=d0 else out=d1;

EQUATIONS when (sel==0) then

ABEL-HDL语言基本元素

1.逻辑电路的基本元素

– 逻辑量 – 逻辑运算 – 逻辑器件

2.逻辑电路的功能描述

– 逻辑方程 – 真值表 – 状态图

ABEL-HDL基本元素

寄存器的点后缀表

.CLK . SP .SR .AP .AR .FB .OE .Q …… 边沿触发器的时钟输入 同步置1 同步置0 异步置1 异步置0 寄存器反馈信号 输出允许 寄存器输出

数字电子技术实验A可编程实 验(必做内容)

内容:第四章可编程器件实验 实验一~实验八 自选三个:设计Æ通电测试 时间:第十一周至第十三周开放时间(自主预 约) 地点: X6303

GAL20V8引脚分布

I/CLK I I I I I I I I I I GND 1 2 3 4 5 6 7 8 9 10 11 12 24 23 22 21 20 19 18 17 16 15 14 13 VCC I I/O I/O I/O I/O I/O I/O I/O I/O I I/OE

Q.CLK=CP;

Q:=Q.FB+1;

逻辑方程描述语句

•用关键字EQUATIONS开始. •按上述语法规则书写逻辑方程。在ABEL-HDL中,每个方 程相应于文件的一行,且对每一行的书写有如下规定: (1)每行的长度不得超过150个字符。 (2)每行用“;”号结尾。 例: S=[Q3..Q0]; EQUATIONS Q.CLK=CP; Q:=!Q; then S:=S.fb+1 Else S:=0; S.CLK=CLK; when (S < 9)

源文件格式

ABEL源文件由1个或多个相互独立的模 块组成,每个模块又由多个完成各自功能的 部分组成,一个模块的ABEL源文件典型结 标题段: MODULE example 构:

TITLE a BCD_counter (可选) 定义段: 信号定义、常量定义、数组定义、…… 逻辑描述段: 逻辑方程(EQUATIONS) 真值表(TRUTH_TABLE) 状态图( STATE_DIAGRAM) 测试向量段: TEST_ VECTORS 结束段: END

时序逻辑电路设计举例

用一片GAL20V8实现: 数字电路实验四: 广告流水灯 A、 用计数译码结构 B、 用状态机结构 C、 用真值表结构

MODULE ex4 CLK PIN; Q1,Q0 PIN ISTYPE'REG'; L3..L0 PIN ISTYPE'COM'; C,X=.C.,.X.; S=[Q1,Q0]; EQUATIONS S.CLK=CLK; S:=S-1; L3=Q1&Q0; L2=Q1&!Q0; L1=!Q1&Q0; L0=!Q1&!Q0; TEST_VECTORS (CLK->[S,L3,L2,L1,L0]) @REPEAT 20{C->X;} END

真值表描述语句 • 关键字truth_table • 描述组合逻辑电路 ([A,B,C]->[ F1,F2,F3]) --表头 [0,0,0]->[ 1, 0, 0]; ... • 描述时序逻辑电路的状态转换真值表 ([Q2,Q1,Q0]:>[ Q2,Q1,Q0]) [0, 0, 0]:>[ 0, 0, 1]; ... [1, 1, 1]:>[ 0, 0, 1]; • 混合 输入数组:> 寄存器输出 -> 组合逻辑输出