NJU8754中文资料

低抖动的串行/解串器芯片组

AT一 (P2 AWG屏蔽 电缆 )的数据 6 R 3 1C接 1 ,能够支持 高达 1 0 / 的通 成 的器件 中包含 了 3个 I 2 7 1 0 Kb s C的功 能( 时钟 C 信速 率。 0 和 数据恢复 、串行器和 解串器) 可 显著 传输范 围延 长至 2 m以上 ,也可支持多 ,

记录仪

闪存 和基于 PL

可用于 不同的工业 、科学和 医疗 (S 时 ,仍 然 能够 提 供 极佳 的 抖 动容 差特 I M)

基于 F—RAM 的事 件数 据记录 仪 频 段 :3 5 1 MHz 3 M Hz 6 MHz 、4 4 、8 8 和 性 ,以 支持 前向纠错 。另外 ,上行速率 (D E R)F 4 M6 是集 成式的事件 监控 解 1 2 决方案 ,能够连续 监控状态 的变化 ,将

Mi r c i Te h o o y co hp c n lg

消费 产品 ,超越 了红外线通信 方式的许 设备制造 商的成本和 功耗 。该器件适 合

多限 制。

PM A 7 0 15

用于 Veio i S等 F TH装置 中的 rz n F O T

光 网络 终 端 。

M AX3 8 8 6采 用 专 有 的 C DR 技 术 ,

91 M HZ 5 。

可以配置为与下行速率相等( 对称工作方

或 非 只需 少 量 组 件 , MA7 5 可 实 现 式 ) 下行 频 率 的 因数( 对 称工 作方 P 就 1 0

。 数据存 储在F RAM中并向 系统 提出有 家居 自动化 系统 、安 防和 报警 系统 、音 式 ) —

可 激 活 事 件 的 时 间 戳 ,并 作 为 系 统 的 时

钟 和 日历 。

电路图集

D

VDD IN COM MUTE STBY

VSS OUTP VDDO OUTN VSS

10 9 8 7 6 C19 C22 104

L8 L9

22UH 22UH C23 105

SP2 8ohms SPEAKER

U3 NJU8754 SSOP10 A5V C25 104 10UF/16V 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25

10K

9 1N4148 11 7 6 5 1.5K

TL494 4 3 2 1

5.6K

VCC 20K 15K 910 B

B

150k 1/2w

2 330K/1/2W 4.7uF 50V

1

4

EI19 7 8 1N4148 1N4753 36v

100K 2

1N4148

FR105

NPN 2sc2625

2.4K

1

2

3

4

5

6

VDD5V USB1 1 2 3 4 L2 C1 101 C2 101 L1 C4 104 R1 22 R2 22 R3 10K R4 10K

USBDM C17 224 LOR C18 104 BUZZ USBDP

R13 4K7 1 2 3 4 5 R15 4K7 C21

VDD5V

R14 4K7

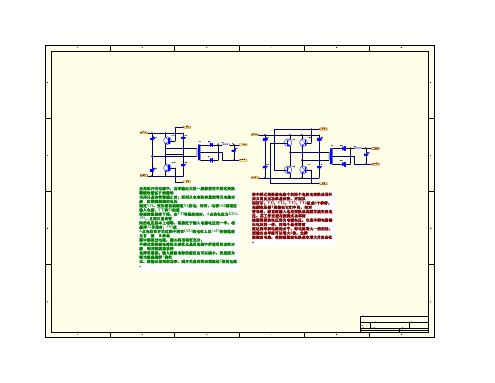

将半桥式变换器电路中的两个电解电容换成另外 两只高反压功率晶体管,并配以 图所示。 VTl、 VT2、 VT3、 VT4组成4个桥臂。 高频变压器T连接在它们中间。相对 替导通,将直流输入电压变换成高频方波交流电 压。其工作过程与推挽式功率转 线圈得到的电压即为电源电压。它是半桥电路输 出电压的一倍,而每个晶体管耐 流达到半桥电路的水平,即电流增大一倍的话, 则输出功率就可以增大 4倍。全桥 极驱动电路,使控制驱动电路成本增大并复杂化 。

湖大微机原理及其应用第6章

D7 D6 D计0 数器

D5

D4

读/写格式

D3

D2

工作方式

D1 数制

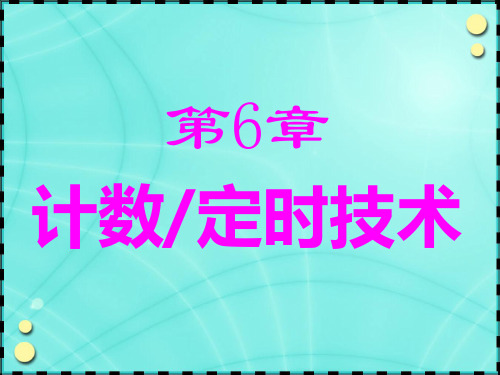

图6.4 8253控制字格式 注:图中×可以是0,也可以是1,一般取0

0 —二进制 1 —二― 十进制(BCD)

000 方式0 001 方式1

10 方式2 11 方式3

100 方式4 101 方式5 00 计数器锁存命令 10 只读/写高8位 01 只读/写低8位 11 首先写低8位

定时范围不易由程序来改变和控制,使用不甚

方便,而且定时精度也不高。

3.可编程的定时器

采用软、硬件相结合的方法,用可编程定时 计数器芯片(如Intel 8253),构成一个方便灵活 的定时计数电路;

这种电路不仅定时值和定时范围可用程序确 定和改变,而且具有多种工作方式,可以输出多 种控制信号;

由微处理器的时钟信号提供时间基准,故计 时也精确稳定。

④ A1A0: 端口选择信号, 当A1A0=00,01,10时表示分别选中计数器0,1,2 ; 当A1A0=11时选中控制寄存器。

(3)控制寄存器

• 接收从CPU来的控制字; • 并由控制字的D7、D6位的编码决定该控制字写

入哪个计数器的控制寄存器; • 控制寄存器只能写入,不能读出。

(4)计数器

8253具有较好的通用性和使用灵活性,几乎适合于任何一 种微处理器组成的系统。

2. 8253的内部结构

图6.1 8253的内部结构示意图

(1)数据总线缓冲器

8位、双向、三态的缓冲器,可直接挂在数据总线上。 CPU通过数据总线D0~D7传送如下信息:

① 向控制寄存器写入控制字; ② 向某计数器写入计数初值; ③ CPU读取某个计数器的当前计数值。

2N5484中文资料

**L2 **L3

6 turns, (approx. — depends upon circuit layout) AWG #24 enameled copper wire, close wound on 7/32″ ceramic coil form. Tuning provided by an aluminum slug. 1 turn, AWG #16 enameled copper wire, 3/8″ I.D. (AIR CORE). 1/2 turn, AWG #16 enameled copper wire, 1/4″ I.D. (AIR CORE).

POWER GAIN

24 f = 100 MHz

20 PG , POWER GAIN (dB)

16

12

400 MHz Tchannel = 25°C VDS = 15 Vdc VGS = 0 V 0 2.0 4.0 6.0 8.0 10 ID, DRAIN CURRENT (mA) 12 14

8.0 4.0

Figure 2. 100 MHz and 400 MHz Neutralized Test Circuit

NOISE FIGURE

(Tchannel = 25°C)

10 ID = 5.0 mA 8.0 NF, NOISE FIGURE (dB) NF, NOISE FIGURE (dB) 5.5 6.5 VDS = 15 V VGS = 0 V

1 2 3

CASE 29–04, STYLE 5 TO–92 (TO–226AA)

ELECTRICAL CHARACTERISTICS (TA = 25°C unless otherwise noted)

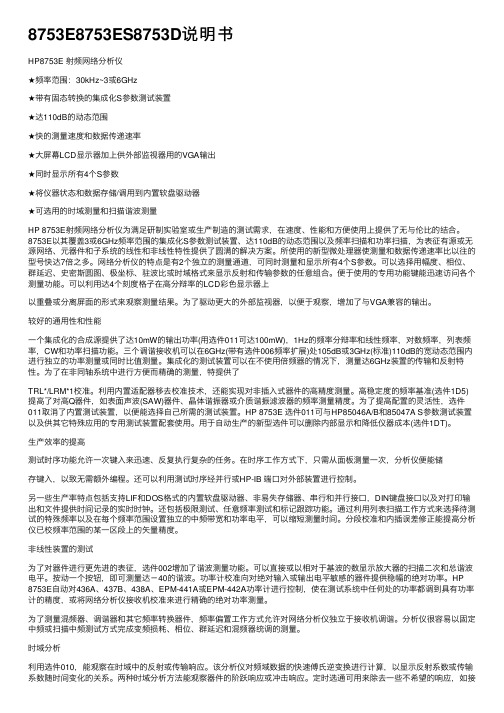

8753E8753ES8753D说明书

HP8753E 射频网络分析仪★频率范围:30kHz~3或6GHz★带有固态转换的集成化S参数测试装置★达110dB的动态范围★快的测量速度和数据传递速率★大屏幕LCD显示器加上供外部监视器用的VGA输出★同时显示所有4个S参数★将仪器状态和数据存储/调用到内置软盘驱动器★可选用的时域测量和扫描谐波测量HP 8753E射频网络分析仪为满足研制实验室或生产制造的测试需求,在速度、性能和方便使用上提供了无与伦比的结合。

8753E以其覆盖3或6GHz频率范围的集成化S参数测试装置、达110dB的动态范围以及频率扫描和功率扫描,为表征有源或无源网络、元器件和子系统的线性和非线性特性提供了圆满的解决方案。

所使用的新型微处理器使测量和数据传递速率比以往的型号快达7倍之多。

网络分析仪的特点是有2个独立的测量通道,可同时测量和显示所有4个S参数。

可以选择用幅度、相位、群延迟、史密斯圆图、极坐标、驻波比或时域格式来显示反射和传输参数的任意组合。

便于使用的专用功能键能迅速访问各个测量功能。

可以利用达4个刻度格子在高分辩率的LCD彩色显示器上以重叠或分离屏面的形式来观察测量结果。

为了驱动更大的外部监视器,以便于观察,增加了与VGA兼容的输出。

较好的通用性和性能一个集成化的合成源提供了达10mW的输出功率(用选件011可达100mW),1Hz的频率分辩率和线性频率,对数频率,列表频率,CW和功率扫描功能。

三个调谐接收机可以在6GHz(带有选件006频率扩展)处105dB或3GHz(标准)110dB的宽动态范围内进行独立的功率测量或同时比值测量。

集成化的测试装置可以在不使用倍频器的情况下,测量达6GHz装置的传输和反射特性。

为了在非同轴系统中进行方便而精确的测量,特提供了TRL*/LRM*1校准。

利用内置适配器移去校准技术,还能实现对非插入式器件的高精度测量。

高稳定度的频率基准(选件1D5)提高了对高Q器件,如表面声波(SAW)器件、晶体谐振器或介质谐振滤波器的频率测量精度。

LC875G24A中文资料

LC875G32A LC875G24A LC875G16A LC875G08AOverviewThe SANYO LC875G32A/24A/16A/08A are 8-bit microcomputer that, centered around a CPU running at a minimum bus cycle time of 100ns, integrates on a single chip a number of hardware features such as 32K/24K/16K/8K-byte ROM, 1024-byte RAM, sophisticated 16-bit timers/counters (may be divided into 8-bit timers), a 16-bit timer/counter (may be divided into 8-bit timers/counters or 8-bit PWMs), four 8-bit timers with a prescaler, a base timer serving as a time-of-day clock, a high-speed clock counter, a synchronous SIO interface (with automatic block transmission/receptioncapabilities), an asynchronous/synchronous SIO interface, a UART interface (full duplex), a 12-bit/8-bit 12-channel AD converter, two 12-bit PWM channels, a system clock frequency divider, and a 22-source 10-vector interrupt feature.FeaturesROM• 32768 × 8-bits (LC875G32A) • 24576 × 8-bits (LC875G24A) • 16384 × 8-bits (LC875G16A) • 8192 × 8-bits (LC875G08A)RAM• 1024 × 9-bits (LC875G32A/24A/16A/08A)Minimum Bus Cycle • 100ns (10MHz)Note : The bus cycle time here refers to the ROM read speed.Minimum Instruction Cycle Time • 300ns (10MHz)CMOS ICROM 32K/24K/16K/8K byte, RAM 1024 byte on-chip8-bit 1-chip MicrocontrollerPorts• Normal withstand voltage I/O portsPorts whose I/O direction can be designated in 1-bit units 30 (P1n,P2n,P30 to P36,P70 to P73,PWM0,PWM1,XT2) Ports whose I/O direction can be designated in 4-bit units 8 (P0n)• Normal withstand voltage input port 1 (XT1)• Dedicated oscillator ports 2 (CF1, CF2)• Reset pins 1 (RES)• Power pins 6 (V SS1 to 3, V DD1 to 3)Timers• Timer 0 : 16-bit timer/counter with a capture register.Mode 0 : 8-bit timer with an 8-bit programmable prescaler (with an 8-bit capture register) × 2-channelsMode 1 : 8-bit timer with an 8-bit programmable prescaler (with an 8-bit capture register) + 8-bit counter (with an 8-bit capture register)Mode 2 : 16-bit timer with an 8-bit programmable prescaler (with a 16-bit capture register)Mode 3 : 16-bit counter (with a 16-bit capture register)• Timer 1 : 16-bit timer/counter that supports PWM/toggle outputsMode 0 : 8-bit timer with an 8-bit prescaler (with toggle outputs) + with an 8-bit prescaler 8-bit timer/counter (with toggle outputs)Mode 1 : 8-bit PWM with an 8-bit prescaler × 2-channelsMode 2 : 16-bit timer/counter with an 8-bit prescaler (with toggle outputs)(toggle outputs also possible from the lower-order 8-bits)Mode 3 : 16-bit timer with an 8-bit prescaler (with toggle outputs)(the lower-order 8-bits can be used as PWM.)• Timer 4 : 8-bit timer with a 6-bit prescaler• Timer 5 : 8-bit timer with a 6-bit prescaler• Timer 6 : 8-bit timer with a 6-bit prescaler (with toggle outputs)• Timer 7 : 8-bit timer with a 6-bit prescaler (with toggle outputs)• Base timer1) The clock is selectable from the subclock (32.768kHz crystal oscillation), system clock, and timer 0 prescaleroutput.2) Interrupts programmable in 5 different time-schemesHigh-speed Clock Counter1) Can count clocks with a maximum clock rate of 20MHz (at a main clock of 10MHz).2) Can generate output real time.SIO• SIO 0 : 8-bit synchronous serial interface1) LSB first/MSB first mode selectable2) Built-in 8-bit baudrate generator (maximum transfer clock cycle4/3 tCYC)3) Automatic continuous data transmission (1 to 256 bits, specifiable in 1-bit units, suspension and resumptionof data transmission possible in 1 byte units)• SIO 1 : 8-bit asynchronous/synchronous serial interfaceMode 0 : Synchronous 8-bit serial I/O (2- or 3-wire configuration, 2 to 512 tCYC transfer clocks)Mode 1 : Asynchronous serial I/O (half-duplex, 8 data bits, 1 stop bit, 8 to 2048 tCYC baudrates)Mode 2 : Bus mode 1 (start bit, 8 data bits, 2 to 512 tCYC transfer clocks)Mode 3 : Bus mode 2 (start detect, 8 data bits, stop detect)UART• Full duplex• 7/8/9 bit data bits selectable• 1stop bit (2-bit in continuous data transmission)• Built-in baudrate generatorAD Converter : 12-bits/8-bits×12-channels• 12-bits/8-bits AD converter selectable• Automatic reference voltage generation controllablePWM : Multifrequency 12-bit PWM×2-channelsRemote Control Receiver Circuit (sharing pins with P73, INT3, and T0IN)• Noise rejection function (noise filter time constant selectable from 1 tCYC, 32 tCYC, and 128 tCYC)Watchdog Timer• External RC watchdog timer• Interrupt and reset signals selectableInterrupts• 22 sources, 10 vector addresses1) Provides three levels (low (L), high (H), and highest (X)) of multiplex interrupt control. Any interrupt requests ofthe level equal to or lower than the current interrupt are not accepted.2) When interrupt requests to two or more vector addresses occur at the same time, the interrupt of the highest leveltakes precedence over the other interrupts. For interrupts of the same level, the interrupt into the smallest vector address takes precedence.SourceNo. VectorAddress Level Interrupt1 00003H X or L INT02 0000BH X or L INT13 00013H H or L INT2/T0L/INT44 0001BH H or L INT3/INT5/base timer5 00023H H or L T0H6 0002BH H or L T1L/T1H7 00033H H or L SIO0/UART1 receive8 0003BH H or L SIO1/UART1 transmit9 00043H H or L ADC/T6/T710 0004BH H or L Port 0/T4/T5/PWM0, PWM1• Priority Level : X > H > L• Of interrupts of the same level, the one with the smallest vector address takes precedence.Subroutine Stack Levels : 512 levels (the stack is allocated in RAM.)High-speed Multiplication/Division Instructions• 16-bits×8-bits (5 tCYC execution time)• 24-bits×16-bits (12 tCYC execution time)• 16-bits÷8-bits (8 tCYC execution time)• 24-bits÷16-bits (12 tCYC execution time)Oscillation Circuits• RC oscillation circuit (internal) : For system clock• CF oscillation circuit : For system clock, with internal Rf• Crystal oscillation circuit : For low-speed system clock, with internal Rf• Frequency variable RC oscillation circuit (internal) : For system clockSystem Clock Divider Function• Can run on low current.• The minimum instruction cycle selectable from 300ns, 600ns, 1.2µs, 2.4µs, 4.8µs, 9.6µs, 19.2µs, 38.4µs, and 76.8µs (at a main clock rate of 10MHz).Standby Function• HALT mode : Halts instruction execution while allowing the peripheral circuits to continue operation.1) Oscillation is not halted automatically.2) Canceled by a system reset or occurrence of an interrupt.• HOLD mode : Suspends instruction execution and the operation of the peripheral circuits.1) The CF, RC, and crystal oscillators automatically stop operation.2) There are three ways of resetting the HOLD mode.(1) Setting the reset pin to the lower level.(2) Setting at least one of the INT0, INT1, INT2, INT4, and INT5 pins to the specified level.(3) Having an interrupt source established at port 0.• X'tal HOLD mode : Suspends instruction execution and the operation of the peripheral circuits except the base timer.1) The CF and RC oscillators automatically stop operation.2) The state of crystal oscillation established when the X'tal HOLD mode is entered is retained.3) There are four ways of resetting the X'tal HOLD mode.(1) Setting the reset pin to the low level.(2) Setting at least one of the INT0, INT1, INT2, INT4, and INT5 pins to the specified level.(3) Having an interrupt source established at port.(4) Having an interrupt source established in the base timer circuit.Package Form• SQFP48 : Lead-free type• QIP48E : Lead-free typeDevelopment Tools• Evaluation chip : LC87EV690• Emulator : EVA62S+ECB876600D+SUB875G00+POD48QFPICE-B877300+SUB875G00+POD48QFP• Onchip debugger : TCB87 TypeA+LC87F5G32ATypeB+LC87F5G32ATCB87Flash ROM Version• LC87F5G32APackage DimensionsPackage Dimensionsunit : mm unit : mmPin AssignmentSANYO: SQFP48 "Lead-free Type" SANYO: QIP48E "Lead-free Type"Top viewP 73/I N T 3/T 0I N R E S X T 1/A N 10X T 2/A N 11V S S 1C F 1C F 2V D D 1P 10/S O 0P 11/S I 0/S B 0P 12/S C K 0P 13/S O 1P 27/I N T 5/T 1I N P 26/I N T 5/T 1I N P 25/I N T 5/T 1I N P 24/I N T 5/T 1I N P 23/I N T 4/T 1I N P 22/I N T 4/T 1I N P 21/U R X /I N T 4/T 1I N P 20/U T X /I N T 4/T 1I N P 07/T 7O /A N 7 P 06/T 6O /A N 6 P 05/C K O /A N 5 P 04/A N 41 2 3 4 5 6 7 8 9 10 11 12363534333231302928272625P36P35V DD 3V SS 3P34P33P32P31P30P70/INT0/T0LCP/AN8P71/INT1/T0HCP/AN9P72/INT2/T0IN242322212019181716151413P03/AN3 P02/AN2 P01/AN1 P00/AN0 V SS 2 V DD 2 PWM0 PWM1P17/T1PWMH/BUZ P16/T1PWML P15/SCK1 P14/SI1/SB137 38 39 40 41 42 43 44 45 46 47 48LC875G32A/LC875G24A/ LC875G16A/ LC875G08ASQFP/QIP NAME1 P73/INT3/T0IN 25 P04/AN4P05/CKO/AN52 RES 26P06/T6O/AN63 XT1/AN10 274 XT2/AN11 28P07/T7O/AN7P20/UTX/INT4/T1IN1 29P21/URX/INT4/T1IN6 CF1 30P22/INT4/T1IN7 CF2 31P23/INT4/T1IN1 32P24/INT5/T1IN9 P10/SO0 3310 P11/SI0/SB0 34 P25/INT5/T1IN11 P12/SCK0 35 P26/INT5/T1INP27/INT5/T1IN12 P13/SO1 3613 P14/SI1/SB1 37 P3614 P15/SCK1 38 P3515 P16/T1PWML 39 V DD316 P17/T1PWMH/BUZ 40 V SS317 PWM1 41 P3418 PWM0 42 P33P322 432 44P3121 P00/AN0 45 P30P70/INT0/T0LCP/AN822 P01/AN1 4623 P02/AN2 47P71/INT1/T0HCP/AN924 P03/AN3 48 P72/INT2/T0INSystem Block DiagramPin DescriptionPin Name I/O DescriptionOptionV SS 1 V SS 2 V SS 3 -- Power supply pinNoV DD 1 V DD 2 V DD 3 -+ Power supply pinNoPort 0 P00 to P07I/O• 8-bit I/O port• I/O specifiable in 4-bit units• Pull-up resistors can be turned on and off in 4-bit units • HOLD reset input • Port 0 interrupt input • Shared pinsP05 : System clock output P06 : Timer 6 toggle output P07 : Timer 7 toggle outputAD converter input port : AN0 (P00) to AN7 (P07)YesPort 1 P10 to P17I/O• 8-bit I/O port• I/O specifiable in 1-bit units• Pull-up resistors can be turned on and off in 1-bit units • Pin functionsP10 : SIO0 data output P11 : SIO0 data input/bus I/O P12 : SIO0 clock I/O P13 : SIO1 data output P14 : SIO1 data input/bus I/O P15 : SIO1 clock I/O P16 : Timer 1PWML outputP17 : Timer 1PWMH output/beeper outputYes Port 2 • 8-bit I/O port• I/O specifiable in 1-bit units• Pull-up resistors can be turned on and off in 1-bit units • Pin functions P20 : UART transmit P21 : UART receiveP20 to P23 : INT4 input/HOLD reset input/timer 1 event input/timer 0L capture input/timer 0H capture inputP24 to P27 : INT5 input/HOLD reset input/timer 1 event input/timer 0L capture input/timer 0H capture inputInterrupt acknowledge type Rising FallingRising &Falling H level L levelINT4 INT5 enable enableenable enableenable enabledisable disabledisable disableP20 to P27I/OYes Continued on next page.Port Output TypesThe table below lists the types of port outputs and the presence/absence of a pull-up resistor. Data can be read into any input port even if it is in the output mode.Port Name Option Selected inUnits ofOption Type Output Type Pull-up Resistor1 CMOS Programmable (Note 1)P00 to P07 1-bit2 Nch-opendrain No1 CMOS Programmable P10 to P17 1-bit2 Nch-opendrain Programmable1 CMOS Programmable P20 to P27 1-bit2 Nch-opendrain Programmable1 CMOSProgrammableP30 to P36 1-bit2 Nch-opendrain ProgrammableP70 -NoNch-opendrain Programmable P71 to P73 - No CMOS ProgrammablePWM0, PWM1 - No CMOSNoXT1 - No Output for 32.768kHz crystal oscillator(Input only)NoXT2 - No Input for 32.768kHz crystal oscillator(Nch-open drain when in general-purposeoutput mode)NoNote 1 : Programmable pull-up resistor of Port 0 is specified in nibble units (P00 to P03, P04 to P07).Note : To reduce V DD signal noise and to increase the duration of the backup battery supply, V SS1, V SS2, and V SS3 should connect to each other and they should also be grounded.Example 1 : During backup in hold mode, port output ‘H’ level is supplied from the back-up capacitor.Example 2 : During backup in hold mode, output is not held high and its value in unsettled.LSIAbsolute Maximum Ratings at Ta = 25°C, V SS 1 = V SS 2 = V SS 3 = 0VSpecificationParameter Symbol Pin/Remarks ConditionsV DD [V] min typ max unitMaximum supply voltage V DD maxV DD 1, V DD 2,V DD 3 V DD 1=V DD 2=V DD 3-0.3 +6.5Input voltage VI XT1, CF1 -0.3 V DD +0.3Input/output voltageVIO Ports 0, 1, 2, Port 3, 7, PWM0, PWM1, XT2-0.3 V DD +0.3VIOPH(1) Ports 0, 1, 2, 3CMOS output select Per 1 applicable pin-10 IOPH(2) PWM0, PWM1 CMOS output select Per 1 applicable pin -20 Peak output currentIOPH(3)Ports P71 to P73 Per 1 applicable pin -5 IOMH(1) Ports 0, 1, 2, 3CMOS output select Per 1 applicable pin -7.5 IOMH(2) PWM0, PWM1 CMOS output select Per 1 applicable pin -15 Mean output current (Note 1-1)IOMH(3)Ports P71 to P73 Per 1 applicable pin -3 ΣIOAH(1) Ports P71 to P73 Total of all applicable pins -10 ΣIOAH(2)Port 0 Total of all applicable pins -25 ΣIOAH(3) Port 1,PWM0, PWM1Total of all applicable pins-25 ΣIOAH(4) Ports 0, 1 PWM0, PWM1 Total of all applicable pins-45 ΣIOAH(5) Ports 2, P35, P36 Total of all applicable pins -25 ΣIOAH(6) Ports P30 to P34 Total of all applicable pins -25 H i g h l e v e l o u t p u t c u r r e n tTotal output currentΣIOAH(7)Ports 2, 3 Total of all applicable pins -45IOPL(1)Ports P02 to P07 Ports 1, 2, 3 PWM0, PWM1 Per 1 applicable pin20IOPL(2) Ports P00, P01 Per 1 applicable pin 30Peak output currentIOPL(3)Port 7, XT2 Per 1 applicable pin 10IOML(1) Ports P02 to P07 Ports 1, 2, 3 PWM0, PWM1 Per 1 applicable pin15IOML(2) Ports P00, P01 Per 1 applicable pin 20Mean output current (Note 1-1)IOML(3)Port 7, XT2 Per 1 applicable pin 7.5ΣIOAL(1) Port 7, XT2 Total of all applicable pins 15ΣIOAL(2) Port 0 Total of all applicable pins 45ΣIOAL(3)Port 1, PWM0, PWM1 Total of all applicable pins45ΣIOAL(4) Ports 0, 1 PWM0, PWM1 Total of all applicable pins80ΣIOAL(5) Ports 2, P35, P36 Total of all applicable pins 45ΣIOAL(6)Ports P30 to P34Total of all applicable pins45L o w l e v e l o u t p u t c u r r e n tTotal output currentΣIOAL(7)Ports 2, 3 Total of all applicable pins60mASQFP48 190Power dissipationPd maxQIP48ETa= -30 to +70°C390mWOperating ambient temperature Topr-30 +70Storage ambient temperatureTstg-55 +125°CNote 1-1 : The mean output current is a mean value measured over 100ms.a division ratio of 1/2.Note 2-2 : See Tables 1 and 2 for the oscillation constants.Serial Input/Output Characteristics at Ta = -30°C to +70°C, V SS 1 = V SS 2 = V SS 3 = 0V1. SIO0 Serial I/O Characteristics (Note 4-1-1)Specification Parameter Symbol Pin/Remarks ConditionsV DD [V] min typ max unitFrequency tSCK(1) 2 Low level pulse width tSCKL(1)1 tSCKH(1) See Fig. 6.1I n p u t c l o c kHigh level pulse widthtSCKHA(1)SCK0(P12) • Continuous datatransmission/reception mode • See Fig. 6. • (Note 4-1-2)2.5 to 5.54Frequency tSCK(2) 4/3 tCYCLow level pulse width tSCKL(2)1/2tSCKH(2)• CMOS output selected • See Fig. 6.1/2tSCKS e r i a l c l o c kO u t p u t c l o c kHigh level pulse widthtSCKHA(2)SCK0(P12) • Continuous datatransmission/reception mode • CMOS output selected • See Fig. 6.2.5 to 5.5tSCKH(2) +2tCYCtSCKH(2)+(10/3)tCYCtCYCData setup timetsDI(1)2.5 to 5.50.03S e r i a l i n p u tData hold time thDI(1) SB0(P11), SI0(P11)• Must be specified with respect to rising edge of SIOCLK. • See Fig. 6.2.5 to 5.50.03tdD0(1)• Continuous datatransmission/reception mode • (Note 4-1-3)2.5 to 5.5(1/3)tCYC+0.05I n p u t c l o c ktdD0(2)• Synchronous 8-bit mode • (Note 4-1-3) 2.5 to 5.51tCYC +0.05S e r i a l o u t p u t O u t p u t c l o c kOutput delay timetdD0(3)SO0(P10), SB0(P11)(Note 4-1-3)2.5 to 5.5(1/3)tCYC+0.05µsNote 4-1-1: These specifications are theoretical values. Add margin depending on its use.Note 4-1-2: To use serial-clock-input in continuous trans/rec mode, a time from SI0RUN being set when serial clock is "H" to the first negative edge of the serial clock must be longer than tSCKHA.Note 4-1-3: Must be specified with respect to falling edge of SIOCLK. Must be specified as the time to the beginning of output state change in open drain output mode. See Fig. 6.2. SIO1 Serial I/O Characteristics (Note 4-2-1)Specification Parameter Symbol Pin/Remarks ConditionsV DD [V] min typ max unitFrequency tSCK(3) 2 Low level pulse width tSCKL(3)1I n p u t c l o c kHigh level pulse width tSCKH(3) SCK1(P15) See Fig. 6.2.5 to 5.51 Frequency tSCK(4) 2tCYCLow level pulse width tSCKL(4)1/2S e r i a l c l o c kO u t p u t c l o c kHigh level pulse width tSCKH(4) SCK1(P15) • CMOS output selected • See Fig. 6.2.5 to 5.51/2tSCKData setup timetsDI(2)2.5 to 5.50.03S e r i a l i n p u tData hold timethDI(2) SB1(P14), SI1(P14)• Must be specified with respect to rising edge of SIOCLK. • See Fig. 6.2.5 to 5.50.03S e r i a l o u t p u tOutput delay time tdD0(4)SO1(P13), SB1(P14)• Must be specified with respect to falling edge of SIOCLK.• Must be specified as the time to the beginning of output state change in open drain output mode. • See Fig. 6.2.5 to 5.5(1/3)tCYC+0.05µsNote 4-2-1: These specifications are theoretical values. Add margin depending on its use.AD Converter Characteristics at V SS1 = V SS2 = V SS3 = 0V<12-bits AD Converter Mode / Ta= -10°C to +50°C>Specification Parameter Symbol Pin/Remarks ConditionsV DD[V] min typ max unit Resolution N 4.75 to 5.2512 bitAbsolute accuracy ET (Note 6-1) 4.75 to 5.25T.B.D LSB Conversion time TCAD See conversion time calculationformulas.(Note 6-2)4.75 to5.2538.5 90µsAnalog input voltage range VAIN4.75 to5.25V SS V DD V IAINH VAIN=V DD 4.75 to 5.251Analog port inputcurrent IAINL AN0(P00) toAN7(P07)AN8(P70)AN9(P71)AN10(XT1)AN11(XT2)VAIN=V SS 4.75 to 5.25-1µA<8-bits AD Converter Mode / Ta= -30°C to +70°C>Specification Parameter Symbol Pin/Remarks ConditionsV DD[V] min typ max unit Resolution N 3.0 to 5.5 8 bitAbsolute accuracy ET (Note 6-1) 3.0 to 5.5 ±1.5LSB4.5 to5.5 22.5 90Conversion time TCAD See conversion time calculationformulas. (Note 6-2) 3.0 to 5.5 45 90µsAnalog input voltage range VAIN3.0 to 5.5 V SS V DD V IAINH VAIN V DD 3.0 to 5.5 1Analog port inputcurrent IAINL AN0(P00) toAN7(P07)AN8(P70)AN9(P71)AN10(XT1)AN11(XT2)VAIN=V SS 3.0 to 5.5 -1µAConversion time calculation formulas :12-bits AD Converter Mode : TCAD (Conversion time) = ((52/(division ratio))+2) × (1/3) × tCYC8-bits AD Converter Mode : TCAD (Conversion time) = ((32/(division ratio))+2) × (1/3) × tCYCNote 6-1 : The quantization error (±1/2LSB) must be excluded from the absolute accuracy. The absolute accuracy must be measured in the microcontroller's state in which no I/O operations occur at the pins adjacent to the analog input channel.Note 6-2 : The conversion time refers to the period from the time an instruction for starting a conversion process till the time the conversion results register(s) are loaded with a complete digital conversion value corresponding tothe analog input value.The conversion time is 2 times the normal-time conversion time when :• The first AD conversion is performed in the 12-bit AD conversion mode after a system reset.• The first AD conversion is performed after the AD conversion mode is switched from 8-bit to 12-bitconversion mode.Consumption Current Characteristics at Ta = -30°C to +70°C, V SS 1 = V SS 2 = V SS 3 = 0VSpecificationParameter Symbol Pin/Remarks ConditionsV DD [V] min typ max unitIDDOP(1) • FmCF =10MHzceramic oscillation mode• FmX’tal=32.768kHz crystal oscillation mode• System clock set to 10MHz side • Internal RC oscillation stopped • Frequency variable RC oscillation stopped • 1/1 frequency division ratio4.5 to5.5712.5IDDOP(2)• CF1=20MHz external clock • FmX’tal=32.768kHz crystal oscillation mode• System clock set to CF1 side • Internal RC oscillation stopped • Frequency variable RC oscillation stopped • 1/2 frequency division ratio4.5 to5.5815IDDOP(3)4.5 to5.53.7 6.8IDDOP(4)• FmCF=5MHzceramic oscillation mode • FmX’tal=32.768kHz crystal oscillation mode• System clock set to 5MHz side • Internal RC oscillation stopped • Frequency variable RC oscillation stopped • 1/1 frequency division ratio2.5 to 4.51.9 5.2IDDOP(5)4.5 to5.50.6 1.9IDDOP(6)• FmCF=0Hz (oscillation stopped) • FmX’tal=32.768kHz crystal oscillation mode• System clock set to internal RCoscillation• Frequency variable RC oscillation stopped • 1/2 frequency division ratio2.5 to 4.50.3 1.4IDDOP(7)4.5 to5.5 1.3 4.2IDDOP(8)• FmCF=0Hz (oscillation stopped)• FmX’tal=32.768kHz crystaloscillation mode• Internal RC oscillation stopped• System clock set to 1MHz with frequency variable RC oscillation• 1/2 frequency division ratio2.5 to 4.50.7 3.2mAIDDOP(9)4.5 to5.52685Normal mode consumption current (Note 7-1)IDDOP(10)V DD 1 =V DD 2 =V DD 3• FmCF=0Hz (oscillation stopped) • FmX’tal=32.768kHz crystal oscillation mode• System clock set to 32.768kHz side• Internal RC oscillation stopped • Frequency variable RC oscillation stopped • 1/2 frequency division ratio2.5 to 4.51165µANote 7-1 : The consumption current value includes none of the currents that flow into the output Tr and internal pull-upresistors.Continued on next page.Continued from preceding page.Specification Parameter SymbolPin/Remarks ConditionsV DD [V] min typ max unitIDDHALT(1)• HALT mode • FmCF=10MHzceramic oscillation mode• FmX’tal=32.768kHz crystal oscillation mode • System clock set to 10MHz side • Internal RC oscillation stopped • Frequency variable RC oscillation stopped • 1/1 frequency division ratio4.5 to5.52.4 4.9IDDHALT(2)• HALT mode• CF1=20MHz external clock• FmX’tal=32.768kHz crystal oscillation mode • System clock set to CF1 side • Internal RC oscillation stopped • Frequency variable RC oscillation stopped • 1/2 frequency division ratio4.5 to5.53.4 7.7IDDHALT(3)4.5 to5.51.5 3.1IDDHALT(4)• HALT mode • FmCF=5MHzceramic oscillation mode• FmX’tal=32.768kHz crystal oscillation mode• System clock set to 5MHz side • Internal RC oscillation stopped • Frequency variable RC oscillation stopped • 1/1 frequency division ratio2.5 to 4.50.7 2.2IDDHALT(5)4.5 to5.50.3 1.1IDDHALT(6)• HALT mode• FmCF=0Hz (oscillation stopped)• FmX’tal=32.768kHz crystal oscillation mode• System clock set to internal RC oscillation • Frequency variable RC oscillation stopped • 1/2 frequency division ratio2.5 to 4.50.150.8IDDHALT(7)4.5 to5.51.1 3.6IDDHALT(8)• HALT mode• FmCF=0Hz (oscillation stopped)• FmX’tal=32.768kHz crystal oscillation mode • Internal RC oscillation stopped• System clock set to 1MHz with frequency variable RC oscillation• 1/2 frequency division ratio2.5 to 4.50.6 2.7mAIDDHALT(9)4.5 to5.518 60HALT mode consumption current (Note 7-1)IDDHALT(10)V DD 1 =V DD 2 =V DD 3• HALT mode• FmCF=0Hz (oscillation stopped)• FmX’tal=32.768kHz crystal oscillation mode • System clock set to 32.768kHz side• Internal RC oscillation stopped • Frequency variable RC oscillation stopped • 1/2 frequency division ratio2.5 to 4.5740IDDHOLD(1) 4.5 to 5.5 0.015 17HOLD mode consumption current IDDHOLD(2) V DD 1 HOLD mode• CF1=V DD or open(External clock mode)2.5 to 4.50.0112IDDHOLD(3)4.5 to5.5 16 55Timer HOLD mode consumption currentIDDHOLD(4) V DD 1Timer HOLD mode • CF1=V DD or open (External clock mode)• FmX’tal=32.768kHz crystal oscillation mode2.5 to 4.510 36µANote 7-1 : The consumption current value includes none of the currents that flow into the output Tr and internal pull-upresistors.UART (Full duplex) Operating Conditions at Ta = -30°C to +70°C, V SS 1 = V SS 2 = V SS 3 = 0VSpecification Parameter Symbol Pin/Remarks ConditionsV DD [V] min typ max unit Transfer rateUBRP20, P212.5 to 5.516/38192/3tCYCData length : 7, 8, and 9 bits (LSB first)Stop bits : 1-bit (2-bit in continuous data transmission)Parity bits : NoneExample of Continuous 8-bit Data Transmission Mode Processing (first transmit data=55H)Example of Continuous 8-bit Data Reception Mode Processing (first receive data=55H)Start bitStop bitStop bitStart bitCharacteristics of a Sample Main System Clock Oscillation CircuitGiven below are the characteristics of a sample main system clock oscillation circuit that are measured using aSANYO-designated oscillation characteristics evaluation board and external components with circuit constant values with which the oscillator vendor confirmed normal and stable oscillation.Table 1 Characteristics of a Sample Main System Clock Oscillator Circuit with a Ceramic OscillatorCircuit ConstantOscillation StabilizationTimeNominal FrequencyVendor NameOscillator NameC1 [pF]C2 [pF] Rf [Ω] Rd1[Ω] Operating Voltage Range [V] typ [ms] max [ms] RemarksCSTCE10M0G52-R0 (10)(10)Open6804.5 to5.5V0.1 0.5 10MHz MURATACSTCE10M0G52-B0 (10)(10) Open 680 4.5 to 5.5V 0.1 0.5 Internal C1, C2(SMD type) CSTCR5M00G53-R0 (15)(15) Open 2.2k 2.5 to 5.5V 0.2 0.6 5MHz MURATACSTCR5M00G53-B0 (15)(15) Open2.2k2.5 to 5.5V0.20.6Internal C1, C2(SMD type) The oscillation stabilization time refers to the time interval that is required for the oscillation to get stabilized after V DDgoes above the operating voltage lower limit (see Figure 4).It is recommended to insert feedback resister (Rf:1M Ω) when power supply voltage is used around 2.5V.Characteristics of a Sample Subsystem Clock Oscillator CircuitGiven below are the characteristics of a sample subsystem clock oscillation circuit that are measured using a SANYO-designated oscillation characteristics evaluation board and external components with circuit constant values with which the oscillator vendor confirmed normal and stable oscillation.Table 2 Characteristics of a Sample Subsystem Clock Oscillator Circuit with a Crystal OscillatorCircuit ConstantOscillation StabilizationTimeNominal FrequencyVendor NameOscillator NameC3 [pF]C4 [pF]Rf [Ω]Rd2 [Ω]Operating Voltage Range [V]typ [s] max [s] Remarks32.768kHz SEIKO EPSONMC-3061818 Open 510k 2.5 to 5.51.13.0Applicable CL value=12.5pF The oscillation stabilization time refers to the time interval that is required for the oscillation to get stabilized after the instruction for starting the subclock oscillation circuit is executed and to the time interval that is required for the oscillation to get stabilized after the HOLD mode is reset (see Figure 4).Note : The components that are involved in oscillation should be placed as close to the IC and to one another as possiblebecause they are vulnerable to the influences of the circuit pattern.Figure 1 CF Oscillator Circuit Figure 2 XT Oscillator Circuit Figure 3 AC Timing Measurement Point0.5V DD。

Si875x数据手册说明书

Si8751/52 Data SheetIsolated FET Driver with Pin Control or Diode Emulator InputsThe Si875x enables new pathways to the creation of custom Solid State Relay (SSR) configurations. The Si875x integrates robust isolation technology with an SSR FET driver. A floating secondary side dc power supply is unnecessary as the product generates its own self-contained gate drive output voltage. When combined with a customer-selected external FET, a complete Solid State Relay is formed, allowing customers to optimize their system for cost, PCB area, power, On-Resistance, and thermal performance.Customers have a choice of digital input control (Si8751) or diode emulation control(Si8752) to best suit their application. The Si875x integrates versatile outputs that support driving AC or DC load configurations.The Si875x eliminates the need for bulky mechanical relays which can be difficult to assem-ble onto PCBs and add switching noise to the system.Traditional SSRs integrate optocoupler-style LED inputs, which limit the operating tempera-ture range of the solution. The Si875x experiences no such limitation and can support full industrial and automotive temperature ranges with increased stability and longer life.The Si875x drives FET gates with a nominal 10 V using as little as 1 mA input current. Increasing the input current to 10 mA enables turn-on times as fast as 94 μs. Input side voltages on the Si8751 are flexible from 2.25 V to 5.5 V supporting seamless connectionto low-power controllers. The Si875x devices provide an Active Miller Clamp to prevent the unintended turn-on of the external FET when a high dV/dt is present on the FET’s drain.The Si875x is qualified to the AEC-Q100 standard, making it suitable for automotive applica-tions. Further, its 2.5 KVrms isolation rating forms the basis for full certification to UL, CSA, VDE, and CQC.Applications include mechanical relay, photo switch, or SSR replacement in motor control, valve control, HVAC relay, automotive, charging, battery monitoring, ac mains line switching, and more.The Si8751 and Si8752 come in ROHS-compliant SOIC-8 packaging, providing a compact, industry-standard footprint and generous margin to creepage and clearance requirements.KEY FEATURES•Drives user-selected external FETs •Choice of digital input control (Si8751) or diode emulation control (Si8752)•Internally generated secondary side power supply•10 V output with 1 mA input current •As fast as 82 μs turn-on time and 46 us turn-off time•Active Miller Clamp to prevent unintended turn-on and reduce inductive chatter•Supports AC or DC load switching •2.5 KVrms isolation rating•UL, CSA, VDE, and CQC certifications •AEC-Q100 qualified•Industrial –40 to 105 °C or Automotive –40 to 125 °C temperature ranges •ROHS-compliant SOIC-8 PackageAPPLICATIONS•Motor Controls•Valve Controls•HVAC Relays•HEV/EV Automotive Charging •Battery Monitoring•AC Mains Line Switching1. Ordering GuideTable 1.1. Si8751/2 Ordering Guide2. System OverviewFigure 2.1. Si8751 Block DiagramFigure 2.2. Si8752 Block DiagramThe operation of an Si875x channel is analogous to that of an optocoupler and gate driver, except an RF carrier is modulated instead of light. This simple architecture provides a robust isolated data path and requires no special considerations or initialization at start-up. A simplified block diagram for a single Si875x channel is shown in the figure below.A BFigure 2.3. Simplified Channel DiagramA channel consists of an RF Transmitter and RF Receiver separated by a semiconductor-based isolation barrier. Referring to the Transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The Receiver contains a demodulator that decodes the input state according to its RF energy content and applies the result to outputB via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it provides best-in-class noise immunity, low power consumption, and better immunity to magnetic fields. See figure below for more details.Input SignalModulation SignalOutput SignalFigure 2.4. Modulation Scheme2.1 Device BehaviorThe following are truth tables for the Si875x family.Table 2.1. Si8751 Truth TableTable 2.2. Si8752 Truth Table2.2 Power Supply Connections (Si8751 Only)The Si8751 requires a 0.1 µF bypass capacitor between VDD and GND. The capacitor should be placed as close as possible to the package. To enhance the robustness of a design, the user may also include a 1 µf capacitor for bulk decoupling as well as a resistor (50–300 Ω) in series with the input if the system is excessively noisy.2.3 TT Pin Description (Si8751 Only)The Si8751 provides a pin to control how much current is consumed by the supply when the input pin is logic high. The more current consumed by the input supply, the faster the output can turn on the external FET. This allows the application designer to optimize the tradeoff between power consumption and switching time.Typically, this pin is connected to the supply ground through a resistor. The greater the value of the resistor, the less current is consumed by the input supply. Values can range from 0 Ω (shorted to ground) to open (TT not connected).In addition to a resistor, a capacitor, typically 0.1 µf, can be placed in parallel to the resistor. This allows the device to draw more current to switch the external FET on quickly yet draw less supply current in the steady state. Total power over time is reduced while maintaining fast switching of the FET.MCAP1GATESOURCEMCAP2Figure 2.5. Si8751 TT Example Figure 2.6. Drive Current vs. Time Using TT with Capacitor2.4 LED Emulator Input (Si8752 Only)Figure 2.8. Diode Emulator Model and I-V CurveThe Si8752 uses input current to achieve the development of power across the isolation barrier. Therefore, the more current provided to the input, the more power is developed on the isolated side of the device. This translates into a faster turn on time of the external FET.This benefit is limited to an input current of about 15 mA. Beyond that, increasing the input current has little effect on the switching time of the external FET.2.5 Output DescriptionThe output of the Si875x device develops a positive voltage on the GATE pin with respect to the SOURCE pin. This voltage is used to turn on a typical field effect transistor (FET). Because power is transmitted across the isolation barrier, no isolated supply is required. This can be used to drive a FET configured as a switch for a dc load. It can also be used to drive a pair of FETs configured as a switch for an ac load. See 3. Applications.2.6 Miller Clamp2.6.1 Miller Clamp DescriptionThe Si875x devices provide a clamping device to prevent unintended turn on of the external FET when a high dV/dt is present on the FET’s drain. To use this feature, a capacitor is connected between the drain(s) of the FET(s) and one of the MCAPx inputs. A sudden, positive slope on this pin will cause the clamp device within the Si875x to activate and provide a low impedance path between the gate and source pins. This will prevent the FET from being unintentionally turned on.The Si875x device provides two miller clamp input pins. This allows for both FET’s to be protected from unintended turn on when the device is used in an AC switch configuration. In this case each drain is connected to an MCAPx input through a capacitor.Connection to a MCAPx pin, and use of the Miller Clamp feature, is optional. The device will function as expected if these pins are left unconnected.2.6.2 Sizing Miller Clamp CapacitorsThe recommended value of the capacitor used to connect the drain of the external FET to the Si875x device is typically 10 pf. If the application has a very large dV/dt and the clamp is not adequately keeping the external FET off, then this capacitor value can be increased up to 100 pf. The voltage rating of the capacitor should be greater than or equal to the peak voltage expected at the drain of the FET. The relationship of the capacitor and the dV/dt is governed by the equation: C = I MC/(dV/dt); where: I MC is the Miller Clamp input current (6mA max, as specified in Electrical Tables), and dV/dt is the expected slew rate.3. ApplicationsThe following examples illustrate typical circuit configurations using the Si8751/52.3.1 DC SSR ExampleThe Si875x device can be used to control a dc load as shown in the following figure:INVDDTTGNDFigure 3.1. Driving an FET for DC Load Including Miller Clamp CapacitorIn this configuration, the Si8751 charges the gate of the external FET; turning it on. This switches on power, supplied by VDC, to the load. The output side circuitry is identical if using the Si8752.3.2 AC SSR ExampleThe Si875x can be used to control power to an ac load using the following circuit:INTTGNDFigure 3.2. Driving FETs for AC Load SwitchingIn this configuration, both FET’s are turned on by the charge delivered by the Si8751. This allows ac current to flow to the load. When the Si875x is turned off, charge is drained form the gates of both FET’s and the ac current is turned off. The output side circuitry is identical if using the Si8752.Si8751/52 Data Sheet • Applications4. Electrical SpecificationsTable 4.1. Electrical Specifications•Automotive: VDD=2.25 to 5.5V; GND=0V; T A=-40 to +125ºC; typical specs at 25ºC; T J=-40 to +150ºC •Industrial: VDD=2.25 to 5.5V; GND=0V; T A=-40 to +105ºC; typical specs at 25ºC; T J=-40 to +150ºC4.1 Test CircuitsThe following figure depicts a common-mode transient immunity test circuit:IsolatedSupplyFigure 4.1. Common-Mode Transient Immunity Test Circuit4.2 Regulatory InformationTable 4.2. Regulatory Information1,2CSAThe Si875x is certified under CSA Component Acceptance Notice 5A. For more details, see Master Contract Number 232873. 60950-1: Up to 125 V RMS reinforced insulation working voltage; up to 600 V RMS basic insulation working voltage.VDEThe Si875x is certified according to VDE 0884-10. For more details, see Certificate 40018443.VDE 0884-10: Up to 630 V peak for basic insulation working voltage.ULThe Si875x is certified under UL1577 component recognition program. For more details, see File E257455.Rated up to 2500 V RMS isolation voltage for basic protection.CQCThe Si875x is certified under GB4943.1-2011. For more details, see Certificate CQC17001177960.Rated up to 125 V RMS reinforced insulation working voltage; up to 600 V RMS basic insulation working voltage.1.Regulatory Certifications apply to2.5 kV RMS rated devices which are production tested to3.0 kV RMS for 1 sec.2.For more information, see 1. Ordering Guide.Table 4.3. Insulation and Safety-Related SpecificationsTable 4.4. IEC 60664-1 RatingsTable 4.5. VDE 0884 Insulation Characteristics1Table 4.6. IEC Safety Limiting Values1Table 4.7. Thermal CharacteristicsFigure 4.2. Thermal Derating Curve for Safety Limiting Current (Si8751)Figure 4.3. Thermal Derating Curve for Safety Limiting Current (Si8752)Table 4.8. Absolute Maximum Ratings14.3 Typical Operating CharacteristicsFigure 4.4. Si8751 Typical Gate Voltage vs. Temperatureand TT Figure 4.5. Si8752 Typical Gate Voltage vs. Temperatureand Anode CurrentFigure 4.6. Si8751 Typical Turn-On Time vs. Temperature and TT with 100 pF Load (50% of Output)Figure 4.7. Si8752 Typical Turn-On Time vs. Temperature and Anode Current with 100 pF Load (50% of Output)Figure 4.8. Si8751 Typical Turn-On Time vs. Temperature and TT with 100 pF Load (90% of Output)Figure 4.9. Si8752 Typical Turn-On Time vs. Temperature and Anode Current with 100 pF Load (90% of Output)Figure 4.10. Si8751 Typical Turn-On Time vs. Capacitanceand TT (50% of Output)Figure 4.11. Si8752 Typical Turn-On Time vs. Capacitance and Anode Current (50% of Output)Figure 4.12. Si8751 Typical Turn-On Time vs. Capacitanceand TT (90% of Output)Figure 4.13. Si8752 Typical Turn-On Time vs. Capacitance and Anode Current (90% of Output)5. Pin Descriptions5.1 Si8751 Pin Descriptions12345678SOURCEMCAP2MCAP1GATEGND TT VDD Si8751IN Figure 5.1. Pin Assignments Si8751Table 5.1. Si8751 Pin Descriptions5.2 Si8752 Pin Descriptions12345678GATEMCAP2MCAP1SOURCECATHODE ANODE NC Si8752NC Figure 5.2. Pin Assignments Si8752Table 5.2. Si8752 Pin Descriptions6. Package Outlines6.1 Package Outline: 8-Pin Narrow Body SOICThe figure below illustrates the package details for the Si875x in an 8-pin narrow-body SOIC package. The table below lists the values for the dimensions shown in the illustration.Figure 6.1. 8-Pin Narrow Body SOIC PackageTable 6.1. 8-Pin Narrow Body SOIC Package Diagram Dimensions7. Land Patterns7.1 Land Pattern: 8-Pin Narrow Body SOICThe figure below illustrates the recommended land pattern details for the Si875x in an 8-pin narrow-body SOIC. The table below lists the values for the dimensions shown in the illustration.Figure 7.1. 8-Pin Narrow Body SOIC Land PatternTable 7.1. 8-Pin Narrow Body SOIC Land Pattern Dimensions8. Top Markings8.1 8-Pin Narrow Body SOICTable 8.1. Top Marking ExplanationLine 1 Marking:Customer Part Number Si875 = ISOdriver product seriesX: 1 = Digital input, 2 = LED emulator inputA: ReservedV: B = 2.5 kV isolation ratingLine 2 Marking:TTTTTT = Mfg code Manufacturing Code from Assembly Purchase Order form.Line 3 Marking:YY = YearWW = Work week Assigned by the Assembly House. Corresponds to the year and workweek of the mold date.9. Revision HistoryRevision A, July 2022•Added Agile data sheet revision in footerRevision 1.0, December 2017•Significant edits with production electrical specifications and load switching diagram.Revision 0.5, September 2016•Significant edits with production electrical specifications.Revision 0.1, May 2016•Initial revision.Table of Contents1. Ordering Guide (2)2. System Overview (3)2.1 Device Behavior (4)2.2 Power Supply Connections (Si8751 Only) (5)2.3 TT Pin Description (Si8751 Only) (5)2.4 LED Emulator Input (Si8752 Only) (5)2.5 Output Description (6)2.6 Miller Clamp (6)2.6.1 Miller Clamp Description (6)2.6.2 Sizing Miller Clamp Capacitors (6)3. Applications (7)3.1 DC SSR Example (7)3.2 AC SSR Example (7)4. Electrical Specifications (8)4.1 Test Circuits (10)4.2 Regulatory Information (10)4.3 Typical Operating Characteristics (16)5. Pin Descriptions (19)5.1 Si8751 Pin Descriptions (19)5.2 Si8752 Pin Descriptions (20)6. Package Outlines (21)6.1 Package Outline: 8-Pin Narrow Body SOIC (21)7. Land Patterns (23)7.1 Land Pattern: 8-Pin Narrow Body SOIC (23)8. Top Markings (24)8.1 8-Pin Narrow Body SOIC (24)9. Revision History (25)Copyright © 2022 Skyworks Solutions, Inc. All Rights Reserved.Information in this document is provided in connection with Skyworks Solutions, Inc. (“Skyworks”) products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by thecustomer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks’ Terms and Conditions of Sale.THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED “AS IS” WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED,STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSL Y DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESUL T FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks’ published specifications or parameters.Skyworks, the Skyworks symbol, Sky5®, SkyOne®, SkyBlue™, Skyworks Green™, ClockBuilder®, DSPLL®, ISOmodem®, ProSLIC®, and SiPHY® are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at , are incorporated by reference.SkyworksSolutions,Inc.|Nasdaq:SWKS|*********************|Portfolio Quality/qualitySupport & Resources/support。

微电子VSC8584-10数据手册:四口10 100 1000BASE-T PHY 同步以太网PHY