LTC1386IS中文资料

LTC1606中文资料

Ext. Reference = 2.5V (Notes 12, 13) q

± 0.50

± 0.25

%

Full-Scale Error Drift

Ext. Reference = 2.5V

±2

±2

ppm/°C

Power Supply Sensitivity VANA = VDIG = VDD

VDD = 5V ±5% (Note 9)

The 90dB signal-to-noise ratio offers an improvement of 3dB over competing devices, and the RMS transition noise is reduced (0.65LSB vs 1LSB) relative to competitive parts.

CONTROL LOGIC AND

TIMING

AGND1 AGND2 DGND

2

5

14

BUSY 26 CS 25 R/C 24

BYTE 23

DIGITAL CONTROL SIGNALS

1606 TA01

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

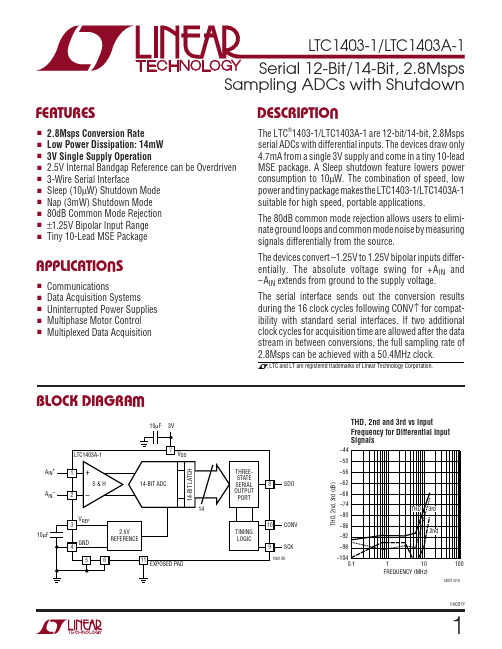

LTC1403CMSE-1#PBF资料

T JMAX = 125°C, θJA = 150°C/W EXPOSED PAD (PIN 11) IS GND MUST BE SOLDERED TO PCB12345A IN +A IN –V REF GND GND 109876CONV SCK SDO V DD GNDTOP VIEW11MSE PACKAGE10-LEAD PLASTIC MSOP (Notes 1, 2)Supply Voltage (V DD ).................................................4V Analog Input Voltage(Note 3)....................................–0.3V to (V DD + 0.3V)Digital Input Voltage ................... – 0.3V to (V DD + 0.3V)Digital Output Voltage..................–0.3V to (V DD + 0.3V)Power Dissipation..............................................100mW Operation Temperature RangeLTC1403C-1/LTC1403AC-1.....................0°C to 70°C LTC1403I-1/LTC1403AI-1..................–40°C to 85°C Storage Temperature Range.................–65°C to 150°C Lead Temperature (Soldering, 10 sec)..................300°CORDER PART NUMBERMSE PART MARKINGLTBGP LTBGQ LTBGR LTBGSLTC1403CMSE-1LTC1403IMSE-1LTC1403ACMSE-1LTC1403AIMSE-1The q denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. With internal reference. V DD = 3VLTC1403-1LTC1403A-1PARAMETERCONDITIONSMIN TYP MAXMIN TYP MAX UNITS Resolution (No Missing Codes)q 1214Bits Integral Linearity Error (Notes 4, 5, 18)q –2±0.252–4±0.54LSB Offset Error (Notes 4, 18)q –10±110–20±220LSB Gain Error (Note 4, 18)q–30±530–60±1060LSB Gain TempcoInternal Reference (Note 4)±15±15ppm/°C External Reference±1±1ppm/°CThe q denotes the specifications which apply over the full operating temperature range,otherwise specifications are at T A = 25°C. V DD = 3VSYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITSV IN Analog Differential Input Range (Notes 3, 8, 9) 2.7V ≤ V DD ≤ 3.3Vq–1.25 to 1.25V V CM Analog Common Mode + Differential 0 to V DDVInput Range (Note 10)I IN Analog Input Leakage Current q 1µA C IN Analog Input Capacitance 13pF t ACQ Sample-and-Hold Acquisition Time (Note 6)q39ns t AP Sample-and-Hold Aperture Delay Time 1ns t JITTER Sample-and-Hold Aperture Delay Time Jitter 0.3ps CMRRAnalog Input Common Mode Rejection Ratiof IN = 1MHz, V IN = 0V to 3V –60dB f IN = 100MHz, V IN = 0V to 3V–15dBConsult LTC Marketing for parts specified with wider operating temperature ranges.ABSOLUTE AXI U RATI GSW W WU PACKAGE/ORDER I FOR ATIOU U WCO VERTER CHARACTERISTICSUA ALOG I PUTUU14031fThe q denotes the specifications which apply over the full operating temperature range,otherwise specifications are at T A = 25°C. V DD = 3V. Single-ended A IN + signal drive with A IN – = 1.5V DC. Differential signal drive with V CM = 1.5V at A IN + and A IN –LTC1403-1LTC1403A-1SYMBOL PARAMETER CONDITIONSMIN TYP MAX MIN TYP MAX UNITS SINADSignal-to-Noise Plus 100kHz Input Signal (Note 19)70.573.5dB Distortion Ratio1.4MHz Input Signal (Note 19)q6870.57073.5dB 100kHz Input Signal, External V REF = 3.3V,7276.3dB V DD ≥ 3.3V (Note 19)750kHz Input Signal, External V REF = 3.3V,7276.3dB V DD ≥ 3.3V (Note 19)THD Total Harmonic 100kHz First 5 Harmonics (Note 19)–87–90dB Distortion 1.4MHz First 5 Harmonics (Note 19)q –83–76–86–78dB SFDR Spurious Free 100kHz Input Signal (Note 19)–87–90dB Dynamic Range 1.4MHz Input Signal (Note 19)–83–86dB IMDIntermodulation 0.625V P-P 1.4MHz Summed with 0.625V P-P –82–82dB Distortion 1.56MHz into A IN + and Inverted into A IN –Code-to-Code V REF = 2.5V (Note 18)0.251LSB RMSTransition Noise Full Power Bandwidth V IN = 2.5V P-P , SDO = 11585LSB P-P (Note 15)5050MHz Full Linear BandwidthS/(N + D) ≥ 68dB55MHzThe q denotes the specifications which apply over thefull operating temperature range, otherwise specifications are at T A = 25°C. V DD = 3VPARAMETER CONDITIONS MINTYP MAXUNITSV REF Output Voltage I OUT = 02.5V V REF Output Tempco 15ppm/°C V REF Line Regulation V DD = 2.7V to 3.6V, V REF = 2.5V 600µV/V V REF Output Resistance Load Current = 0.5mA0.2ΩV REF Settling Time2msThe q denotes the specifications which apply over thefull operating temperature range, otherwise specifications are at T A = 25°C. V DD = 3VSYMBOL PARAMETERCONDITIONS MINTYP MAX UNITSV IH High Level Input Voltage V DD = 3.3V q 2.4V V IL Low Level Input Voltage V DD = 2.7V q 0.6V I IN Digital Input Current V IN = 0V to V DD q±10µA C IN Digital Input Capacitance (Note 20)5pF V OH High Level Output Voltage V DD = 3V, I OUT = –200µA q 2.5 2.9V V OL Low Level Output Voltage V DD = 2.7V, I OUT = 160µA 0.05V V DD = 2.7V, I OUT = 1.6mA q 0.100.4V I OZ Hi-Z Output Leakage D OUT V OUT = 0V to V DDq±10µA C OZ Hi-Z Output Capacitance D OUT 1pF I SOURCE Output Short-Circuit Source Current V OUT = 0V, V DD = 3V 20mA I SINKOutput Short-Circuit Sink CurrentV OUT = V DD = 3V 15mADY A IC ACCURACYUW I TER AL REFERE CE CHARACTERISTICSU U UDIGITAL I PUTS A D DIGITAL OUTPUTSUUSYMBOL PARAMETERCONDITIONSMIN TYP MAXUNITS f SAMPLE(MAX)Maximum Sampling Frequency per Channel q 2.8MHz (Conversion Rate)t THROUGHPUT Minimum Sampling Period (Conversion + Acquisiton Period)q357ns t SCK Clock Period (Note 16)q19.810000nst CONV Conversion Time(Note 6)1618SCLK cyclest 1Minimum Positive or Negative SCLK Pulse Width (Note 6)2ns t 2CONV to SCK Setup Time(Notes 6, 10)3ns t 3Nearest SCK Edge Before CONV(Note 6)0ns t 4Minimum Positive or Negative CONV Pulse Width (Note 6)4ns t 5SCK to Sample Mode (Note 6)4ns t 6CONV to Hold Mode(Notes 6, 11) 1.2ns t 716th SCK ↑ to CONV ↑ Interval (Affects Acquisition Period)(Notes 6, 7, 13)45ns t 8Minimum Delay from SCK to Valid Data (Notes 6, 12)8ns t 9SCK to Hi-Z at SDO(Notes 6, 12)6ns t 10Previous SDO Bit Remains Valid After SCK(Notes 6, 12)2ns t 12V REF Settling Time After Sleep-to-Wake Transition(Notes 6, 14)2msTI I G CHARACTERISTICSWU The q denotes the specifications which apply over the full operating temperaturerange, otherwise specifications are at T A = 25°C. V DD = 3VPOWER REQUIRE E T SWU The q denotes the specifications which apply over the full operating temperaturerange, otherwise specifications are at T A = 25°C. (Note 17)SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSV DD Supply Voltage2.73.6V I DDPositive Supply VoltageActive Mode q 4.77mA Nap Modeq1.1 1.5mA Sleep Mode (LTC1403)215µA Sleep Mode (LTC1403A)210µA P DPower DissipationActive Mode with SCK in Fixed State (Hi or Lo)12mWNote 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.Note 2: All voltage values are with respect to GND.Note 3: When these pins are taken below GND or above V DD , they will be clamped by internal diodes. This product can handle input currents greater than 100mA below GND or greater than V DD without latchup.Note 4: Offset and full-scale specifications are measured for a single-ended A IN + input with A IN – grounded and using the internal 2.5V reference.Note 5: Integral linearity is tested with an external 2.55V reference and is defined as the deviation of a code from the straight line passing through the actual endpoints of a transfer curve. The deviation is measured from the center of quantization band.Note 6: Guaranteed by design, not subject to test.Note 7: Recommended operating conditions.Note 8: The analog input range is defined for the voltage differencebetween A IN + and A IN –. Performance is specified with A IN – = 1.5V DC while driving A IN +.Note 9: The absolute voltage at A IN + and A IN – must be within this range.Note 10: If less than 3ns is allowed, the output data will appear one clock cycle later. It is best for CONV to rise half a clock before SCK, when running the clock at rated speed.Note 11: Not the same as aperture delay. Aperture delay is smaller (1ns)because the 2.2ns delay through the sample-and-hold is subtracted from the CONV to Hold mode delay.Note 12: The rising edge of SCK is guaranteed to catch the data coming out into a storage latch.Note 13: The time period for acquiring the input signal is started by the 16th rising clock and it is ended by the rising edge of convert.Note 14: The internal reference settles in 2ms after it wakes up from Sleep mode with one or more cycles at SCK and a 10µF capacitive load.Note 15: The full power bandwidth is the frequency where the output code swing drops to 3dB with a 2.5V P-P input sine wave.Note 16: Maximum clock period guarantees analog performance during conversion. Output data can be read without an arbitrarily long clock.Note 17: V DD = 3V, f SAMPLE = 2.8Msps.Note 18: The LTC1403A-1 is measured and specified with 14-bitResolution (1LSB = 152µV) and the LTC1403-1 is measured and specified with 12-bit Resolution (1LSB = 610µV).Note 19: Full-scale sinewaves are fed into the noninverting input while the inverting input is kept at 1.5V DC.Note 20: The sampling capacitor at each input accounts for 4.1pF of the input capacitance.DRIVING THE ANALOG INPUTThe differential analog inputs of the LTC1403-1/LTC1403A-1are easy to drive. The inputs may be driven differentially or as a single-ended input (i.e., the A IN – input is set to V CM ). Both differential analog inputs, A IN + with A IN –, are sampled at the same instant. Any unwanted signal that is common to both inputs of each input pair will be reduced by the common mode rejection of the sample-and-hold circuit. The inputs draw only one small current spike while charging the sample-and-hold capacitors at the end of conversion. During conversion, the analog inputs draw only a small leakage current. If the source impedance of the driving circuit is low, then the LTC1403-1/LTC1403A-1 inputs can be driven directly. As source imped-ance increases, so will acquisition time. For minimum acqui-sition time with high source impedance, a buffer amplifier must be used. The main requirement is that the amplifier driving the analog input(s) must settle after the small current spike before the next conversion starts (settling time must be 39ns for full throughput rate). Also keep in mind while choosing an input amplifier, the amount of noise and har-monic distortion added by the amplifier.CHOOSING AN INPUT AMPLIFIERChoosing an input amplifier is easy if a few requirements are taken into consideration. First, to limit the magnitude of the voltage spike seen by the amplifier from charging the sam-pling capacitor, choose an amplifier that has a low output impedance (<100Ω) a t t he c losed-loop b andwidth f requency.For example, if an amplifier is used with a gain of 1 and has a unity-gain bandwidth of 50MHz, then the output impedance at 50MHz must be less than 100Ω. The second requirement is that the closed-loop bandwidth must be greater than 40MHz to ensure adequate small-signal settling for full throughput rate. If slower op amps are used, more time for settling can be provided by increasing the time between conversions. The best choice for an op amp to drive the LTC1403-1/LTC1403A-1 w ill d epend o n t he a pplication. G en-erally, applications fall into two categories: AC applications where dynamic specifications are most critical and time domain applications where DC accuracy and settling time are most critical. The following list is a summary of the op amps that are suitable for driving the LTC1403-1/LTC1403A-1.(More detailed information is available in the Linear Technol-ogy Databooks and our website at .)LTC ®1566-1: Low Noise 2.3MHz Continuous Time Low-Pass Filter.LT1630: Dual 30MHz Rail-to-Rail Voltage FB Amplifier. 2.7V to ±15V supplies. Very high A VOL , 500µV offset and 520ns settling to 0.5LSB for a 4V swing. THD and noise are –93dB to 40kHz and below 1LSB to 320kHz (A V = 1, 2V P-P into 1k Ω,V S = 5V), making the part excellent for AC applications (to 1/3 Nyquist) where rail-to-rail performance is desired. Quad version is available as LT1631.LT1632: Dual 45MHz Rail-to-Rail Voltage FB Amplifier. 2.7V to ±15V supplies. Very high A VOL , 1.5mV offset and 400ns settling to 0.5LSB for a 4V swing. It is suitable for applica-tions with a single 5V supply. THD and noise are –93dB to 40kHz and below 1LSB to 800kHz (A V = 1,2V P-P into 1k Ω, V S = 5V), making the part excellent for AC applications where rail-to-rail performance is desired. Quad version is available as LT1633.LT1813: Dual 100MHz 750V/µs 3mA Voltage Feedback Amplifier. 5V to ±5V supplies. Distortion is –86dB to 100kHz and –77dB to 1MHz with ±5V supplies (2V P-P into 500Ω).Excellent part for fast AC applications with ±5V␣supplies.LT1801: 80MHz GBWP, –75dBc at 500kHz, 2mA/Amplifier,8.5nV/√Hz.LT1806/LT1807: 325MHz G BWP, –80dBc D istortion a t 5MHz,Unity-Gain S table, R -R I n a nd O ut, 10mA/Amplifier, 3.5nV/√Hz.LT1810: 180MHz GBWP, –90dBc Distortion at 5MHz,Unity-Gain S table, R -R I n a nd O ut, 15mA/Amplifier, 16nV/√Hz.LT1818/LT1819: 400MHz, 2500V/µs,9mA, Single/Dual Volt-age Mode Operational Amplifier.LT6200: 165MHz GBWP, –85dBc Distortion at 1MHz, Unity-Gain Stable, R-R In and Out, 15mA/Amplifier,0.95nV/√Hz.LT6203: 100MHz GBWP, –80dBc Distortion at 1MHz,Unity-Gain Stable, R-R In and Out, 3mA/Amplifier,1.9nV/√Hz.LT6600-10: Amplifier/Filter Differential In/Out with 10MHz Cutoff.APPLICATIO S I FOR ATIOW UUU111214031 F07Figure 7. Recommended LayoutDigital circuitry grounds must be connected to the digital supply common. In applications where the ADC data outputs and control signals are connected to a continu-ously active microprocessor bus, it is possible to get errors in the conversion results. These errors are due to feedthrough from the microprocessor to the successive131414031fmode and the power drain drops from 14mW to 6mW. The internal reference remains powered in Nap mode. One or more rising edges at SCK wake up the LTC1403-1/LTC1403A-1 for service very quickly, and CONV can start an accurate conversion within a clock cycle. Four rising edges at CONV, without any intervening rising edges at SCK, put the LTC1403-1/LTC1403A-1 in Sleep mode and the power drain drops from 16mW to 10µW. One or more rising edges at SCK wake up the LTC1403-1/LTC1403A-1for operation. The internal reference (V REF ) takes 2ms to slew and settle with a 10µF load. Note that, using sleep mode more frequently than every 2ms, compromises the settled accuracy of the internal reference. Note that, for slower conversion rates, the Nap and Sleep modes can be used for substantial reductions in power consumption.DIGITAL INTERFACEThe LTC1403-1/LTC1403A-1 has a 3-wire SPI (Serial Protocol Interface) interface. The SCK and CONV inputs and SDO output implement this interface. The SCK and CONV inputs accept swings from 3V logic and are TTL compatible, if the logic swing does not exceed V DD . A detailed description of the three serial port signals follows:Conversion Start Input (CONV)The rising edge of CONV starts a conversion, but subse-quent rising edges at CONV are ignored by the LTC1403-1/LTC1403A-1 until the following 16 SCK rising edges have occurred. It is necessary to have a minimum of 16 rising edges of the clock input SCK between rising edges of CONV. But to obtain maximum conversion speed, it is necessary to allow two more clock periods between con-versions to allow 39ns of acquisition time for the internal ADC sample-and-hold circuit. With 16 clock periods per conversion, the maximum conversion rate is limited to 2.8Msps to allow 39ns for acquisition time. In either case,the output data stream comes out within the first 16 clock periods to ensure compatibility with processor serial ports. The duty cycle of CONV can be arbitrarily chosen to be used as a frame sync signal for the processor serial port. A simple approach to generate CONV is to create a pulse that is one SCK wide to drive the LTC1403-1/LTC1403A-1 and then buffer this signal with the appropri-ate number of inverters to ensure the correct delay drivingthe frame sync input of the processor serial port. It is good practice to drive the LTC1403-1/LTC1403A-1 CONV input first to avoid digital noise interference during the sample-to-hold transition triggered by CONV at the start of conver-sion. It is also good practice to keep the width of the low portion of the CONV signal greater than 15ns to avoid introducing glitches in the front end of the ADC just before the sample-and-hold goes into hold mode at the rising edge of CONV.Minimizing Jitter on the CONV InputIn high speed applications where high amplitude sinewaves above 100kHz are sampled, the CONV signal must have as little jitter as possible (10ps or less). The square wave output of a common crystal clock module usually meets this requirement easily. The challenge is to generate a CONV signal from this crystal clock without jitter corrup-tion from other digital circuits in the system. A clock divider and any gates in the signal path from the crystal clock to the CONV input should not share the same integrated circuit with other parts of the system. As shown in the interface circuit examples, the SCK and CONV inputs should be driven first, with digital buffers used to drive the serial port interface. Also note that the master clock in the DSP may already be corrupted with jitter, even if it comes directly from the DSP crystal. Another problem with high speed processor clocks is that they often use a low cost,low speed crystal (i.e., 10MHz) to generate a fast, but jittery, phase-locked-loop system clock (i.e., 40MHz). The jitter in these PLL-generated high speed clocks can be several nanoseconds. Note that if you choose to use the frame sync signal generated by the DSP port, this signal will have the same jitter of the DSP’s master clock.Serial Clock Input (SCK)The rising edge of SCK advances the conversion process and also udpates each bit in the SDO data stream. After CONV rises, the third rising edge of SCK starts clocking out the 12/14 data bits with the MSB sent first. A simple approach is to generate SCK to drive the LTC1403-1/LTC1403A-1 first and then buffer this signal with the appropriate number of inverters to drive the serial clock input of the processor serial port. Use the falling edge of the clock to latch data from the Serial Data Output (SDO)APPLICATIO S I FOR ATIOW UUU151614031fAPPLICATIO S I FOR ATIOW UU U ; 10-23-03 ******************************************************************; Files: 014SI.ASM -> 1403 bipolar Sine wave collection with Serial Port interface ; bvectors.asm buffered mode.; s2k14ini.asm 2k buffer size.; first element at 1024, last element at 1023, two middles at 2047 and 0000; bipolar mode; Works 16 or 64 clock frames.; negative edge BCLKR ; negative BFSR pulse ; -0 data shifted; 1' cable from counter to CONV at DUT ; 2' cable from counter to CLK at DUT; *************************************************************************** .width 160 .length 110.title “sineb0 BSP in auto buffer mode” .mmregs.setsect “.text”, 0x500,0 ;Set address of executable.setsect “vectors”, 0x180,0 ;Set address of incoming 1403 data.setsect “buffer”, 0x800,0 ;Set address of BSP buffer for clearing .setsect “result”, 0x1800,0 ;Set address of result for clearing .text ;.text marks start of codestart:;this label seems necessary;Make sure /PWRDWN is low at J1-9 ;to turn off AC01 adc tim=#0fh prd=#0fhtcr = #10h ; stop timertspc = #0h ; stop TDM serial port to AC01pmst = #01a0h ; set up iptr. Processor Mode STatus register sp = #0700h ; init stack pointer. dp = #0 ; data pagear2 = #1800h ; pointer to computed receive buffer.ar3 = #0800h ; pointer to Buffered Serial Port receive buffer ar4 = #0h ; reset record countercall sineinit ; Double clutch the initialization to insure a proper sinepeek:call sineinit ; reset. The external frame sync must occur 2.5 clocks ; or more after the port comes out of reset.wait goto wait; ————————Buffered Receive Interrupt Routine —————————breceive:ifr = #10h ; clear interrupt flagsTC = bitf(@BSPCE,#4000h) ; check which half (bspce(bit14)) of buffer if (NTC) goto bufull ; if this still the first half get next half bspce = #(2023h + 08000h); turn on halt for second half (bspce(bit15)) return_enable; ———————mask and shift input data ——————————————bufull:b = *ar3+ << -0 ; load acc b with BSP buffer and shift right -0 b = #03FFFh & b ; mask out the TRISTATE bits with #03FFFhb = b ^ #2000h ; invert the MSB for bipolar operation B *ar2+ = data(#0bh) ; store B to out buffer and advance AR2 pointer TC = (@ar2 == #02000h) ; output buffer is 2k starting at 1800h if (TC) goto start ; restart if out buffer is at 1fffh goto bufull1714031fAPPLICATIO S I FOR ATIOW UU U ; —————————dummy bsend return————————————bsend return_enable ;this is also a dummy return to define bsend ;in vector table file BVECTORS.ASM ; ——————————— end ISR ——————————————.copy “c:\dskplus\1403\s2k14ini.asm” ;initialize buffered serial port .space 16*32 ;clear a chunk at the end to mark the end ;======================================================================;; VECTORS ;;====================================================================== .sect “vectors” ;The vectors start here .copy “c:\dskplus\1403\bvectors.asm” ;get BSP vectors.sect “buffer” ;Set address of BSP buffer for clearing .space 16*0x800.sect “result” ;Set address of result for clearing .space 16*0x800 .end; ***************************************************************************; File: BVECTORS.ASM -> Vector Table for the ‘C54x DSKplus 10.Jul.96; BSP vectors and Debugger vectors ; TDM vectors just return; ***************************************************************************; The vectors in this table can be configured for processing external and ; internal software interrupts. The DSKplus debugger uses four interrupt ; vectors. These are RESET, TRAP2, INT2, and HPIINT.; * DO NOT MODIFY THESE FOUR VECTORS IF YOU PLAN TO USE THE DEBUGGER *;; All other vector locations are free to use. When programming always be sure ; the HPIINT bit is unmasked (IMR=200h) to allow the communications kernel and ; host PC interact. INT2 should normally be masked (IMR(bit 2) = 0) so that the ; DSP will not interrupt itself during a HINT. HINT is tied to INT2 externally.;;;.title “Vector Table” .mmregsreset goto #80h ;00; RESET * DO NOT MODIFY IF USING DEBUGGER * nop nopnmi return_enable ;04; non-maskable external interrupt nop nop noptrap2 goto #88h ;08; trap2 * DO NOT MODIFY IF USING DEBUGGER * nop nop.space 52*16 ;0C-3F: vectors for software interrupts 18-30int0 return_enable ;40; external interrupt int0 nop nop nopint1 return_enable ;44; external interrupt int1 nop nop nop1814031fAPPLICATIO S I FOR ATIOW UUU int2 return_enable ;48; external interrupt int2 nop nop noptint return_enable ;4C; internal timer interrupt nop nop nopbrint goto breceive ;50; BSP receive interrupt nop nop nopbxint goto bsend ;54; BSP transmit interrupt nop nop noptrint return_enable ;58; TDM receive interrupt nop nop noptxint return_enable ;5C; TDM transmit interrupt nop nopint3 return_enable ;60; external interrupt int3 nop nop nophpiint dgoto #0e4h ;64; HPIint * DO NOT MODIFY IF USING DEBUGGER * nop nop.space 24*16 ;68-7F; reserved area*********************************************************************** (C) COPYRIGHT TEXAS INSTRUMENTS, INC. 1996 ************************************************************************ ** File: s2k14ini.ASM BSP initialization code for the ‘C54x DSKplus ** for use with 1403 in buffered mode ** BSPC and SPC are the same in the ‘C542 ** BSPCE and SPCE seem the same in the ‘C542 *********************************************************************** .title “Buffered Serial Port Initialization Routine”ON .set 1OFF .set !ON YES .set 1NO .set !YES BIT_8 .set 2BIT_10 .set 1BIT_12 .set 3BIT_16 .set 0GO .set 0x80*********************************************************************** This is an example of how to initialize the Buffered Serial Port (BSP).* The BSP is initialized to require an external CLK and FSX for* operation. The data format is 16-bits, burst mode, with autobuffering * enabled.*1914031fAPPLICATIO S I FOR ATIOW UUU ******************************************************************************************************LTC1403 timing from board with 10MHz crystal.**10MHz, divided from 40MHz, forced to CLKIN by 1403 board. **Horizontal scale is 25ns/chr or 100ns period at BCLKR **Timing measured at DSP pins. Jxx pin labels for jumper cable. **BFSR Pin J1-20 ~~\____/~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~\____/~~~~~~~~~~~**BCLKR Pin J1-14 _/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~\_/~**BDR Pin J1-26 _—_—_—<B13-B12-B11-B10-B09-B08-B07-B06-B05-B04-B03-B02-B01-B00>—_—<B13-B12**CLKIN Pin J5-09 ~~~~~\_______/~~~~~~~\_______/~~~~~~~\_______/~~~~~~~\_______/~~~~~~~\_______/~~~~~**C542 read 0 B13 B12 B11 B10 B09 B08 B07 B06 B05 B04 B03 B02 B01 B00 0 0 B13 B12** ** negative edge BCLKR * negative BFSR pulse * no data shifted* 1' cable from counter to CONV at DUT * 2' cable from counter to CLK at DUT*No right shift is needed to right justify the input data in the main program **the two msbs should also be masked *******************************************************************************************************Loopback .set NO ;(digital looback mode?) DLB bit Format .set BIT_16 ;(Data format? 16,12,10,8) FO bit IntSync .set NO ;(internal Frame syncs generated?) TXM bit IntCLK .set NO ;(internal clks generated?) MCM bit BurstMode .set YES ;(if BurstMode=NO, then Continuous) FSM bit CLKDIV .set 3 ;(3=default value, 1/4 CLOCKOUT)PCM_Mode .set NO ;(Turn on PCM mode?)FS_polarity .set YES ;(change polarity)YES=^^^\_/^^^, NO=___/^\___CLK_polarity .set NO ;(change polarity)for BCLKR YES=_/^, NO=~\_Frame_ignore .set !YES ;(inverted !YES -ignores frame)XMTautobuf .set NO ;(transmit autobuffering)RCVautobuf .set YES ;(receive autobuffering)XMThalt .set NO ;(transmit buff halt if XMT buff is full)RCVhalt .set NO ;(receive buff halt if RCV buff is full)XMTbufAddr .set 0x800 ;(address of transmit buffer)XMTbufSize .set 0x000 ;(length of transmit buffer)RCVbufAddr .set 0x800 ;(address of receive buffer)RCVbufSize .set 0x800 ;(length of receive buffer)works up to 800** See notes in the ‘C54x CPU and Peripherals Reference Guide on setting up * valid buffer start and length values. Page 9-44************************************************************************.eval ((Loopback >> 1)|((Format & 2)<<1)|(BurstMode <<3)|(IntCLK <<4)|(IntSync <<5)) ,SPCval .eval ((CLKDIV)|(FS_polarity <<5)|(CLK_polarity<<6)|((Format &1)<<7)|(Frame_ignore<<8)|(PCM_Mode<<9)), SPCEval.eval (SPCEval|(XMTautobuf<<10)|(XMThalt<<12)|(RCVautobuf<<13)|(RCVhalt<<15)), SPCEval sineinit:bspc = #SPCval ; places buffered serial port in reset ifr = #10h ; clear interrupt flagsimr = #210h ; Enable HPINT,enable BRINT0intm = 0 ; all unmasked interrupts are enabled. bspce = #SPCEval ; programs BSPCE and ABUaxr = #XMTbufAddr ; initializes transmit buffer start address bkx = #XMTbufSize ; initializes transmit buffer sizearr = #RCVbufAddr ; initializes receive buffer start address bkr = #RCVbufSize ; initializes receive buffer sizebspc = #(SPCval | GO) ; bring buffered serial port out of reset return ;for transmit and receive because GO=0xC0Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.。

LTCXX中文资料

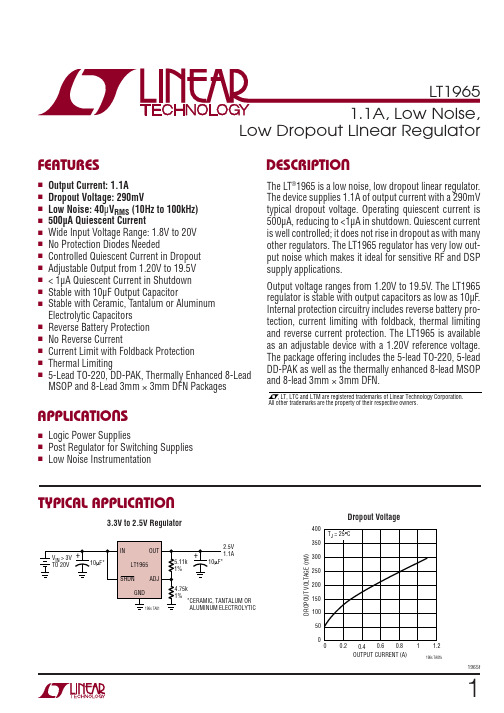

Output Voltage Noise ADJ Pin Bias Current (Notes 4, 9)

ILOAD = 0.5A ILOAD = 1.1A

MSOP and 8-Lead 3mm × 3mm DFN Packages

APPLICATIONS

■ Logic Power Supplies ■ Post Regulator for Switching Supplies ■ Low Noise Instrumentation

DESCRIPTION

, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

TYPICAL APPLICATION

Dropout Voltage

400 TJ = 25°C

350

300

250

200

150

100

50

0 0 0.2 0.4 0.6 0.8 1 1.2

OUTPUT CURRENT (A)

1965 TA01b

1965f

1

元器件交易网

LT1965

ABSOLUTE MAXIMUM RATINGS

TJMAX = 125°C, θJA = 30°C/W

TOP VIEW

OUT 1

8 IN

OUT 2

9

7 IN

ADJ 3

LTC4213 1 4213f 电子电路保护器说明书

2µs/DIV4213 TA01b124213fBias Supply Voltage (V CC )...........................–0.3V to 9V Input VoltagesON, SENSEP, SENSEN.............................–0.3V to 9V I SEL ..........................................–0.3V to (V CC + 0.3V)Output VoltagesGATE .....................................................–0.3V to 15V READY.....................................................–0.3V to 9V Operating Temperature RangeLTC4213C ...............................................0°C to 70°C LTC4213I.............................................–40°C to 85°C Storage Temperature Range.................–65°C to 150°C Lead Temperature (Soldering, 10sec)...................300°CORDER PART NUMBER DDB PART*MARKING T JMAX = 125°C, θJA = 250°C/WEXPOSED PAD (PIN 9)PCB CONNECTION OPTIONALConsult LTC Marketing for parts specified with wider operating temperature ranges.*The temperature grade is identified by a label on the shipping container.LBHVLTC4213CDDB LTC4213IDDB ABSOLUTE AXI U RATI GSW W WU PACKAGE/ORDER I FOR ATIOUUW (Note 1)ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V, I SEL = 0 unless otherwise noted. (Note 2)SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSV CC Bias Supply Voltage ● 2.36V V SENSEP SENSEP Voltage ●06V I CC V CC Supply Current●1.63mA V CC(UVLR)V CC Undervoltage Lockout Release V CC Rising● 1.8 2.07 2.23V ∆V CC(UVHYST)V CC Undervoltage Lockout Hysteresis ●30100160mV I SENSEP SENSEP Input Current V SENSEP = V SENSEN = 5V, Normal Mode 154080µA V SENSEP = V SENSEN = 0, Normal Mode –1±15µA I SENSENSENSEN Input CurrentV SENSEP = V SENSEN = 5V, Normal Mode 154080µA V SENSEP = V SENSEN = 0, Normal Mode –1±15µA V SENSEP = V SENSEN = 5V,50280µAReset Mode or Fault ModeV CBCircuit Breaker Trip Voltage I SEL = 0, V SENSEP = V CC●22.52527.5mV V CB = V SENSEP – V SENSEN I SEL = Floated, V SENSEP = V CC ●455055mV I SEL = V CC, V SENSEP = V CC ●90100110mV V CB(FAST)Fast Circuit Breaker Trip Voltage I SEL = 0, V SENSEP = V CC●63100115mV V CB(FAST)= V SENSEP – V SENSEN I SEL = Floated, V SENSEP = V CC ●126175200mV I SEL = V CC, V SENSEP = V CC ●252325371mV I GATE(UP)GATE Pin Pull Up Current V GATE = 0V●–50–100–150µA I GATE(DN)GATE Pin Pull Down Current ∆V SENSEP – V SENSEN = 200mV, V GATE = 8V ●1040mA ∆V GSMAX External N-Channel Gate Drive V SENSEN = 0, V CC ≥ 2.97V, I GATE = –1µA ● 4.8 6.58V V SENSEN = 0, V CC = 2.3V, I GATE = –1µA ● 2.65 4.38V ∆V GSARMV GS Voltage to Arm Circuit BreakerV SENSEN = 0, V CC ≥ 2.97V ● 4.4 5.47.6V V SENSEN = 0, V CC = 2.3V●2.53.57VTOP VIEWDDB PACKAGE8-LEAD (3mm × 2mm) PLASTIC DFN567894321READY ON I SEL GND V CC SENSEP SENSEN GATE34213f∆V GSMAX – ∆V GSARM Difference Between ∆V GSMAX and V SENSEN = 0, V CC ≥ 2.97V ●0.3 1.1V ∆V GSARMV SENSEN = 0, V CC = 2.3V●0.150.8VV READY(OL)READY Pin Output Low Voltage I READY = 1.6mA, Pull Down Device On ●0.20.4V I READY(LEAK)READY Pin Leakage Current V READY = 5V, Pull Down Device Off ●0±1µA V ON(TH)ON Pin High Threshold ON Rising, GATE Pulls Up ●0.760.80.84V ∆V ON(HYST)ON Pin Hysteresis ON Falling, GATE Pulls Down104090mV V ON(RST)ON Pin Reset Threshold ON Falling, Fault Reset, GATE Pull Down ●0.360.40.44V I ON(IN)ON Pin Input Current V ON = 1.2V●0±1µA ∆V OV Overvoltage Threshold ●0.410.7 1.1V ∆V OV = V SENSEP – V CCt OVOvervoltage Protection Trip Time V SENSEP = V SENSEN = Step 5V to 6.2V 2565160µs t FAULT(SLOW)V CB Trips to GATE Discharging ∆V SENSE Step 0mV to 50mV,●71627µs V SENSEN Falling, V CC = V SENSEP = 5V t FAULT(FAST)V CB(FAST) Trips to GATE Discharging ∆V SENSE Step 0V to 0.3V, V SENSEN Falling,●12.5µs V SENSEP = 5Vt DEBOUNCE Startup De-Bounce Time V ON = 0V to 2V Step to Gate Rising,2760130µs (Exiting Reset Mode)t READY READY Delay Time V GATE = 0V to 8V Step to READY Rising,2250115µs V SENSEP = V SENSEN = 0t OFF Turn-Off Time V ON = 2V to 0.6V Step to GATE Discharging 1.5510µs t ON Turn-On Time V ON = 0.6V to 2V Step to GATE Rising,4816µs (Normal Mode)t RESETReset TimeV ON Step 2V to 0V2080150µsNote 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V, I SEL = 0 unless otherwise noted. (Note 2)SYMBOLPARAMETERCONDITIONSMIN TYP MAX UNITSNote 2: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.4564213ft RESET vs Temperaturet FAULT(SLOW) vs V CCt FAULT(SLOW) vs Temperaturet FAULT(FAST) vs V CCt FAULT(FAST) vs TemperatureTYPICAL PERFOR A CE CHARACTERISTICSU WSpecifications are at T A = 25°C. V CC = 5Vunless otherwise noted.t F A U L T (F A S T ) (µs )4213 G230.90.80.71.01.11.21.3TEMPERATURE (°C)–50050100125–252575BIAS SUPPLY VOLTAGE (V)2.010t F A U L T (S L O W ) (µs )14121618 3.0 4.0 5.0 6.04213 G202022 2.53.54.55.5TEMPERATURE (°C)–500501001254213 G21–25257510t F A U L T (S L O W ) (µs )141216182022TEMPERATURE (°C)–500501001254213 G19–252575t R E S E T (µs )60708090100BIAS SUPPLY VOLTAGE (V)2.0t F A U L T (F A S T ) (µs )3.04.05.06.04213 G222.53.54.55.50.90.80.71.01.11.21.374213fPI FU CTIO SU U UREADY (Pin 1): READY Status Output. Open drain output that goes high impedance when the external MOSFET is on and the circuit breaker is armed. Otherwise this pin pulls low.ON (Pin 2): ON Control Input. The LTC4213 is in reset mode when the ON pin is below 0.4V. When the ON pin increases above 0.8V, the device starts up and the GATE pulls up with a 100µA current source. When the ON pin drops below 0.76V, the GATE pulls down. To reset a circuit breaker fault, the ON pin must go below 0.4V.I SEL (Pin 3): Threshold Select Input. With the I SEL pin grounded, float or tied to V CC the V CB is set to 25mV, 50mV or 100mV, respectively. The corresponding V CB(FAST)values are 100mV, 175mV and 325mV.GND (Pin 4): Device Ground.GATE (P in 5): GATE D rive Output. An internal charge pump supplies 100µA pull-up current to the gate of the external N-channel MOSFET. Internal circuitry limits thevoltage between the GATE and SENSEN pins to a safe gate drive voltage of less than 8V. When the circuit breaker trips, the GATE pin abruptly pulls to GND.SENSEN (Pin 6): Circuit Breaker Negative Sense Input.Connect this pin to the source of the external MOSFET.During reset or fault mode, the SENSEN pin discharges the output to ground with 280µA.SENSEP (P in 7): Circuit Breaker Positive Sense Input.Connect this pin to the drain of external N-channel MOSFET.The circuit breaker trips when the voltage across SENSEP and SENSEN exceeds V CB . The input common mode range of the circuit breaker is from ground to V CC + 0.2V when V CC < 2.5V. For V CC ≥ 2.5V, the input common mode range is from ground to V CC + 0.4V.V CC (Pin 8): Bias Supply Voltage Input. Normal operation is between 2.3V and 6V. An internal under-voltage lockout circuit disables the device when V CC < 2.07V.Exposed Pad (Pin 9): Exposed pad may be left open or connected to device ground.8910114213fsupply transient dips below 1.97V of less than 80µs are ignored.ON FunctionWhen V ON is below comparator COMP1’s threshold of 0.4V for 80µs, the device resets. The system leaves reset mode if the ON pin rises above comparator COMP2’s threshold of 0.8V and the UVLO condition is met. Leaving reset mode, the GATE pin starts up after a t DEBOUNCE delay of 60µs. When ON goes below 0.76V, the GATE shuts off after a 5µs glitch filter delay. The output is discharged by the external load when V ON is in between 0.4V to 0.8V. At this state, the ON pin can re-enable the GATE if V ON exceeds 0.8V for more than 8µs. Alternatively, the device resets if the ON pin is brought below 0.4V for 80µs. Once reset, the GATE pin restarts only after the t DEBOUNCE 60µs delay at V ON rising above 0.8V. To protect the ON pin from overvoltage stress due to supply transients, a series resistor of greater than 10k is recommended when the ON pin is connected directly to the supply. An external resis-tive divider at the ON pin can be used with COMP2 to set a supply undervoltage lockout value higher than the inter-nal UVLO circuit. An RC filter can be implemented at the ON pin to increase the powerup delay time beyond the internal 60µs delay.Gate FunctionThe GATE pin is held low in reset mode. 60µs after leaving reset mode, the GATE pin is charged up by an internal 100µA current source. The circuit breaker arms when V GATE > V SENSEN + ∆V GSARM . In normal mode operation,the GATE peak voltage is internally clamped to ∆V GSMAX above the SENSEN pin. When the circuit breaker trips, an internal MOSFET shorts the GATE pin to GND, turning off the external MOSFET.READY StatusThe READY pin is held low during reset and at startup. It is pulled high by an external pullup resistor 50µs after the circuit breaker arms. The READY pin pulls low if the circuit breaker trips or the ON pin is pulled below 0.76V, or V CC drops below undervoltage lockout.∆V GSARM and V GSMAXEach MOSFET has a recommended V GS drive voltage where the channel is deemed fully enhanced and R DSON is minimized. Driving beyond this recommended V GS volt-age yields a marginal decrease in R DSON . At startup, the gate voltage starts at ground potential. The GATE ramps past the MOSFET threshold and the load current begins to flow. When V GS exceeds ∆V GSARM , the circuit breaker is armed and enabled. The chosen MOSFET should have a recommended minimum V GS drive level that is lower than ∆V GSARM . Finally, V GS reaches a maximum at ∆V GSMAX.Trip and Reset Circuit BreakerFigure 2 shows the timing diagram of V GATE and V READY after a fault condition. A tripped circuit breaker can be reset either by cycling the V CC bias supply below UVLO thresh-old or pulling ON below 0.4V for >t RESET . Figure 3 shows the timing diagram for a tripped circuit breaker being reset by the ON pin.Calculating Current LimitThe fault current limit is determined by the R DSON of the MOSFET and the circuit breaker voltage V CB .I V R LIMIT CB DSON=()2The R DSON value depends on the manufacturer’s distribu-tion, V GS and junction temperature. Short Kelvin-sense connections between the MOSFET drain and source to the LTC4213 SENSEP and SENSEN pins are strongly recommended.For a selected MOSFET, the nominal load limit current is given by:I V R LIMIT NOM CB NOM DSON NOM ()()()()=3The minimum load limit current is given by:I V R LIMIT MIN CB MIN DSON MAX ()()()()=4APPLICATIO S I FOR ATIOW UUU1213144213fOperating temperature of 0° to 70°C.R DSON @ 25°C = 100%R DSON @ 0°C = 90%R DSON @ 70°C = 120%MOSFET resistance variation:R DSON(NOM) = 15m • 0.82 = 12.3m ΩR DSON(MAX) = 15m • 1.333 • 0.93 • 1.2 = 15m • 1.488= 22.3m ΩR DSON(MIN) = 15m • 0.667 • 0.80 • 0.90 = 15m • 0.480= 7.2m ΩV CB variation:NOM V CB = 25mV = 100%MIN V CB = 22.5mV = 90%MAX V CB = 27.5mV = 110%The current limits are:I LIMIT(NOM) = 25mV/12.3m Ω = 2.03A I LIMIT(MIN) = 22.5mV/22.3m Ω = 1.01A I LIMIT(MAX) = 27.5mV/7.2m Ω = 3.82AFor proper operation, the minimum current limit must exceed the circuit maximum operating load current with margin. So this system is suitable for operating load current up to 1A. From this calculation, we can start with the general rule for MOSFET R DSON by assuming maxi-mum operating load current is roughly half of the I LIMIT(NOM). Equation 7 shows the rule of thumb.I V R OPMAX CB NOM DSON NOM =()()•()27Note that the R DSON(NOM) is at the LTC4213 nominal operating ∆V GSMAX rather than at typical vendor spec.Table 1 gives the nominal operating ∆V GSMAX at the various operating V CC . From this table users can refer to the MOSFET’s data sheet to obtain the R DSON(NOM) value.Table 1. Nominal Operating ∆V GSMAX for Typical Bias Supply VoltageV CC (V)∆V GSMAX (V)2.3 4.32.5 5.02.7 5.63.0 6.53.37.05.07.06.07.0Load Supply Power-Up after Circuit Breaker Armed Figure 4 shows a normal power-up sequence for the circuit in Figure 1 where the V IN load supply power-up after circuit breaker is armed. V CC is first powered up by an auxiliary bias supply. V CC rises above 2.07V at time point 1. V ON exceeds 0.8V at time point 2. After a 60µs debounce delay, the GATE pin starts ramping up at time point 3. The external MOSFET starts conducting at time point 4. At time point 5, V GATE exceed ∆V GSARM and the circuit breaker is armed. After 50µs (t READY delay), READY pulls high by an external resistor at time point 6. READY signals the V IN load supply module to start its ramp. The load supply begins soft-start ramp at time point 7. The load supply ramp rate must be slow to prevent circuit breaker tripping as in equation (8).∆∆V t I I C IN OPMAX LOADLOAD<−()8Where I OPMAX is the maximum operating current defined by equation 7.For illustration, V CB = 25mV and R DSON = 3.5m Ω at the nominal operating ∆V GSMAX . The maximum operating current is 3.5A (refer to equation 7). Assuming the load can draw a current of 2A at power-up, there is a margin of 1.5A available for C LOAD of 100µF and V IN ramp rate should be <15V/ms. At time point 8, the current through the MOSFET reduces after C LOAD is fully charged.APPLICATIO S I FOR ATIOW UUU1516174213fThe selected MOSFET V GS absolute maximum rating should meet the LTC4213 maximum ∆V GSMAX of 8V.Other MOSFET criteria such as V BDSS , I DMAX , and R DSON should be reviewed. Spikes and ringing above maximum operating voltage should be considered when choosing V BDSS . I DMAX should be greater than the current limit. The maximum operating load current is determined by the R DSON value. See the section on “Calculating Current Limit” for details.Supply RequirementsThe LTC4213 can be powered from a single supply or dual supply system. The load supply is connected to the SENSEP pin and the drain of the external MOSFET. In the single supply case, the V CC pin is connected to the load supply, preferably with an RC filter. With dual supplies,V CC is connected to an auxiliary bias supply V AUX where V AUX voltage should be greater or equal to the load supply voltage. The load supply voltage must be capable of sourcing more current than the circuit breaker limit. If the load supply current limit is below the circuit breaker trip current, the LTC4213 may not react when the output overloads. Furthermore, output overloads may trigger UVLO if the load supply has foldback current limit in a single supply system.V IN Transient and Overvoltage ProtectionInput transient spikes are commonly observed whenever the LTC4213 responds to overload. These spikes can be large in amplitude, especially given that large decoupling capacitors are absent in hot swap environments. These short spikes can be clipped with a transient suppressor of adequate voltage and power rating. In addition, the LTC4213can detect a prolonged overvoltage condition. WhenAPPLICATIO S I FOR ATIOW UUU point 6 should be within the circuit breaker limits. Other-wise, the system fails to start and the circuit breaker trips immediately after arming. In most applications additional external gate capacitance is not required unless C LOAD is large and startup becomes problematic. If an external gate capacitor is employed, its capacitance value should not be excessive unless it is used with a series resistor. This is because a big gate capacitor without resistor slows down the GATE turn off during a fault. An alternative method would be a stepped I SEL pin to allow a higher current limit during startup.In the event of output short circuit or a severe overload, the load supply can collapse during GATE ramp up due to load supply current limit. The chosen MOSFET must withstand this possible brief short circuit condition before time point 6 where the circuit breaker is allowed to trip. Bench short circuit evaluation is a practical verification of a reliable design. To have current limit while powering a MOSFET into short circuit conditions, it is preferred that the load supply sequences to turn on after the circuit breaker is armed as described in an earlier section.Power-Off CycleThe system can be powered off by toggling the ON pin low.When ON is brought below 0.76V for 5µs, the GATE and READY pins are pulled low. The system resets when ON is brought below 0.4V for 80µs.MOSFET SelectionThe LTC4213 is designed to be used with logic (5V) and sub-logic (3V) MOSFETs for V CC potentials above 2.97V with ∆V GSMAX exceeding 4.5V. For a V CC supply range between 2.3V and 2.97V, sub-logic MOSFETs should be used as the minimum ∆V GSMAX is less than 4.5V.1819Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.201630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2005LT/TP 0405 500 • PRINTED IN USA。

LTC1143资料

PACKAGE/ORDER INFORMATION

TOP VIEW SENSE+3 1 16 SENSE– 3

ORDER PART NUMBER LTC1143CS LTC1143LCS

SHUTDOWN 3 2 GND3 3 P-DRIVE 3 4 VIN5 5 CT5 6 ITH5 7 SENSE–5 8

s s

Dual Outputs LTC1143, LTC1143L: 3.3V, 5V LTC1143L-ADJ: Dual Adjustable Very High Efficiency: Over 95% Possible Current Mode Operation for Excellent Line and Load Transient Response High Efficiency Maintained over Three Decades of Output Current Low Standby Current at Light Loads: 160µA/Output Logic-Controlled Shutdown (LTC1143, LTC1143L) Wide VIN Range: 3.5V to 16V (LTC1143L, LTC1143L-ADJ) Very Low Dropout Operation: 100% Duty Cycle Available in Narrow 16-Pin SO Package

VOUT1 3.3V/2A

RSENSE1 0.05Ω

L1 27µH

+

R2 82.5k 1%

16 D1 MBRS320T3 2 100pF

SENSE – 1

VFB1 GND1 3 CT1 14 ITH1 15 RC1 1k CC1 CC2 3300pF 3300pF ITH2 7 RC2 1k CT2 300pF CT2 6

常用集成芯片

常用芯片作用2007-07-30 16:40mc2831(mc2833)低功耗FM发射机mc3362低功耗FM接收机CXA1691BM收音机FM/AM接收芯片双音频编码器件是HM9187,解码芯片是MT8870(注意:HM9187输出的双音频信号幅值太大了,串联一个160K的电阻,送到M 幅度,幅度过高会导致窄带FM的调制/解调出问题.)ICL8038 单片集成压控波形发生器(应用广泛),在0.01~300kHz的范围里可以同时产生正弦波、矩形波和三角波。

使用时只作为压控振荡器、调频信号发生器或单片函数发生器。

其输出电平特性为:方波0.2V suppl y(2mA);三角波幅度为0.33V suppl y,输出阻22V supply,输出阻抗典型值为1kΩ。

MC145151 -2 锁相环芯片,是MC145151-1的性能改进产品,功耗降低而ESD和锁定性能则大有改进。

MC145151-2分别用N计数器和R计数器编程。

本器件集成了参考振荡器、可选参考频率分频器、数字相位鉴相器和14位可编程的除N计数器。

该芯工艺而具有低功耗,电压范围为3~9V;具有片上或离片参考振荡器的操作条件;有两路鉴相信号输出,其中PD out是鉴相器A的是鉴相误差信号,LD用来输出相位锁定信号;除N的范围为3~16383;8个用户可选的除R值分别为8、128、256、512、1应RA2~RA0从000到111的8个状态。

1.音频pcm编码DA转换芯片cirrus logic的cs4344,cs4334 。

4334是老封装,据说已经停产,4344封装比较小,非常好用2.音频放大芯片4558,LM833,5532,此二芯片都是双运放。

3.244和245,由于244是单向a=b的所以只是单向驱动。

而245是用于数据总线等双向驱动选择。

同时245的封装走线非常适4.373和374,地址锁存器,5.max232和max202,max3232 TTL电平转换6.网络接口变压器。

2SB1386中文资料(secos)中文数据手册「EasyDatasheet - 矽搜」

V I /I = -4A/-0.1A

*

V = -2V, I = -0.5A

*

MHz V = -6V, I = -50mA, f=30MHz

pF V = -20V, I =0, f=1MHz

10-Dec-2010 版本B

第1页3

芯片中文手册,看全文,戳 特性曲线

转换频率 输出电容

*测量

采用脉冲电流.

(T A = 25°C除非另有说明)

符号

V V V

I I V h f C

Min.

Typ.

-30

-

-20

-

-6

-

-

-

-

-

-

-

82

-

-

120

-

60

Max.

-0.5 -0.5 -1.0 390 -

单元

测试条件

V IC=-50µA

V I = -1mA

V I = -50µA

2SB1386

-5A, -30V PNP硅低频晶体管

10-Dec-2010 版本B

分页:1 2 3

芯片中文手册,看全文,戳 特性曲线

2SB1386

-5A, -30V PNP硅低频晶体管

10-Dec-2010 版本B

第3页3

(T A = 25°C除非另有说明)

符号

额定值

V

-30

V

-20

V

-6

I

-5 -10

P

0.5 2

T ,T

150, -55~150

单元 V V V

A(DC) A(脉冲)

W

°C

ltisim元器件中文与英文对照表

ltisim元器件中文与英文对照表1。

Source库:包括电源、信号电压源、信号电流源、可控电压源、可控电流源、函数控制器件6个类。

?2。

BASIC库:包含基础元件,如电阻、电容、电感、二极管、三极管、开关等;?3。

Diodes:二极管库,包含普通二极管、齐纳二极管、二极管桥、变容二极管、PIN二极管、发光二极管等。

?4。

Transisitor库:三极管库,包含NPN、PNP、达林顿管、IGBT、MOS管、场效应管、可控硅等;?5。

Analog库:模拟器件库,包括运放、滤波器、比较器、模拟开关等模拟器件?6。

TTL库:包含TTL型数字电路如7400 7404等门BJT电路。

?7。

COMS库:COMS型数字电路如74HC00 74HC04等MOS管电路。

?8。

MCU Model:MCU模型,Multisim的单片机模型比较少,只有8051 PIC16的少数模型和一些ROM RAM等?9。

Advance Periphearls库:外围器件库,包含键盘、LCD、和一个显示终端的模型。

?10。

MIXC Digital:混合数字电路库,包含DSP、CPLD、FPGA、PLD、单片机-微控制器、存储器件、一些接口电路等数字器件。

?11。

Mixed:混合库,包含定时器、AC/DA转换芯片、模拟开关、震荡器等;?12。

Indicators:指示器库,包含电压表、电流表、探针、蜂鸣器、灯、数码管等等显示器件。

?13。

Power:电源库,包含保险丝、稳压器、电压抑制、隔离电源等?14。

Misc:混合库,包含晶振、电子管、滤波器、MOS驱动、和其他一些器件等?15。

RF:RF库,包含一些RF器件,如高频电容电感、高频三极管等?16。

Elector Mechinical:电子机械器件库,包含传感开关、机械开关、继电器、电机等。

Proteus 元件名称对照1元件名称中文名说明?7407 驱动门?1N914 二极管?74Ls00 与非门?74LS04 非门?74LS08 与门?74LS390 TTL 双十进制计数器?7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码?7SEG 3-8译码器电路BCD-7SEG[size=+0]转换电路?ALTERNATOR 交流发电机?AMMETER-MILLI mA安培计?AND 与门?DCPOWER 电池/电池组?BUS 总线?CAP 电容?CAPACITOR 电容器?CLOCK 时钟信号源?CRYSTAL 晶振?D-FLIPFLOP D触发器?FUSE 保险丝?GROUND 地?LAMP 灯?LED-RED 红色发光二极管?LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN 三个控制端口(共14线),工作电压为5V。

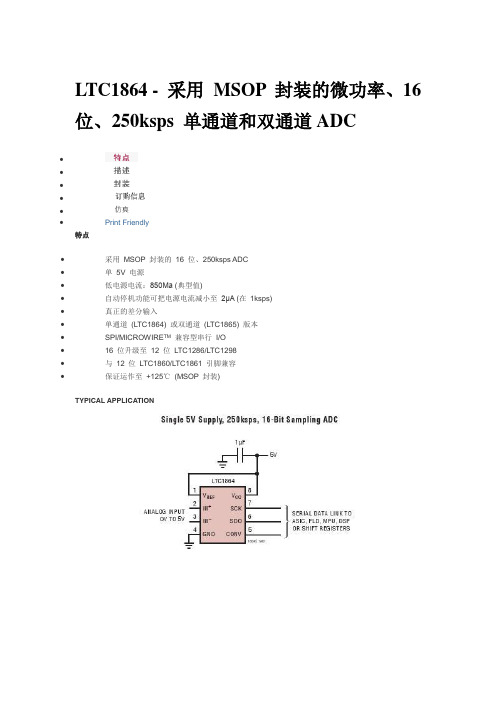

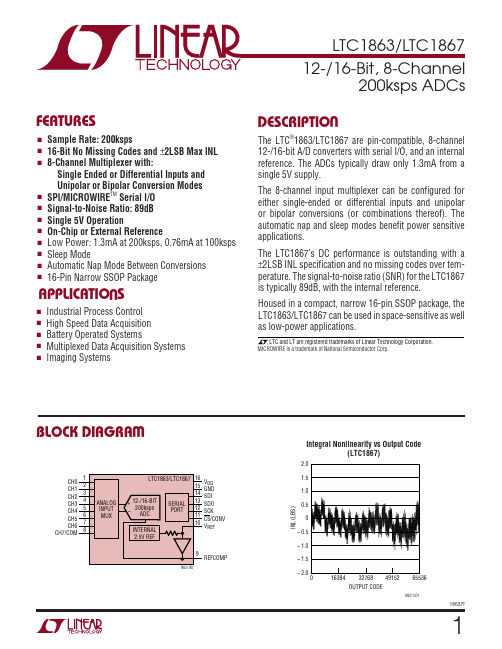

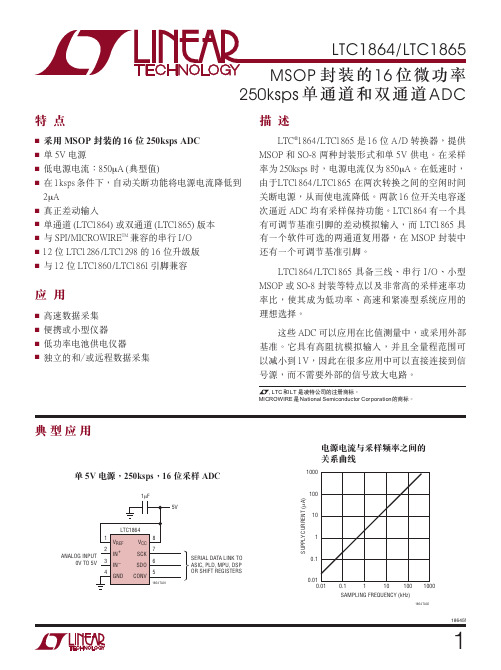

LTC1864

LTC1864 - 采用MSOP 封装的微功率、16 位、250ksps 单通道和双通道ADC••••••Print Friendly特点•采用MSOP 封装的16 位、250ksps ADC•单5V 电源•低电源电流:850Μa (典型值)•自动停机功能可把电源电流减小至2μA (在1ksps)•真正的差分输入•单通道(LTC1864) 或双通道(LTC1865) 版本•SPI/MICROWIRE TM兼容型串行I/O•16 位升级至12 位LTC1286/LTC1298•与12 位LTC1860/LTC1861 引脚兼容•保证运作至+125℃(MSOP 封装)TYPICAL APPLICATIONBACK TO TOP描述LTC®1864/LTC1865 是采用MSOP 和SO-8 封装的16 位A/D 转换器,采用单5V工作电源。

在250ksps 采样速率条件下,电源电流仅为850μA。

在较低的速度下,电源电流将减小,原因是LTC1864/LTC1865 在转换操作之间自动断电。

这些16 位开关电容器逐次逼近型ADC 包括采样及保持电路。

LTC1864 具有一个差分模拟输入和一个可调基准引脚。

LTC1865 提供了一个可利用软件来选择的双通道MUX 和一个可调基准引脚(在MSOP 封装版本上)。

三线式串行I/O、小外形MSOP 或SO-8 封装、以及极高的采样速率与功率之比使得这些ADC 非常适合于紧凑、低功率、高速系统。

这些ADC 可在比例式应用中使用,或与外部基准一起使用。

高阻抗模拟输入以及可在缩减的电压范围内(低至1V 全标度) 运作的能力使得它们在许多应用中可与信号源直接相连,从而免除了增设外部增益级的需要。

BACK TO TOP封装SO-8, MSOP-8BACK TO TOP订购信息•以PBF 结尾的器件型号表示这些是无铅型器件。

如需了解有关含铅涂层器件的信息,请与凌力尔特公司联系。

IS1684S芯片数据手册原厂资料数据表datasheet

Preliminary DatasheetIS1684S Bluetooth 3.0(EDR) Multimedia SOC1. General DescriptionISSC IS1684S is a compact, high integration, ultra-low cost, CMOS single-chip RF + baseband IC for Bluetooth v3.0(EDR) (Enhanced Data Rate) 2.4GHz applications. This chip is fully compliant with Bluetooth specification and completely backward-compatible with Bluetooth 1.1, 1.2, 2.0 or 2.1 systems.It incorporates Bluetooth 1M/2M/3Mbps RF, single-cycle 8051, TX/RX modem, memory controller, task/hopping controller, UART interface, and ISSC Bluetooth software stack to achieve the required Bluetooth v3.0(EDR) functions.The IS1684S is designed to support high quality audio applications, an audio engine and a high performance stereo DAC are integrated for this purpose.The audio engine supports the SBC audio decoding and equlizer to offer the best audio quality.In addition, to minimize the external components required for portable devices, a voltage sensor for battery, Li-ion battery charger, a switching regulator and LDOs are integrated to reduce BOM cost for various Bluetooth applications.The device incorporates built-in self-test (BIST) and auto-calibration functions to simplify production test.2. FeaturesSystem Specification•Compliant with Bluetooth Specification v.3.0 (EDR) in 2.4 GHz ISM bandBaseband Hardware•16MHz main clock input•Built-in internal ROM for program memory•Built-in 32 KB RAM for data storage and baseband data transfer buffering•Enhanced Power Control•Bluetooth 2.1 featureso Encryption Pause and Resumeo Erroneous Data Reportingo Extended Inquiry Responseo Link Supervision Timeout Changed Evento Non-Flushable Packet Boundary Flago Secure Simple Pairingo Sniff Subtracting•Support both Pico-net and Scatter-net applications•Hard-wired logic for modulation, demodulation, access code correlation, whitening, forward error correction (FEC), header error check (HEC), shorten hamming code, CRC generation/checking, frame check sequence (FCS), encryption bit stream generation, and transmit pulse shaping•Adaptive Frequency Hopping (AFH) avoids occupied RF channels•Fast Connection supportedRF Hardware•Fully Bluetooth 3.0 (EDR) system in 2.4 GHz ISM band.•Combined TX/RX RF terminal simplifies external matching and reduces external antenna switches.•Max. +4dBm output power with 20 dB level control from register control.•Build-in T/R switch for Class 2/3 application•Build-in channel filter.•To avoid temperature variation, temperature sensor with temperature calibration is utilized into bias current and gain control.•Fully integrated synthesizer has been created. There requires no external VCO, varactor diode, resonator and loop filter.•Crystal oscillation with build-in digital trimming for temperature/process variations.Audio processor•SBC decoding•Packet error concealmentAudio Codec•16 bit stereo codec•94dB SNR DAC playback•Integrate headphone amplifier for 16Ω speakersPeripherals•Built-in Lithium-ion battery charger•Integrate 3V, 1.8V LDO and Switching mode regulator•Built-in 10-bit Aux-ADC for battery monitor and voltage sense.•LED driverFlexible HCI interface•High speed HCI-UART (Universal Asynchronous Receiver Transmitter) interfacePackage•7x7mm2 56 pins, 0.4mm pitch SAW QFN standard package3.Functional Diagram5 Pin DescriptionsPin No. I/O Pin Name Pin Descriptions23 P SAR_AVDD SAR 1.8V input24 P SYS_PWR System Power Output25 P BK_VDD Buck VDD Power Input26 P BK_LX Buck feedback input27 P BK_GND Buck Ground28 P BK_OUT Buck output29 P MFB Multi-Function Push Button key, push high30 AI LED1 LED Driver 131 AI LED2 LED Driver 232 I/O P2_4 GPIO, default pull-high inputKEY PIN for FT TestSystem Configuration, H: Boot Mode33 I/O P2_2 GPIO, default pull-low input.Keep alive for external LDO power enable application.34 I/O P0_2 GPIO, default pull-high inputPlay/Pause key as the default setting35 I/O P2_7 GPIO, default pull-high inputFWD key when class 2 RFFWD key(short press) when class 1 RF36 I/O P0_5 GPIO, default pull-high inputKEY PIN for FT TestREV key when class 2 RFREV key(short press) when class 1 RF37 O HCI_TXD KEY PIN for FT Test HCI TX data38 I HCI_RXD KEY PIN for FT Test HCI RX data39 I/O P1_6 GPIO P1_6, default pull-high input Volume down key when class 2 RF Audio AMP Enable when class 1 RF40 P VDD_IO I/O power supply input41 I XO_P 16MHz Crystal input positivePin No. I/O Pin Name Pin Descriptions42 I XO_N 16MHz Crystal input negative43 RP VCC_RF RF power input for both synthesizer and TX/RX block44 I RX_CLASS1 Class1 RF RX path45 I/O RTX Class2 RTX path; Class1/Class2 TX path46 I/O P0_1 GPIO, default pull-high inputVolume up key when class 2 RF.Class1 Control signal of external TR switch when class 1 RF47 I/O P0_3 GPIO, default pull-high inputKEY PIN for FT TestUART RX_IND when class 2 RFClass1 Control signal of external TR switch when class 1 RF48 I/O P3_0 GPIO, default pull-high input Line-in Detector (Low Active)49 I/O P2_0 GPIO, default pull-high inputKEY PIN for FT TestSystem Configuration, H: Application L: Baseband(IBDK Mode)50 I/O P0_0 GPIO, default pull-low input.KEY PIN for FT TestSlide Switch Detector/TX_IND when class 2 RF51 I/O P0_4 GPIO, default pull-high inputAudio AMP Enable when class 2 RF52 P VDD_IO I/O power supply input53 I/O P3_5 GPIO 3_5, default pull-high input. Buzzer Signal Output54 I EAN Embedded ROM/External Flash enable H: Embedded; L: External Flash55 P 1V8 Core 1.8V power input56 AO AOHPR R-channel single ended analog headphone output57 P GND Exposed pad as groundApplication Note for GPIO Setting:1) KEY PIN for FT TestHCI_RXD, HCI_TXD, RST_N, P2_0, P2_4, P1_3, P1_2, P0_3, P0_5, P0_02) For Class2 RF application: VOL+:P0_1, VOL-: P1_6, FWD:P2_7, REV:P0_5, AUDIOAMP ENABLE: P0_43) For Class1 RF application: VOL+:P2_7(Long Press), VOL-: P0_5(Long Press),FWD:P2_7(Short Press) , REV: P0_5(Short Press) , AUDIO AMP ENABLE: P1_64) Play/Pause: P0_25) P1_2:EEPROM Clock/Clock Signal for OLED(5028-202 not support)P1_3:EEPROM Data/Data Signal for OLED(5028-202 not support)6) SLIDE SWITCH DETECT: P0_07) Buzzer Signal Output: P3_58) CLASS 1 RF TX: P0_1, CLASS 1 RF RX: P0_39) External LDO power enable keep alive: P2_210) S ystem Configuration: P2_0, P2_411) P0_0/P0_3 are used as TX_IND/RX_IND of UART control in MCU application6 Functional Description6.1 Overall ArchitectureThe ISSC IS1684S integrates an enhanced EDR Bluetooth RF & BB core, HCI controller, audio engine and an ENHANCED 8051 processor with an internal mask ROM for program memory and SRAM for data memory. An innovative interconnection structure called the Common-Memory Architecture (CMA) is designed to provide a fast and flexible data movement scheme between the embedded processor, Bluetooth core, and peripheral hardware.For audio application and power management, IS1684S has build-in an audio processor, mono codec and power management unit to reduce the external components.6.2 Radio Frequency (RF)6.2.1 TransmitterThe internal PA has a maximum output power of +4dBm with level control 20dB from amplitude control. This is applied into Class 2/3 radios without external RF PA. For Class1 application, the build-in level control can be used with external PA for power control requirement.The transmitter features IQ direct conversion to minimize the frequency drift. And it can excess 30dB power range with temperature compensation machine.6.2.2 ReceiverThe LNA can be operated into two type modes. One type is TR-combined mode for single port application. The other type is TR-separated mode for external PA/LNA application.An ADC is used to sample input analogue wave for digital demodulation. Before the ADC, a channel filter has been integrated into receiver channel to increase the anti-interference capacity and also reduce the external component count.For avoiding temperature variation issues, a temperature sensor with temperature calibration is utilized into bias current and gain control of LNA, Mixers, and RF AMP.6.2.3 SynthesizerThe internal loop filter is used to reduce external RC components. This can reduce cost and variations for components. This internal LC tank for VCO is utilized to reduce variation for components. The cost is down at the same time.A fully integrated synthesizer has been created. There requires no external VCO, varactor diode, resonator and loop filter.6.3 MODEMThere are three different modulations for Bluetooth v3.0 (EDR). Table 6.3 summarizes these modulations and data rate.Figure 6.3 Modulation type for Bluetooth v3.0 (EDR)Data Rate Modulation Bits/SymbolBDR: 1 Mbps GFSK 1EDR: 2 Mbps π/4 DQPSK 2EDR: 3 Mbps 8DPSK 36.3.1 Basic Data Rate MODEM (BDR)On the Bluetooth v1.2 specification and below, 1 Mbps was the standard data rate based on Gaussian Frequency Shift Keying (GFSK) modulation scheme. This basic rate modem meets BDR requirements of Bluetooth v3.0(EDR) specification.Figure 6.3.1 Data format for BDRAccess Code Header Payload6.3.2 Enhanced Data Rate MODEM (EDR)On the Bluetooth v3.0(EDR) specification, Enhanced Data Rate (EDR) has been introduced to provide 2 and 3 Mbps data rates as well as 1 Mbps. This enhanced data rate modem meets EDR requirements of Bluetooth v3.0(EDR) specification. For the viewpoint of baseband, both BDR and EDR utilize the same 1MHz symbol rate and 1.6 KHz slot rate. For BDR, 1 symbol represents 1 bit. However each symbol in the payload part of EDR packets represents 2 or 3 bits. This is achieved by using two different modulations, π/4 DQPSK and 8DPSK.Figure 6.3.2.A Data format for EDRAccess Code Header Guard Sync Payload TrailerFor π/4 DQPSK modulation, each symbol carries 2 bits of information. For its constellation diagram, although there are 8 possible phase states, the encoding scheme guarantees the trajectory of the modulation between symbols is restricted to 4 states. For a given startingpoint, every phase change between symbols is restricted to +45°, +135°, -45°, and -135°.Figure 6.3.2.B Phase shift & bit pattern for 2 MHz data ratePhase Shift Bit Pattern+45° (+π/4) 00+135° (+3π/4) 01-135°(-3π/4) 11-45°(-π/4) 10For 8DPSK modulation, each symbol carries 3 bits of information. For its constellation diagram, it is similar toπ/4 DQPSK but the trajectory of the modulation between symbols has 8 possible phase states. For a given starting point, every phase change between symbols is restricted to 0°, +45°, +90°, +135°, +180°, -135°, -90°, and -45°.Figure 6.3.2.C Phase shift & bit pattern for 3 MHz data ratePhase Shift Bit Pattern0° (+0) 000+45° (+π/4) 001+90° (+π/2) 011+135° (+3π/4) 010+180° (+π) 110-135° (-3π/4) 111-90° (-π/2) 101-45° (-π/4) 1006.4 BasebandThe following modules implemented in hardware constitute the Bluetooth Baseband Core. The frequency hopping sequence generator produces the correct hop frequency control sequence based on the Bluetooth clock, Bluetooth device address, and the current operating mode.The access code generates the access code based on the Lower Address Part (LAP) of the Bluetooth device address. The access code is comprised of the preamble, sync word and trailer bits. The detection of the access code uses correlation to detect a valid access code.Bluetooth uses two types of FEC: 1/3 repetition code and (15, 10) shorten Hamming code respectively. The former basically repeats each transmitted bit three times while the latter has 15 bits of codeword which contains 5 parity bits. The code has capability of correction of all single-bit errors in each codeword.The purpose of HEC is to protect the header bits. Dedicated header error code generator calculates the HEC bits in the header of a transmitted packet. While on the receiver side, HEC detects corrupted headers.A 16-bit CRC is adopted to protect payload data transmitted using certain types of Bluetooth packets.Information confidentiality can be protected by encryption of the packet payload. Dedicated encryption/decryption hardware is designed into the baseband core.6.5 MCUThe embedded processor for IS1684S is a single-cycle 8051 CPU. The embedded processor will be referred to as simply the processor, 8051, or MCU throughout the remainder of this document. There are a few minor differences between a standard 8051 and this CPU. These include:1. Alteration of memory timings to match internal and external memoryconfigurations.2. Modification of idle mode to disable internal CPU clocking. Onlyexternally-clocked interrupt sources can allow the CPU to recover from idle mode.A single-port synchronous interface is provided to memory. From this single port, the bandwidth is divided among the 7 interfaces spread amongst 5 physical busses described below:•Embedded processor bus•Baseband TX bus•Baseband RX bus•HCI TX bus•HCI RX bus•Audio bus•DMA busIn addition, attached to the embedded processor bus are a register bank, a dedicated single-port memory (data segment 1), and flash memory (program segment). The processor coordinates all link control procedures and data movement using a set of pointer registers. For example, when an HCI packet (from the host via USB or UART) is received into the HCI buffer, the processor is interrupted. The processor can then read astatus register to determine the HCI packet type and determine whether to set up the Baseband pointer registers for this memory region for RF-retransmission, or to otherwise directly perform packet processing with the CPU.6.6 Bluetooth Clock and TimersA Bluetooth standard 28-bit counter running at 3.2 kHz implements the native clock defined by Bluetooth specification. This clock provides the transmission and receiving timing of a half time slot (312.5 µs). Another finer counter implemented in 16 bits is also provided as the phase of a half time slot. This phase information is very helpful when a Bluetooth slave wants to adapt to its master’s clock. The counter is pre-scalable for the purpose of power saving operations. The diagram below describes a standard Bluetooth native clock and master clock. The clock signal is also used as a slot boundary signal to trigger a baseband packet transmission or receipt.There are several timers provided by the system, two timers for TX/RX and the others for general purpose.The powerful pre-scheduling functions for the transceiver are realized different sets of programmable timers. Each set of timers is associated with the task of transmission or receiving. When the timer is configured by firmware, it will automatically execute the TX or RX task at a specific time. Sub-tasks and timing for a TX task remain to be defined.Figure 6.6 Bluetooth clock6.7 HCI Control Logic for USB/UARTHardwired control logic is presented in front of the UART devices for HCI protocol handling and packet buffering. This control logic is part of the HCI controller defined in Bluetooth specification 1.2. This logic is partially responsible for the HCI protocol handling to/from the host and it also maps the registers of the UART devices indirectly to the 8051 such that the system can receive or send a HCI packet to/from the respective host interface. Major functions of this logic include:•HCI packet formatter and de-formatter (identifying the packet type)•Frame boundary determination, segmentation and reassembly of HCI packets.•HCI packet transmission, receiving, and buffering (using common memory HCI buffer).•Independent receive / transmit channels•Universal device interface6.7.1 HCI UART InterfaceAn embedded HCI UART (Universal Asynchronous Receiver Transmitter) with programmable data rate up to 3Mbps is included in this design. The HCI UART supports the following functions:•Full-Duplex operation•Programmable BAUD rate (using 16-bit input clock divider to obtain Baud Rate x16 or x24 or x13 clock base)•7 or 8 Data bits• 1 or 2 Stop bits•Even / Odd / Mark / Space / None Parity configurations•Break Generation / Detection•Maskable individual interrupts to CPU and combined Error interrupt to HCI•Selectable Direct CPU interface or interface to HCI module6.8 General Purpose I/OThe IS1684S provides 15 general purpose I/O ports. These general I/Os can be defined as input or output port individually by setting specific register bit. While setting as an input port, a build-in 50KΩpull high or pull low resistor can be enabled for different application purpose.6.9 Audio ProcessorThe IS1684S builds in an enhanced audio engine to offer high quality of audio for audio application. The standard SBC A2DP audio function is implemented in the audio engine.6.10 Audio DACThe build in audio circuits contain a digital to analog converter (DAC) and a headphone driver. The DAC output is available for both line level and through the headphone amplifier to drive a low impedance headphone. The headphone output volume is adjustable by the combination of the digital/analog gain control.Figure 6.10 Audio DAC6.11 Auxiliary ADCThe 10-bit auxiliary analog to digital converter (SAR ADC) provides one dedicated channel for battery power detection and one other channel for external peripheral sensing. This ADC has 10 bits resolution that provides an accurate monitoring for battery voltage. The operating current is very low and almost consumes no power when disabled.6.12 Power Management (PMU)The power management unit of IS1684S includes several power control blocks, linear regulators, switch-mode regulator, Aux-ADC, LED driver and Lithium-ion/Polymer battery charger.6.12.1 3V1_LDOThe IS1684S has build-in the programmable output voltage LDOs (1.8~3.2V) for codec and digital IO power supply. The programmable LDO is used to regulate the high input voltage from battery or adapter. This LDO needs 1uF bypass capacitor.6.12.2 Buck regulatorThe built-in programmable output voltage buck (1.8~2.4V) converts battery voltage for RF and baseband core power supply. This converter has high conversion efficiency and fast transient response.6.12.3 Voltage DectectorThe 10-bit Successive-Approximation analog to digital converter (SAR ADC) monitors the battery power and adapter power for charging and power management control.6.12.4 Li-ion Battery ChargerIS1684S includes a built-in battery charger optimized for use with lithium polymer batteries. The charger features a current sensor for charging control, user programmable current regulation and high accuracy voltage regulation. It charges the battery in four phases:reviving mode : 2mA charging current to charge BAT to 2.5Vpre-charge mode : 0.1C charging current to charge BAT to 3.0Vconstant current mode : 0.xC (default 0.7C) charging current to charge BAT to 4.2V (programmable)constant voltage mode : charging is terminated while the charging current drops below 0.YC (default 0.13C)Charging current in the constant current mode can be configured to provide a wide range of charging current up to 180mA (1mA per step). Charger will re-start charging if the battery voltage falls below an internal threshold.System operation is allowed when the battery is charging.6.13 Miscellaneous (Watchdog Timer, and Clock Divider)System related functions such as watchdog timer, Endian control, and interrupt vectors are also provided. The purpose of the watchdog timer is to provide a reset to CPU in case when the CPU fails to service the watchdog timer in a pre-defined (programmable) period.7 Electrical CharacteristicsAbsolute Maximum RatingsRating Min Max Max Operation Temperature -20ºC +70ºC ºCCore supply voltage VDD_CORE, VCC_RF,AVDD_SAR,AVDD_PLL1.7V 1.98VVCodec supply voltage VDD_AUDIO 3.3 V I/O voltage VDD_IO 3.3 VSupply voltage BK_VDD 4.7 V 3V1_VIN 5 V BAT_IN 4.3 V ADAP_IN 6 V LED[1:0] 5 V Power switch 6 VRecommended Operate ConditionSymbol Parameter Min Typical Max Unit V DD18 Digital core supply voltageSAR ADC supply voltageCODEC supply voltage1.62 1.8 1.92 VV DDIO I/O supply voltageRF supply voltage2.5 2.73.3 VT OPERATION Operating temperature range -20 +25 +70 ºC T stg Storage temperature -40 +125 ºC V LDO LDO supply voltage 1.8 3.3 V V BAT_IN Input voltage for SAR ADC 0.9 3.3 VRadio Characteristics: Transmitter section for BDRVCC_RF = 2.7V Temperature = 25ºC Min Typ MaxBluetoothspecificationUnitMaximum RF transmit power 3 4.0 -6 to 4 dBmRF power variation over temperaturerange with compensation enabled±2 dB RF power control range 20 ≥16 dB RF power range control resolution 0.5 dB 20dB bandwidth for modulated carrier 900 ≤1000 KHzACPNote:F0=2441MHz F = F0±2MHz -28 ≤-20 dBm F = F0±3MHz -46 ≤-40 dBmF = F0±>3MHz -54 ≤-40 dBm∆f1avg maximum modulation 150165 140<∆f1avg<175KHz∆f2max maximum modulation 140 150 ≥115 KHz ∆f2avg/∆f1avg0.95 1 ≥0.80ICFT (abs) 0 5 10 75 KHzDrift rate (abs) 2 7 ≤20 KHz/50usDrift (single slot packet, abs) 12 ≤25 KHz 2nd harmonic content @ Tx= 4dBm -53 ≤-47 dBm 3rd harmonic content @ Tx= 4dBm -55 ≤-47 dBmReceiver section for BDRTemperature = 25ºC Frequency(GHz)Min Typ MaxBluetoothspecificationUnitSensitivity at 0.1% BER for all basic rate packet types 2.402 -91≤-70 dBm 2.441 -912.480 -91Maximum received signal at 0.1%BER-10 ≥-20 dBm C/I co-channel 5 ≤11 dBAdjacent channel selectivity C/INote: F0=2441MHz F =F0+1MHz-7≤0 dB F =F0-1MHz-7 ≤0 dB F =F0+2MHz-36 ≤-30 dB F =F0-2MHz-22 ≤-9 dB F =F0-3MHz-24 ≤-20 dB F =F0+5MHz-50 ≤-40 dB F = F image-22 ≤-9 dBMaximum level of intermodulationinterferers-38 ≥-39 dBTransmitter Section for EDRTemperature = 25ºC Min Typ MaxBluetooth specificationUnitRelative transmit power -1.6-4 to 1 dBπ/4 DQPSK max carrier frequency stability |ωo|freq. error5≤10 for allblocksKHz |ωi|initial freq.error10≤75 for allblocksKHz|ωo+ωi|block freq.error10≤75 for allblocksKHz8DPSK max carrier frequency stability |ωo|freq. error5≤10 for allblocksKHz |ωi|initial freq.error10≤75 for allblocksKHz|ωo+ωi|block freq.error10≤75 for allblocksKHzπ/4 DQPSK modulation accuracy @ Tx= 2dBm RMS DEVM 7 ≤20 % 99% DEVM Pass ≤30 % Peak DEVM 25 ≤35 %8DQPSK modulation accuracy @ Tx=2dBm RMS DEVM 7≤13 % 99% DEVM Pass≤20 % Peak DEVM 20 ≤25 %In-band spurious emissionsNote: F0=2441MHz F > F0+3MHz <-54≤-40 dBm F = F0-3MHz -46≤-40 dBm F = F0-2MHz -28 ≤-20 dBm F = F0-1MHz -30 ≤-26 dBm F = F0+1MHz -30≤-26 dBm F = F0+2MHz -28≤-20 dBm F = F0+3MHz -46≤-40 dBmEDR differential phase encoding 100 ≥99 %Receiver Section for EDR8DPSK -21 ≤0 dBF = F0-3MHz π/4DQPSK-27 ≤-20 dB 8DPSK -20 ≤-13 dBF = F0+5MHz π/4DQPSK-52 ≤-40 dB 8DPSK -45 ≤-33 dBF = F image π/4DQPSK-21 ≤-7 dB 8DPSK -21 ≤0 dBAudio DACTest Condition: T= 25o C, Vdd=2.8V, 1KHz sine wave input, Bandwidth= 20~20KHz Parameter Condition Min. Typ. Max. Unit Output Level Full scale 2.1 Vpp Resolution 16 bits Output Sampling Rate 8 48 KHzSNR f in=1KHzB/W=20~20KHzA-weightedTHD+N < 0.01%0dBFS signalLoad=100KΩ8KHz 94 dB 16KHz 94dB 32KHz 94dB 44.1KHz 94dB 48KHz 94dBMax Output Power R L=16Ohm 35 mW R L=32Ohm 17 mWTHD+N 16Ohm load 0.05 % 100KΩload 0.01 %Digital Gain -54 4.85 dB Digital Gain Resolution 6 dB Analog Gain -28 3 dB Analog Gain step 1 dB Output resistance R L 8 16 Ohm Output capacitance Cp 500 pFCrosstalk between channelsL vs. R, measured at-10dBFS@1KHz input-90 -80 dBAnalog supply voltage(AVDD)1.82.83.0 VBattery ChargerCharging Mode (BAT_IN rising to 4.2V) Min Typ Max Unit Operation Temperature -20 70 ℃Input Voltage (Vin)Note: It needs more time to get battery fullycharged when Vin=4.5V4.5 6 VBattery trickle charge current(BAT_IN < trickle charge voltage threshold)0.1C mA Trickle charge voltage threshold 3 VMaximum battery charge current Headroom > 0.7V 350 mA Headroom = 0.3V 150 mAMinimum battery charge current Headroom > 0.7V 1 mA Headroom = 0.3V 1 mABattery charge termination current,% of fast charge current10 %Battery recharge hysteresis (Note1) 100 mVBattery recharge current (Note2)Note: C Battery capacity0.25C mANote1:When charging complete and the adapter is still in, the battery voltage will slowly drop down.When the voltage drop is larger than 100mV from the full voltage, the re-charging cycle will start.Note2:If the battery voltage during plug in is larger than 4V, the charging current will be limited to0.25C to avoid the battery voltage overshoot.Switching RegulatorNormal Operation Min Typ Max Unit Operation Temperature -20 70 ℃Input Voltage (Vin) 3 3.7 4.5 V Output Voltage (Vout) 1.6 1.85 2.4 mA Output Ripple 20 mVrms Max. Average Load Current(I load) 120 mA Max. Output Current (peak) 200 mAConversion Efficiency (Bat.@3.7V) I load =50mA 88% I load≥ 10mA 80I load≥ 250uA 65Switching Frequency 800 KHz Start-up current Limit 0 50 210 mA Start-up Settling Time 1.2 2 ms Shutdown Current <1 uALDONormal Operation Min Typ Max Unit Input Voltage (Vin) 3.0 4.5 VOutput Voltage (V OUT)(1) V OUT_CODEC(2) V OUT_IO V OUT = 2.9V (2.4~3.4V) 2.9V V OUT = 1.8V (1.3~2.3V) 1.8Accuracy (V IN=3.7V, I LOAD=100mA, 27’C) ±5 % Output Voltage adjustable step 100 mV/Step Output adjustment range ±0.5 V Start-up inrush current 200 400 mA Start-up Settling Time 250 500 µs Output current(average) 100 mA Output Current(peak) 150 mA Drop-out voltag e (I load = maximum outputcurrent)300 mV Quiescent Current(excluding load, I load < 1mA)45 µA Load Regulation (I load = 0mA to 100mA), ∆Vout 80 mV Shutdown Current<1 µA Note: Two 100mA LDOs, one for IO and one for audio CODEC.ClockParameters MIN TYP MAX Unit Crystal Frequency 16 MHz Frequency Tolerence ±20 ppm Operating Temperature -20 70 O C Trimming Capacitance 6.4 pF Trimming Step Size 0.2 pFDigital GPIO (2.8V)Parameters MIN TYP MAX Unit Input Voltage 2.7 3 3.6 V V IH (Input High Voltage) 2.0 Vdd V V IL (Input Low Voltage) 0 0.8 V Input Reference ResistorR PU (Pull-Up Resistor) 50K Ohm R PD (Pull-Down Resistor) 50K Ohm Output VoltageV OH (Output High Voltage) 2.4 Vdd V V OL (Output Low Voltage) 0 0.4 V8 Package InformationAppendix A. Reflow Profile1.) Follow: IPC/JEDEC J-STD-020 C2.) Condition:Average ramp-up rate (217℃ to peak): 1~2℃/sec max.Preheat:150~200C、60~180 secondsTemperature maintained above 217℃ : 60~150 secondsTime within 5℃ of actual peak temperature: 20 ~ 40 sec.Peak temperature:250+0/-5℃ or 260+0/-5℃Ramp-down rate : 3℃/sec. max.Time 25℃ to peak temperature : 8 minutes max.Cycle interval:5 minusAppendix B. BQB certificationTPG Project ISSC Bluetooth 3.0(EDR) Single Chip (Component (Tested)) Qualified Design ID (QD ID)B016749 | Export PICSPRD 1.0 ID (QP ID)Design Name ISSC Bluetooth 3.0(EDR) Single ChipWi-Fi® Certification IDSubsetted Designs Date Created Type PICSJun 28, 2010 Main PICSMember Company ISSC Technologies Corp.Specification Name3.0Core Spec Addenda N/ADesign Model Number IS1XYZ, where X, Y and Z means 1~9Hardware Version Number ISBT_BB_v30Software Version Number ISBT_BB_v30Qualification Assessment Date July/21/2010Listing Date July/21/2010Design Description ISSC Bluetooth 3.0(EDR) Single ChipProduct Type Component (Tested)Technical Data Sheet (RIN)**Open Reference Integration Notes (RIN)**Listed By Charlie LeeBQE Jan-Willem VonkProfile / Protocol Role / Version (If Any)BasebandRadioLink Manager。

LTC2950ITS8-2中文资料

Control ■ Simple Interface Allows Graceful μP Shut Down ■ High Input Voltage PB Pin with Internal Pull Up

LTC2950-1/LTC2950-2

ELECTRICAL CHARACTERISTICS The ● denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25C. VIN = 2.7V to 26.4V, unless otherwise noted. (Note 2)

8-Lead Plastic TSOT-23

TRM = 500 pieces. *Temperature grades are identified by a label on the shipping container.

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on lead based finish parts.

Push Button Pin (PB)

VPB(MIN, MAX) IPB

PB Voltage Range PB Input Current

VPB(VTH) VPB(VOC)

SYMBOL

LTC2803中文资料

ABSOLUTE MAXIMUM RATINGS

(Note 1)

Input Supplies

VCC........................................................... –0.3V to 7V VL.......................................................... –0.3V to 6.7V Generated Supplies

These parts are compatible with the TIA/EIA-232-F standard. Driver outputs are protected from overload and can be shorted to ground or up to ±15V without damage. To extend battery life, receivers can be kept active, operating at reduced speed, with only 15μA current. In shutdown mode, current is further reduced to 1μA. Line sharing and half-duplex operation are also supported.

11 TIN

10 VL 13

9 MODE

8 PS

VEE

7 CAP

DE PACKAGE 12-LEAD (4mm s 3mm) PLASTIC DFN

TJMAX = 125°C, θJA = 43°C/W, θJC = 4.3°C/W (4 Layer) EXPOSED PAD (PIN 13) IS VEE, MUST BE SOLDERED TO PCB

LTC3826资料

Voltages ........................................... INTVCC to –0.3V EXTVCC ...................................................... 10V to –0.3V ITH1, ITH2, VFB1, VFB2 Voltages ................. 2.7V to –0.3V PGOOD1, PGOOD2 Voltages ..................... 8.5V to –0.3V

元器件交易网

LTC3826

FEATURES

30µA IQ, Dual, 2-Phase Synchronous Step-Down Controller

DESCRIPTION