基于延时比较仲裁的模拟I 2C多主通信的软件设计实现

I_2C总线技术在DSP系统中的实现

收稿日期:2007-10-30作者简介:柯艳明(1968— ),男,湖北大冶人,讲师,硕士。

文章编号:1008-8245(2008)01-0007-03I 2C 总线技术在DSP 系统中的实现柯艳明(黄石理工学院电气与电子信息工程学院,湖北黄石435003)摘 要:许多嵌入式系统处理器由于不带有I 2C 总线接口而限制了I 2C 总线接口器件在其上的应用。

介绍了I 2C 总线的特点和时序,并以串行E 2PROM 为例,给出了在T MS320F240X DSP 系统中模拟实现I 2C 总线的方法。

实践证明,该方法简单、可靠,对于构建实际的DSP 应用系统来说具有现实的参考价值。

关键词:I 2C 总线;DSP;E 2PROM 中图分类号:TP336 文献标识码:AThe I mple ment ati on of I 2C Bus Technology i n DSP Syste mKE Yan m ing(School of Electrical and Electronic Infor mation Engineering,Huangshi Institute of Technology,Huangshi Hubei 435003)Abstract:Many e mbedded syste m p r ocess or can not use I 2C bus devices because of its lack of I 2C bus interface .This paper intr oduces the character and ti m e sequence of I 2C bus and taking serial E 2PROM as exa mp le and p resents the si m ulating app licati on method of I 2C bus in DSP syste m.The p ractice p r oves that this method is si m p le and reliable and gives p ractical reference value for actual constructi on of DSP app licati on syste m.Key words:I 2C bus;DSP;E 2PROM I 2C (I nter I C BUS )总线是PH I L I PS 公司推出的一种新型串行总线,它可使芯片之间通过简单的双线进行通讯。

模拟I2C总线多主通信的通用软件包.

模拟I2C总线多主通信的【论文集】通用软件包1 模拟I2C多主通信的设计原理在I2C总线系统中,可以有多个主器件节点。

当多个主器件节点都企图控制总线时,就会出现多主竞争。

这时就需要进行仲裁,裁决的结果只允许其中一个主器件节点成为主控器。

而硬件I2C系统之所以支持多主系统,是因为其具有的三个特性:①接口的线“与”逻辑功能;②内部冲突检测电路;③I2C中断和状态处理程序。

这使其能够自动完成多主竞争时的时钟同步与总线仲裁,无须用户介入。

而在模拟I2C系统中,如果能通过软硬件设计模拟出上述的三个特性,就等于解决了竞争仲裁与同步问题,那么模拟I2C总线就完全可以应用于多主机系统中。

首先,经过理论分析与实验验证,得知并联在一起的MCU的普通I/O口线本身就具有线“与”特性。

其次,为了避免主节点在总线繁忙时启动总线而引起的冲突,需要增加一条握手线,即BUSY线来代表总线的忙/闲状态。

因为数据线(SDA)和时钟线(SCL)上的信号是变化的,所以不能用它们充当BUSY线。

另外,当多个MCU都检测到总线空闲,同时企图控制总线时,将形成多主竞争状态,同样会引起冲突。

这时就需要引入时间片,用划分的时间片来决定竞争时各MCU占用I2C总线的优先次序。

结合SDA的线“与”特性,检测SDA上是否已经存在启动信号(即SDA是否为0),如果直到相应的时间片结束都没有检测到SDA上的启动信号,自己就可以控制总线。

最后,由于模拟系统中没有硬件I2C中断,MCU作为从器件时不知何时开始接收总线上的数据,所以,需要提供一根I2C中断信号线,使MCU在中断程序中处于从接收状态,中断线可以与BUSY线合用。

通过上述分析,利用三根信号线就能模拟出硬件I2C的竞争仲裁过程,实现模拟I2C的多主通信。

2 系统连接示意图三线模拟I2C总线系统的连接框图如图1所示。

模拟I2C多主系统中,要参与竞争的主器件节点采用三级连接方式,如MCU (A)、MCU(B)、MCU(C);对于外围器件节点如24C64等,因不具备主动控制I2C总线的能力,不会参与总线的竞争,所以仍可采用通用的两线连接方式。

51单片机延时函数

51单片机延时函数在嵌入式系统开发中,51单片机因其易于学习和使用、成本低廉等优点被广泛使用。

在51单片机的程序设计中,延时函数是一个常见的需求。

通过延时函数,我们可以控制程序的执行速度,实现定时器功能,或者在需要的时候进行延时操作。

本文将介绍51单片机中常见的延时函数及其实现方法。

一、使用for循环延时这种方法不精确,但是对于要求不高的场合,可以用来估算延时。

cvoid delay(unsigned int time){unsigned int i,j;for(i=0;i<time;i++)for(j=0;j<1275;j++);}这个延时函数的原理是:在第一个for循环中,我们循环了指定的时间次数(time次),然后在每一次循环中,我们又循环了1275次。

这样,整个函数的执行时间就是time乘以1275,大致上形成了一个延时效果。

但是需要注意的是,这种方法因为硬件和编译器的不同,延时时间会有很大差异,所以只适用于对延时时间要求不精确的场合。

二、使用while循环延时这种方法比使用for循环延时更精确一些,但是同样因为硬件和编译器的不同,延时时间会有差异。

cvoid delay(unsigned int time){unsigned int i;while(time--)for(i=0;i<1275;i++);}这个延时函数的原理是:我们先进入一个while循环,在这个循环中,我们循环指定的时间次数(time次)。

然后在每一次循环中,我们又循环了1275次。

这样,整个函数的执行时间就是time乘以1275,大致上形成了一个延时效果。

但是需要注意的是,这种方法因为硬件和编译器的不同,延时时间会有差异,所以只适用于对延时时间要求不精确的场合。

三、使用定时器0实现精确延时这种方法需要在单片机中开启定时器0,并设置定时器中断。

在中断服务程序中,我们进行相应的操作来实现精确的延时。

这种方法需要使用到单片机的定时器中断功能,相对复杂一些,但是可以实现精确的延时。

i2c协议仲裁机制

i2c协议仲裁机制摘要:I2C 协议仲裁机制1.I2C 协议简介2.I2C 协议仲裁机制的作用3.I2C 协议仲裁机制的工作原理4.I2C 协议仲裁机制的优缺点5.应用案例正文:I2C(Inter-Integrated Circuit)协议,又称为两线制串行通信协议,是一种串行通信总线,广泛应用于各种电子设备之间的低速通信。

I2C 协议仲裁机制是保证多个设备在总线上进行通信时,能够高效、有序地完成数据传输的关键。

1.I2C 协议简介I2C 协议是一种串行通信协议,它只需要两根信号线即可实现设备之间的通信,分别是数据线(SDA)和时钟线(SCL)。

I2C 协议支持多个设备连接在同一条总线上,设备之间可以进行地址识别和数据传输。

2.I2C 协议仲裁机制的作用I2C 协议仲裁机制的主要作用是在多个设备同时发送数据时,保证数据传输的有序进行,防止数据冲突。

通过仲裁机制,设备能够确定发送数据的顺序,确保数据传输的可靠性。

3.I2C 协议仲裁机制的工作原理I2C 协议仲裁机制的工作原理主要基于总线上的电平。

在数据传输过程中,设备会根据总线上的电平情况来判断是否可以发送数据。

当总线上的电平为高电平时,设备会认为总线空闲,可以发送数据;当总线上的电平为低电平时,设备会认为总线上有其他设备正在发送数据,此时设备需要等待,直到总线空闲再发送数据。

4.I2C 协议仲裁机制的优缺点优点:- 简单易用:I2C 协议仲裁机制基于电平判断,不需要复杂的逻辑电路。

- 支持多设备通信:I2C 协议可以连接多个设备,实现多设备间的通信。

缺点:- 通信速度受限:由于I2C 协议仲裁机制基于电平判断,当总线上的设备数量较多时,电平判断的延迟会影响通信速度。

- 可能出现数据冲突:在多个设备同时发送数据时,仲裁机制不能完全保证数据传输的有序性,可能导致数据冲突。

5.应用案例I2C 协议仲裁机制广泛应用于各种电子设备,如微控制器、存储器、传感器等。

企业IT软硬件资源整合的实现方式

体架构类似于 OalR rc AC多用户共享模式 , e 其主 【式 , 实现虚拟分区的高可用性 , 通过服务器虚拟化 要的不 同点是单一用户独享该数据库系统 ,这种 技术可 以有效和充分的利用服务器资源,减少服 模式主要用于处理类型比较特殊的应用 ( 例如一 务器数量和采购, 管理, 维护成本。 4存储整合

中间件与硬件结合 的整合方式,主要依赖于

硬件系统的分区或者虚拟化技术 ,将系统资源进 行合理分配 ,在不同的分 区上安装 Welg bo/ c实 例 ,再应用部署 到不同的 We l i bo c实例中去 , g 从

而实 现 :基于主机或服 务器的虚拟化、基于磁盘或磁盘子系统的虚拟化 和基于网络的虚拟化: () 1基于主机层 的虚拟化 基于主机( 应用服务器 ) 上的虚拟化一般通过 运行在存储管理软件加以实现。一般常见的管理 软件如逻辑卷管理软件( V 。 L M)逻辑卷, 一般也会

() 1服务器资源池。服务器统一采购, 统一部 署, 统一使用和统一管理, 构建统一的服务器资源

池 , 种应 用 部署 于不 同的 服务 器群 上 。 各 目前信 息系统 大 部分 都 是 基 于 BS的 三层 架 /

终实现的就是卷独立 于其所属的存储设备。根据

采用的方案不同, A D、 R I 镜像 、 盘到盘的复制以及 基于时间的快照都采用了此类虚拟化。通过虚拟

服务器方式整合到一台或几台高端服务器上。 目前服务器硬件平台主要为 U I N X小型机 和

P c服 务 器 , NX 小 型机 上 的虚 拟 化 技 术 主 要 为 UI

是不需要在主机上安装任何代理软件。基于交换

机或路由器的虚拟技术的另一个优势体现在安全 性上 ,该层次比前面的虚拟应用对外来的攻击有

基于I~2C总线的温度测量系统设计

系统硬 件 工作 流 程为 : 作 人 员通过 键 盘控 制 系 操

统 向单 片机 最 小 系统 输入 控 制命 令 ,单 片机 根据 按键

1 C总线介绍 .l 3

I c总线 是一 种 由 P LP HII S公 司开发 的两线 式 串行 总线 ,用 于连接 微控制器 及其 外 围设 备 。其 中包含 串行 数 据线 ( DA)及串行时钟 线 ( C ,一个用来 传输通 S S L) 信 数据 ,另一个 用来控 制数据传 输 时钟 ,由此 来实现 总 线上器 件之 间的数据 传输 ,并 根据地 址识 别总线 上的每 个器件 。I 2 线主要包含有 : C总 主控 器 、 被控器 、 总线仲裁 、 时钟同步等 [6 51 -。

T 11 过 I MP 0 通 2 C总 线与 单片 机 之 间进行 控 制 命令 与 温度 数据 的相 互传 输 ,数 据传 输过 程 遵照 I 。 线协 c总 议 ,基本 过程 为开 始 ,数 据传 输 ,应 答 ,结束 。其程 序流 程如 图 4所 示 。

开 始

4 结 论

将I c总线 技术 应用 于温 度测 量系统 中 ,充分 利用

锺蛊赫

I

A S C 1 T g 3

竺 l

——————]

糯 部 分 l

单视 片 最 小

系 镜

领 域 。传统 温 度测 量 系统 大 多采 用热 敏 电阻 作 为传 感

器 ,该系统必 须经 过专 门的接 口电路转 换成数字信号 后

图1系统结构 图

才 能 由单 片机进 行 处 理 ,存在 可 靠性 差 、成 本高 、精

设计做 了详 细说明 。传感器将 温度数据及时 、准确 的通过I C总线传输给微控 制器 ,并 在L D上显示 ,为温控 E

I2C,SPI,UART和CAN的区别

I2C,SPI,UART和CAN的区别(转)SPI--Serial Peripheral Interface,(Serial Peripheral Interface:串行外设接口)串行外围设备接口,是Motorola公司推出的一种同步串行通讯方式,是一种三线同步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务.I2C——INTER—IC(INTER IC BUS:意为IC之间总线)串行总线的缩写,是PHILIPS公司推出的芯片间串行传输总线。

它以1根串行数据线(SDA)和1根串行时钟线(SCL)实现了双工的同步数据传输。

具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。

在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。

能用于替代标准的并行总线,能连接的各种集成电路和功能模块。

I2C是多主控总线,所以任何一个设备都能像主控器一样工作,并控制总线.总线上每一个设备都有一个独一无二的地址,根据设备它们自己的能力,它们可以作为发射器或接收器工作。

多路微控制器能在同一个I2C总线上共存。

最主要的优点是其简单性和有效性。

它支持多主控(multimastering),其中任何能够进行发送和接收的设备都可以成为主总线.一个主控能够控制信号的传输和时钟频率.当然,在任何时间点上只能有一个主控.UART(Universal Asynchronous Receiver Transmitter:通用异步收发器):单端,远距离传输。

大多数计算机包含两个基于RS232的串口。

串口同时也是仪器仪表设备通用的通信协议;很多GPIB兼容的设备也带有RS—232口。

同时,串口通信协议也可以用于获取远程采集设备的数据。

串口通信的概念非常简单,串口按位(bit)发送和接收字节。

尽管比按字节(byte)的并行通信慢,但是串口可以在使用一根线发送数据的同时用另一根线接收数据。

带RTC的I_2C总线铁电存储器FM31256

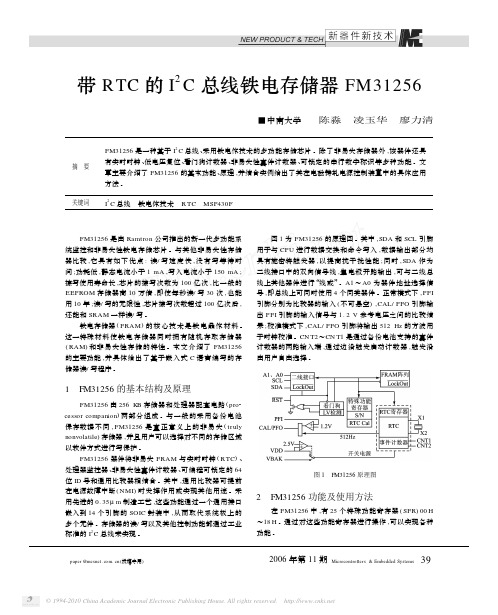

带R TC的I2C总线铁电存储器FM31256■中南大学 陈淼 凌玉华 廖力清 摘 要FM31256是一种基于I2C总线、采用铁电体技术的多功能存储芯片。

除了非易失存储器外,该器件还具有实时时钟、低电压复位、看门狗计数器、非易失性事件计数器、可锁定的串行数字标识等多种功能。

文章主要介绍了FM31256的基本功能、原理,并结合实例给出了其在电磁铸轧电源控制装置中的具体应用方法。

关键词I2C总线 铁电体技术 R TC MSP430F FM31256是由Ramtron公司推出的新一代多功能系统监控和非易失性铁电存储芯片。

与其他非易失性存储器比较,它具有如下优点:读/写速度快,没有写等待时间;功耗低,静态电流小于1mA,写入电流小于150mA;擦写使用寿命长,芯片的擦写次数为100亿次,比一般的EEPROM存储器高10万倍,即使每秒读/写30次,也能用10年;读/写的无限性,芯片擦写次数超过100亿次后,还能和SRAM一样读/写。

铁电存储器(FRAM)的核心技术是铁电晶体材料。

这一特殊材料使铁电存储器同时拥有随机存取存储器(RAM)和非易失性存储的特性。

本文介绍了FM31256的主要功能,并具体给出了基于嵌入式C语言编写的存储器读/写程序。

1 FM31256的基本结构及原理FM31256由256K B存储器和处理器配套电路(pro2 cessor companion)两部分组成。

与一般的采用备份电池保存数据不同,FM31256是真正意义上的非易失(truly nonvolatile)存储器,并且用户可以选择对不同的存储区域以软件方式进行写保护。

FM31256器件将非易失FRAM与实时时钟(R TC)、处理器监控器、非易失性事件计数器、可编程可锁定的64位ID号和通用比较器相结合。

其中,通用比较器可提前在电源故障中断(NMI)时发挥作用或实现其他用途。

采用先进的0.35μm制造工艺,这些功能通过一个通用接口嵌入到14个引脚的SOIC封装中,从而取代系统板上的多个元件。

I 2C

总线上每个实际节点器件 的 I 2 C总线接 口都有一定 的等效电容 ,等效电容 的存在会造成总线传输的延 迟 ,导致数据传输出错 。通常 P C总线负载能力为

4 0p 0 F,据 此 可计 算 出 总线 长 度及 节 点数 目的限制

③因为在总线上可能有多个主 P C器件 ,因此

P C总线 接 口协议 中有 冲 突监 测 和 仲裁 机制 , 以防 止 通 信 中的数 据 丢 失或 发 生错 误 。

维普资讯

文 章 编 号 :0 19 4 (0 2 0 -0 10 1 0 .9 4 2 0 ) 40 2 -3I 总 线技 术及 应 用 Nhomakorabea例 2 C

季宏锋 , 吴军辉 , 立鸿 徐

( 同济 大 学 电 子 与 信 息 X 程 学 院 , 海 2 0 9 ) - 上 0 0 2

作 者 简 介 : 宏 锋 (9 7一) 男 , 士 研 究 生 , 要从 事 嵌 入 式 单 片 机 系统 的研 究 与 开 发 ; 军 辉 (9 4一) , 士 ; 立 季 17 , 硕 主 吴 17 男 博 徐 鸿 (9 0一) 男 , 授 , 士 生 导 师 . 16 , 教 博

直 与蓑2( 动 04 0) 2

特 性 、 片 的 基 本 操 作 以 及读 写 逻 辑 。给 出 了该 芯 片 的 应 用 实例 , 芯 包括 硬 件 设 计 及 C语 言 的 软 件 实现 。I 线 提 供 了 简单 的硬 件 接 口 , C总 简化 了 电路 的 设 计 , 实 际 的应 用 中受 到 电 在

子 工 程 师 的欢 迎 。

团

维普资讯

供 了两 根线 与微 控 器相 连 :一 根 是数 据 线 (dt) S aa ,

i2c协议仲裁机制

i2c协议仲裁机制摘要:一、I2C协议简介二、I2C协议仲裁机制原理三、I2C协议仲裁机制的具体实现四、仲裁机制在I2C协议中的优势五、应用案例及实践分析六、总结与展望正文:一、I2C协议简介I2C(Inter-Integrated Circuit)协议,即集成电路之间互连的接口标准,是由Philips公司(现为NXP半导体公司)于1980年代研发的一种串行通信协议。

I2C协议主要用于低速度、短距离的双向通信,广泛应用于嵌入式系统、微控制器等领域。

二、I2C协议仲裁机制原理在I2C通信过程中,多个设备可能需要竞争有限的带宽资源。

为了解决这一问题,I2C协议引入了仲裁机制。

仲裁机制是在设备之间进行竞争,以决定哪个设备获得通信优先权。

仲裁机制的核心是比较设备之间的地址,地址越小的设备具有更高的优先级。

三、I2C协议仲裁机制的具体实现I2C仲裁机制的具体实现主要包括以下几个步骤:1.初始化:I2C总线上的设备在通信开始前,首先进行初始化,包括时钟同步、设备地址分配等。

2.仲裁:通信发起设备向总线发送起始信号,随后发送设备地址和读/写操作位。

其他设备收到地址后,根据地址进行竞争。

地址越小的设备优先级越高,获得通信权。

3.数据传输:获得通信权的设备与发起设备进行数据传输。

通信过程中,其他设备需等待下次仲裁机会。

4.结束:通信完成后,发起设备发送停止信号,结束本次通信。

随后,其他设备可以继续进行仲裁,争取下一次通信机会。

四、仲裁机制在I2C协议中的优势1.公平性:I2C仲裁机制确保了设备之间公平竞争带宽资源,降低了设备间的通信冲突。

2.高效性:仲裁机制使得通信过程更加有序,提高了总线利用率,降低了通信延迟。

3.灵活性:I2C协议支持多主设备,通信发起权可以随时转移,便于实现分布式控制。

五、应用案例及实践分析1.嵌入式系统:在嵌入式系统中,多个传感器、执行器等设备通过I2C总线与微控制器通信,微控制器根据设备地址进行仲裁,确保各设备有序地获取通信权。

用于片上网络的延时无关异步动态优先级仲裁器

用于片上网络的延时无关异步动态优先级仲裁器

杨延飞;朱樟明;周端;杨银堂

【期刊名称】《西安电子科技大学学报(自然科学版)》

【年(卷),期】2012(039)001

【摘要】针对通用片上网络异步路由器服务质量问题,提出了一种延时无关的异步动态优先级仲裁器.通过比较请求数据包的优先级,可以实现在一个仲裁周期内按优先级由高到低输出.若优先级相同,则顺序输出.解决了传统静态优先级仲裁器的优先级数据输入方式固定问题,提高了仲裁器和路由器的可扩展性,该仲裁器在0.18μm 标准CMOS工艺下实现.Spice仿真结果显示,其平均响应时间为0.92 ns,平均每个请求信号的动态功耗为0.75 mW,可用于通用片上网络异步路由器的仲裁.

【总页数】8页(P42-48,110)

【作者】杨延飞;朱樟明;周端;杨银堂

【作者单位】西安电子科技大学微电子技术研究所,陕西西安710071;西安电子科技大学微电子技术研究所,陕西西安710071;西安电子科技大学计算机学院,陕西西安710071;西安电子科技大学微电子技术研究所,陕西西安710071

【正文语种】中文

【中图分类】TN402

【相关文献】

1.用于片上网络的准延时不敏感全异步仲裁器 [J], 管旭光;杨银堂;朱樟明

2.一种高速延时无关片上异步转同步通信接口的设计 [J], 彭瑶;周端;杨银堂;朱樟

明

3.一种高速延时无关同异步转换接口电路 [J], 彭瑶;杨银堂;朱樟明;周端

4.多机多级动态优先级总线仲裁器的研究 [J], 田俊峰;刘玉玲

5.基于拥塞和热点感知的低延时片上网络路由器设计 [J], 刘炎华;石世领;孙海燕;孙玲;黄新明

因版权原因,仅展示原文概要,查看原文内容请购买。

基于延时比较仲裁的模拟I2C多主通信的软件设计实现

基于延时比较仲裁的模拟I2C多主通信的软件设计实现卢霞【摘要】This paper proposes a general project of a data delay arbitration, and a realization method of software on the principle of simulation I2 C multiple host node communication, and makes the MCU without I2C interface realized a function of simulation I2C multiple host node communication, further advance the application for I G.%根据模拟I2C总线多主节点通信原理,提出采用延时接收比较来实现仲裁的软件实现方法,为不具备I2C接口的普通微控制器(MCU)实现模拟I2C总线的多主节点通信,促进对I2C总线的推广应用.【期刊名称】《工业仪表与自动化装置》【年(卷),期】2011(000)004【总页数】4页(P25-27,44)【关键词】多主通信;模拟I2C总线;仲裁;软件设计【作者】卢霞【作者单位】兰州工业高等专科学校软件工程系,兰州730050【正文语种】中文【中图分类】TP3110 引言I2C总线是双向两线串行通信标准。

由于它具有接口少、通信效率高等优点,现已得到广泛的应用。

它除了可以进行简单的单主节点通信外,还可以应用在多主节点的通信系统中。

在多主节点通信系统中,如果2个或者更多的主节点同时启动数据传输,总线具有冲突检测和仲裁功能,保证通信正常进行并防止数据破坏。

然而,对于没有I2C总线接口的微控制器(MCU),采用2条I/O接口线进行模拟,只能在单主节点系统中进行,使得模拟I2C总线的应用受到限制。

现在,根据总线仲裁的思想,给出模拟I2C多主节点通信的思路及实现流程,从而使不具备I2C接口的MCU方便地进行I2C总线设计。

毕业论文(设计)—基于单片机的按摩器系统的设计与实现

郑州大学西亚斯国际学院本科毕业论文(设计)题目_基于单片机的按摩器系统的设计与实现指导教师职称学生姓名学号专业自动化班级(1)班院(系)电子信息工程学院完成时间基于单片机的按摩器系统的设计与实现摘要按摩器(massager)是根据物理学,仿生学学,生物电学、中医学以及多年临床实践而研制开发出的新一代保健器材。

电子按摩器还分为:电磁按摩、震动按摩和红外按摩。

本设计所选择的是电子按摩器中的震动按摩器,利用单片机PWM(脉宽调制技术)控制直流电机的转速,从而控制震动的快慢和幅度。

本文介绍了基于AT89C52单片机的按摩器系统的硬件结构和软硬件设计方法。

系统以AT89C52单片机为控制器,产生PWM(脉冲宽度调制)控制波形输出,利用直流电机芯片L298N驱动12V直流电机。

实现了电机的正转,反转以及多级调速,在LED上现实按摩器档位和正反转情况。

此按摩器具有显示直观、功能多样、电路简洁、成本低廉等诸多优点,具有广阔的市场前景。

关键字:AT89C52,PWM(脉冲宽度调制),L298N,12V直流电机。

Microcontroller based massage system design andimplementationABSTRACTMassager (massager) is based on physics, bionics, bio-electricity, medicine and clinical practice for many years and developed a new generation of health-care equipment. Electronic massager is also divided into: electromagnetic massage, vibration massage and infrared massage. The design was chosen by the vibration in the electronic massage massage, use of microcontroller PWM (pulse width modulation) control DC motor speed to control the speed and magnitude of vibration. This article describes the massage based on AT89C52 microcontroller system hardware and software and hardware design methods. AT89C52 microcontroller as the control system, resulting in PWM (pulse width modulation) control waveform output, the use of DC motor 12V DC Motor Driver IC L298N. To achieve the motor forward, reverse and multi-level speed, the LED on the real massage stalls and reversing the situation. This massage has a visual display, versatile, circuit simplicity, low cost and many other advantages, and has broad market prospects.Keywords: AT89C52, PWM (pulse width modulation), L298N, 12V DC motor目录中文摘要 (1)英文摘要 (2)1概述 (5)1.1选题背景 (5)1.2设计的应用 (6)2系统总体方案及硬件设计 (6)2.1系统设计要求 (6)2.2总体设计方案 (6)2.3主要元器件介绍 (7)2.3.1主控芯片AT89C52简介 (7)2.3.2 电机驱动芯片l298n功能简介 (10)2.3.3 显示模块简介 (10)2.4系统硬件设计 (13)3系统软件设计 (16)3.1系统结构设计 (16)3.2系统初始化及调速过程 (16)3.3响应过程 (17)4 PROTEUS软件仿真 (17)4.1P ROTEUS ISIS简介 (17)4.2P ROTEUS运行流程 (18)4.3P ROTEUS功能仿真 (18)总结 (19)致谢 (20)参考文献 (21)附录 (22)1概述1.1选题背景按摩器(massager)是根据物理学,仿生学学,生物电学、中医学以及多年临床实践而研制开发出的新一代保健器材。

基于延时比较仲裁的模拟I^2C多主通信的软件设计实现

基于延时比较仲裁的模拟I^2C多主通信的软件设计实现杨建平;卢霞

【期刊名称】《自动化与仪器仪表》

【年(卷),期】2011(0)3

【摘要】根据模拟I2C总线多主节点通信原理,提出采用延时接收比较来实现仲裁的软件实现方法,为不具备I2C接口的普通微控制器(MCU)实现模拟I2C总线的多主节点通信,促进对I2C总线的推广应用。

【总页数】3页(P120-122)

【关键词】多主通信;模拟I2C总线;仲裁;软件设计

【作者】杨建平;卢霞

【作者单位】兰州工业高等专科学校软件工程系

【正文语种】中文

【中图分类】TP311.51

【相关文献】

1.基于延时比较仲裁的模拟I2C多主通信的软件设计实现 [J], 卢霞

2.基于硬件仲裁和串行总线的多主通信 [J], 陈松岭

3.模拟I2C总线多主通信研究与软件设计 [J], 郑旭阳;李兵兵;黄新平

4.利用VISUAL BASIC实现串行通信的两种延时方法的比较 [J], 刘志远;徐海涛

5.基于知识库调度主站端的工作票自动生成软件设计与实现 [J], 谢传林;何润泉;陈槾露

因版权原因,仅展示原文概要,查看原文内容请购买。

i2c协议仲裁机制

i2c协议仲裁机制摘要:1.I2C 协议概述2.I2C 协议仲裁机制的原理3.I2C 协议仲裁机制的实现方式4.I2C 协议仲裁机制的优点与局限性正文:一、I2C 协议概述I2C(Inter-Integrated Circuit)协议是一种串行通信协议,主要用于在微控制器(MCU)和周边设备(如EEPROM、LCD 显示器、传感器等)之间进行低速通信。

I2C 协议具有主从模式、多主控制器模式和仲裁机制等特点,使得系统可以灵活地配置和扩展。

二、I2C 协议仲裁机制的原理在I2C 总线上,可以连接多个设备。

当多个设备同时尝试在总线上发送数据时,就会产生冲突。

为了解决这个问题,I2C 协议引入了仲裁机制。

仲裁机制的核心思想是,在数据传输过程中,只有优先级最高的设备可以成功发送数据,其他设备需要等待下一次机会。

仲裁机制主要通过仲裁地址和仲裁位来实现。

仲裁地址是I2C 地址的一部分,用于表示设备的优先级。

优先级高的设备具有较小的仲裁地址。

当多个设备同时发送数据时,I2C 控制器会根据仲裁地址来判断哪个设备具有发送权限。

仲裁位是I2C 数据传输中的一个位,用于表示数据传输的优先级。

优先级高的设备会在仲裁位上设置更高的值。

三、I2C 协议仲裁机制的实现方式I2C 协议仲裁机制的实现方式主要包括以下两种:1.软件仲裁:软件仲裁是指在MCU 软件中实现仲裁逻辑。

当多个设备同时尝试发送数据时,MCU 会根据设备的仲裁地址和仲裁位来判断哪个设备具有发送权限。

具有权限的设备可以继续发送数据,其他设备则需要等待下一次机会。

2.硬件仲裁:硬件仲裁是指在I2C 控制器硬件中实现仲裁逻辑。

与软件仲裁相比,硬件仲裁具有更快的响应速度和更高的优先级。

当多个设备同时发送数据时,I2C 控制器会根据设备的仲裁地址和仲裁位来判断哪个设备具有发送权限。

具有权限的设备可以继续发送数据,其他设备则需要等待下一次机会。

四、I2C 协议仲裁机制的优点与局限性I2C 协议仲裁机制具有以下优点:1.解决了多设备同时发送数据时的冲突问题,保证了数据传输的稳定性。

可设置仲裁优先程度的NOC路由节点设计

第37卷 第5期 电 子 科 技 大 学 学 报 V ol.37 No.52008年9月 Journalof University of Electronic Science and Technology of China Sep. 2008 可设置仲裁优先程度的NOC 路由节点设计武 畅,李玉柏,彭启琮,柴 松,杨中明(电子科技大学通信与信息工程学院DSP 技术中心 成都 610054)【摘要】针对片上网络(NOC)具体应用中各个IP 之间出现不同的通信情况的问题,提出了一种可设置仲裁优先程度的NOC 路由节点。

该节点采用基于Lottery 算法的仲裁机制,取代了目前NOC 路由节点中广泛采用的轮询调度(RR)仲裁机制,可以根据具体应用的通信状况来设定仲裁响应的优先程度。

在NOC 路由节点中,设计了内部TUM(时间单元复用)的传输机制来解决不同输入口竞争同一输出口所带来的节点内部阻塞问题,使得即使在有多个端口竞争同一端口的情况下,路由节点仍然能保证输入的数据包和进入输出缓冲的数据包数量上的一致,大大提高了路由节点的处理性能。

关 键 词 片上网络; 路由节点; 仲裁器; 优先级; 仿真 中图分类号 TN929 文献标识码 ADesign of a Customized Arbitral Priority NOC RouterWU Chang, LI Yu-bai, PENG Qi-cong, CHAI Song, and YANG Zhong-ming(DSP Center of School of Communication and Information Engineering, University of Electronic Science and Technology of China Chengdu 610054)Abstract For the different communication cases of specific network on chip (NOC) applications, a customized arbitral priority NOC router is proposed. This router uses the arbitral mechanism based on lottery algorithm instead of the round robin (RR) algorithm, which is widely used in the arbiter of current NOC routers. The arbitral priority of lottery router can be customized by users according to the communication cases among IPs in NOC. This router also includes a time unit multiplex (TUM) transmission mechanism to alleviate the problem of internal block, which may be induced by the case of several input ports competing for one output port. The TUM mechanism guarantees the number of input data is equal to the number of output data and improves the router processing performance.Key words arbiter; NOC; priority; router; simulation收稿日期: 2007 − 11 − 13; 修回日期: 2008 − 03 − 19基金项目:国家自然科学基金(60575031)作者简介:武 畅(1979 − ),男,博士生,主要从事片上网络技术、实时信号处理和DSP 技术方面的研究.随着工艺技术和集成水平的高速发展,使得在单个芯片上集成几十亿个晶体管成为可能[1],单个芯片的计算和处理能力也大大提高,同时,大量的片上资源也使SoC 设计面临更多的挑战。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

s

-- 』L jL _ 1 L 』 』 L L

停止 信 号 传输 … ’ 0或 佑输 … ’ 1或 应答 位 ( ) 非应 答位 ( ) A / A

起 始信 号

图1 I C总线上基本信号 的时序

收 稿 日期 :0 1一 1—2 21 O 8

基金项 目: 甘肃省教育厅科研基金 资助 (0 0 4 0 ) 2 1 1D一 2 作者简介 : 卢霞( 9 6 , , 16 ) 女 河北 涿州人 , 高级工程师 ,18 9 9年毕

.

v nc h p iai n f r1 a e t e a pl to o 2 c C

ห้องสมุดไป่ตู้

.

Ke r s: o y wo d c mmu i ain fr mu tp e h s d smu ain 1 abi ain; sg fs fwa e n c to o li l o tno e;i l to 2 C; r t to de in o ot r r

法, 为 ̄-备 I g . - c接 口的普通微控制器( C ) M U 实现模拟 1 2 C总线的多主节点通信 , 促进对 I c总线

的推 广 应 用。

关 键词 : 多主 通信 ; 拟 IC总线 ; 模 仲裁 ; 软件 设 计 中图分 类号 :P 1 T 31 文献标 志 码 : A 文 章编 号 :0 0— 6 2 2 1 ) 4— 0 5— 3 10 0 8 ( 0 1 0 0 2 0

LU a Xi

( azo o t h i C lg , a zo 3 0 0 hn ) L nh uP l e nc ol e L nh u7 0 5 ,C ia yc e

Abta tT i p prpo oe agn rl r e t f a e yabt t n a dara zt nme o src : hs a e rp ss eea po c o dt dl riai ,n l a o t d j a a a r o ei i h

o ot r n t e p i c p e o i lto C fs fwa e o h rn i l f smu ai n I mu t e h s o o li o t n de c mmu ia in,a d ma e he MCU pl nc t o n k st wi u 2 n ef c e lz d a f n to fsmu a in 1 li l o tn d o t t1 i tra e r aie u c in o i l t 2 mu tpe h s o e c mmu i ain f rh ra ho C o C n c to u t e d

以应 用在 多 主节点 的通信 系统 中 。在 多 主节点 通信 系统中, 如果 2个 或 者 更 多 的 主节 点 同时 启 动 数据 传输 , 总线具 有 冲突检 测和 仲裁 功能 , 保证 通信 正 常

进行 并 防止数 据 破 坏 。然 而 , 于 没有 IC总 线 接 对

求, 总线工作时 , S L传送 时钟脉冲,D 由 C S A传送数

0 引言

Ic总线是 双 向两 线 串行 通信 标 准 。 由于 它 具

1 1C总线 系统及 其仲裁 2

Ic总 线 系统 是 由 S L( C 串行 时 钟 ) S A( 和 D 串 行数 据 ) 2根 总线 构 成 的 。该 总 线有 严 格 的时 序 要

有接 口少、 通信效率高等优 点 , 现已得到广泛 的应 用 。它除了可以进行 简单 的单主节点通信外 , 还可

2 1 年第 4期 01

工业仪表与 自动化装置

・2 5・

基 于 延 时 比较 仲 裁 的

模 拟 I C 多 主 通 信 的软 件 设 计 实 现 2

卢 霞

( 兰州工 业 高等专科 学校 软 件 工程 系, 兰州 705 ) 300

摘 要 : 据模 拟 IC总线 多主 节 点通信 原理 , 出采 用延 时接 收 比较 来 实现 仲裁 的软 件 实现 方 根 提

De i n n i plm e a i n o i ul to 1 m u tpl s d o mun c to sg a d m e nt to fsm a i n 2 C li e ho tno e c m ia in

’ s fwa e b s d o r ir to fd t l y o t r a e n a b t a i n o a dea a

图2表示 了一个完整的数据传送过程 。在 I C

总线发送起始信号后 , 发送从机 的 7位寻址地址和 1 表示这次操作性质的读写位 , 位 在有应答信号后

业于郑州轻 工业学 院信息 与控制工程系计算机应用专业 , 现主要从事 计算机 与 自 动化技术等方 面的教学与科研开发工作。

s 。

口的微控 制器 ( U) 采用 2条 IO接 口线进 行 模 MC , / 拟, 只能在 单 主节 点 系统 中进 行 , 使得 模 拟 IC总线 的应 用受 到 限制 。现在 , 根据 总线 仲裁 的思 想 , 出 给 模 拟 Ic多主节 点 通 信 的思 路 及 实 现 流 程 , 而 使 从 不具备 Ic接 口的 MC U方便 地进行 1C总线设 计 。 2

据 。总线 协议 规定 , 主节 点 进 行 通 信 时都 要 有 起 各

始、 结束 、 发送数据和应答信号。这些信号都是通信

过程 中的基本 单元 , 1中列 出了包括起 始信 号 、 图 停 止信 号 、 答信 号 、 应 非应答 信 号 以及 传 输 数 据 “ ” 0 和 数据 “ ” 1 的时序 。