ZL50019GAG2中文资料

格拉斯腾达泡杯冰凌机操作手册与配件目录说明书

Operation Manual and Parts DirectoryGlastender, Inc. · 5400 North Michigan Road · Saginaw, MI · 48604-9780800.748.0423 · 989.752.4275 · Fax 800.838.0888 / 989.752.4444 · © 2010 Glastender, Inc.Rev. 04-26-11MF24-SMF48-B2MF24, MF36, MF48M ug F rosters and P late C hillersGlastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • iiP riCes:All prices are LIST. Applicable taxes will be added.Q uotations:Unless otherwise stated, quotations are effective for 30 days only.a CCePtanCe:All orders are subject to acceptance by Glastender, Inc.’s headquarters in Saginaw, Michigan. Possession of the Product Directory and Price List is not an offer to sell.s hiPMents:F.O.B. factory in Saginaw, Michigan. Freight terms are Third Party or Collect if shipped directly to you. Prepay and Add to Invoice freight terms are available upon request. The approximate shipping weights of all products are listed with the prices. Partial shipments will be made unless otherwise specified by the customer. Surface freight classifica-tions are:Glasswashers, Line Chillers - Class 92.5Cocktail Stations, Underbar Equipment - Class 85Bar Die/Underbar Equipment – Class 125Refrigeration Equipment, 48” long or smaller - Class 100Refrigeration Equipment, greater than 48” long - Class 110All small items are evaluated to see the most cost effective means for shipment. Many small items ship via UPS or FedEx; however, when dimensional weight is excessive DB Schenker, UPS Supply Chain, or even common LTL carriers are the most cost effective choice. Spare parts orders received before 1:00 PM EST can usually be shipped the same day.The order department is happy to assist with routing or shipping ques-tions.P ayMent t erMs:Cash should be included with all orders unless credit terms have been arranged. To establish credit, banking and trade references are required.A convenient credit application is available upon request. Payment via credit card is not our normal means of receiving payment. Visa and MasterCard will be accepted, but must be charged at the time of ship-ment. In addition, a payment via credit card for orders totaling more than $500 will incur a 3% convenience fee on the total transaction amount.d elivery:The majority of equipment is manufactured to order and typically ships within three to six weeks after complete order information is received by the factory. In-stock equipment typically ships within two to three days of the factory receiving complete order information.r eturns:Items specified as “Manufactured to Order” are NOT returnable.A Return Material Authorization (RMA) number must be issued by the factory in advance for any items that are returnable. The RMA number MUST be noted on the outside of the returned package. Returns must be received within 90 days of the RMA issue date. Shipping charges must be prepaid. A minimum 20% restocking charge will be applied to all authorized returns if received in new, unused condition in the original packaging.The above conditions apply to spare part returns, except spare part returns must be received within 30 days of original shipment for elec-tronic or electrical parts or within 90 days for all other parts.l oss or d aMage:For customer routed shipments, Glastender, Inc. is not responsible for any loss, damage, or delay of merchandise during shipment. Such transit claims must be filed with the carrier. Merchandise must be examined on arrival. If shortages occur, Glastender, Inc. must be notified in writing within five (5) days of delivery to honor any shortage claim. Glastender will assume responsibility for freight claims on Prepay and Add ship-ments but the customer must inspect freight and note any damage upon receipt. Failure to do so may result in losses at the customer’s expense.C ustoM o rders:Custom orders must be paid in advance and are not subject to cancel-lation.l aMinates:Some products include common, readily available plastic laminates of the customer’s selection. There may be an additional charge if uncom-mon varieties are ordered.05/18/10Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 1Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 2APPLICABLE TO ALL PRODUCTS SOLD WITHIN THE UNITED STATES AND CANADAGlastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 3i ntroduCtionThis manual describes the operational features of Mug Froster/Plate Chiller models MF24, MF36, and MF48. Please review this information before attempting installation and operation.Long term, trouble-free service will follow if good housekeeping and maintenance procedures are followed. Thank you for selecting Glastender, Inc. products.u tility r eQuireMents and C onneCtions• Electrical: 115 V olt AC, 1 Phase, 60 Hz, 6.7 Full Load Amps. A separate 15 Amp circuit is recommended. A 6-footgrounded cord is included.• Plumbing: None required. Automatic condensate evaporator is included.u nCrating and s tart -u P i nstruCtionsAll Mug Frosters and Plate Chiller models are shipped in one carton. These steps should be followed:1. If legs or casters are included, bolt them to the base with the bolts provided.2. Unwrap power cord from base.3. Position Mug Froster/Plate Chiller and level and/or seal as required (see page 2).4. Install shelves.5. Plug into 115 volt AC outlet.6. Load with mugs, glasses, plates, etc.7.Your Glastender Mug Froster/Plate Chiller is now ready for use.s ealing M ug F roster and P late C hiller B ase to F loorTo comply with NSF & health codes. The Mug Froster base must be sealed to the floor using NSF listed sealant.Place a bead of sealant along outer edges of the base and remove excess with disposable towel.Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 4o PerationThe Mug Froster/Plate Chiller is designed to chill mugs, glasses, plates, etc. that will appear “frosted” when removed. The operating temperature range of 0°F (-18°C) to 35°F (2°C).The Mug Froster/Plate Chiller should be filled with dry, room-temperature mugs, glasses, plates, etc. to allow maximum chilling. During business hours, the Mug Froster/Plate Chiller can be loaded with additional dry, room-temperature mugs, glasses, plates, etc. Allow 30 minutes for chilling.The Mug Froster/Plate Chiller includes an automatic defrost system. Defrosting will occur every six hours for approxi-mately 20 minutes. During the defrost cycle, the fan inside the Mug Froster/Plate Chiller will turn off and a small amount of mist may appear if the top is opened.There is also a manual defrost system controlled by a switch located on the front left bottom of the Mug Froster/Plate Chiller. This is used when there is ice or snow accumulation inside. An end-of-the-day or weekly schedule can be estab-lished for the activation of this manual defrost cycle.When the manual defrost switch is pushed, a light will turn on and the Mug Froster/Plate Chiller will go into a six-hour defrost. After six hours, the Mug Froster/Plate Chiller will resume normal operation.If the manual defrost switch is accidentally pushed, the defrost cycle can be terminated by unplugging the power cord for three seconds.C leaning i nstruCtionsCleaning is essential to sustaining the integrity of your equipment and preventing corrosion.ESTIMATED CLEANING TIME: 5 to 10 minutes per unit daily, 30 minutes quarterlyFREQUENCY: Daily cleaning of exterior & door gaskets. Quarterly cleaning of interior, including shelves.PROCEDURE:1. A non-chlorine based cleaner or mild detergent and warm water applied with a soft cloth or sponge to all contact sur-faces.2. Immediately rinse off cleaning agent(s), using clean warm water, clean soft cloth or sponge.3. Dry with a soft clean cloth, removing standing water as soon as possible.NOTES:1. Never use hydrochloric acid, wire brushes, steel wool, scrapers, or chlorine based cleaners on stainless steel surfaces,since they will break down the passivity layer and allow corrosion to occur.2. On stainless steel surfaces, you may use a soft bristle brush or Scotch-Brite ® pad for more stubborn stains. Alwaysscrub with the direction of the grain. Follow with a thorough cleaning as described above.3. Deposits from food preparation must be properly removed. Even hard water deposits will rust stainless steel, if notremoved.4. Repeated cleaning may dry up black-vinyl-clad steel (exterior) surfaces of the cooler. Armor All ® or similar productcan bring back the shine. Apply the product to a cloth and then rub into the surface, rather than spraying it directly onto the black-vinyl-clad surface.5. The cooler door gaskets are most often overlooked when cleaning. Failure to clean them regularly will lead to prema-ture failure, since alcohol and moisture build-up breaks down the gasket material.6. Mug frosters have a manual defrost timer switch on the front near the bottom, which will activate a 6-hour defrost cycle.Depressing the switch before you close for the evening will remove excess frost build-up on the interior liner. This pro-cedure should be done as often as is necessary. It should also be done the night before the quarterly interior cleaning.e leCtriCal and r eFrigeration s PeCiFiCationsd esignM odel r eFrigerant P ressure(L-to-R length) e leCtriCal t yPe C harge h igh l oW 24”, 36”, 48” 115V, 1Ph., 60 Hz., 6.7 Amp R404A 8.5oz. 350 175800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 5Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 6Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 7P art n o .o ld P art n o .d esCriPtionP riCe3. 07000127Overload protector for R404 Aspera compressor 15.00 4. 07000175 GT-035026 1/3 HP Tecumseh compressor, R404A (after 1/00) 375.000700023719. 07000235 GT-038203 Wicking material, consists to 11 4” pieces, MF24 14.0007000724Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 8Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 9P art n o .o ld P art n o .d esCriPtionP riCe12. 07000227 GT-037419 Control module, complete400.00Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 10P art n o .o ld P art n o .d esCriPtionP riCe07000159 9. 07000162 GT-033108 Shelf, 12” x 19-5/8” [MF36 = 3 (bottom, middle, top),40.0007000224 Complete shelf kit for MF36 (includes: 1- 07000159, MF24 = 1MF36 = 1MF48 = 2MF24 = 0MF36 = 0MF48 = 119-5/8″19-5/8″19-5/8″19-5/8″0700015907000158Glastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 11P artn o .o ldP art n o .d esCriPtionP riCeGlastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 1207000193 GT-036112 Back, stainless steel, MF24 80.00 07000194 GT-036113 Back, black vinyl-clad, MF36 50.00 07000195 GT-036114 Back, stainless steel, MF36 100.00 2. 07000196 GT-036115 Back, black vinyl-clad, MF48 55.00 07000197 GT-036116 Back, stainless steel, MF4896.00 3. 07000198 GT-036117 Side, left, black vinyl-clad, all models 40.00Model MF48Front viewRear viewFront viewGlastender, Inc. • 5400 North Michigan Road • Saginaw, MI • 48604-9780800.748.0423 • 989.752.4275 • Fax 800.838.0888 / 989.752.4444 • 13Installation Notes____________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________Original System InstallerCompany: _____________________________________________Address: __________________________________________________________________________________________City, State, Zip: _____________________________________________Phone Number: _____________________________________________Fax Number: _____________________________________________Contact:_____________________________________________P artno .desCriPtionPriCeExpect moremore flexibilitymore featuresGlastender has the most complete line of bar equipment andthe ability to manufacture custom units, giving you virtuallyunlimited design flexibility. Each piece of equipment isengineered with features that enhance your efficiency, easeyour maintenance, and prolong the life of your investment.The flexibility you want. The features you need. GLASSWASHERS • COCKTAIL STAT。

ZL30120GGG中文资料

1A full Design Manual is available to qualified customers.To register, please send an email to TimingandSync@.Features•Synchronizes with standard telecom system references and synthesizes a wide variety of protected telecom line interface clocks that are compliant with Telcordia GR-1244-CORE, GR-253-CORE, ITU-T G.813, and compatible with ITU-T G.8261 (formerly G.pactiming)•Internal low jitter APLL provides SONET/SDHclocks including 6.48MHz, 19.44MHz, 38.88MHz, 51.84MHz and 77.76MHz, or 25MHz and 50MHz Synchronous Ethernet output clocks•Programmable output synthesizers (P0, P1)generate general purpose clock frequencies from any multiple of 8kHz up to 100MHz•Jitter performance of <8 ps RMS on the low jitter APLL outputs, and <20 ps RMS on the programmable synthesizer outputs.•Provides 8 reference inputs which support clock frequencies with any multiples of 8kHz up to 77.76MHz in addition to 2kHz•Provides two DPLLs which have independent modes of operation (locked, free-run, holdover) and optional hitless reference switching.•Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities•Provides 3 sync inputs for output frame pulse alignment•Generates several styles of output frame pulses with selectable pulse width, polarity, and frequency •Configurable input to output delay, and output to output phase alignment•Supports IEEE 1149.1 JTAG Boundary ScanMay 2006Figure 1 - Block DiagramZL30120SONET/SDH/EthernetMulti-Rate Line Card SynchronizerData SheetOrdering InformationZL30120GGG 100 Pin CABGA Trays ZL30120GGG2100 Pin CABGA**Trays**Pb Free Tin/Silver/Copper-40o C to +85o CZL30120Data SheetApplications•AMCs for AdvancedTCA TM and MicroTCA Systems•Synchronous Ethernet•Multi-Service Edge Switches or Routers•DSLAM Line Cards•WAN Line Cards•RNC/Mobile Switching Center Line Cards•ADM Line CardsZL30120Data SheetTable of Contents1.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.1 DPLL Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.2 DPLL Mode Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121.3 Ref and Sync Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131.4 Ref and Sync Monitoring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.5 Output Clocks and Frame Pulses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151.6 Configurable Input-to-Output and Output-to-Output Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172.0 Software Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.0 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25ZL30120Data SheetList of FiguresFigure 1 - Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Automatic Mode State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 3 - Reference and Sync Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 4 - Output Frame Pulse Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM Failures. . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 6 - Output Clock Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 7 - Phase Delay Adjustments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17ZL30120Data SheetList of TablesTable 1 - DPLL1 and DPLL2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 2 - Set of Pre-Defined Auto-Detect Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 3 - Set of Pre-Defined Auto-Detect Sync Frequencies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 4 - Output Clock and Frame Pulse Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16ZL30120Data Sheet Pin DescriptionPin # Name I/OType DescriptionInput ReferenceC1 B2 A3 C3 B3 B4 C4 A4ref0ref1ref2ref3ref4ref5ref6ref7I d Input References (LVCMOS, Schmitt Trigger). These are input referencesavailable to both DPLL1 and DPLL2 for synchronizing output clocks. All eightinput references can be automatically or manually selected using softwareregisters. These pins are internally pulled down to Vss.B1 A1 A2sync0sync1sync2I d Frame Pulse Synchronization References (LVCMOS, Schmitt Trigger).These are the frame pulse synchronization inputs associated with inputreferences 0, 1 and 2. These inputs accept frame pulses in a clock format (50%duty cycle) or a basic frame pulse format with minimum pulse width of 5ns.These pins are internally pulled down to V ss.Output Clocks and Frame PulsesD10apll_clk0O APLL Output Clock 0 (LVCMOS). This output can be configured to provide anyone of the available SONET/SDH clock outputs up to 77.76MHz, or 25MHz and50MHz. The default frequency for this output is 77.76MHz.G10apll_clk1O APLL Output Clock 1 (LVCMOS). This output can be configured to provide anyone of the available SONET/APLL clock outputs up to 77.76MHz, or 25MHz and50MHz. The default frequency for this output is 19.44MHz.E10apll_fp0O APLL Output Frame Pulse 0 (LVCMOS). This output can be configured toprovide virtually any style of output frame pulse synchronized with an associatedAPLL output clock. The default frequency for this frame pulse output is 8kHz.F10apll_fp1O APLL Output Frame Pulse 1 (LVCMOS). This output can be configured toprovide virtually any style of output frame pulse synchronized with an associatedAPLL output clock. The default frequency for this frame pulse output is 2kHz.K9p0_clk0O Programmable Synthesizer 0 - Output Clock 0 (LVCMOS). This output can beconfigured to provide any frequency with a multiple of 8kHz up to 100MHz inaddition to 2kHz. The default frequency for this output is 2.048MHz.K7p0_clk1O Programmable Synthesizer 0 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p0_clk0frequency within the range of 2kHz to 100MHz. The default frequency for thisoutput is 8.192MHz.K8p0_fp0O Programmable Synthesizer 0 - Output Frame Pulse 0 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.J7p0_fp1O Programmable Synthesizer 0 - Output Frame Pulse 1 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.ZL30120Data SheetJ10p1_clk0OProgrammable Synthesizer 1 - Output Clock 0 (LVCMOS). This output can be configured to provide any frequency with a multiple of 8kHz up to 100MHz in addition to 2kHz. The default frequency for this output is 1.544MHz (DS1).K10p1_clk1OProgrammable Synthesizer1 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p1_clk0 frequency within the range of 2kHz to 100MHz. The default frequency for this output is 3.088MHz (2x DS1).H10fb_clk OFeedback Clock (LVCMOS). This output is a buffered copy of the feedback clock for DPLL1. The frequency of this output always equals the frequency of the selected reference.E1dpll2_ref ODPLL2 Selected Output Reference (LVCMOS). This is a buffered copy of the output of the reference selector for DPLL2. Switching between input reference clocks at this output is not hitless.Control H5rst_bIReset (LVCMOS, Schmitt Trigger). A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. Reset should be asserted for a minimum of 300ns.J5dpll1_hs_enI uDPLL1 Hitless Switching Enable (LVCMOS, Schmitt Trigger). A logic high at this input enables hitless reference switching. A logic low disables hitless reference switching and re-aligns DPLL1’s output phase to the phase of the selected reference input. This feature can also be controlled through software registers. This pin is internally pulled up to Vdd.C2D2dpll1_mod_sel0dpll1_mod_sel1I uDPLL1 Mode Select 1:0 (LVCMOS, Schmitt Trigger). During reset, the levels on these pins determine the default mode of operation for DPLL1 (Automatic, Normal, Holdover or Freerun). After reset, the mode of operation can becontrolled directly with these pins, or by accessing the dpll1_modesel register through the serial interface. This pin is internally pulled up to Vdd.Status H1dpll1_lockOLock Indicator (LVCMOS). This is the lock indicator pin for DPLL1. This output goes high when DPLL1’s output is frequency and phase locked to the input reference.J1dpll1_holdover OHoldover Indicator (LVCMOS). This pin goes high when DPLL1 enters the holdover mode.Serial Interface E2sck I Clock for Serial Interface (LVCMOS). Serial interface clock.F1si I Serial Interface Input (LVCMOS). Serial interface data input pin.G1so O Serial Interface Output (LVCMOS). Serial interface data output pin.E3cs_bI uChip Select for Serial Interface (LVCMOS). Serial interface chip select. This pin is internally pulled up to Vdd.Pin # Name I/O Type DescriptionZL30120Data Sheet G2int_b O Interrupt Pin (LVCMOS). Indicates a change of device status prompting theprocessor to read the enabled interrupt service registers (ISR). This pin is anopen drain, active low and requires an external pulled up to VDD.APLL Loop FilterA6apll_filter A External Analog PLL Loop Filter terminal.B6filter_ref0A Analog PLL External Loop Filter Reference.C6filter_ref1A Analog PLL External Loop Filter Reference.JTAG and TestJ4tdo O Test Serial Data Out (Output). JTAG serial data is output on this pin on thefalling edge of tck. This pin is held in high impedance state when JTAG scan isnot enabled.K2tdi I u Test Serial Data In (Input). JTAG serial test instructions and data are shifted inon this pin. This pin is internally pulled up to Vdd. If this pin is not used then itshould be left unconnected.H4trst_b I u Test Reset (LVCMOS). Asynchronously initializes the JTAG TAP controller byputting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internallypulled up to Vdd. If this pin is not used then it should be connected to GND.K3tck I Test Clock (LVCMOS): Provides the clock to the JTAG test logic. If this pin is notused then it should be pulled down to GND.J3tms I u Test Mode Select (LVCMOS). JTAG signal that controls the state transitions ofthe TAP controller. This pin is internally pulled up to V DD. If this pin is not usedthen it should be left unconnected.Master ClockK4osci I Oscillator Master Clock Input (LVCMOS). This input accepts a 20MHzreference from a clock oscillator (TCXO, OCXO). The stability and accuracy ofthe clock at this input determines the free-run accuracy and the long termholdover stability of the output clocks.K5osco O Oscillator Master Clock Output (LVCMOS). This pin must be left unconnectedwhen the osci pin is connected to a clock oscillator.MiscellaneousA9 A10 B5 B9 B10 C5 D1 D3 G3NC No Connection. Leave unconnected.Pin # Name I/OType DescriptionZL30120Data Sheet J2J6H7K1IC Internal Connection. Connect to ground.F2F3K6IC Internal Connection. Leave unconnected.Power and GroundD9 E4 G8 G9 J8 J9 H6 H8V DD PPPPPPPPPositive Supply Voltage. +3.3V DC nominal.E8 F4V CORE PPPositive Supply Voltage. +1.8V DC nominal.A5 A8 C10AV DD PPPPositive Analog Supply Voltage. +3.3V DC nominal.B7 B8 H2AV CORE PPPPositive Analog Supply Voltage. +1.8V DC nominal.D4 D5 D6 D7 E5 E6 E7 F5 F6 F7 G4 G5 G6 G7 E9 F8 F9 H9V SS GGGGGGGGGGGGGGGGGGGround. 0 Volts.Pin # Name I/OType DescriptionZL30120Data SheetI - InputI d -Input, Internally pulled down I u -Input, Internally pulled up O -Output A -Analog P -Power G -GroundA7C7C8C9D8H3AV SSG G G G G GAnalog Ground. 0 Volts.Pin # Name I/O Type DescriptionZL30120Data Sheet1.0 Functional DescriptionThe ZL30120 Multi-Rate Line Card Synchronizer is a highly integrated device that provides timing and synchronization for network interface cards. It incorporates two independent DPLLs, each capable of locking to one of eight input references and provides a wide variety of synchronized output clocks and frame pulses.1.1 DPLL FeaturesThe ZL30120 provides two independently controlled Digital Phase-Locked Loops (DPLL1, DPLL2) for clock and/or frame pulse synchronization. DPLL1 is the main DPLL and is always enabled. To save on power, DPLL2 is disabled by default. For applications where DPLL2 is required, it must be enabled using the dpll_en bit of the dpll2_ctrl_0register (0x2A). Table 1 shows a feature summary for both DPLLs.FeatureDPLL1DPLL2Modes of Operation Free-run, Normal (locked), Holdover Free-run, Normal (locked), Holdover Loop Bandwidth User selectable: 14Hz, 28Hz, or wideband 1 (890Hz / 56Hz / 14Hz)1. In the wideband mode, the loop bandwidth depends on the frequency of the reference input. For reference frequencies equal to or greater than 64kHz, the loop bandwidth = 890Hz. For reference frequencies equal to or greater than 8kHz and less than 64 kHz, the loop bandwidth = 56Hz. For reference frequencies equal to 2kHz, the loop bandwidth is equal to 14Hz.Fixed: 14HzPhase Slope Limiting User selectable: 885ns/s, 7.5µs/s, 61µs/s, or unlimited User selectable: 61µs/s, or unlimited Pull-in Range Fixed: 130ppmFixed: 130ppmHoldover ParametersSelectable Update Times: 26ms, 1s, 10s, 60s, and Selectable Holdover Post Filter BW: 18mHz, 2.5Hz, 10Hz. Fixed Update Time: 26ms No Holdover Post FilteringHoldover Frequency AccuracyBetter than 1ppb (Stratum 3E) initial frequency offset. Frequency drift depends on the 20MHz external oscillator.Better than 50ppb (Stratum 3) initial frequency offset. Frequency drift depends on the 20MHz external oscillator.Reference Inputs Ref0 to Ref7Ref0 to Ref7Sync Inputs Sync0, Sync1, Sync2Sync inputs are not supported.Input Reference Selection/Switching Automatic (based on programmable priority and revertiveness), or manual Automatic (based on programmable priority and revertiveness), or manual Hitless Ref Switching Can be enabled or disabledCan be enabled or disabled Output Clocks apll_clk0, apll_clk1, p0_clk0, p0_clk1, p1_clk0, p1_clk1, fb_clk.p0_clk0, p0_clk1, p1_clk0, p1_clk1.Output Frame Pulses apll_fp0, apll_fp1, p0_fp0, p0_fp1 synchronized to active sync reference.p0_fp0, p0_fp1 not synchronized to sync reference.External Pins Status IndicatorsLock, HoldoverNoneTable 1 - DPLL1 and DPLL2 FeaturesZL30120Data Sheet1.2 DPLL Mode ControlBoth DPLL1 and DPLL2 independently support three modes of operation - free-run, normal and holdover. The mode of operation can be manually set or controlled by an automatic state machine as shown in Figure 2.Figure 2 - Automatic Mode State MachineFree-runThe free-run mode occurs immediately after a reset cycle or when the DPLL has never been synchronized to areference input. In this mode, the frequency accuracy of the output clocks is equal to the frequency accuracy of the external master oscillator. Lock AcquisitionThe input references are continuously monitored for frequency accuracy and phase regularity. If at least one of the input references is qualified by the reference monitors, then the DPLL will begin lock acquisition on that input. Given a stable reference input, the ZL30120 will enter in the Normal (locked) mode.Normal (locked)The usual mode of operation for the DPLL is the normal mode where the DPLL phase locks to a selected qualified reference input and generates output clocks and frame pulses with a frequency accuracy equal to the frequency accuracy of the reference input. While in the normal mode, the DPLL’s clock and frame pulse outputs comply with the MTIE and TDEV wander generation specifications as described in Telcordia and ITU-T telecommunication standards.HoldoverWhen the DPLL operating in the normal mode loses its reference input, and no other qualified references are available, it will enter the holdover mode and continue to generate output clocks based on historical frequency data collected while the DPLL was synchronized.ResetAnother reference is qualified and availablefor selectionPhase lock on the selected reference is achievedLock AcquisitionNormal (Locked)No references are qualified and available for selectionFree-RunHoldoverSelected referencefailsAll references are monitored for frequency accuracy and phase regularity, and at least one reference is qualified.Normal (Locked)ZL30120Data Sheet1.3 Ref and Sync InputsThere are eight reference clock inputs (ref0 to ref7) available to both DPLL1 and DPLL2. The selected reference input is used to synchronize the output clocks. Each of the DPLLs have independent reference selectors which can be controlled using a built-in state machine or set in a manual mode.Figure 3 - Reference and Sync InputsIn addition to the reference inputs, DPLL1 has three optional frame pulse synchronization inputs (sync0 to sync2)used to align the output frame pulses. The sync n input is selected with its corresponding ref n input, where n = 0, 1,or 2. Note that the sync input cannot be used to synchronize the DPLL, it only determines the alignment of the frame pulse outputs. An example of output frame pulse alignment is shown in Figure 4.Figure 4 - Output Frame Pulse Alignmentref7:0sync2:0DPLL2DPLL1ref napll/p0/p1_clk xapll/p0_fp xWithout a frame pulse signal at the sync input, the output frame pulses will align to any arbitrary cycle of its associated output clock.sync n - no frame pulse signal presentWhen a frame pulse signal is present at the sync input, the DPLL will align the output frame pulses to the output clock edge that is aligned to the input frame pulse.ref n apll/p0/p1_clk xapll/p0_fp xsync nn = 0, 1, 2x = 0, 1n = 0, 1, 2x = 0, 1ZL30120Data Sheet Each of the ref inputs accept a single-ended LVCMOS clock with a frequency ranging from 2kHz to 77.76MHz. Built-in frequency detection circuitry automatically determines the frequency of the reference if its frequency is within the set of pre-defined frequencies as shown in Table 2. Custom frequencies definable in multiples of 8kHz are also available.2 kHz8 kHz64 kHz1.544 MHz2.048 MHz6.48 MHz8.192 MHz16.384 MHz19.44 MHz38.88 MHz77.76 MHzCustom ACustom BTable 2 - Set of Pre-Defined Auto-Detect Clock FrequenciesEach of the sync inputs accept a single-ended LVCMOS frame pulse. Since alignment is determined from the rising edge of the frame pulse, there is no duty cycle restriction on this input, but there is a minimum pulse width requirement of 5ns. Frequency detection for the sync inputs is automatic for the supported frame pulse frequencies shown in Table 3.166.67 Hz(48x 125 µs frames)400 Hz1 kHz2 kHz8 kHz64 kHzTable 3 - Set of Pre-Defined Auto-Detect Sync Frequencies1.4 Ref and Sync MonitoringAll input references (ref0 to ref7) are monitored for frequency accuracy and phase regularity. New references are qualified before they can be selected as a synchronization source, and qualified references are continuously monitored to ensure that they are suitable for synchronization. The process of qualifying a reference depends on four levels of monitoring.Single Cycle Monitor (SCM)The SCM block measures the period of each reference clock cycle to detect phase irregularities or a missing clock edge. In general, if the measured period deviates by more than 50% from the nominal period, then an SCM failure (scm_fail) is declared.ZL30120Data SheetCoarse Frequency Monitor (CFM)The CFM block monitors the reference frequency over a measurement period of 30µs so that it can quickly detect large changes in frequency. A CFM failure (cfm_fail) is triggered when the frequency has changed by more than 3%or approximately 30000ppm.Precise Frequency Monitor (PFM)The PFM block measures the frequency accuracy of the reference over a 10 second interval. To ensure an accurate frequency measurement, the PFM measurement interval is re-initiated if phase or frequency irregularities are detected by the SCM or CFM. The PFM provides a level of hysteresis between the acceptance range and the rejection range to prevent a failure indication from toggling between valid and invalid for references that are on the edge of the acceptance range.When determining the frequency accuracy of the reference input, the PFM uses the external oscillator’s output frequency (f ocsi ) as its point of reference. Guard Soak Timer (GST)The GST block mimics the operation of an analog integrator by accumulating failure events from the CFM and the SCM blocks and applying a selectable rate of decay when no failures are detected.As shown in Figure 5, a GST failure (gst_fail) is triggered when the accumulated failures have reached the upper threshold during the disqualification observation window. When there are no CFM or SCM failures, the accumulator decrements until it reaches its lower threshold during the qualification window.Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM FailuresAll sync inputs (sync0 to sync2) are continuously monitored to ensure that there is a correct number of reference clock cycles within the frame pulse period.1.5 Output Clocks and Frame PulsesThe ZL30120 offers a wide variety of outputs including two low jitter LVCMOS (apll_clk0, apll_clk1) output clocks and four programmable LVCMOS (p0_clk0, p0_clk1, p1_clk0, p1_clk1) output clocks. In addition to the clock outputs, two LVCMOS frame pulse outputs (apll_fp0, apll_fp1) and two LVCMOS programmable frame pulses (p0_fp0, p0_fp1) are also available.The feedback clock (fb_clk ) of DPLL1 is available as an output clock. Its output frequency is always equal to DPLL1’s selected input frequency.refCFM or SCM failuresupper thresholdlower thresholdt d - disqualification timet q - qualification time = n * t dt dt qgst_failZL30120Data SheetThe output clocks and frame pulses derived from the low jitter APLL are always synchronous with DPLL1, and the clocks and frame pulses generated from the programmable synthesizers can be synchronized to either DPLL1 or DPLL2. This allows the ZL30120 to have two independent timing paths.Figure 6 - Output Clock ConfigurationThe supported frequencies for the output clocks and frame pulses are shown in Table 4.apll_clk0, apll_clk1(LVCMOS)11. The apll_clk x outputs can generate either SONET/SDH or Ethernet frequencies (25MHz, 50MHz). p0_clk0, p1_clk0(LVCMOS)p0_clk1, p1_clk1(LVCMOS)apll_fp0, apll_fp1, p0_fp0, p0_fp1(LVCMOS)22. apll_fp x frequencies are available only when the low jitter apll is generating SONET/SDH frequencies6.48 MHz 2 kHz p x _clk0 p x _clk1 =2M166.67 Hz (48x 125 µs frames)9.72 MHz N * 8 kHz (up to 100MHz)400 Hz 12.96 MHz 1 kHz 19.44 MHz 2 kHz 25.92 MHz 4 kHz 38.88 MHz 8 kHz 51.84 MHz 32 kHz 77.76 MHz 64 kHz25 MHz 50 MHzTable 4 - Output Clock and Frame Pulse Frequenciesp0_clk0p0_fp0p0_clk1p0_fp1 P0 Synthesizerp1_clk0p1_clk1P1 Synthesizerapll_clk0apll_fp0apll_clk1apll_fp1Low Jitter APLLFeedback Synthesizerfb_clkDPLL2DPLL1ZL30120Data Sheet1.6 Configurable Input-to-Output and Output-to-Output DelaysThe ZL30120 allows programmable static delay compensation for controlling input-to-output and output-to-output delays of its clocks and frame pulses.All of the output synthesizers (APLL, P0, P1, Feedback) locked to DPLL1 can be configured to lead or lag the selected input reference clock using the DPLL1 Fine Delay . The delay is programmed in steps of 119.2ps with a range of -128 to +127 steps giving a total delay adjustment in the range of -15.26ns to +15.14ns. Negative values delay the output clock, positive values advance the output clock. Synthesizers that are locked to DPLL2 are unaffected by this delay adjustment.In addition to the fine delay introduced in the DPLL1 path, the APLL, P0, and P1 synthesizers have the ability to add their own fine delay adjustments using the P0 Fine Delay , P1 Fine Delay , and APLL Fine Delay . These delays are also programmable in steps of 119.2ps with a range of -128 to +127 steps.In addition to these delays, the single-ended output clocks of the APLL, P0, and P1 synthesizers can be independently offset by 90, 180 and 270 degrees using the Coarse Delay . The output frame pulses (APLL, P0) can be independently offset with respect to each other using the FP Delay .Figure 7 - Phase Delay AdjustmentsDPLL1DPLL2P0 Fine Delayp0_clk0p0_clk1p0_fp0p0_fp1 P0 SynthesizerCoarse DelayCoarse Delay FP Delay FP Delay fb_clkp1_clk0p1_clk1P1 Fine DelayLow Jitter APLLapll_clk0apll_clk1apll_fp0apll_fp1APLL Fine DelayFeedback SynthesizerDPLL1 Fine DelayCoarse DelayCoarse Delay FP Delay FP DelayCoarse Delay Coarse DelayP1 SynthesizerZL30120Data Sheet 2.0 Software ConfigurationThe ZL30120 is mainly controlled by accessing software registers through the serial peripheral interface (SPI). The device can be configured to operate in a highly automated manner which minimizes its interaction with the system’s processor, or it can operate in a manual mode where the system processor controls most of the operation of the device.The following table provides a summary of the registers available for status updates and configuration of the device.Addr (Hex)RegisterNameResetValue(Hex)Description TypeMiscellaneous Registers00id_reg A4Chip and version identification and reset readyindication registerR01use_hw_ctrl00Allows some functions of the device to becontrolled by hardware pinsR/WInterrupts02ref_fail_isr FF Reference failure interrupt service register R 03dpll1_isr70DPLL1 interrupt service register StickyR 04dpll2_isr00DPLL2 interrupt service register StickyR 05ref_mon_fail_0FF Ref0 and ref1 failure indications StickyR 06ref_mon_fail_1FF Ref2 and ref3 failure indications.StickyR 07ref_mon_fail_2FF Ref4 and ref5 failure indications StickyR 08ref_mon_fail_3FF Ref6 and ref7 failure indications StickyR 09ref_fail_isr_mask00Reference failure interrupt service registermaskR/W 0A dpll1_isr_mask00DPLL1 interrupt service register mask R/W 0B dpll2_isr_mask00DPLL2 interrupt service register mask R/W 0C ref_mon_fail_mask_0FF Control register to mask each failure indicatorfor ref0 and ref1R/W0D ref_mon_fail_mask_1FF Control register to mask each failure indicatorfor ref2 and ref3R/W0E ref_mon_fail_mask_2FF Control register to mask each failure indicatorfor ref4 and ref5R/W。

ZLG500A读卡模块使用指南141

ZLG500A读卡模块使用指南版本1.412005年8月20日目 录§1 概述 (3)1.1 照片 (3)1.1.1 独立模块 (3)1.1.2 天线一体化模块 (3)1.2 特征 (4)1.3 电气特性 (4)§2 硬件描述 (5)2.1 引脚描述 (5)2.2 串行接口...............................................................................................................................6 §3 ZLG500三线三线串行读串行读串行读卡模块接口规范卡模块接口规范.. (7)3.1 接口原理 (7)3.2 时序图 (7)3.3 写数据MCU ZLG500 (8)§4 ZLG500读卡模块数据传输协议 (9)4.1 介绍 (9)4.2 协议 (9)4.2.1协议描述 (9)4.2.2 数据块格式 (9)4.3 ZLG500和MCU 命令C51函数(版本号1.4) (11)4.3.1 底层函数和高级函数 (11)4.3.2 状态值列表 (12)4.3.2版本说明 (13)4.4 函数描述 (13)4.4.1 请求Request (14)4.4.2 防碰撞Anticoll (15)4.4.3 选择Select (16)4.4.4 证实Authentication (17)4.4.5 暂停Halt (18)4.4.6 读Read (19)4.4.7 写Write (20)4.4.8 加Increment (21)4.4.9 减Decrement (22)4.4.10 恢复Restore (23)4.4.11 传送Transfer (24)4.4.12 装载密钥Load Key (25)4.4.13 复位Reset (26)4.4.14 获取信息Get Info (27)4.4.15 置位控制位Set Control Bit (28)4.4.16 清除控制位Clr Control Bit (29)4.4.17 配置Config (30)4.4.18检查写—Check Write (31)4.4.19输出蜂鸣器信号Buzzer (32)4.4.20读EEPROM (33)4.4.21写EEPROM (34)4.4.22关闭RC500—Close (35)4.4.23值操作 (36)4.4.24防碰撞2—Anticoll2 (37)4.4.25 证实2—Authentication2 (38)4.4.26 直接密码证实AuthKey (39)4.4.27多层防碰撞CascAnticoll (40)4.4.28多层选择Select (41)4.4.29写UltraLight—ULWrite (42)4.4.30带内部自动传送的值操作 (43)4.4.31写寄存器 (44)4.4.32读寄存器 (45)4.5 利用SPI_INIT()初始化SPI接口 (46)4.6 全局变量 (46)4.7 SPI看门狗定时器 (46)4.8 应用程序举例 (47)1 概述1.1 照片1.1.1独立模块需外加天线才可使用实际尺寸41.5mm25.3mm1.1.2天线一体化模块实际尺寸58mm×34.5mm1.2 特征!"四层电路板设计双面表贴EMC性能优良!"采用最新PHILIPS高集成ISO14443A读卡芯片MF RC500!"三线SPI接口能与任何MCU接口!"控制线输出口!"无源蜂鸣器信号输出口能用软件控制输出频率及持续时间!"能读写RC500内EEPROM!"发光二极管指示模块当前状态!"可提供C51函数库1.3 电气特性符号参数最小典型最大单位T STR环境或存储温度范围 -40 +150 O CO C+85+25T OP工作温度范围 -25V5.5V CC工作电压范围 4.55I CC1电流消耗config成功后75 MAI CC2电流消耗close成功后7 MA2 硬件描述2.1 引脚描述如照片所示J1为与天线的接口J2为与MCU的接口如下二表所示管脚符号描述J1-1 GND 地J1-2 TX1 天线发送1J1-3 GND 地J1-4 TX2 天线发送2J1-5 GND 地J1-6 RX 天线接收管脚符号类型描述J2-1 SCLK 输入三线SPI接口时钟线总是由外部MCU产生J2-2 SDA TA 双向数据线可双向传输J2-3 SS 双向传输启动线接MCU外部中断J2-4 VCC PWR 电源正端J2-5 RST 复位模块复位端若模块名后缀不带G如zlg500A T则高电平有效若模块名后缀带G如zlg500A TG则低电平有效或该端悬空J2-6 GND PWR 电源负端J2-7 CTRL 输出控制线输出J2-8 BZ 输出蜂鸣器信号输出2.2 串行接口ZLG500模块可方便地与任何MCU 进行接口如下图所示与MCS51单片机的典型接口三线分别为片选SS 时钟线SCLK 和数据线SDATA 主控制器的MCU 和读卡模块内的MCU 通过此三线相连三根线上的实际电平是双方口线状态逻辑线与的结果3 ZLG500三线三线串行读卡模块接口规范串行读卡模块接口规范3.1 接口原理接口空闲时主机SS=1SCLK=0SDATA=0从机SS=1SCLK=1SDATA=0其中SS和DATA是双向的而时钟线SCLK是单向的即时钟只能由主控制器产生该信号必须严格遵守时序规范否则将出现通信错误读卡模块必须释放该线SS 为数据发送使能若一方有数据要发送给另一方则该方控制SS线为低并在发送结束后将该线置高接收数据方不得控制该线双方必须遵守通信协议不得同时控制该线SDATA 为数据线由数据发送端控制数据接收端必须释放该线该线在一次传输开始时还同时作为数据接收端的响应信号以下几个概念必须搞清楚数据发送器在一次传输中控制SS信号和写数据的一方数据接收器在一次传输中响应SS信号和读数据的一方MCU 外部控制器在一次数据传输中可以是数据接收器或发送器但必须产生SCLK信号ZLG500本模块在一次数据传输中可以是数据接收器或发送器但必须接收SCLK信号3.2 时序图如图所示无论数据传输的方向如何SPI线上信号的波形总是如下由图中可以看出在SS为低的情况时钟和数据线上的信号才有效且在SCLK为低时SDATA变化在SCLK为高时SDATA应保持稳定以上传输中从数据发送器请求开始至数据接收器响应的时间是不确定的取决接收器内的MCU是否忙有必要设置一个看门狗定时器对数据接收器的响应进行监视一旦接收器响应则MCU必须根数据传输的方向严格控制以下几个时间以确保数据传输无误t1—数据接收器响应至MCU产生第一个SCLK上升沿的时间t2—两个字节传输之间SCLK低电平的持续时间t3—传输最后一个字节的最后一位的SCLK信号的上升沿至SS上升沿的时间tH—SCLK信号的高电平持续时间tL—SCLK信号的低电平持续时间在数据传输的不同方向时对时间t1— t3tH 和tL 都有各自不同的要求3.3 写数据MCU ZLG500除响应信号外三根线上的信号全由MCU 产生MCU 在SS 线上产生一个下降沿发出请求数据传输的信号等待ZLG500响应后本次数据传输开始ZLG500将在SCLK 为高时读取SDATA 线上的数据传输完毕后MCU 应在SS 线上产生一个上升沿结束本次传输见下表动作序号 动作发出者动作 动作接收者 动作说明1 MCU 置SDATA为输入SCLK=0SS= ZLG500 本次数据传输开始请求 2 ZLG500 SDATA = MCU 本次数据传输响应 3 MCU 置SDATA 为输出且输出串行数据 ZLG500 数据传输4 MCU SCLK=延时 ZLG500 MCU 产生时钟脉冲高电平时ZLG500读数据 5 MCU 重复动作34传送N 8位 ZLG500 数据传输N 字节 6 MCU SS=SDATA=0SCLK =0 ZLG500 本次数据传输结束传输过程中必须严格遵守以下时间要求 t1>7s t2>14s tH>7s tL>9s t3=任意3.4读数据MCU ZLG500响应信号SCLK 信号由MCU 产生SS 信号和SDATA 信号由ZLG500产生ZLG500会在SS 线上产生一个下降沿发出请求数据传输的信号等待MCU 响应后本次数据传输开始MCU 将在SCLK 为高时读取SDATA 线上的数据传输完毕后ZLG500将会在SS 线上产生一个上升沿结束本次传输见下表动作序号 动作发出者动作动作接收者 动作说明1 ZLG500 SDATA =1SS= MCU 本次数据传输开始请求2 MCU 置SDATA 为输入 ZLG500 本次数据传输响应3 ZLG500 SDATA =串行数据 MCU 数据传输4 MCU SCLK=延时 ZLG500 MCU 产生时钟且读取数据 5 双方 重复动作34传送N 8位 双方 数据传输N 字节 6 ZLG500 SS =SDATA =0 MCU 本次数据传输结束传输过程中必须严格遵守以下时间要求t1>14s t2>16s tH>6s tL>6s t3>9s4 ZLG500读卡模块数据传输协议4.1 介绍本文档描述了MIFARE串行读卡模块ZLG500与主机微处理器之间的串行通信软件的通信协议和命令ZLG500是一个简单的串行读写模块它可以读写MIFARE无线智能卡在这个器件中包括了一个PCB天线提供了一个三线通信接口CMOS电平SPI可受控于主机微处理器4.2 协议4.2.1协议描述通信必须先由MCU发送命令和数据给ZLG500ZLG500执行命令完毕后将命令执行的状态和响应数据发回MCU开始通信前收发双方必须处于空闲状态ZLG500的RST有两种接法一是接硬件复位电路如阻容复位等这样系统上电后必须要等待ZLG500复位结束二是接外部MCU的一个I/O口由MCU控制复位推荐使用第二种方法这样在ZLG500出现异常时可由MCU控制复位首先MCU发出SS下降沿信号然后等待ZLG500在SDATA线上的响应若在50ms内未检测到此响应则退出本次传输将错误代码返回给主程序由主程序进行错误处理若ZLG500正确响应则MCU可将命令和数据发送出去然后MCU等待ZLG500发回的状态和响应数据也即等待SS线上的下降沿的产生此时的MCU可用软件查询也可用外部中断若在500ms内未检测到此信号则退出本次传输且向主程序报告错误代码若正确检测到SS信号则可接收状态和数据4.2.2 数据块格式4.2.2.1 MCU ZLG500命令模式SeqNr Command Len Data[0N] BCC INFO[0] . . . . . . INFO[n]SeqNr 1 Byte 数据交换包的序号Command 1 Byte 命令字符Len 1 Byte 数据的长度Data[]Len Byte 数据字节BCC1Byte的BCC校验4.2.2.2 ZLG500MCU响应模式SeqNr status Len Data[0N] BCC INFO[0] . . . . . . INFO[n]SeqNr 1 Byte 数据交换包的序号status 1 Byte 状态字符Len 1 Byte 数据的长度Data[]Len Byte 数据字节BCC1Byte的BCC校验4.2.2.3 数据块格式描述!"每个字节命令或数据传输时高位在先!"数据交换包的序号由MCU发送数据块时产生在经过一次正确的数据交换后主机在发送下一个命令时将数据包的序号加1ZLG500返回最近接收的包序号通常主机应用程序最好检查命令/响应包交换时的数据包的序号!"不管在执行命令时出现了任何错误响应包中的数据长度为0Len = 0!"BCC校验码计算数据块中所有的INFO字节然后将结果传送到数据块的最后一个字节如下式所示INFO[n] = BCC = ~INFO[0] ⊕ INFO[1] ⊕ ... ⊕ INFO[n-1](⊕ ... XOR~…NOT)4.3 ZLG500和MCU 命令C51函数(版本号1.4) 4.3.1 底层函数和高级函数命令 参数名称数值发送接收说明Request 0x41 _Mode _TagType 发出询问命令检查在有效范围内是否有卡存在Anticoll 0x42 _Bcnt _SNR 开始防冲突操作返回卡的序号Anticoll2 0x71 _Encoll,_Bcnt _SNR 可禁止或允许多张卡进入 CascAnticoll* 0x74 _Bcnt,_Select_Code _SNR 可实现三层防碰撞协议 Select 0x43 _SNR _Size 选择卡返回卡的存贮容量 CascSelect* 0x75_Select_Code, _SNR _Sak可实现三层选择Authentication 0x44 _Mode,_SecNr -- 开始验证操作 Authentication2 0x72 _Mode,_SecNr,_KeyNr 可选择密匙区验证 AuthKey 0x73 _Mode,_SecNr,_Key(6) -- 直接密码验证 Halt 0x45 -- -- 将卡置于挂起模式 Read 0x46 _Adr _Data 从卡中相应地址中读出一个16字节的块Write 0x47 _Adr,_Data -- 向卡中相应地址写入一16字节的数据块ULWrite* 0x76_Adr,_Data -- 向mifare UltraLight 卡中相应地址页写入4字节数据 Increment 0x48 _Adr,_Value -- 增加访问单元块的字节数并将结果保存在卡的内部寄存器Decrement 0x49 _Adr,_Value -- 减少访问单元块的字节数并将结果保存在卡的内部寄存器 Resore 0x4A _Adr -- 将所访问单元块的字节数保存在卡的内部寄存器中 Transfer 0x4B_Adr --将卡内部寄存器的内容转输到访问快的字节数Value 0x70_Mode,_Adr,_Value,_Trans_Adr 包含加减恢复函数并带自动传送ValueDebit* 0x77_Mode,_Adr,_Value -- 带内部自动传送的值操作支持Mifare Light LoadKey 0x4C _Mode,_SecNr,,_Nkey -- 改变存贮在EEPROM 中的密钥Reset 0x4E _Msec -- 关闭天线输出数ms 使卡复位 Get Info 0x4F -- _Info 读取固件信息RC500序列号 Set Control Bit0x50----将控制位置为高电平Clr Control Bit 0x51 -- -- 将控制位置为低电平 Config 0x52 -- -- 复位且配置RC500Write_Reg 0x3D_Reg,_Value写RC500内寄存器Read_Reg 0x3E _Reg *_Value 读RC500内寄存器Close 0x3F -- -- 关闭RC500 Check Write0x53_SNR,_Authmode,_Adr,_Data--将所传送的数据和上一次所写的数据进行比较Buzzer 0x60 _Freguence,_10ms -- 输出驱动无源蜂鸣器信号 Read E2 0x61 _Adr,_Length _Data 读RC500内EEPROM 的内容 Write E20x62_Adr,_Length,_Data-- 写数据到RC500内EEPROM Init_spi初始化spi 接口不与ZLG500通信4.3.2 状态值列表名称值 描述MI_OK, SPI_OK函数调用成功MI_NOTAGERR 1 在有效区域内没有卡MI_CRCERR 2 从卡中接收到了错误的CRC 校验和 MI_EMPTY 3 值溢出 MI_AUTHERR 4 不能验证MI_PARITYERR 5 从卡中接收到了错误的校验位 MI_CODEERR 6 通信错误MI_SENDRERR 8 在防冲突时读到了错误的串行码 MI_NOTAUTHERR 10 卡没有验证MI_BITCOUNTERR 11 从卡中接收到了错误数量的位 MI_BYTECOUNTERR 12 从卡中接收了错误数量的字节 MI_TRANSERR 14 调用Transfer 函数出错 MI_WRITEERR 15 调用Write 函数出错 MI_INCRERR 16 调用Increment 函数出错 MI_DECRERR 17 调用Decrment 函数出错 MI_READERR 18 调用Read 函数出错 MI_COLLERR 24 冲突错MI_QUIT 30 上一次了送命令时被打断 MIS_CHK_OK 0 Check Write 正确 MIS_CHK_FAILED 1 Check Write 出错 MIS_CHK_COMPERR 2 Check Write:写出错比较出错SPI_ERR 255 串行通信错误4.3.2版本说明一版本1.1对应于1.0增加了两个函数!"防碰撞Anticoll2可允许或禁止多张卡同时进入开线区!"证实Authentication2可选择不同的密匙区对一个扇区进行密码验证二版本1.2对应于1.1增加了一个函数!"直接密码证实AuthKey证实时6字节密码直接由主控制器MCU传入模块三版本1.3对应于1.2增加了四个函数!"多层防碰撞CascAnticoll支持多字节序列号!"多层选择CascSelect支持多字节序列号!"UL写函数ULWrite支持Mifare Ultralight四字节写!"自动传送值操作ValueDebit支持Mifare Light和pro四版本1.4相对于1.3增加了二个函数2004年8月10日升级!"写寄存器Write_Reg可直接控制RC500内的寄存器!"读寄存器Read_Reg可读出RC500内的寄存器4.4 函数描述下面是C51函数声明包含在头文件ZLG500.h中写应用程序时将其包含在应用函数中即可4.4.1 请求Request声明uchar mifs_request(uchar _Mode,uchar idata *_TagType);MCU ⇒ZLG500命令符0x41 长度 1Data[0]:_ModeZLG500 ⇒ MCU状态值MI_OK MI_NOTAGERRMI_BITCOUNTERR SPI_ERR长度2Data[0]: tagtype (低字节)Data[1]: tagtype (高字节)参数 _ModeALL=0请求天线范围内IDLE 状态的卡HALT 状态的除外ALL =1请求天线范围内的所有卡_tagtype 当发生错误时不返回任何内容Len=0描述此函数发送Request 命令检查在有效范围内是否有卡存在这个函数在选择一个新的卡是必须调用的ALL4.4.2防碰撞Anticoll声明uchar mifs_anticoll(uchar _Bcnt,uchar idata *_SNR);MCU ⇒ ZLG500命令符0x42长度 1Data[0]_BcntZLG500⇒ MCU状态值MI_OK MI_NOTAGERR MI_BITCOUNTERR SPI_RERR长度 4Data[0]snr(LL)Data[1]snr(LH)Data[2]snr(HL)Data[3]snr(HH)参数_Bcnt为预选卡所分配的位的个数通常Bcnt=0_SNR卡的序列号存贮在一个无符号的四字节数组中低字节放在地址处描述此函数开始防冲突操作必须在调用了Request命令后立即调用当知道了所要选择卡的序列号后就没有必要调用AntiColl此时调用了Request后直接调用Select函数即可4.4.3选择Select声明uchar mifs_select(uchar idata *_SNR,uchar idata *_Size);MCU ⇒ ZLG500命令符0x43长度 4Data[0]snr(LL)Data[1]snr(LH)Data[2]snr(HL)Data[3]snr(HH)ZLG500⇒ MCU状态值 MI_OK MI_QUIT MI_NOTAGERR MI_CRCERR MI_PAROTUERRMI_BITCOUNTERR SPI_ERR长度 1Data[0]_Size参数_SNR卡的序号存贮在一个无符号4字节字符数组中低字节放在代地址处_Size当Select命令返回值为MI_OK时A TS (answer to select)将返回主机描述这个函数选择某一个序列号的卡返回A TS字节给主机4.4.4 证实Authentication声明uchar mifs_authentication(uchar _Mode,uchar _SecNr);MCU ⇒ZLG500命令符 0x44 长度 2Data[0] _ModeData[1]_SecNrZLG500 ⇒ MCU状态值MI_OKMI_QUITMI_NOTAGERRMI_PAROTUERRMI_BITCOUNTERRSPI_ERR长度参数 _ModeAB = 0 利用密钥A 进行验证AB = 1利用密钥B 进行验证_SecNr所访问卡的扇区号描述 在对卡进行读写加减等操作前必须对卡进行验证若卡中的密钥与RC500中存储的密码相匹配则证实成功函数将返回MI_OKAB4.44.5暂停Halt4.声明uchar mifs_halt(void);MCU ⇒ ZLG500命令符0x45长度0ZLG500⇒ MCU状态值 MI_OK MI_QUIT MI_CODE SPI_ERR长度0参数无描述此函数将所选择卡置为挂起状态如果要进行重新选择则应用ALL模式调用Request命令或将卡复位如将卡离开天线操作区再进入或执行复位函数mifs_reset();4.4.6读Read描述uchar mifs_read(uchar _Adr,uchar idata *_Data);MCU ⇒ ZLG500命令符0x46长度 1Data[0]_AdrZLG500⇒ MCU状态值 MI_OK MI_QUIT MI_NOTAGERR MI_CRCERR MI_NOTAUTHERRMI_PAROTUERR MI_BITCOUNTERR SPI_ERR长度 16Data[0]所访问块的第一个字节Data[15]所访问块的最后一个字节参数_Adr所读数据地址描述此函数在所选的卡通过验证后读取一个16字节的块4.4.7写Write描述uchar mifs_write(uchar _Adr, uchar idata *_Data);MCU ⇒ ZLG500命令符0x47长度17Data[0]addressData[1]所访问块的第一个字节Data[16]所访问块的最后一个字节ZLG500⇒ MCU状态值 MI_OK MI_QUIT MI_NOTAGERR MI_NOTAUTHERR MI_WRITEERRMI_BITCOUNTERR SPI_ERR长度 0参数_Adr所写数据块地址063_Data16字节数据指针描述此函数在所选的卡通过验证后写入一个16字节的块4.4.8加Increment声明uchar mifs_increment(uchar _Adr,ulong idata *_Value);MCU ⇒ ZLG500命令符0x48长度 5Data[0]_AdrData[1]_Value(LL)Data[2]_Value(LH)Data[3]_Value(HL)Data[4]_Value(HH)ZLG500⇒ MCU状态值 MI_OK MI_QUIT MI_NOTAGERR MI_NOTAUTHERR MI_INCRERRMI_BITCOUNTERR SPI_ERR MI_INCRERR长度0参数_Adr所加数据块的地址_Value增加值贮在一个无符号的长整型变量4Byte中低地址存放高字节描述该函数读被访问的值块检查数据的结构用传输的值减值块的值并将结果贮存在卡的内部寄存器中值块有标准的格式不能自动进行对卡中EEPROM的写操作4.44.9减Decrement4.声明uchar mifs_decrement(uchar _Adr,ulong idata *_Value);MCU ⇒ ZLG500命令符0x49长度 5Data[0]_AdrData[1]_Value(LL)Data[2]_Value(LH)Data[3]_Value(HL)Data[4]_Value(HH)MSR⇒ 主机状态值 MI_OK MI_QUIT MI_NOTAGERR MI_NOTAUTHERR MI_DECRERRMI_BITCOUNTERR SPI_ERR长度0参数_Adr所减数据块的地址_Value减少值贮在一个无符号的长整型变量4Byte中低地址存放高字节描述该函数读被访问的值块检查数据的结构用传输的值减值块的值并将结果贮存在卡的内部寄存器中值块有标准的格式不能自动进行对卡中EEPROM的写操作4.4.44.1.100 恢复Restore 声明uchar mifs_restore(uchar _Adr);MCU ⇒Z LG500命令符0x4A长度1 Data[0] _AdrZLG500⇒M CU 状态值MI_OK, MI_QUIT, MI_NOTAGERR, MI_NOTAUTHERR, MI_DECRERR, MI_BITCOUNTERR, SPI_ERR, MIS_EMPTY长度 0 参数 _Adr所读块的地址描述该函数读被访问的值块且检查数据的结构并将结果贮存在卡的内部寄存器中不能自动进行对卡中EEPROM 的写操作4.4.44.1.111 传送Transfer 声明uchar mifs_transfer(uchar _Adr);MCU ⇒Z LG500命令符0x4B长度1 Data[0] _AdrZLG500⇒ MCU 状态值MI_OK, MI_QUIT, MI_NOTAGERR, MI_CODE, MI_BITCOUNTERR, MI_TRANSERR,MI_CODEERR, SPI_RERR长度 0 参数 _Adr卡中欲传输的块地址描述此函数将卡的内部寄存器内容转送给所选块地址在此操作前必须通过验证这个函数只能在Increment,Decrement,或Restore 操作后4.4.44.1.122 装载密钥Load Key 声明uchar mifs_load_key(uchar _Mode,uchar _SecNr,uchar *_Nkey);MCU ⇒ZLG500命令符0x4C长度 8Data[0] _ModeData[1] _SecNrData[2] _Nkey[0]: :Data[7]_Nkey[5]MSR ⇒主机 状态值 MI_OK MI_QUIT MI_AUTHERR SPI_ERR长度 0 参数 _ModeAB = 0 利用密钥A 进行验证AB = 1 利用密钥B 进行验证_SecNr: 密钥扇区号_Nkey: 6字节密钥首址描述这个函数将一个新的密钥写入到RC500的只写EEPROM 存贮器中AB4.4.44.1.133 复位Reset 声明uchar mifs_reset(uchar _Msec);MCU ⇒Z LG500命令符0x4E长度1 Data[0] _MsecZLG500⇒M CU 状态值 MI_OK MI_QUIT SPI_ERR长度 0 参数 _Msec射频电路关闭时间以毫秒为单位 描述该函数使射频电路关闭所规定的时间若_Msec=0射频电路部分将一直处于关闭状态一直到下一个Request 命令到来关闭射频能使天线内的所有卡复位举例_Msec = 0⇒ 射频电路关闭_Msec = 0x01⇒ 1 ms 射频电路关闭1ms _Msec= 0xFF⇒ 255 ms射频电路关闭255ms4.4.44.1.144 获取信息Get Info 声明uchar mifs_get_info(uchar idata *_Info);MCU ⇒Z LG500命令符 0x4F长度 0ZLG500⇒M CU 状态值 MI_OK MI_QUIT SPI_ERR 长度10 Data[0]产品类型标识0: : Data[4]产品类型标识4Data[5]RC500序列号0: : Data[8]RC500序列号3Data[9]软件版本号参数 _Info_Info[0]—_Info[4]为RC500的产品类型标识依次为0x30,0x88,0xf8,0x00,0xXX _Info[5]—_Info[8]为RC500的序列号 描述此函数返回一个包含有RC500的产品类型标识序列号和软件版本信息的数组4.4.44.1.155 置位控制位Set Control Bit 声明uchar mifs_set_control_bit();MCU ⇒Z LG500命令符 0x50长度 0ZLG500⇒M CU 状态值 MI_OK MI_QUIT SPI_ERR长度 0 描述此函数设置MIFARE 读卡器中的控制位为高电平4.4.44.1.166 清除控制位Clr Control Bit 声明uchar mifs_clr_control_bit();MCU ⇒Z LG500命令符 0x51长度 0ZLG500⇒M CU 状态值 MI_OK MI_QUIT SPI_ERR长度 0 描述此函数清除MIFARE 读卡器中的控制位4.44.17配置Config4.声明mifs_config(void);ucharMCU ⇒Z LG500命令符0x52长度0ZLG500⇒M CU状态值 MI_OK MI_QUIT SPI_ERR长度0参数说明模块每次上电复位之后都必须首先调用此函数对模块进行初始化才能进行进一步的操作4.4.18检查写Check Write声明uchar mifs_check_write(uchar idata *_SNR, uchar _Authmode, uchar _Adr, uchar idata *_Data);MCU ⇒Z LG500命令符0x53长度22Data[0]_SNR(LL)Data[1]_SNR(LH)Data[2]_SNR(HL)Data[3]_SNR(HH)Data[4]_AuthmodeData[5]_AdrData[6]块的第一个字节::Data[21]块的最后一个字节ZLG500⇒M CU状态值 MI_QUIT MIS_CHK_OK MIS_CHK_FAILED MIS_CHK_COMPERR SPI_ERR 长度0参数_SNR所要检查的卡的序号_Authmode上一次写命令时的验证模式_Adr所要检查的数据块的地址_Data所检查的数据描述此函数在数据写入卡的数据进行检查将重新进行Request/Select/Authenticated操作此函数进行将所给出的数据与相应地址的数据进行比较如果正确则返回MIS_CHK_OK信息如果两者间数据不相符则返回MIS_CHK_COMPERR信息发生其它任何错误时返回MIS_CHK_FAILED信息4.44.19输出蜂鸣器信号Buzzer4.声明mifs_buzzer(uchar _Frquence, uchar _10ms);MCU ⇒Z LG500命令符0x60长度 2Data[0]_FrequenceData[1]: _10msZLG500⇒M CU状态值 MI_OK SPI_ERR长度0参数_Frequence: 输出方波频率取值0255对应频率0.73—4K取值198对应2K_10ms: 方波输出持续时间取值025510ms的分辨率描述此函数输出一方波可驱动无源蜂鸣器频率和持续时间可调4.4.44.2.200 读EEPROM声明uchar mifs_read_E2(uchar _Adr,uchar _Length,uchar idata *_Data);MCU ⇒Z LG500命令符0x61长度2 Data[0]_AdrData[1]_LengthZLG500⇒M CU 状态值 MI_OK MI_QUIT MI_CRCERR MI_BITCOUNTERR SPI_ERR 长度_LengthData[0] byte… Data[_Length]byte参数 _Adr被读RC500内EEPROM 首址必须小于0x80_Length被读数据长度_Data读出数据缓冲区首址 描述此函数将RC500内EEPROM 的数据读出4.4.44.2.211 写EEPROM声明uchar mifs_write_E2(uchar _Adr,uchar _Length,uchar idata *_Data);MCU ⇒Z LG500命令符0x62长度_Length+2 Data[0]_AdrData[1]_LengthData[2]_Data[0]… Data[_Length+1]_Data[_Length-1]ZLG500⇒M CU 状态值 MI_OK MI_QUIT MI_CRCERR MI_BITCOUNTERR SPI_ERR长度 0参数 _Adr RC500内EEPROM 的写入首址取值范围0x300x7F_Length被写数据长度_Data写入数据缓冲区首址 描述此函数将数据写入RC500内EEPROM 中RC500内EEPROM 的0x00—0x0F 为只读产品信息区0x10—0x2F 为启动寄存器初始化文件区最好不要改写0x80—0x1FF 为只读密钥区可用LoadKey 写入4.4.44.2.222 关闭RC500Close 声明uchar mifs_close(void);MCU ⇒Z LG500命令符 0x3F长度 0ZLG500⇒M CU 状态值 MI_OK SPI_ERR长度 0参数描述此函数将RC500的复位管脚置为高电平关闭RC500使之电流最小若要重新启动则需调用Config()4.4.44.2.233 值操作声明uchar mifs_value(uchar _Mode, uchar _Adr, ulong idata *_Value, uchar _Trans _Adr);MCU ⇒Z LG500命令符0x70长度7 Data[0]_ModeData[1]_AdrData[2]_Value(LL)Data[3]_Value(LH)Data[4]_Value(HL)Data[5]_Value(HH)Data[6]_Trans_AdrZLG500⇒M CU 状态值MI_OK, MI_QUIT, MI_NOTAGERR, MI_CODE, MI_BITCOUNTERR, MI_TRANSERR, MI_CODEERR, SPI_RERR长度 0 参数_Mode: 0xC0—减0xC1—加0xC2恢复 _Adr 卡内块地址对该块进行值操作取值范围063_Value 当进行加或减操作时为加数或减数当进行恢复操作时该值为空值 _Trans_Adr传输块地址取值范围063描述此函数对卡内的某一块进行加减或数据备份该块必须为值块格式并支持自动传送4.4.24防碰撞2Anticoll2声明uchar mifs_anticoll2(uchar _Encoll, uchar _Bcnt,uchar idata *_SNR);MCU ⇒ ZLG500命令符0x71长度 2Data[0]_EncollData[1]_BcntZLG500⇒ MCU状态值MI_OK MI_NOTAGERR MI_BITCOUNTERR MI_COLLERR SPI_RERR长度 4Data[0]snr(LL)Data[1]snr(LH)Data[2]snr(HL)Data[3]snr(HH)参数_Encoll: 若为1则使能多张卡进入天线区若为0则不多张卡进入此时返回错误MI_COLLERR._Bcnt为预选卡所分配的位的个数通常Bcnt=0_SNR卡的序列号存贮在一个无符号的四字节数组中低字节放在地址处描述此函数开始防冲突操作必须在调用了Request命令后立即调用当知道了所要选择卡的序列号后就没有必要调用AntiColl此时调用了Request后直接调用Select函数即可4.4.25 证实2Authentication2 声明uchar mifs_authentication2(uchar _Mode, uchar _SecNr, uchar _KeyNr);MCU ⇒ZLG500命令符0x72 长度3Data[0]_ModeData[1]_SecNrData[2]_KeyNrZLG500 ⇒ MCU状态值MI_OKMI_QUITMI_NOTAGERRMI_PAROTUERRMI_BITCOUNTERR SPI_ERR长度 0 参数 _ModeAB = 0 利用密钥A 进行验证AB = 1 利用密钥B 进行验证_SecNr所访问卡的扇区号_KeyNr用于证实的密匙区号 描述在对卡进行读写加减等操作前必须对卡进行验证若卡中的密钥与RC500中所选择的密码相匹配则证实成功函数将返回MI_OKAB4.4.26 直接密码证实AuthKey 声明uchar mifs_authentication2(uchar _Mode, uchar _SecNr, uchar *_Key);主机 ⇒ 读卡器命令符0x73 长度8Data[0]_ModeData[1]_SecNrData[2]_Key[0] …Data[7]_Key[5]读卡器 ⇒ 主机状态值MI_OKMI_QUITMI_NOTAGERRMI_PAROTUERRMI_BITCOUNTERR COMM_ERR长度 0 参数 _ModeAB = 0 利用密钥A 进行验证AB = 1 利用密钥B 进行验证_SecNr所访问卡的扇区号 _Key用于证实的密码首址描述在对卡进行读写加减等操作前必须对卡进行验证若卡中的密钥与所传输的密码相匹配则证实成功函数将返回MI_OKAB4.4.27多层防碰撞CascAnticoll声明uchar mifs_Cascanticoll(uchar _Select_Code,uchar _Bcnt,uchar *_SNR);主机⇒ 读卡器命令符0x74长度 2Data[0]_Select_CodeData[1]_Bcnt读卡器⇒ 主机状态值MI_OK MI_QUIT MI_NOTAGERR MI_BITCOUNTERR COMM_ERR长度 4Data[0]snr(LL)Data[1]snr(LH)Data[2]snr(HL)Data[3]snr(HH)参数_Select_Code防碰撞层级编码一层0x93二层0x95三层0x97_Bcnt为预选卡所分配的位的个数通常Bcnt=0_SNR卡的序列号存贮在一个无符号的四字节数组中低字节放在地址处描述此函数开始防冲突操作必须在调用了Request命令后立即调用当知道了所要选择卡的序列号后就没有必要调用AntiColl此时调用了Request后直接调用Select函数即可4.4.28多层选择Select声明uchar mifs_CascSelect(uchar _Select_Code, uchar *_SNR,uchar *_Sak);主机⇒ 读卡器命令符0x75长度 5Data[0]_Select_CodeData[1]snr(LL)Data[2]snr(LH)Data[3]snr(HL)Data[4]snr(HH)读卡器⇒ 主机状态值MI_OK, MI_QUIT, MI_NOTAGERR, MI_CRCERR, MI_PARITYERR,MI_BITCOUNTERR,COMM_ERR长度 1Data[0]_Sak参数_Select_Code防碰撞层级编码一层0x93二层0x95三层0x97_SNR卡的序号存贮在一个无符号4字节字符数组中低字节放在代地址处_Sak当Select命令返回值为MI_OK时Sak将返回主机若_Sak.2为1则表示还有序列号的一部分未读出应进行下一层的选择否则选择结束描述这个函数选择某一个序列号的卡返回A TS字节给主机4.4..4.229写UltraLight ULWrite描述uchar mifs_ULWrite(uchar _Adr, uchar *_Data);主机⇒ 读卡器命令符0x76长度 5Data[0]页地址Data[1]所访问块的第一个字节Data[4]所访问块的最后一个字节读卡器⇒ 主机状态值 MI_OK MI_QUIT MI_NOTAGERR MI_NOTAUTHERR MI_WRITEERRMI_BITCOUNTERR COMM_ERR长度 0参数_Adr所写数据块地址015_Data4字节数据指针描述写入一个4字节的数据4.44.30带内部自动传送的值操作4.声明uchar mifs_ValueDebit(uchar _Mode, uchar _Adr, ulong *_Value);主机⇒读卡器命令符0x77长度 6Data[0]_ModeData[1]_AdrData[2]_Value(LL)Data[3]_Value(LH)Data[4]_Value(HL)Data[5]_Value(HH)读卡器⇒主机状态值MI_OK, MI_QUIT, MI_NOTAGERR, MI_CODE, MI_BITCOUNTERR, MI_TRANSERR, MI_CODEERR, COMM_RERR长度 0参数_Mode: 0xC0—减Mifare Light只支持减0xC1—加0xC2恢复_Adr卡内块地址对该块进行值操作取值范围063_Value当进行加或减操作时为加数或减数当进行恢复操作时该值为空值描述此函数对卡内的某一块进行加减或数据备份该块必须为值块格式并支持内部自动传送支持Mifare Light4.4.31写寄存器声明uchar mifs_write_reg(uchar _Reg,uchar _Value);主机⇒读卡器命令符0x3d长度 2Data[0]_RegData[1]_Value读卡器⇒主机状态值MI_OK , COMM_RERR长度 0参数_Reg寄存器地址_Value寄存器值描述此函数可对RC500内的寄存器直接进行控制在某些应用中是比较方便的例如1向地址0x11写入值0x59或0x5a可关闭一个发送管脚从而节省功耗2向地址0x12写入0x01至0x3f之间的一个值可以控制天线发送管脚的电导率值越大电导率越高功耗越大读卡距离越远反之功耗越低读卡距离越近4.4.32读寄存器声明uchar mifs_read_reg(uchar _Reg,uchar *_Value);主机⇒读卡器命令符0x3e长度 1Data[0]_Reg读卡器⇒主机状态值MI_OK , COMM_RERR长度 1Data[0]寄存器值参数_Reg寄存器地址*_Value寄存器值地址描述此函数可读RC500内的寄存器的值4.5 利用spi_init()初始化SPI接口声明spi_ini (void);void描述此函数将SPI接口初始化成空闲状态接SS线的外部中断1为下降沿触发且将定时器1配置成SPI接口的看门狗定时器4.6 全局变量在ZLG500.C中使用了二个全局变量一是通信数据缓冲区spi_buffer[26]所有的要通过SPI接口发送和接收的数据都放在这里包括序号命令/状态长度和BCC等为了方便地访问这些变量定义了如索引常量#defineSEQNR#define COMMAND 11STA TUS#define#define LENGTH 23MODE#defineBCNT3#defineADR 3#define3#defineSERNRSIZE 3#defineTIME 3#define#define TAGTYPE 3INFO 3#define#define4SECNR#define DA TABYTES 4V ALUE4#defineNKEY5#define#define AUTHMODE 7#define ADRCHKWR 8#define DA TACHKWR 9二是标志位newdata当外部中断1中断接收到新数据时该位置位4.7 SPI看门狗定时器定时器0或1作为SPI接口看门狗定时器该定时器被设置成50ms溢出发送时开定时器中断若中断之前通信未能完成ZLG500在SDA TA线上未返回响应信号而造成该定时器产生中断则取消本次传输发送子程序返回SPI_ERR接收时关中断用软件判断溢出次数若在500ms内未收到ZLG500返回的数据SS线上未产生下降沿则退出本次命令的执行命令返回SPI_ERR广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 4.8 应用程序举例例子读出RC500和MIFARE 卡的序列号然后选择一个卡将该卡的20块初始化成值块且备份到21块中最后使该卡进入HALT 状态且驱动2KHz 蜂鸣器响200毫秒 将ZLG500.c mface_3.asm 及主程序文件main.c 放于同一项目中然后在主程序中输入以下代码#include "zlg500.h" #include “string.h” sbit zlg500_RST=P1^2; //假若ZLG500的复位接到MCU 的P1.2口uchar idata card_snr[4]; uchar idata RC500_snr[4];uchar code Nkey_a[6] = {0xA0, 0xA1, 0xA2, 0xA3, 0xA4, 0xA5}; uchar code Nkey_b[6] = {0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF}; main() { uchar idata tt[2]; uchar idata size; uchar idata bankdata[16]; ulong idata value=1; uchar i,j;zlg500_RST =1; //使ZLG500复位 for(i =255;i>0;i--) for(j =255;j>0;j--); zlg500_RST =0; for(i =255;i>0;i--)for(j =255;j>0;j--); spi_init(); EA =1;i =mifs_config(); //ZLG500配置 i =mifs_get_info(bankdata); //读信息memcpy(RC500_snr,&bankdata[8],4); //存RC500序列号 mifs_load_key(KEYA,5,Nkey_b); //装载密钥 while(1) {while(mifs_request(IDLE,tt)!=0); //请求 if(mifs_anticoll(0,card_snr)!=0) continue; //防碰撞 if(mifs_select(card_snr,&size)!=0) continue; //选择 if(mifs_authentication(KEYA,5)!=0) continue; //证实 bankdata[0]=0x10; bankdata[4]=~0x10;广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 bankdata[8]=0x10;for(i=1;i<4;i++){bankdata[i]=0x00;bankdata[4+i]=0xff;bankdata[8+i]=0x00;}bankdata[12]=0x14;bankdata[13]=~0x14;bankdata[14]=0x14;bankdata[15]=~0x14;if(mifs_write(20,bankdata)!=0) continue;//写一个值块if(mifs_check_write(card_snr,KEYA,20,bankdata)!=0) continue;//检查写if(mifs_restore(20)!=0) continue;//恢复20块的数据if(mifs_transfer(21)!=0) continue;//传送到21块if(mifs_read(21,bankdata)!=0) continue;//读出mifs_halt(); //使卡进入HALT状态mifs_buzzer(198,20);//蜂鸣器口输出2KHz 方波持续200毫秒 }}。

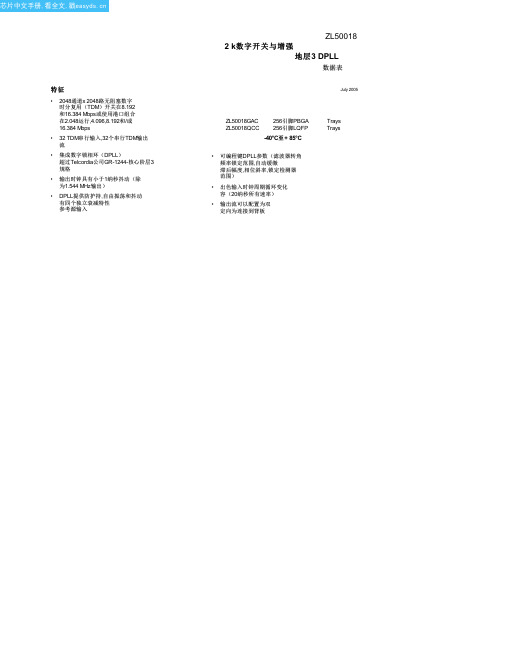

ZL50018GAG2中文资料(Zarlink Semiconductor)中文数据手册「EasyDatasheet - 矽搜」

数据表

该装置包含两种类型内部存储器 - 数据存储器和连接存贮器.有四种模式 操作 - 连接模式,消息模式,BER模式和高阻抗模式.在连接模式下, 连接存贮器内容限定,对于每个输出流和信道,源数据流和信道 (实际要输出数据存储在数据存储器中).在消息模式中,连接存储器用于 微处理器数据存储.采用卓联消息模式能力,微处理器数据可以 广播到在每个通道为基础数据输出流.传输控制这个功能是有用, 状态信息外部电路或其他TDM设备.在BER模式输出信道数据被替换为 从32PRBS发生器1,其产生2伪随机比特序列(PRBS) 输入侧通道可以被路由到32位差错检测器之一.在高阻抗模式中选择输出通道可以置于高阻抗状态.

ZL50018

数据表

目录

特征 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 应用. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 说明. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 更改总结. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

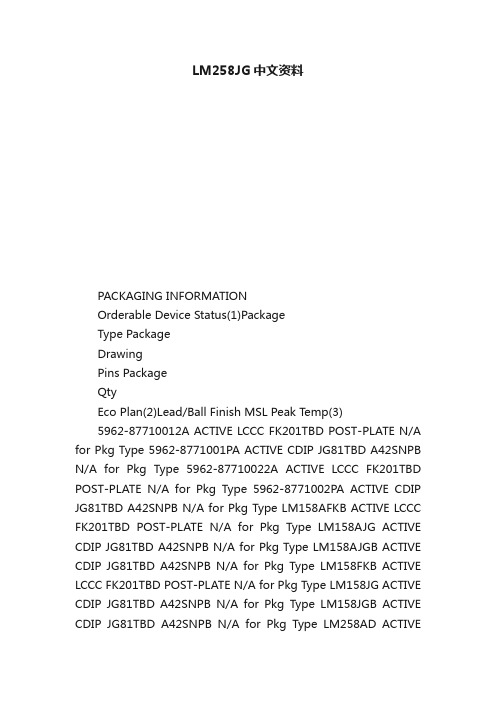

LM258JG中文资料

LM258JG中文资料PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-87710012A ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type 5962-8771001PA ACTIVE CDIP JG81TBD A42SNPB N/A for Pkg Type 5962-87710022A ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type 5962-8771002PA ACTIVE CDIP JG81TBD A42SNPB N/A for Pkg Type LM158AFKB ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type LM158AJG ACTIVE CDIP JG81TBD A42SNPB N/A for Pkg Type LM158AJGB ACTIVE CDIP JG81TBD A42SNPB N/A for Pkg Type LM158FKB ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type LM158JG ACTIVE CDIP JG81TBD A42SNPB N/A for Pkg Type LM158JGB ACTIVE CDIP JG81TBD A42SNPB N/A for Pkg Type LM258AD ACTIVESOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258ADE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258ADG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258ADGKR ACTIVE MSOP DGK82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258ADGKRG4ACTIVE MSOP DGK82500Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258ADR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258ADRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258ADRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258AP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLM258APE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLM258D ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258DE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258DG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258DGKR ACTIVE MSOP DGK82500Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258DGKRG4ACTIVE MSOP DGK82500Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258DR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258DRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258DRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM258P ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)LM258PE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLM2904AVQDR ACTIVE SOIC D82500Pb-Free(RoHS)CU NIPDAU Level-2-250C-1YEAR/Level-1-235C-UNLIMLM2904AVQDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904AVQPWR ACTIVE TSSOP PW82000TBD CU NIPDAU Level-1-250C-UNLIM LM2904AVQPWRG4ACTIVE TSSOP PW82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904D ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904DE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904DG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904DGKR ACTIVE MSOP DGK82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904DGKRG4ACTIVE MSOP DGK82500Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904DR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904DRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904DRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904P ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLM2904PE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLM2904PSR ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904PSRE4ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904PSRG4ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904PW ACTIVE TSSOP PW8150Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904PWE4ACTIVE TSSOP PW8150Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904PWG4ACTIVE TSSOP PW8150Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM LM2904PWLE OBSOLETE TSSOP PW8TBD Call TI Call TILM2904PWR ACTIVE TSSOP PW82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904PWRE4ACTIVE TSSOP PW82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904PWRG4ACTIVE TSSOP PW82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904QD OBSOLETE SOIC D8TBD Call TI Call TILM2904QDR NRND SOIC D82500Pb-Free(RoHS)CU NIPDAU Level-2-250C-1YEAR/Level-1-235C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)LM2904QP OBSOLETE PDIP P8TBD Call TI Call TILM2904VQDR ACTIVE SOIC D82500Pb-Free(RoHS)CU NIPDAU Level-2-250C-1YEAR/Level-1-235C-UNLIMLM2904VQDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM2904VQPWR ACTIVE TSSOP PW82000TBD CU NIPDAU Level-1-250C-UNLIM LM2904VQPWRG4ACTIVE TSSOP PW82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358AD ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358ADE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358ADG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358ADGKR ACTIVE MSOP DGK82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358ADGKRG4ACTIVE MSOP DGK82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358ADR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358ADRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358ADRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358AP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLM358APE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLM358APW ACTIVE TSSOP PW8150Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358APWE4ACTIVE TSSOP PW8150Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358APWG4ACTIVE TSSOP PW8150Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358APWR ACTIVE TSSOP PW82000Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358APWRE4ACTIVE TSSOP PW82000Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358APWRG4ACTIVE TSSOP PW82000Green(RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358D ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358DE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358DG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358DGKR ACTIVE MSOP DGK82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358DGKRG4ACTIVE MSOP DGK82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358DR ACTIVE SOIC D82500Green(RoHS&CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)LM358DRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358DRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358P ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLM358PE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type LM358PSLE OBSOLETE SO PS8TBD Call TI Call TILM358PSR ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358PSRE4ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358PSRG4ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358PW ACTIVE TSSOP PW8150Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358PWE4ACTIVE TSSOP PW8150Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358PWG4ACTIVE TSSOP PW8150Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM LM358PWLE OBSOLETE TSSOP PW8TBD Call TI Call TILM358PWR ACTIVE TSSOP PW82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358PWRE4ACTIVE TSSOP PW82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLM358PWRG4ACTIVE TSSOP PW82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /doc/da778fb869dc5022aaea0090.html /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps usedbetween the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it isprovided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF LM258A,LM2904:Automotive:LM2904-Q1Enhanced Product:LM258A-EPNOTE:Qualified Version Definitions:Automotive-Q100devices qualified for high-reliability automotive applications targeting zero defectsEnhanced Product-Supports Defense,Aerospace and Medical ApplicationsTAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant LM258ADGKR MSOP DGK 82500330.012.4 5.3 3.3 1.38.012.0Q1LM258ADGKR MSOP DGK 82500330.013.0 5.3 3.4 1.48.012.0Q1LM258ADR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1LM258ADR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1LM258DGKR MSOP DGK 82500330.013.0 5.3 3.4 1.48.012.0Q1LM258DGKR MSOP DGK 82500330.012.4 5.3 3.3 1.38.012.0Q1LM258DR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1LM258DR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1LM2904DGKR MSOP DGK 82500330.012.4 5.3 3.3 1.38.012.0Q1LM2904DGKR MSOP DGK 82500330.013.0 5.3 3.4 1.48.012.0Q1LM2904DR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1LM2904DR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1LM2904PSR SO PS 82000330.016.48.2 6.6 2.512.016.0Q1LM2904PWR TSSOP PW 82000330.012.47.0 3.6 1.68.012.0Q1LM358ADGKR MSOP DGK 82500330.012.4 5.3 3.3 1.38.012.0Q1LM358ADGKR MSOP DGK 82500330.013.0 5.3 3.4 1.48.012.0Q1LM358ADR SOIC D82500330.012.4 6.4 5.2 2.18.012.0Q1LM358ADRSOICD82500330.012.46.45.22.18.012.0Q1Device PackageType PackageDrawingPins SPQ ReelDiameter(mm)ReelWidthW1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W(mm)Pin1QuadrantLM358APWR TSSOP PW82000330.012.47.0 3.6 1.68.012.0Q1LM358DGKR MSOP DGK82500330.012.4 5.3 3.3 1.38.012.0Q1 LM358DGKR MSOP DGK82500330.013.0 5.3 3.4 1.48.012.0Q1 LM358DR SOIC D8*******.012.4 6.4 5.2 2.18.012.0Q1 LM358DR SOIC D8*******.012.4 6.4 5.2 2.18.012.0Q1 LM358PSR SO PS82000330.016.48.2 6.6 2.512.016.0Q1 LM358PWR TSSOP PW82000330.012.47.0 3.6 1.68.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) LM258ADGKR MSOP DGK82500370.0355.055.0LM258ADGKR MSOP DGK82500358.0335.035.0LM258ADR SOIC D8*******.0346.029.0LM258ADR SOIC D8*******.5338.120.6LM258DGKR MSOP DGK82500358.0335.035.0LM258DGKR MSOP DGK82500370.0355.055.0LM258DR SOIC D8*******.0346.029.0LM258DR SOIC D8*******.5338.120.6LM2904DGKR MSOP DGK82500370.0355.055.0LM2904DGKR MSOP DGK82500358.0335.035.0Device Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) LM2904DR SOIC D8*******.5338.120.6LM2904DR SOIC D8*******.0346.029.0LM2904PSR SO PS82000346.0346.033.0LM2904PWR TSSOP PW82000346.0346.029.0LM358ADGKR MSOP DGK82500370.0355.055.0LM358ADGKR MSOP DGK82500358.0335.035.0LM358ADR SOIC D8*******.0346.029.0LM358ADR SOIC D8*******.5338.120.6LM358APWR TSSOP PW82000346.0346.029.0 LM358DGKR MSOP DGK82500370.0355.055.0 LM358DGKR MSOP DGK82500358.0335.035.0 LM358DR SOIC D8*******.5338.120.6LM358DR SOIC D8*******.0346.029.0LM358PSR SO PS82000346.0346.033.0LM358PWR TSSOP PW82000346.0346.029.0。

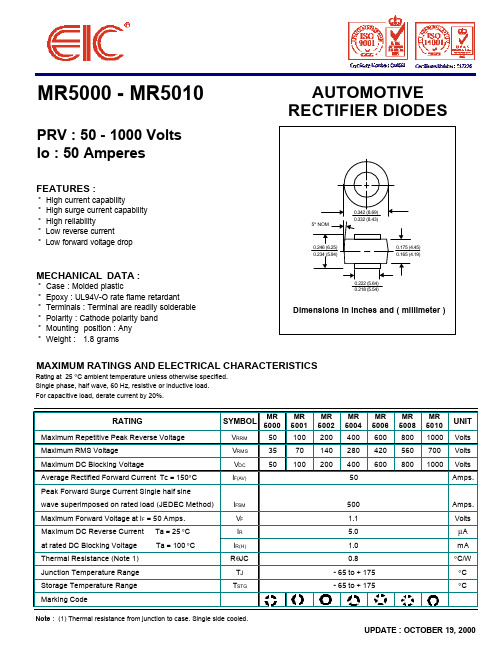

MR5001资料

UPDATE : OCTOBER 19, 2000

元器件交易网

RATING AND CHARACTERISTIC CURVES ( MR5000 - MR5010 )

AVERAGE FORWARD OUTPUT CURRENT, AMPERES

FIG.1 - DERATING CURVE FOR OUTPUT RECTIFIED CURRENT PEAK FORWARD SURGE CURRENT, AMPERES

UNIT

Volts Volts Volts Amps.

IFSM VF IR IR(H) RθJC TJ TSTG

500 1.1 5.0 1.0 0.8 - 65 to + 175 - 65 to + 175

Amps. Volts µA mA °C/W °C °C

Note : (1) Thermal resistance from junction to case. Single side cooled.

PERCENT OF RATED REVERSE VOLTAGE, (%)

0.222 (5.64) 0.218 (5.54)

Dimensions in inches and ( millimeter )

MAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICS

Rating at 25 °C ambient temperature unless otherwise specified. Single phase, half wave, 60 Hz, resistive or inductive load. For capacitive load, derate current by 20%.

ZLG500模块简介

ZLG500B 读卡模块简介

1 概述

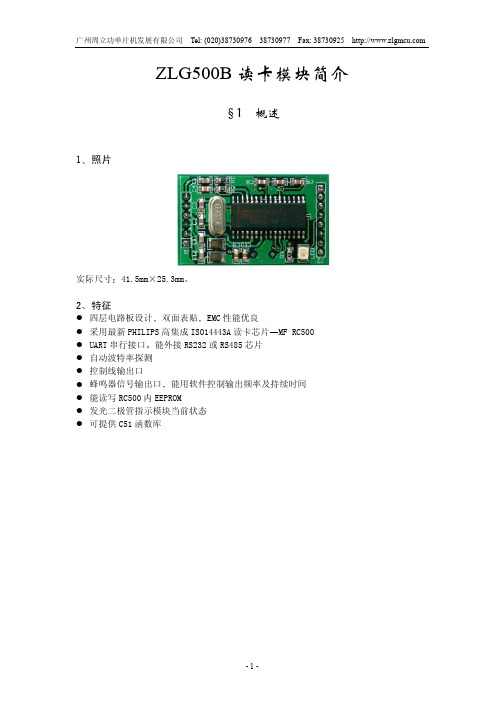

1 照片

实际尺寸 41.5mm 25.3mm

2 特征

z四层电路板设计 双面表贴 EMC 性能优良 z采用最新 PHILIPS 高集成 ISO14443A 读卡芯片 MF RC500 zUART 串行接口 能外接 RS232 或 RS485 芯片 z自动波特率探测 z控制线输出口 z蜂鸣器信号输出口 能用软件控制输出频率及持续时间 z能读写 RC500 内 EEPROM z发光二极管指示模块当前状态 z可提供 C51 函数库

将 ZLG500B.c 及主程序文件 main.c 放于同一项目中 然后在主程序中输入以下代码 #define __SRC #include "main.h" #undef __SRC

#include "zlg500B.h"

sbit zlg500B_RST=P1^4; uchar baud_num; uchar card_snr[4]; uchar code Nkey_a[6] = {0xA0, 0xA1, 0xA2, 0xA3, 0xA4, 0xA5}; uchar code Nkey_b[6] = {0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF};

-2-

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925

3 ZLG500B 读卡模块 MCU 命令 C51 函数

命令 名称 Request

数值 0x41

Anticoll Anticoll2 Select Authentication Authentication2 Halt Read

鼎阳科技射频产品手册说明书