SC8802_EVM_C2_sch

Micrel DSC8002 1.8V至3.3V可编程低功耗CMOS振荡器说明书

1.8 to 3.3VGeneral DescriptionThe DSC8002 is a programmable MEMS based PureSilicon™ O scillator. Using the DragonFly™ or TimeFlash™ handheld programmer, the end user can program the DSC8002 within seconds to any frequency from 1 to 150MHz in increments of 100Hz (up to four decimal point resolution). The nominal operational range spans from 1.8 to 3.3 Volts, without any need for additional external components, providing ease of use and flexibility in multi-voltage applications.The DSC8002 incorporates an all silicon resonator that is extremely robust and nearly immune to stress related fractures, common to crystal based oscillators. Without sacrificing the performance and stability required of today’s systems, a crystal-less design allows for a higher level of reliability, making the DSC8002 ideal for rugged, industrial, and portable applications where stress, shock, and vibration can damage quartz crystal based systems.Available in industry standard packages, the DSC8002 can be “dropped-in” to the same PCB footprint as standard crystal oscillators. Block DiagramFeatures∙Frequency Range: 1 to 150MHz∙Exceptional Stability over Temperature o±25 PPM, ±50 PPM∙Operating voltageo 1.8 to 3.3V (nominal)o 1.65 to 3.60V (absolute max) ∙Operating Temperature Rangeo Industrial -40ºC to 85ºCo Ext. Commercial -20ºC to 70ºCo Commercial 0ºC to 70ºC ∙Low Operating and Standby Currento3mA Operating (40MHz)o1uA Standby∙Ultra Miniature Footprinto 2.5 x 2.0 x 0.85 mmo 3.2 x 2.5 x 0.85 mmo 5.0 x 3.2 x 0.85 mmo7.0 x 5.0 x 0.85 mm∙Excellent shock and VibrationResistance∙Lead Free, RoHS & Reach SVHCCompliant∙Handheld programmer available for purchaseBenefits∙Pin for pin “d rop in” replacement for industry standard oscillators∙Semiconductor level reliability,significantly higher than quartz ∙Frequency Resolution to 4 decimals∙Fully Programmable Operating Voltage and Frequency∙Longer Battery Life / Reduced Power∙Compact Plastic package∙Cost EffectiveApplications∙Mobile Applications∙Consumer Electronics∙Portable Electronics∙CCD Clock for VTR Cameras∙Low Profile Applications∙Industrial1.8 to 3.3V1Ordering CodeSpecifications1. Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not beoperated beyond these limits.2. Output frequency to within 100ppm of final stable output frequency.3. See typical cycle to cycle jitter graph for frequency dependence.* See Ordering Information for detailsNominal Performance Characteristics 1.8V Characteristics3.3V CharacteristicsOutput WaveformStandby FunctionTest CircuitV DD15pF*V SD 50% OutputStandby#Board Layout (recommended)Solder Reflow ProfilePackage DimensionsT e m p e r a t u r e (°C )200°217°150°25°260°3.2 x 2.5 mm Plastic Package2.5 x 2.0 mm Plastic PackageOrdering InformationDSC8002 PTS – TDisclaimer:Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel’s terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. MICREL, Inc. ● 2180 Fortune Drive, San Jose, California 95131 ● USAPhone: +1 (408) 944-0800 ● Fax: +1 (408) 474-1000 ● Email:******************● 。

超米特电子有限公司产品说明书

1US Headquarters TEL +(1) 781-935-4850FAX +(1) 781-933-4318 • Europe TEL +(44) 1628 404000FAX +(44) 1628 404090Asia Pacific TEL +(852) 2 428 8008FAX +(852) 2 423 8253South America TEL +(55) 11 3917 1099FAX +(55) 11 3917 0817Superior elongation and tensilestrength help to prevent tearing in use due to mishandling. Typical properties for CHO-SEAL 1310 and 1273 materi-al are shown on pages 33 and 32respectively.High Shielding PerformanceCHO-SEAL 1310 material provides more than 80 dB of shielding effectiv-ness from 100 MHz to 10 GHz, while CHO-SEAL 1273 material provides more than 100 dB.Low Volume ResistivityBoth materials have exceptionally low volume resistivity, which makes them well suited for grounding appli-cations in which a flexible electrical contact is needed.Low Compression GasketSpacer gaskets are typicallydesigned to function under low deflec-tion forces. Chomerics uses design tools such as Finite Element Analysis (FEA) to accurately predict compres-sion-deflection behavior of various cross section options. Refer to page16.LCP Plastic SpacerLiquid crystal polymer (LCP)spacers, including those made with Vectra A130 material, provide aCHO-SEAL ®1310 or 1273Conductive ElastomersWith EMI spacer gaskets, shielding and grounding are provided by Chomerics’CHO-SEAL 1310 and 1273 conductive elastomers, specifi-cally formulated for custom shape molded parts. They provide excellent shielding and isolation against electro-magnetic interference (EMI), or act as a low impedance ground path between PCB traces and shielding media. Physically tough, these elas-tomers minimize the risk of gasket damage, in contrast to thin-walled extrusions or unsupported molded gaskets.Silicone-based CHO-SEAL 1310and 1273 materials offer excellent resistance to compression set over a wide temperature range, resulting in years of continuous service. CHO-SEAL 1310 material is filled with silver-plated-glass particles, while 1273 utilizes silver-plated-copper filler to provide higher levels of EMI shielding effectiveness.EMI Spacer GasketsThe unique design of Chomerics’EMI spacer gaskets features a thin plastic retainer frame onto which a conductive elastomer is molded. The elastomer can be located inside or outside the retainer frame, as well as on its top and bottom surface. EMI spacer gaskets provide a newapproach to designing EMI gaskets into handheld electronics such as dig-ital cellular phones. Board-to-board spacing is custom designed to fit broad application needs. Customized cross sections and spacer shapes allow for very low closure forcerequirements and a perfect fit in any design or device.Robotic InstallationSpacer gaskets can be installed quickly by robotic application. Integral locater pins in the plastic spacer help ensure accuratepositioning in both manual and pick-and-place assembly. Benefits include faster assembly and lower labor costs.The integrated conductive elastomer/plastic spacer gasket is a low cost,easily installed system for providing EMI shielding and grounding in small electronic enclosures.Figure 1Single Piece EMI Gasket/Locator PinsCHO-SEAL 1310 or 1273 Conductive Elastomer (Inside)Plastic Spacer Around Outsideor InsideApplications for EMI Spacer GasketsThe spacer gasket concept is especially suited to digital and dual board telephone handsets or other handheld electronic devices. It provides a low impedance path between peripheral ground traces on printed circuit boards and components such as:•the conductive coating on a plastic housing•another printed circuit board •the keypad assemblyTypical applications for EMI spacer gaskets include:•Digital cellular, handyphone and personal communications services (PCS) handsets •PCMCIA cards•Global Positioning Systems (GPS)•Radio receivers•Other handheld electronics, e.g.,personal digital assistants (PDAs)•Replacements for metal EMI shield-ing “fences” on printedcircuit boards in wireless tele-communications devicesstable platform for direct, highprecision molding of conductive elas-tomers. The Vectra A130 material described in Table 1 has excellent heat deflection temperature character-istics (489°F, 254°C). For weight con-siderations, the LCP has aspecific gravity of only 1.61. This plas-tic is also 100% recyclable.Typical EMI Spacer Gasket Design ParametersThe EMI spacer gasket concept can be considered using the design parameters shown in Table 2. Some typical spacer gasket profiles are shown below.Figure 2Typical Spacer Gasket Profiles3US Headquarters TEL +(1) 781-935-4850FAX +(1) 781-933-4318 • Europe TEL +(44) 1628 404000FAX +(44) 1628 404090Asia Pacific TEL +(852) 2 428 8008FAX +(852) 2 423 8253South America TEL +(55) 11 3917 1099FAX +(55) 11 3917 0817Finite Element AnalysisChomerics, a division of the Parker Hannifin Corporation’s Seal Group, is the headquarters of Parker Seal’s Elastomer Simulation Group. This unit specializes in elastomer finite element analysis (FEA) using MARC K6 series software as a foundation for FEA capability.Benefits of FEA include:•Quickly optimizing elastomer gasket designs•Allowing accurate predictions of alternate elastomer design concepts •Eliminating extensive trial and error prototype evaluationTypical use of FEA in EMI spacer gasket designs is to evaluate the force vs. deflection requirements of alternate designs.For example, onespacer design features a continuous bead of con-ductive elastomer molded onto a plastic spacer. An alternative designemploys an “interrupted bead,” where the interrup-tions (gaps left on the plastic frame) are sized to maintain the requiredlevel of EMI shielding. Figure 4illustrates these alternative designs.Gasket DeflectionFigure 5 compares the effect of continuous and interrupted elastomer gasket designs in terms of the force required to deflect the conductive elastomer. This actual cellular handset application required a spacer gasket with interrupted bead to meet desired deflection forces.Chomerics Designand Application ServicesChomerics will custom design a spacer for your application. Advice,analysis and design assistance will be provided by Chomerics Applications and Design engineers at no additional fee. Contact Chomerics directlyat the locations listed at the bottom of the page.Figure 3FEA Example of an EMISpacer Gasket Cross SectionFigure 4Continuous (top) and InterruptedElastomer GasketsFigure 5Typical Spacer Gasket Deflection。

微斯米微波式芯片公司2014年产品说明书

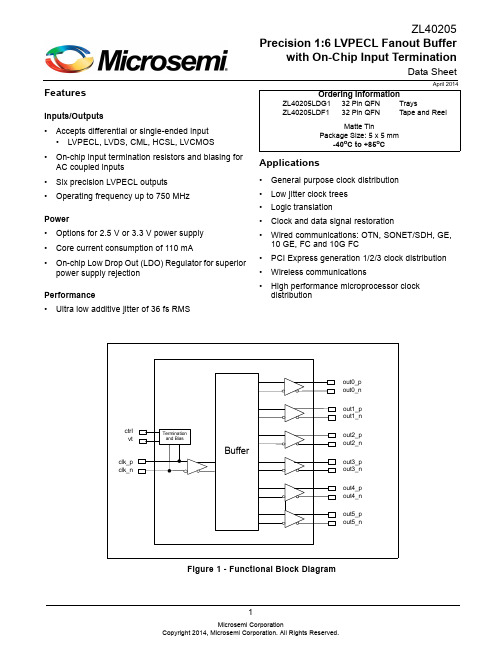

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •On-chip input termination resistors and biasing for AC coupled inputs•Six precision LVPECL outputs •Operating frequency up to 750 MHzPower •Options for 2.5 V or 3.3 V power supply •Core current consumption of 110 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply rejectionPerformance •Ultra low additive jitter of 36 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE,10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40205Precision 1:6 LVPECL Fanout Bufferwith On-Chip Input TerminationData SheetOrdering InformationZL40205LDG1 32 Pin QFN TraysZL40205LDF132 Pin QFNTape and ReelMatte TinPackage Size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217.0 Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - Simplified Diagram of Input Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4 - Clock Input - LVPECL - DC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5 - Clock Input - LVPECL - AC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6 - Clock Input - LVDS - DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7 - Clock Input - LVDS - AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 8 - Clock Input - CML- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 9 - Clock Input - HCSL- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 10 - Clock Input - AC-coupled Single-Ended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 11 - Clock Input - DC-coupled 3.3V CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 12 - Simplified Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 13 - LVPECL Basic Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 14 - LVPECL Parallel Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 16 - LVPECL AC Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 17 - LVPECL AC Output Termination for CML Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 19 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 21 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Change SummaryPage Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.8Figure 4 and Figure 5Removed 22 ohm series resistors from Figure 4 and 5. These resistor are not required; however there is no impact to performance if the resistors are included.16Power supply filtering 18Figure 20Clarification of V ID and V OD .Below are the changes from the February 2013 issue to the April 2014 issue:Page Item Change8Figure 4Changed text to indicate the circuit is not recommended for VDD_driver=2.5V.Below are the changes from the November 2012 issue to the February 2013 issue:Corrected typo of 0.3 Ohm to 0.15 Ohm.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0 Pin DescriptionPin # Name Description3, 6clk_p, clk_n,Differential Input (Analog Input). Differential (or single ended) input signals.For all input configurations see “Clock Inputs” on page 728, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.1, 8vdd_core Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.2, 7,20, 21gnd Ground. 0 V.4vt On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohmtermination resistors.The use of this pin is detailed in section 3.1, “Clock Inputs“, for various input signal types.5ctrl Digital Control for On-Chip Input Termination (Input). Selects differential input mode;0: DC coupled LVPECL or LVDS modes1: AC coupled differential modesThis pin are internally pulled down to GND. The use of this pin is detailed in section 3.1,“Clock Inputs“, for various input signal types.10, 11,12, 29,30, 31NC No Connection. Leave unconnected.Exposed Pad Device GND.3.0 Functional DescriptionThe ZL40205 is an LVPECL clock fan out buffer with six output clock drivers capable of operating at frequencies up to 750MHz.The ZL40205 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40205 can accept DC or AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.The ZL40205 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.Receiverclk_n 50clk_pVt 50BiasctrlFigure 3 - Simplified Diagram of Input StageThis following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the Vt and ctrl pins in each case.In the following diagrams where the ctrl pin is logically one and the Vt pin is not connected, the Vt pin can be instead connected to VDD with a capacitor. A capacitor can also help in Figure 4 between Vt and VDD. This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.Figure 4 - Clock Input - LVPECL - DC CoupledFigure 5 - Clock Input - LVPECL - AC CoupledFigure 6 - Clock Input - LVDS - DC CoupledFigure 7 - Clock Input - LVDS - AC CoupledFigure 8 - Clock Input - CML- AC CoupledFigure 9 - Clock Input - HCSL- AC CoupledFigure 10 - Clock Input - AC-coupled Single-EndedFigure 11 - Clock Input - DC-coupled 3.3V CMOS3.2 Clock OutputsLVPECL has a very low output impedance and a differential signal swing between 1V and 1.6 V. A simplified diagram for the output stage is shown in Figure 12.The LVPECL to LVDS output termination is not shown since there is a different device with the same inputs and LVDS outputs.out_pout_nFigure 12 - Simplified Output DriverThe methods to terminate the ZL40205 LVPECL drivers are shown in the following figures.Figure 15 - LVPECL Parallel Thevenin-Equivalent Output TerminationFigure 16 - LVPECL AC Output TerminationFigure 17 - LVPECL AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40205 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40205 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40205 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive random jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 18.Figure 18 - Additive Jitter3.4 Power SupplyThis device operates employing either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40205 is equipped with a low drop out (LDO) regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringJitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 19. •10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating •0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating •Capacitors should be placed next to the connected device power pins •A 0.15 Ohm resistor is recommended3.4.3 PCB layout considerationsThe power nets in Figure 19 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.ZL402051891922320.1 µF 0.1 µFvdd_core10 µF 0.1 µF0.15 Ωvdd0.1 µF 10 µFFigure 19 - Decoupling Connections for Power PinsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5VDD V 4LVPECL output current I out30mA 5Soldering temperature T260 °C 6Storage temperature T ST-55125 °C 7Junction temperature T j125 °C 8Voltage on input pin V input VDD V 9Input capacitance each pin C p500fF 4.0 AC and DC Electrical Characteristics* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVPECL drivers -unloadedI dd_unload110mA Unloaded2Supply current LVPECL drivers - loaded (all outputs are active)I dd_load209mA Including powerto R L = 50DC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes1CMOS control logic high-level inputvoltageV CIH0.7*V DD V2CMOS control logic low-level inputvoltageV CIL0.3*V DD V3CMOS control logic Input leakagecurrentI IL1µA V I = V DD or 0 V4Differential input common modevoltageV CM 1.1 2.0V5Differential input voltage difference V ID0.251V6Differential input resistance V IR80100120ohm* This parameter was measured from 125 MHz to 750 MHz.* This parameter was measured from 125 MHz to 750 MHz.Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions7LVPECL output high voltage V OH V DD -1.40V 8LVPECL output low voltage V OL V DD - 1.62V 9LVPECL output differential voltage*V OD0.50.9VDC Electrical Characteristics - Inputs and Outputs - for 2.5 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes1Differential input common mode voltageV CM 1.1 1.6V 2Differential input voltage difference V ID 0.251V 3Differential input resistance V IR 80100120ohm 4LVPECL output high voltage V OH V DD -1.40V 5LVPECL output low voltage V OL V DD - 1.62V 6LVPECL output differential voltage*V OD0.40.9VDC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units NotesAC Electrical Characteristics* - Inputs and Outputs (see Figure 21) - for 2.5/3.3 V supply.Characteristics Sym.Min.Typ.Max.Units Notes 1Maximum Operating Frequency1/t p750MHz2Input to output clock propagation delay t pd012ns3Output to output skew t out2out50100ps4Part to part output skew t part2part80300ps5Output clock Duty Cycle degradation t PWH/ t PWL-202Percent6LVPECL Output clock slew rate r SL0.75 1.2V/ns* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWL t pdt PWHOutputFigure 21 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1392212.512 kHz - 20 MHz 1093311.0412 kHz - 20 MHz 85442512 kHz - 20 MHz 57550012 kHz - 20 MHz 506622.0812 kHz - 20 MHz 40775012 kHz - 20 MHz36Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1152212.512 kHz - 20 MHz 853311.0412 kHz - 20 MHz 72442512 kHz - 20 MHz 55550012 kHz - 20 MHz 486622.0812 kHz - 20 MHz 41775012 kHz - 20 MHz395.0 Performance Characterization*The values in this table were taken with an approximate slew rate of 0.8 V/ns.*The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter from a Power Supply Tone*Carrier frequencyParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 115fs RMS 750MHz25 mV at 100 kHz59fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 2.5 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Phase Noise at 622.08 MHzTypical Waveformat 155.52 MHzV OD versus FrequencyPropagation Delay versus TemperatureNote:This is for a single device. For more details see thePower Supply Tone Frequency (at 25 mV) versus PSRR at 125 MHz Power Supply Tone Frequency (at 25 mV) versus Additive Jitter at 125 MHzPower Supply Tone Magnitude (at 100 kHz) versus PSRR at 125 MHz Power Supply Tone Magnitude (at 100 kHz) versus Additive Jitter at 125 MHz7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

EDACS

Operator’s ManualEDACS® ALLEGRAVEHICLE HANDSFREE ericssonz2NOTICE!This manual covers Ericsson and General Electric products manufactured and sold byThis manual is published by Ericsson Inc., without any warranty. Improvements and changes to this manual necessitated by typographical errors, inaccu-racies of current information, or improvements to programs and/or equipment, may be made by Er-icsson Inc., at any time and without notice. Such changes will be incorporated into new editions of this manual. No part of this manual may be reproduced or transmitted in any form or by any means, elec-tronic or mechanical, including photocopying and recording, for any purpose, without the express writ-ten permission of Ericsson Inc.Copyright © February 1995, Ericsson Inc.VEHICLE HANDSFREE PACKAGEThe VEHICLE HANDSFREE Package lets you talk on a portable radio in your car without taking your hands off the wheel. Your radio operates as usual, except that you use an external microphone, speaker, and antenna.The HANDSFREE powers the radio and charges its battery (standard or slim-line only).USING YOUR HANDSFREE UNIT INSERTING THE RADIOBefore inserting the radio remove the following:• the round rubber plug in the antenna port on the back of the radio.• the system connector plug from the bottom of the radio.3INSERT THE RADIO INTO THE HANDSFREE HOLDER1. Slide the radio straight down parallel tothe back of the holder.2. Push the radio all the way down tomake sure the system connector is properly seated.3. Push the radio back until the side tabsof the handsfree unit lock into place.4OPERATING INSTRUCTIONS Service Available IndicatorThe indicator light on the top edge of the radio shows a steady green light when service is available from the service net-work.Answering A CallRefer to your radio user’s guide to se-lect an answering option. Most radios have at least three options:• answer with the SEND key• answer with any key except VOL-UME keys• answer automatically after a num-ber of rings Adjusting The Speaker VolumeWhen the radio is in the cradle and turned on, you can adjust the speaker vol-ume using the volume keys. The radio stores two volume settings independently--one for when the radio is used as a port-able, and one for the speaker volume when the radio is in the HANDSFREE unit. Both settings remain unchanged after the radio is turned off.CHARGING YOUR RADIO BATTERYWhen your radio is on and in standby mode in the HANDSFREE unit, the radio battery is automatically charged. You can charge your radio battery by leaving the phone in the cradle overnight. However, continuously charging the battery in this5way for more than a week can temporarily weaken the vehicle battery.• When your radio is in the HANDSFREE unit, the radio dis-play will indicate charge status. Theindicator alternates between C for“Charging” and the charge level (0through 9). When the battery isfully charged, the display shows an“F” for “Full Charge.”• The HANDSFREE unit recharges a standard battery in less than twohours and a similar battery in lessthan an hour.NOTE: Charging pauses when acall is in progress, but a tricklecharge maintains the batterycharge level.• To use your radio in the HANDSFREE unit if the radio bat-tery is completely discharged (i.e., the radio will not turn on), place the radio in the unit and wait 10 min-utes before placing a call.6REMOVING THE RADIO1. To release the radio from theHANDSFREE unit, squeeze the tabson both sides of the holder until theradio tilts slightly forward.2. Slide the radio straight up out of theholder so that the HANDSFREE sys-tem connector detaches from the baseof the phone.7CARE AND MAINTENANCE• Carefully follow the instructions on Inserting and Removing the radiofrom the HANDSFREE unit.• Do not attempt to service the HANDSFREE unit or componentsyourself. Doing so will void the war-ranty.• Follow all safety precautions and user guidelines8TROUBLESHOOTINGRADIO PROBLEM PROBABLE CAUSE REMEDYThe LED does not light when the vehicle power is supplied.The holder is not receivingpower, or vehicle power polar-ity is reversed.Check the power connec-tions and fuse. Be sure theradio battery is charged.The portable radio functions outside the holder, but not in the holder.Radio is not properly seated inthe holder, or the system con-nector contacts are dirty, or theexternal antenna is discon-nected or defective.Be sure the radio is properlyseated in the holder. If sys-tem connector contacts aredirty, carefully clean them.The other party of the radio connection cannot hear sound.The microphone jack is not in-serted into the connection box.Clean the microphone plugand insert it into the connec-tion box.No audio The speaker jack is notinserted into the connectionbox.Clean the speaker plug and insert it into the connection box.9NOTES 101112Ericsson Inc.Private Radio SystemsMountain View RoadLynchburg, Virginia 24502AE/LZT 123 1873 R1A 1-800-528-7711 (Outside USA, 804-528-7711)Printed in U.S.A.。

EM88F752N

Hoffman Enclosures Inc. 电子变压器操作适配器(适用于Eaton Cutle

89115496

© 2018 Hoffman Enclosures Inc.

PH 763 422 2211 • /HOFFMAN

-3-

For Floor-Mounted, Two-Door Enclosures with Disconnect on Right Flange

0DVWHU 'RRU

)RURQHWKURXJKVL[GRRUIUHHVWDQGLQJHQFORVXUHV ZLWKWKHGLVFRQQHFWWKHWKHULJKWIODQJH 0DVWHU 'RRU

)RUIORRUPRXQWHGHQFORVXUHVZLWK WKHGLVFRQQHFWRQWKHFHQWHUSRVW

Step 5 Attach the bottom of the slide arm (item 4) to the offset arm of the lock release mechanism. Use two flat washers (item 8), two lockwashers (item 9), and two hex nuts (item 10). Do not tighten until parts are adjusted (see step 6B)

Item No. Description

Part No.

Qty.

1

MOUNTING PLATE, C-H C361 AND C371

26385001

1

2

GASKET, PLATE

89109613

1

3

SCREW, 1/4-20X1/2 PAN HEAD

99401031

4

4

VAR-SOM-MX8M-PLUS based on NXP i.MX 8M Plus Evalua

VAR-SOM-MX8M-PLUS based on NXP i.MX 8M PlusEvaluation Kit Quick Start GuideFeatures:1. Power ON Switch (SW7)2. 12V DC In Jack (J24)3. USB Debug (J29)4. micro SD Card slot (J28)5. USB 3.0 OTG (J26)6. USB 2.0 Host (J23)7. Gigabit Ethernet #0 (J21) 8. Gigabit Ethernet #1 (J20)9. MIPI-CSI #1 Camera connector [optional] (J19) 10. Miscellaneous Header #1 (J17)11. HDMI/ MIPI-CSI #2 Camera connector[optional] (J13)12. Mini PCI Express Connector (J15) 13. Miscellaneous Header #2 (J3) 14. SOM Connector (J1) 15. LVDS#B Header (J5)16. LVDS#A/ DSI Header (J7) 17. Fan Power Connector (J9) 18. Digital Microphone (U1) 19. Resistive Touch (J10) 20. Capacitive Touch (J11)21. User Buttons (SW1, SW2, SW4) 22. Line-In Connector (J12)23. Headphones Connector (J14) 24. Boot Select Switch (SW3)25. SAI/I2C/SPI/CAN Header (J16) 26. Reset Button (SW5)27. PWR Select Switch (SW6) 28. UART/PWM Header (J18) 29. RTC Battery Holder (JBT1)Evaluation kit initial Setup1. Carefully remove the 7” LCD and Symphony-Board from the package.2. Connect the 7” LCD Display and Touch cablesto the Evaluation Kit connectors J7, J11 respectively.Note:connect the display cable with the red wire on pin 1. Connect the touch cable with the metal contacts facing down.3. Plug the USB type A to micro B cable betweenthe USB debug connector (J29) and a PC USB port.4. For heatsink assembly instructions, pleasefollow the VHP-VS8M documentation .Please note that the heatsink is mainly used for CPU/GPU intensive applications and may be required per your specific use case.P/N VSS0177AVAR-SOM-MX8M-PLUS based on NXP i.MX 8M PlusEvaluation Kit Quick Start GuideSetting the host PC for debug1. Download any PC terminal software (e.g. Putty ).2. Set the PC terminal software parameters as follows:- Baud Rate: 115200 - Data bits: 8 - Stop bits: 1 - Parity: None- Flow Control: NoneBooting from eMMC1. Set Boot select switch (SW3) to “Internal” position to boot from the VAR-SOM-MX8M-PLUS internal storage.2. Plug the wall adapter into the 12V power jack (J24) and to a 120VAC~240VAC power source.3. Set Power ON switch (SW7) to ON state.4. Boot messages are printed within the PC terminal window.Booting from a micro SD cardThe microSD card is supplied within the package. Updated SD card images can also be downloaded from the Variscite FTP server.See more details in the recovery SD card section in the Variscite Wiki pages.1. Set Power ON switch (SW7) to off state.2. Set Boot select switch (SW3) to “SD ” positionin order to boot from SD Card.3. Push microSD card into the microSD cardslot (J28) of the Symphony-Board.4. Set Power ON switch (SW7) to ON state.5. Boot messages are print ed within PC’sterminal window.(Re-)Installing the file system to eMMCPlease refer to the recovery SD card section in the Variscite Wiki pages.Linkso Wiki page:https:///index.php?title=VAR-SOM-MX8M-PLUSo VAR-SOM-MX8M-PLUS Evaluation kits:https:///product/evaluation-kits/var-som-mx8m-plus-evaluation-kits/o VAR-SOM-MX8M-PLUS System on Module:https:///product/system-on-module-som/cortex-a53-krait/var-som-mx8m-plus-nxp-i-mx-8m-plus/o Symphony carrier board:https:///product/single-board-computers/symphony-board/o Customer portal:https:///loginThank you for purchasing Variscite’s product.For additional assistance please contact: *******************。

KCD2-STC-Ex1.ES 智能传输器电源供应器说明书

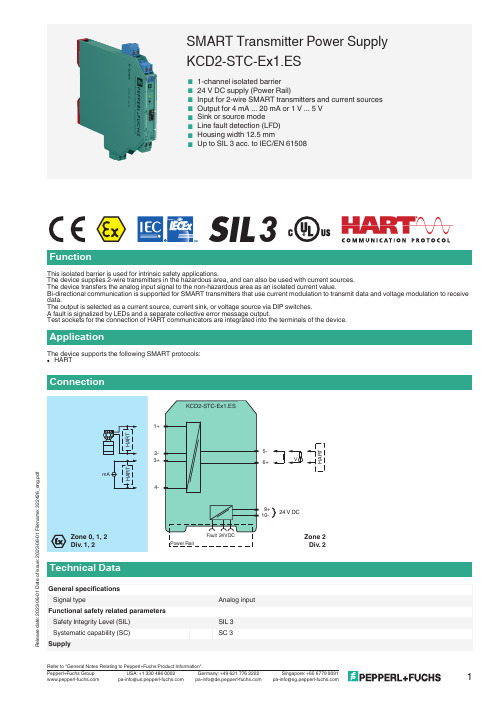

SMART Transmitter Power SupplyKCD2-STC-Ex1.ES<1-channel isolated barrier<24 V DC supply (Power Rail)<Input for 2-wire SMART transmitters and current sources<Output for 4 mA ... 20 mA or 1 V ... 5 V<Sink or source mode<Line fault detection (LFD)<Housing width 12.5 mm<Up to SIL 3 acc. to IEC/EN 61508This isolated barrier is used for intrinsic safety applications.The device supplies 2-wire transmitters in the hazardous area, and can also be used with current sources.The device transfers the analog input signal to the non-hazardous area as an isolated current value.Bi-directional communication is supported for SMART transmitters that use current modulation to transmit data and voltage modulation to receive data.The output is selected as a current source, current sink, or voltage source via DIP switches.A fault is signalized by LEDs and a separate collective error message output.Test sockets for the connection of HART communicators are integrated into the terminals of the device.ApplicationThe device supports the following SMART protocols:l HARTConnection5-6+1+2-3+4-Zone 2Div. 224 V DC9+10-Technical Dataedate:223-6-1Dateofissue:223-6-1Filename:322426_eng.pdfe d a t e : 2023-06-01 D a t e of i s s u e : 2023-06-01 F i l e n a m e : 322426_e ng .p d fe d a t e : 2023-06-01 D a t e of i s s u e : 2023-06-01 F i l e n a m e : 322426_e ng .p d fAccessoriese d a t e : 2023-06-01 D a t e of i s s u e : 2023-06-01 F i l e n a m e : 322426_e ng .p d fKC-ST-5BUTerminal block for KC modules, 2-pin screw terminal, bluee d a t e : 2023-06-01 D a t e of i s s u e : 2023-06-01 F i l e n a m e : 322426_e ng .p d fe d a t e : 2023-06-01 D a t e of i s s u e : 2023-06-01 F i l e n a m e : 322426_e ng .p d fKCD2-STC-Ex1.ESSMART Transmitter Power Supply Factory setting: current source output 4 ... 20 mATransfer characteristicOutput switch settingsMode of operationS1S2S3S4Current source output 4 ... 20 mA II II I II Voltage source output 1 ... 5 V II II I I Current sink output 4 ... 20 mAIIIIIII。

赛米控丹佛斯电子 SEMiX202GB066HDs 数据表

SEMiX ®2sTrench IGBT ModulesSEMiX202GB066HDsFeatures•Homogeneous Si•Trench = Trenchgate technology •V CE(sat) with positive temperature coefficient•UL recognised file no. E63532Typical Applications*•Matrix Converter •Resonant Inverter•Current Source InverterRemarks•Case temperature limited to T C =125°C max.•Product reliability results are valid for T j =150°C•For short circuit: Soft R Goff recommended•Take care of over-voltage caused by stray inductanceAbsolute Maximum Ratings SymbolConditions Values UnitIGBT V CES T j =25°C 600V I C T j =175°CT c =25°C 274A T c =80°C207A I Cnom 200A I CRMI CRM = 2xI Cnom 400A V GES -20 (20)V t psc V CC =360V V GE ≤ 15V V CES ≤ 600VT j =150°C6µs T j-40...175°C Inverse diode I F T j =175°CT c =25°C 291A T c =80°C 214A I Fnom200A I FRM I FRM = 2xI Fnom400A I FSM t p =10ms, sin 180°, T j =25°C1000A T j -40 (175)°C Module I t(RMS)T terminal =80°C600A T stg -40...125°C V isolAC sinus 50Hz, t =1min4000VCharacteristics SymbolConditions min.typ.max.UnitIGBT V CE(sat)I C =200A V GE =15V chiplevelT j =25°C 1.45 1.85V T j =150°C 1.7 2.1V V CE0T j =25°C 0.91V T j =150°C0.850.9V r CE V GE =15VT j =25°C 2.8 4.3m ΩT j =150°C4.3 6.0m ΩV GE(th)V GE =V CE , I C =3.2mA 55.86.5V I CES V GE =0V V CE =600V T j =25°C 0.150.45mA T j =150°C mA C ies V CE =25V V GE =0Vf =1MHz 12.3nF C oes f =1MHz 0.77nF C res f =1MHz0.37nF Q G V GE =- 8 V...+ 15 V 1600nC R Gint T j =25°C 1.00Ωt d(on)V CC =300V I C =200A V GE =±15V R G on =4.2ΩR G off =4.2ΩT j =150°C 65ns t r T j =150°C 80ns E on T j =150°C 6mJ t d(off)T j =150°C 545ns t f T j =150°C 95ns E off T j =150°C8mJ R th(j-c)per IGBT 0.21K/WCharacteristics SymbolConditionsmin.typ.max.UnitInverse diodeV F = V EC I F =200AV GE =0V chipT j =25°C 1.4 1.60V T j =150°C 1.4 1.6V V F0T j =25°C 0.91 1.1V T j =150°C0.750.850.95V r FT j =25°C 1.5 2.0 2.5m ΩT j =150°C2.32.83.3m ΩI RRM I F =200A di/dt off =3900A/µs V GE =-8VV CC =300VT j =150°C 205A Q rr T j=150°C28µC E rr T j =150°C 6.5mJR th(j-c)per diode0.27K/WModule L CE 18nH R CC'+EE'res., terminal-chip T C =25°C 0.7m ΩT C =125°C1m ΩR th(c-s)per module 0.045K/W M s to heat sink (M5)35Nm M tto terminals (M6)2.55Nm Nmw250gTemperatur Sensor R 100T c =100°C (R 25=5 k Ω)493 ± 5%ΩB 100/125R (T)=R 100exp[B 100/125(1/T-1/T 100)]; T[K];3550 ±2%K SEMiX ® 2sTrench IGBT ModulesSEMiX202GB066HDsFeatures•Homogeneous Si•Trench = Trenchgate technology •V CE(sat) with positive temperature coefficient•UL recognised file no. E63532Typical Applications*•Matrix Converter •Resonant Inverter•Current Source InverterRemarks•Case temperature limited to T C =125°C max.•Product reliability results are valid for T j =150°C•For short circuit: Soft R Goff recommended•Take care of over-voltage caused by stray inductanceFig. 1: Typ. output characteristic, inclusive R CC'+ EE'Fig. 2: Rated current vs. temperature I C = f (T C )Fig. 3: Typ. turn-on /-off energy = f (I C )Fig. 4: Typ. turn-on /-off energy = f (R G )Fig. 5: Typ. transfer characteristic Fig. 6: Typ. gate charge characteristicFig. 7: Typ. switching times vs. I C Fig. 8: Typ. switching times vs. gate resistor R GFig. 9: Typ. transient thermal impedance Fig. 10: Typ. CAL diode forward charact., incl. R CC'+EE'Fig. 11: Typ. CAL diode peak reverse recovery current Fig. 12: Typ. CAL diode recovery chargeThis is an electrostatic discharge sensitive device (ESDS), international standard IEC 60747-1, Chapter IX* The specifications of our components may not be considered as an assurance of component characteristics. Components have to be tested for the respective application. Adjustments may be necessary. The use of SEMIKRON products in life support appliances and systems is subject to prior specification and written approval by SEMIKRON. We therefore strongly recommend prior consultation of our staff.。

2V68-S用户指南说明书

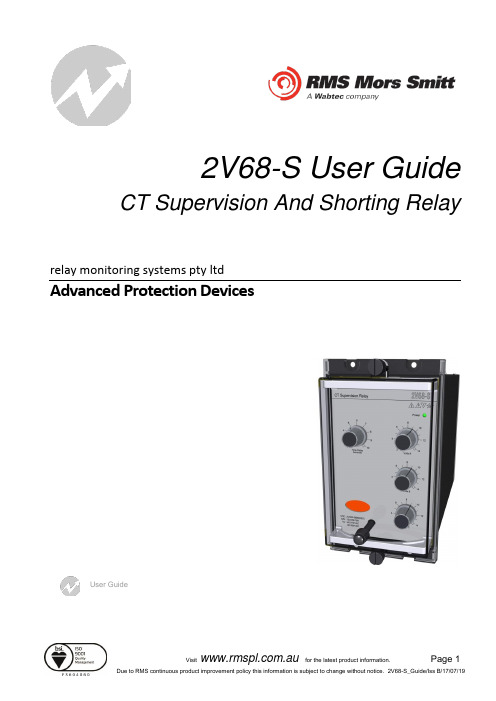

2V68-S User Guide CT Supervision And Shorting Relayrelay monitoring systems pty ltdAdvanced Protection DevicesUser Guide2V68-SUser GuideAbout This ManualThis User Guide covers all 2V68-S relays manufactured from July 2019. Earlier relays do not necessarily incorporate all the features described. Our policy of continuous development means thatextra features & functionality may have been added.The 2V68-S User Guide is designed as a generic document to describe the common operating parameters for all relays built on this platform. Some relay applications are described but for specific model information the individual “K” number Product / Test manuals should be consulted.The copyright and other intellectual property rights in this document, and in any model or article produced from it (and including any Registered or unregistered design rights) are the property of Relay Monitoring Systems Pty Ltd. No part of this document shall be reproduced or modified or stored in another form, in any data retrieval system, without the permission of Relay Monitoring Systems Pty Ltd, nor shall any model or article be reproduced from this document without consent from Relay Monitoring Systems Pty Ltd.While the information and guidance given in this document is believed to be correct, no liability shall be accepted for any loss or damage caused by any error or omission, whether such error or omission is the result of negligence or any other cause. Any and all such liability is disclaimed.Contact UsRelay Monitoring Systems Pty Ltd 2006-20136 Anzed Court • Mulgrave 3170 • AUSTRALIAPhone 61 3 8544 1200 • Fax 61 3 8544 1201Email ********************• Web .auHow this Guide is Organised This guide is divided into five parts: Part 1 OverviewPart 2 DocumentationPart 3 ApplicationPart 1Part2 DocumentationTechnical BulletinThe detailed technical attributes, functional description & performance specifications for the 2V68-S are described in the product Technical Bulletin. For the most up to date version go to:.auThe order of precedence for product information is as follows:•Technical Bulletin•User GuideUser GuideThis User Guide covers all 2V68-S relay versions & describes the generic features & attributes common across all versions.Different relay versions are required to cater for varying customer requirements such as auxiliary voltage range, I/O configuration, case style, relay functionality etc.The product ordering code described in the Technical Bulletin is used to generate a unique version of the relay specification & is called a Type Number. This code takes the form 2V68-SKxx where the Kxx is the “K” or version number.Part3 ApplicationIntroduction (6)General Safety Precautions Working With Current Transformer Circuits (6)Application (6)Relay Operator Interface (6)Voltage Setting Dials (6)Optional Time Delay Setting Dial (6)Power Indication (6)Flag Indicator (7)Flag Reset (7)Scheme Wiring (8)Terminal Layout and Relay Dimensions (8)2V68-S Connection diagram (9)Relay Settings (10)Setting Assumptions (10)Voltage Setting Criteria (11)Sample Setting Calculation Method 1 (12)Sample Setting Calculation Method 2 (13)Application Of External Resistors For Elevated Voltage Settings (14)Sample Setting Calculation For Elevated Voltage Settings (15)Commissioning (16)Commissioning Preliminaries (16)Site Commissioning Verification Checklist (16)System Power Up (16)Voltage Setting Check (17)IntroductionGeneral Safety Precautions Working With Current Transformer CircuitsThe secondary circuit of a live CT must not be open circuited.Non-observance of this precaution can result in injury to personnel or damage to equipment. ApplicationThe 2V68 is a three phase monitoring device designed to provide continuous supervision of the CT summation circuit in high impedance type protection schemes. The relay will detect open circuited CT wiring as well as open circuited main current transformers.The relay provides three (3) latching N/O alarm output contacts to signal faults. Three (3) additional N/O latching output contacts are provided for an integral summation circuit CT shorting facility.The 2V68 type relays have a setting range of 2-14V adjusted on a per phase basis from calibrated potentiometers at the front panel. The relay is continuously rated at 300V RMS & no external components are required.An optional harmonic filter is available to reject 2nd, 3rd, 4th and 5th harmonics to reduce the effect of switching transients.The AC input voltage is continuously monitored and when it exceeds the pre-set level, latching contacts are actuated after a three (3) second time delay. An optional adjustable time delay setting version is also available.Relay Operator InterfaceVoltage Setting DialsThe adjustable voltage setting for each phase is set via front panel rotary dials. The setting range is from 2 – 14 Vac.Optional Time Delay Setting DialThe 2V68-S comes standard with a fixed 3 sec operate time delay. The optional adjustable time delay model provides a time delay setting dial that may be set from 3 – 20 sec.Power IndicationThe green power LED indicates the presence of an auxiliary supply to the relay.Flag IndicatorA hand reset mechanical flag is provided to indicate operation of the relay and a potential open circuitin the CT summation.Flag ResetHand reset push button for the latched output contacts and the mechanical flag.Power Indication OptionalTime Delay Setting DialPhase SegregatedVoltage SettingDialsOperate FlagFlag Reset2V68-S Front FasciaScheme WiringTerminal Layout and Relay DimensionsAll dimensions are in mm.The module may be either flush panel mounted or alternatively mounted on a 4U high 19 inch rack frame.The relay terminal numbers are as viewed from the rear of the relay. M4 screw terminals are provided for relay wiring.2V68-S Connection diagram2V68-SThe connection diagram shows typical relay connections of the relay supervision inputs to a CT summation circuit :Terminals 7-9 : R phaseTerminals 11-13 : W phaseTerminals 15-17 : B phaseAlso shown are connections of the CT shorting contacts of the 2V68-S to the CT summation circuit, shorting is provided to the CT summation neutral point :Terminals 16-14 : R phaseTerminals 12-10 : W phaseTerminals 8-6 : B phaseRelay SettingsSetting AssumptionsThe 2V68-S is a voltage detection relay used to monitor the shunt voltage across the stabilising resistor in series with a current operated High Impedance relay. The equivalent circuit presented to the CT summation circuit is shown below (one phase shown only for clarity).Given that Z 2V68 >> (R Stab + Z High Impedance Relay ), the equivalent circuit then simplifies to :In the event of a CT secondary becoming open-circuit or the CT wiring being broken, a resultant current spill will flow into the stabilising resistor and the high impedance relay. The current spill will develop a voltage across the stabilising resistance and the high impedance relay.It should be noted that the supervision principle requires some load current to be flowing for a spill current to be developed on the occurrence of an open circuit. Inevitably there will besituations where, for part of the time, particularly under light loading conditions the supervision relay would not operate on the occurrence of an open circuit in the secondary circuit due to there being insufficient spill current developed.To CT Summation CircuitZ High Impedance relayR StabZ 2V68To CT Summation CircuitZ High Impedance relayR StabA variable load profile would however cause the eventual operation of the CT supervision relay as the spill current increased.Given the low incidence of open circuits in CT secondary wiring coupled with the coincident low probability of a busbar fault, the abovementioned limitation of the CT supervision scheme is generally accepted.Voltage Setting CriteriaTypically in a high impedance scheme R Stab >> Z High Impedance Relay , a good approximation of the equivalent circuit is :Therefore the developed voltage across the 2V68 relay will be R Stab x I spillThe voltage setting on the 2V68 is made as sensitive as possible subject to the following criteria :V set > 2 x R Stab x I spill due to CT error at Full Load (Criteria 1) &V set < 0.5 x R Stab x I set (where I set is the High Impedance relay current setting) (Criteria 2)Without information on the amount of spill current due to CT error at Full Load the following voltage setting may be trialled :V set = 0.1 x R Stab x I set (where I set is the High Impedance relay current setting) (Equation 1)With this setting, on site adjustment may be required if the supervision scheme operates due to load only.To CT Summation CircuitR StabSample Setting Calculation Method 1The following sample setting calculation is based on the following High Impedance Protection Settings :R Stab = 200 ΩI set = 400 mAI spill due to CT error at Full Load = 5 mATo satisfy Criteria 1V set > 2 x R Stab x I spill due to CT error at Full LoadV set > 2 x 200 Ω x 5 mAV set > 2 VTo satisfy Criteria 2V set < 0.5 x R Stab x I setV set < 0.5 x 200 Ω x 400 mAV set < 40 VWe can chooseV set = 2 V which satisfies both Criteria 1 and Criteria 2.The standard time delay of 3 sec will be suitable for most circumstances.Where a longer time delay is called for the adjustable time delay option may be specified to allow a time delay setting range of 3 – 20 sec.Sample Setting Calculation Method 2Without information on the CT error at Full Load and based on the above High Impedance Protection Settings we can use Criteria 3 to determine our voltage setting :R Stab = 200 ΩI set = 400 mAAccording to Criteria 3V set = 0.1 x R Stab x I setV set = 0.1 x 200 Ω x 400 mAV set = 8 VThe standard time delay of 3 sec will be suitable for most circumstances.Where a longer time delay is called for the adjustable time delay option may be specified to allow a time delay setting range of 3 – 20 sec.Application Of External Resistors For Elevated Voltage SettingsWhere the required voltage setting needs to be greater than 14V an external resistor in series with the 2V68 relay may be applied.By using a voltage divider calculation at a given relay setting voltage and the required applied voltage for operation, a suitable series resistor value can be determined.The equivalent circuit would be :The following derivation would then yield :V appliedR series −R relay =V relay R relayR series =(V appliedV relay−1)×R relayR series =(V appliedV relay−1)×30kΩfor 2 Volt ≤V relay ≤14 Volt (Equation 2)Note that the effective applied voltage for the relay to operate would be subject to the tolerances of the chosen series resistor and the relay input impedance, so at best say +/- 10%.The relay must be capable of sustaining the temporary shunt voltage during a fault condition and the continuous shunt voltage at the chosen relay setting. In practice the power dissipation is low due to the overall shunt impedance and usually results in a power dissipation of < 20 W.R seriesR relayV relayV appliedSample Setting Calculation For Elevated Voltage SettingsAssume that the calculated operate voltage needs to be :40 VWith the relay set at say 14VUsing equation 2R series =(V appliedV relay − 1) ×30kΩR series =(40 V14 V− 1) ×30kΩR series =56 kΩ , 20 W power rating.CommissioningCommissioning PreliminariesCarefully examine the module to ensure that no damage has occurred during transit. Check that the model number and rating information are correct.InsulationThe relay, and its associated wiring, may be insulation tested between:- all electrically isolated circuits- all circuits and earthAn electronic or brushless insulation tester should be used, having a dc voltage not exceeding 1000V. Accessible terminals of the same circuit should first be strapped together. Deliberate circuit earthing links, removed for the tests, subsequently must be replaced.Site Commissioning Verification ChecklistObserve all site specific standard safety procedures.System Power UpItem Description Complete1 Confirm all necessary primary equipment isolations2 Confirm all necessary secondary equipment isolations3 Check panel installation of the 2V68-S monitor4 Check for correct case earthing5 Check the 2V68-S is wired to the protection design schematic6 Confirm Fail alarm relay is closed (Terminals 25 and 27)7 Apply correct Auxiliary voltage to power up the 2V68-S8 Observe that the green power LED remains illuminated solid9 Confirm Fail alarm relay is open (Terminals 25 and 27)Voltage Setting CheckItem Description Complete 1 Apply an AC test voltage to inputs 7 and 9 (R phase voltagesensing input) that is greater than the setting applied to the frontdial2 Confirm operation of the relay after the nominal3 sec delay oras per the optional time delay setting3 Confirm Relay flag has dropped, Alarm outputs 1 – 3 haveoperated and the CT shorting contacts for R, W and B phasehave all operated4 Remove the AC test voltage and confirm that the Relay flagremains in the operated position, the Alarm output contacts 1 –3 are latched and the CT shorting contacts for R, W and Bphase are latched5 Depress the Relay reset push button and confirm that Alarm andCT shorting contacts reset to the open position and the operateflag is reset6 Repeat items 1 through 5 with the test voltage instead applied toinputs 11 and 13 (B phase voltage sensing input) in place of Rphase7 Repeat items 1 through 5 with the test voltage instead applied toinputs 15 and 17 (C phase voltage sensing input) in place of Rphase。

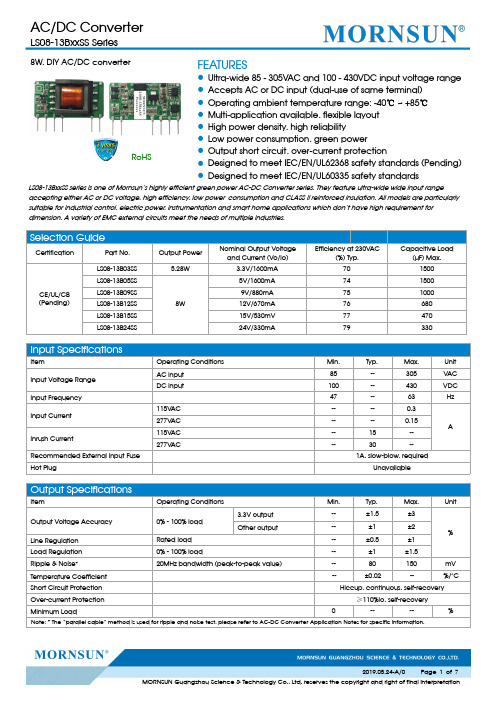

MORNSUN LS08-13BxxSS系列AC DC电源说明书

8W,DIY AC/DC converterRoHSFEATURES●Ultra-wide 85-305VAC and 100-430VDC input voltage range ●Accepts AC or DC input (dual-use of same terminal)●Operating ambient temperature range:-40℃~+85℃●Multi-application available,flexible layout ●High power density,high reliability●Low power consumption,green power●Output short circuit,over-current protection●Designed to meet IEC/EN/UL62368safety standards (Pending)●Designed to meet IEC/EN/UL60335safety standardsLS08-13BxxSS series is one of Mornsun’s highly efficient green power AC-DC Converter series.They feature ultra-wide wide input rangeaccepting either AC or DC voltage,high efficiency,low power consumption and CLASS II reinforced insulation.All models are particularly suitable for industrial control,electric power,instrumentation and smart home applications which don’t have high requirement for dimension.A variety of EMC external circuits meet the needs of multiple industries.Input SpecificationsItemOperating Conditions Min.Typ.Max.Unit Input Voltage Range AC input 85--305V AC DC input100--430VDC Input Frequency 47--63HzInput Current 115V AC ----0.3A 277V AC ----0.15Inrush Current115V AC --15--277V AC--30--Recommended External Input Fuse 1A,slow-blow,requiredHot PlugUnavailableOutput SpecificationsItemOperating Conditions Min.Typ.Max.UnitOutput Voltage Accuracy 0%-100%load 3.3V output --±1.5±3%Other output--±1±2Line Regulation Rated load --±0.5±1Load Regulation 0%-100%load--±1±1.5Ripple &Noise *20MHz bandwidth (peak-to-peak value)--80150mV Temperature Coefficient --±0.02--%/°C Short Circuit Protection Hiccup,continuous,self-recoveryOver-current Protection ≥110%Io,self-recoveryMinimum Load----%Note:*The “parallel cable”method is used for ripple and noise test,please refer to AC-DC Converter Application Notes for specific information.Selection GuideCertificationPart No.Output PowerNominal Output Voltage and Current (Vo/Io)Efficiency at 230V AC(%)Typ.Capacitive Load(µF)Max.CE/UL/CB (Pending)LS08-13B03SS 5.28W3.3V/1600mA 701500LS08-13B05SS8W 5V/1600mA 741500LS08-13B09SS 9V/880mA 751000LS08-13B12SS 12V/670mA 76680LS08-13B15SS 15V/530mV 77470LS08-13B24SS24V/330mA79330General SpecificationsItem Operating Conditions Min.Typ.Max.UnitIsolation Test Input-output Electric Strength Test for1min.,(leakage current<5mA)3000----VACOperating Temperature-40--+85℃Storage Temperature-40--+105Storage Humidity----95%RHPower Derating -40℃~-25℃ 2.67----%/℃+55℃~+85℃ 2.5----85V AC-100VAC1----277V AC-305V AC0.54----Safety Standard IEC/EN/UL62368,IEC/EN/UL60335 Safety Certification IEC/EN/UL62368(Pending) Safety CLASS CLASS IIMTBF MIL-HDBK-217F@25°C>300,000h Mechanical SpecificationsCase Material44.50x24.00x15.00mmWeight11g(Typ.)Cooling method Free air convectionElectromagnetic Compatibility(EMC)Emissions CECISPR32/EN55032CLASS A(Recommended circuit1,4)CISPR32/EN55032CLASS B(Recommended circuit2,3) RECISPR32/EN55032CLASS A(Recommended circuit1,4)CISPR32/EN55032CLASS B(Recommended circuit2,3)Immunity ESD IEC/EN61000-4-2Contact±6KV Perf.Criteria B RS IEC/EN61000-4-310V/m perf.Criteria AEFTIEC/EN61000-4-4±2KV(Recommended circuit1,2)perf.Criteria BIEC/EN61000-4-4±4KV(Recommended circuit3,4)perf.Criteria B SurgeIEC/EN61000-4-5line to line±1KV(Recommended circuit1,2)perf.Criteria BIEC/EN61000-4-5line to line±2KV(Recommended circuit3,4)IEC/EN61000-4-5line to line±4KV(Recommended circuit4)perf.Criteria B CS IEC/EN61000-4-610Vr.m.s perf.Criteria A Voltage dips,shortinterruptions and voltagevariations immunityIEC/EN61000-4-110%,70%perf.Criteria BProduct Characteristic CurveNote:①With an AC input between85-100VAC/277-305VAC and a DC input between100-120VDC/390-430VDC,the output power must be derated as per temperature derating curves;②This product is suitable for applications using natural air cooling;for applications in closed environment please consult factory or one of our FAE.Additional Circuits Design ReferenceLS series additional circuits design referenceLS08series additional components selection guidePart No.FUSE(required)C1required)C2(required)L1(required)C3(required )C4CY1(required )LS08-13B03SS 1A/300V22µF/450V470µF/16V(solid-state capacitor) 4.7µH 150µF/35V 0.1µF/50V1.0nF/400V ACLS08-13B05SS LS08-13B09SS 220µF/16V(solid-state capacitor)100µF/35V LS08-13B12SS LS08-13B15SS 470uF/35V 47µF/35VLS08-13B24SS220uF/35VNote:1.C1:input capacitors,C2:output storage capacitors,they must be connected externally.2.We recommend using an electrolytic capacitor with high frequency and low ESR rating for C3(refer to manufacture’s datasheet).Combined with C2,L1,they form a pi-type filter circuit.Choose a capacitor voltage rating with at least 20%margin,in other words not exceeding 80%.C4is a ceramic capacitor,used for filtering high frequency noise.A suppressor diode (TVS)is a recommended to protect the application in case of a converter failure and specification should be 1.2times of the output voltage.Immunity design circuits for referenceEmissions design circuits for referenceCLASS ⅢCLASS ⅣCLASS ACLASS BEnvironmental Application EMC SolutionLS series environmental application EMC solution selection tableRecommendedcircuit Application environmental Typical industryInput voltagerangeEnvironment temperature Emissions Immunity 1Basic applicationNone85~305V AC -40℃~+85℃CLASS A CLASS Ⅲ2Indoor civil environment Smart home/Home appliances(2Y)-25℃~+55℃CLASS BCLASS ⅢIndoor general environment Intelligent building/Intelligentagriculture 3Indoor industrial environment Manufacturing workshop -25℃~+55℃CLASS B CLASS Ⅳ4Outdoor general environmentITS/Video monitoring/Charging point/Communication/Securityand protection-40℃~+85℃CLASS ACLASS ⅣOutdoor harsh environmentOn-line power meter Communication base station-40℃~+85℃CLASS A>CLASS ⅣSurge:line to ground ±4KV EFT:CLASS ⅣElectromagnetic Compatibility Solution--Recommended Circuit1.Recommended circuit 1——Basic applicationrecommended circuit 1Application environmentalAmbient temperature rangeImmunity CLASSEmissions CLASSBasic application-40℃~+85℃CLASS ⅢCLASS AComponentRecommended valueR112Ω/3W LDM4.7mH2.Recommended circuit 2——Indoor civil /Universal system recommended circuits for general environmentRecommended circuit 2Application environmentalAmbient temperature rangeImmunity CLASSEmissions CLASS Indoor civil /general -25℃~+55℃CLASS ⅢCLASS BComponentRecommended valueR112Ω/3W CY1(CY2) 1.0nF/400V ACLCM 3.5mH LDM 0.33mH CX0.1µF/310VAC FUSE (required)1A/300V ,slow-blowNote:In the home appliance application environment,the two Y capacitors of the primary and secondary need to be externally connected (CY1/CY2,value at 2.2nF/400VAC),which can meet the EN60335certification.In other industries,only one Y capacitor is needed.3.Recommended circuit 3——Universal system recommended circuits for indoor industrial environmentRecommended circuit 3Application environmental Ambienttemperature rangeImmunity CLASSEmissions CLASSIndoor industrial-25℃~+55℃CLASS ⅣCLASS BComponentRecommended valueMOV S14K350C1450V/22uF CY1 2.2nF/400V AC CX 0.1µF/310V ACLCM 3.5mH LDM 0.33mH R112Ω/3WFUSE (required)2A/300V ,slow-blow4.Recommended circuit 4——Universal system recommended circuits for outdoor general/harsh environmentRecommended circuit 4Application environmental Ambienttemperature rangeImmunity CLASSEmissions CLASSOutdoor general environment-40℃~+85℃CLASS ⅣCLASS AComponentRecommended valueMOV S14K350C1450V/22uF LDM 4.7mH R112Ω/3WFUSE (required)2A/300V ,slow-blowApplication environmental Ambient temperaturerangeImmunity CLASS EmissionsCLASSOutdoor harsh environment -40℃~+85℃>CLASSⅣSurge:line to ground±4KVEFT:CLASSⅣCLASS AComponent Recommended valueMOV S20K350C1450V/33uF(Surge protection priority)LDM 4.7mHR133Ω/5WFUSE(required) 6.3A/300V,slow-blow5.For additional information please refer to application notes on . LS08-13BxxSS Dimensions and Recommended LayoutNote:1.For additional information on Product Packaging please refer to .Packaging bag number:58220032;2.External electrolytic capacitors are required to modules,more details refer to typical applications;3.This part is open frame,at least6.4mm safety distance between the primary and secondary external components of the module isneeded to meet the safety requirement;4.Unless otherwise specified,parameters in this datasheet were measured under the conditions of Ta=25℃,humidity<75%,nominal inputvoltage(115V and230V)and rated output load;5.In order to improve the efficiency at light load,there will be audible noise generated,but it does not affect product performance andreliability;6.Module required dispensing fixed after assembled;7.All index testing methods in this datasheet are based on our company corporate standards;8.We can provide product customization service,please contact our technicians directly for specific information;9.Products are related to laws and regulations:see"Features"and"EMC";10.Our products shall be classified according to ISO14001and related environmental laws and regulations,and shall be handled byqualified units.Mornsun Guangzhou Science&Technology Co.,Ltd.Address:No.5,Kehui St.1,Kehui Development Center,Science Ave.,Guangzhou Science City,Huangpu District,Guangzhou,P.R.China Tel:86-20-38601850Fax:86-20-38601272E-mail:***************。

北京时代民芯科技有限公司 CLGA封装芯片测试夹具说明书

(19)国家知识产权局(12)实用新型专利(10)授权公告号 (45)授权公告日 (21)申请号 202122081758.0(22)申请日 2021.08.31(73)专利权人 北京时代民芯科技有限公司地址 100076 北京市丰台区东高地四营门北路2号专利权人 北京微电子技术研究所(72)发明人 李明远 闫静 姜扬 刘利新 常国义 闫兰丰 黄玉凤 吕学明 (74)专利代理机构 中国航天科技专利中心11009专利代理师 范晓毅(51)Int.Cl.G01R 1/04(2006.01)G01R 31/28(2006.01)(54)实用新型名称一种针对CLGA封装芯片的测试夹具(57)摘要本实用新型提供一种针对CLGA封装芯片的测试夹具,将夹具中传统的单一尺寸导向框改进为包括最大外形导向框和可拆装导向块的导向框组件,最大外形导向框中设有大于等于待测芯片最大外形尺寸上限的内腔,可拆装导向块安装于最大外形导向框,调整内腔的尺寸与待测芯片最大外形尺寸相匹配,实现待测芯片在所述内腔中的定位,进而利用导向框组件,测试座,探针和手测盖之间的配合,实现对待测芯片的测试。

本实用新型解决了陶瓷平面网格阵列封装器件公差较大、器件在测试夹具内定位不精准的问题,可以快速组装不同定位腔尺寸的导向框,不需要通过新制或者返修原有导向框的方法来兼容陶瓷封装器件的最大外形公差,节约了重新制作导向框的成本。

权利要求书2页 说明书4页 附图3页CN 216525901 U 2022.05.13C N 216525901U1.一种针对CLGA封装芯片的测试夹具,包括测试座(1),探针(2)和手测盖(4),其特征在于,还包括导向框组件(3);导向框组件(3)包括最大外形导向框(31)和可拆装导向块(32);所述最大外形导向框(31)设有顶部开口的内腔(311),所述内腔(311)的尺寸大于等于待测芯片最大外形的尺寸上限;待测芯片置于所述内腔(311)中,可拆装导向块(32)固定安装于最大外形导向框(31)上,实现待测芯片在所述内腔(311)中的定位;导向框组件(3)固定安装于测试座(1)上,手测盖(4)设于导向框组件(3)上方,用于测试时向待测芯片施加压力;测试座(1)和导向框组件(3)上分别设有第一针孔和第二针孔,探针(2)通过第一针孔固定安装于测试座(1)上,待测芯片受到所述压力时,探针(2)穿过第二针孔与待测芯片焊盘接触,实现对待测芯片的测试。

该版权及产品最终解释权归广州金升阳科技有限公司所有

③ 整机效率 VS 输出负载

URB2405LD-20W

效率% 90 80 70 60 50 40 30 20 10 0 10 20 30 40 50 60 70 80 90 100 输出负载%Io

该版权及产品最终解释权归广州金升阳科技有限公司所有

产品规格更新时恕不另行通知

URB_LD-20W

A/0-2009

1000 --100 --

标称、满载

产品选型

MTBF 重量 冷却方式 外壳材料

万小时 克

URB2405LD-20W

额定输出功率 封装形式 ห้องสมุดไป่ตู้出电压 输入电压 产品系列

自然空冷 铜镀镍(六面)

输入特性

项目 测试条件 标称输入 欠压保护

(24V) Min. Typ. ----Pi -10 -ms Max. 9.0 -17.8 -VDC

Vin

C in

Vout

DC

DC

C o ut

GND

0V

(图 1)

若要进一步减小输出纹波,可将输出外 接电容 Cout 加大或使用 ESR 小的电容,但容 值不能大于该产品的最大容性负载。 ② 推荐电容取值

全电压输入 全电压输入

3.3V 输出 5V 输出 12V 输出 15V 输出

打嗝式, 可持续,自恢复

100

③ 该系列产品不能并联使用, 不支持热插拔

Trim 的使用以及 Trim 电阻的计算

Trim 的使用电路(虚线框为产品内部)

+Vo +Vo

工作温度曲线和效率曲线

① 典型温度曲线 (输出电压≤5V)

R1 Vref R2 R3 Trim Vref RT R2 R1 R3 Trim

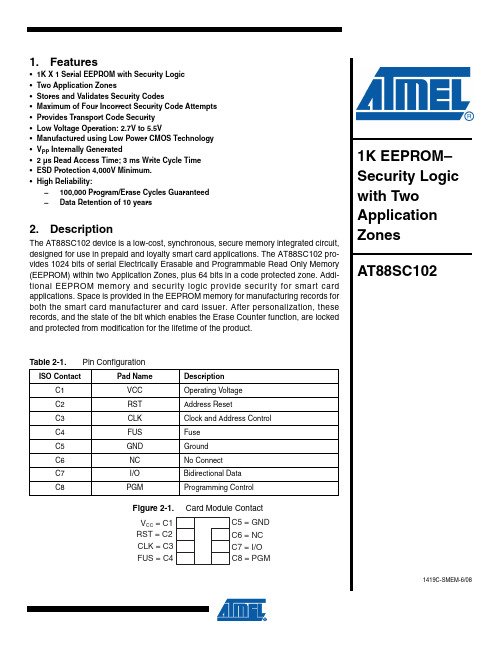

AT88SC102-09AT-xx资料