GS8662D09GE-333I中文资料

KSZ8851-16MLL DEMO BOARD 48-PIN ETHERNET CONTROLLE

SD13

SD7 40

CPU_D14 3

6

SD14

SD8 39

CPU_D15 4

5

SD15

SD9 36

SD10 35

33

SD11 34

CPU_CMD

33

SD12 33

R10

SD13 32

CPU_CSN

33

SD14 31

R12

SD15 30

CPU_WRN

33

CMD

11

R14

CPU_RDN

33

CSN

12

R16

5 6 7 8

TANT

C27

R28 10uF

470pF 2.49K

Power 3.3V 0.1uF (red LED)

CSN CMD

4.7K R27 4.7K R29

GBLC03C_0 D3

GND 2 GND

VR 5 3.3VA

INTRN 4.7K R30

VOUT = 1.24 X [ 1 + ( 2.49k/ 1.5K ) ]

5

4

3

KSZ8851-16MLL (48-pin) Demo Board Black Diagram

D

Headers 20x2

RJ45

LAN1 T

KSZ8851-16MLL

Reset

Power

+1.8V

+2.5V

+3.3V

STATUS LEDs

OSC

EEPROM

C

MIC5209YM

25 MHz

AT93C46

x2

2

1

DATE:

GSxxxxA系列交流伺服驱动器操作手册

外形尺寸及重量

驱动器型号 GS0020A/ GS0040A /GS0075A/GS0100A

GS0150A/GS0210A

外形尺寸图 (mm) 图1

图2

重量 (Kg) 1.5

2.8

产 品 概 要

图 1:GS0020A/ GS0040A /GS0075A/GS0100A

版权申明

北京和利时电机技术有限公司保留所有权力

产品使用说明书内容参照了相关法律基准和行业基准。您在使用我们的产品时,如对本说 明书提供的内容有疑问,请向购买产品的销售人员、或向本公司邮箱、客户服务热线咨询。

北京和利时电机技术有限公司(以下简称和利时电机)保留在不事先通知的情况下,修改 本手册中的产品和产品规格参数等文件的权力。

产品特性 型号命名 产品组成 产品概要

GS 系列伺服驱动器以美国 TI 公司最新的数字处理芯片(DSP)作为核心控制芯片,采 用了先进的全数字电机控制算法,完全以软件方式实现了电流环、速度环、位置环的闭环 伺服控制,具备良好的鲁棒性和自适应能力,可配合多种规格的伺服电机,适应于需要快 速响应的精密转速控制与定位控制的应用系统,如:数控机床、印刷机械、包装机械、造 纸机械、塑料机械、纺织机械、工业机器人、自动化生产线等。

试运行和操作

通电前注意事项 ……………………………………………………………… 24 操作和显示 …………………………………………………………………… 24 通电试运行 …………………………………………………………………… 29 参数汇总和说明 ……………………………………………………………… 33

运行和调整

产品特性

DSP 全数字控制方式,可以实现多种电机控制算法,软件更新、升级方便; 内置电子齿轮控制功能; 多种控制模式:脉冲(≤500kpps)、模拟电压(±10V)、数字设定、混合模式等; 六种脉冲输入方式,与用户上位机接口方便灵活; 编码器反馈脉冲可分频输出,分频数:1~255; 键盘及 LED 数码管显示; RS232C / RS485 / CANBUS 通讯接口可选,与 PC 机联接,可进行伺服参数的设定与修改; 保护功能:具有过压、泄放回路、过流、过载、堵转、失速、位置超差、编码器信号异常等报警; 内置回馈能量吸收电路,也可外接放电电阻; 提供一路接口电源输出:12V(100mA)。 通过 CE 认证。

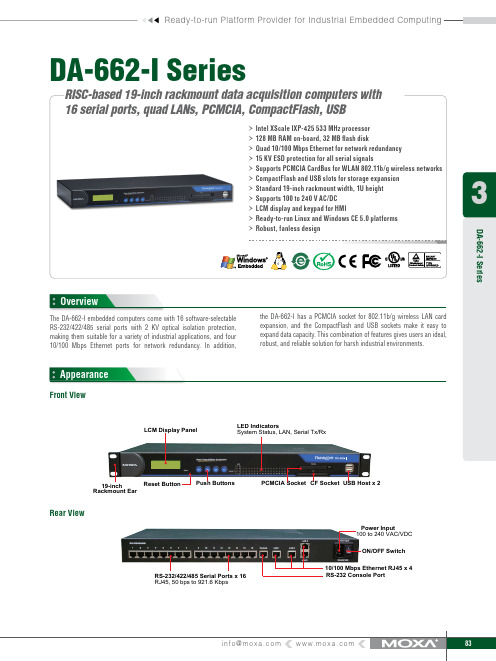

DA-662A系列硬件用户手册说明书

DA-662A Series Hardware User’s ManualEdition 2.0, September 2018/product© 2018 Moxa Inc. All rights reserved.DA-662A Series Hardware User’s Manual The software described in this manual is furnished under a license agreement and may be used only in accordance withthe terms of that agreement.Copyright Notice© 2018 Moxa Inc. All rights reserved.TrademarksThe MOXA logo is a registered trademark of Moxa Inc.All other trademarks or registered marks in this manual belong to their respective manufacturers.DisclaimerInformation in this document is subject to change without notice and does not represent a commitment on the part of Moxa.Moxa provides this document as is, without warranty of any kind, either expressed or implied, including, but not limited to, its particular purpose. Moxa reserves the right to make improvements and/or changes to this manual, or to the products and/or the programs described in this manual, at any time.Information provided in this manual is intended to be accurate and reliable. However, Moxa assumes no responsibility for its use, or for any infringements on the rights of third parties that may result from its use.This product might include unintentional technical or typographical errors. Changes are periodically made to the information herein to correct such errors, and these changes are incorporated into new editions of the publication.Technical Support Contact Information/supportMoxa AmericasToll-free: 1-888-669-2872 Tel: +1-714-528-6777 Fax: +1-714-528-6778Moxa China (Shanghai office) Toll-free: 800-820-5036Tel: +86-21-5258-9955 Fax: +86-21-5258-5505Moxa EuropeTel: +49-89-3 70 03 99-0 Fax: +49-89-3 70 03 99-99Moxa Asia-PacificTel: +886-2-8919-1230 Fax: +886-2-8919-1231Moxa IndiaTel: +91-80-4172-9088 Fax: +91-80-4132-1045Table of Contents1.Introduction ...................................................................................................................................... 1-1Overview ........................................................................................................................................... 1-2 Package Checklist ............................................................................................................................... 1-2 Product Features ................................................................................................................................ 1-2 Hardware Specifications ...................................................................................................................... 1-3 2.Hardware Introduction...................................................................................................................... 2-1Appearance ........................................................................................................................................ 2-2 DA-662A-8 ................................................................................................................................. 2-2DA-662A-16 ............................................................................................................................... 2-2 Dimensions ........................................................................................................................................ 2-3 Hardware Block Diagram ..................................................................................................................... 2-3 DA-66A-8 ................................................................................................................................... 2-3DA-662A-16 ............................................................................................................................... 2-4 LED Indicators .................................................................................................................................... 2-4 Reset Button ...................................................................................................................................... 2-4 LCD Screen ........................................................................................................................................ 2-5 Push Buttons ...................................................................................................................................... 2-5 Real-time Clock .................................................................................................................................. 2-5 3.Hardware Connection Description ..................................................................................................... 3-1Placement Options .............................................................................................................................. 3-2 Rack Mounting ............................................................................................................................ 3-2 Connecting the Hardware..................................................................................................................... 3-2 Wiring Requirements ................................................................................................................... 3-2Connecting the Power .................................................................................................................. 3-2Connecting to the Network ........................................................................................................... 3-3Connecting to a Serial Device ....................................................................................................... 3-3Configurable Pull High/Low Resistors for the RS-485 Port ................................................................. 3-4Connecting to the Console Port ..................................................................................................... 3-5USB Host.................................................................................................................................... 3-5CompactFlash ............................................................................................................................. 3-51Introduction The DA-662A series embedded computers come with 8 to 16 software selectable RS-232/422/485 serial ports, making them suitable for a variety of industrial applications. Models are available with 4 10/100 Mbps Ethernet ports. The DA-662A series model also comes with CF and USB ports to make it easy to add additional storage space. The computers are designed with a standard 19-inch, rugged 1U rackmount case, and are embedded with a 100-240 VAC power input. This combination of features gives users a robust and reliable ready-to-run solution for applications such as data acquisition and power substations.The following topics are covered in this chapter:❒Overview❒Package Checklist❒Product Features❒Hardware SpecificationsOverviewThe DA-662A series are RISC-based, ready-to-run embedded computers designed for industrial dataacquisition applications. Each model has 8 or 16 RS-232/422/485 serial ports, and 2 USB hosts based on the Moxa Macro 500 MHz communication processor. The DA-662A series has 4 Ethernet ports. The casing is astandard 1U, 19-inch wide rack-mounted rugged enclosure. The robust, rack-mountable mechanism design provides the hardened protection needed for industrial environment applications, and makes it easy for users to install the DA-662A series on a standard 19-inch rack. The DA-662A series are ideal for applications that require a distributed embedded technology, such as SCADA systems, plant floor automation, and powerelectricity monitoring applications.The DA-662A series are suitable for IT control room applications, the critical assets used in the control andautomation system of industrial plant floors, and in electric power utility substations. The DA-662A series can accept a wide range of power inputs (from 100 to 240V), which means that they can be connected to AC power lines. Because of the no hard disk, fan-less, energy efficient design, the DA-662A series minimize heatgeneration, can operate around the clock, year in and year out, in heavy duty, harsh industrial environments, delivering the kind of reliable computing power expected of a multifunctional controller.Choose from models of the DA-662A series that come pre-installed with the open-standard Linux OS. Thebuilt-in SDK makes program development easy by allowing you to follow the common programmingprocedures used on a standard PC. All of the software you develop for your own applications can be stored in the onboard Flash memory. The DA-662A series embedded computers are ideal for creating control systems with distributed architecture that are based on embedded technologies. Typical applications include SCADAsystems, plant floor automation, and power electricity monitoring.Package ChecklistBefore installing the DA-662A series, verify that the package contains the following items:• 1 DA-662A series embedded computer• 6 jumper caps•19-inch Rackmount Kit with 2 L-shaped metal plates and 8 screws•Ethernet Cable: RJ45-to-RJ45 cross-over cable, 100 cm•CBL-RJ45M9-150: RJ45-to-DB9 male serial port cable, 150 cm•CBL-RJ45F9-150: RJ45-to-DB9 female console port cable, 150 cm•Quick installation guide•Documentation and software CD•Warranty cardNOTE: Notify your sales representative if any of the above items are missing or damaged.Product Features•Moxa Macro 500 MHz Processor•On-board 128 MB RAM, 32 MB Flash ROM•8 to 16 RS-232/422/485 serial ports• 4 10/100 Mbps Ethernet•Standard 19-inch rack-mount installation, 1U height•Wide range of power input voltages from 100 to 240VAC•LCD screen and push buttons for Human-Machine Interface (HMI)•Ready-to-run Linux platform•Robust, fanless designHardware SpecificationsComputerCPU: MoxaMacro 500 MHzOS: Embedded Linux (pre-installed)DRAM: 128 MB onboardFlash: 32 MB onboardEthernet InterfaceLAN: 4 auto-sensing 10/100 Mbps ports (RJ45)Magnetic Isolation Protection: 1.5 kV built-inSerial InterfaceSerial Standards: 8 to 16 RS-232/422/485 ports, software selectable (8-pin RJ45)ESD Protection: 8 kV contact, 15 kV Air ESD protection for all signalsSurge Protection: 2 kV line-to-line and 4 kV line-to-ground surge protection, 8/20 μs waveform(DA-662A-I-8/16-LX only)Insulation: 500 V (DA-662A-I-8/16-LX only)Isolation: 2 kV digital isolation (DA-662A-I-8/16-LX only)Termination Resistor: 120 ohm, jumper selectableConsole Port: RS-232 (all signals), RJ45 connectorSerial Communication ParametersData Bits: 5, 6, 7, 8Stop Bits: 1, 1.5, 2Parity: None, Even, Odd, Space, MarkFlow Control: RTS/CTS, XON/XOFF, ADDC® (automatic data direction control) for RS-485Baudrate: 50 bps to 921.6 Kbps (supports non-standard baudrates; see user’s manual for details)Serial SignalsRS-232: TxD, RxD, DTR, DSR, RTS, CTS, DCD, GND(DA-662A-I-8/16-LX only: TxD, RxD, RTS, CTS, GND)RS-422: TxD+, TxD-, RxD+, RxD-, GNDRS-485-4w: TxD+, TxD-, RxD+, RxD-, GNDRS-485-2w: Data+, Data-, GNDLEDsSystem: OS ReadyLAN: 10/100M x 4Serial: TxD, RxD (8 to 16 of each)Mini Screen with Push ButtonsLCD Panel: Liquid Crystal Display on the case, 2 x 16 text modePush Buttons: Four membrane buttons for convenient on-site configurationPhysical CharacteristicsHousing: SECC sheet metal (1 mm)Weight: 4.3 kgDimensions:Without ears: 440 x 45 x 237 mm (17.32 x 1.77 x 9.33 in)With ears: 480 x 45 x 237 mm (18.90 x 1.77 x 9.33 in)Mounting: Standard 19-inch rackmountEnvironmental LimitsOperating Temperature: -10 to 60°C (14 to 140°F)Storage Temperature: -20 to 70°C (-4 to 158°F)Ambient Relative Humidity: 5 to 95% (non-condensing)Anti-Vibration: 1 g @ IEC-68-2-6, sine wave (resonance search), 5-500 Hz, 1 Oct/min, 1 Cycle, 13 mins 17 sec per axisPower RequirementsInput Voltage: 100 to 240 VAC auto ranging(47 to 63 Hz for AC input)Power Consumption: 20 WStandards and CertificationsSafety: UL 60950-1EMC:EN 55022/24CISPR 22, FCC Part 15B Class AIEC 61000-4-2 ESD: Contact 8 kV; Air 15 kVIEC 61000-4-3 RS: 3 V/m (80 MHz to 1 GHz)IEC 61000-4-4 EFT: Power 1 kV; Signal 0.5 kVIEC 61000-4-5 Surge: Power 2 kV; Signal 4 kVIEC 61000-4-6 CS: 3 VIEC 61000-4-8IEC 61000-4-11Green Product: RoHS, CRoHS, WEEEReliabilityAlert Tools: Built-in buzzer and RTC (real-time clock) Automatic Reboot Trigger: Built-in WDT (watchdog timer) MTBF (mean time between failures): 125,733 hrs WarrantyWarranty Period: 5 yearsDetails: See /warranty2Hardware Introduction DA-662A series hardware is compact, well-designed, and built rugged for industrial applications. LED indicators help you monitor the performance and identify trouble spots. Multiple ports allow the connection of different devices for wireless operation. With the reliable and stable hardware platform that is provided, you may devote your attention to the development of your application. In this chapter, learn the basics about the embedded computer hardware and its different parts.The following topics are covered in this chapter:❒AppearanceDA-662A-8DA-662A-16❒Dimensions❒Hardware Block DiagramDA-66A-8DA-662A-16❒LED Indicators❒Reset Button❒LCD Screen❒Push Buttons❒Real-time ClockAppearance DA-662A-8Front ViewRear ViewDA-662A-16Front ViewRear ViewDimensionsHardware Block DiagramThe following block diagrams show the layout of the DA-662A series’ internal components. DA-66A-8DA-662A-16LED IndicatorsLED indicators are located on the front panel of the DA-662A series. LED Name LED Color LED FunctionReady Red Power is On, and system is ready (after booting up) LAN1, LAN2, LAN3, LAN4 Orange10 Mbps Ethernet connection Green 100 Mbps Ethernet connectionP1-P16 (Rx) Orange Serial port is receiving RX data from the serial device Off Serial port is not receiving RX data from the serial device P1-P16 (Tx)Green Serial port is transmitting TX data to the serial device OffSerial port is transmitting TX data to the serial deviceReset ButtonPress the Reset button on the front panel continuously for at least 5 seconds to load the factory default configuration . After the factory default configuration has been loaded, the system will reboot automatically. The Ready LED will blink on and off for the first 5 seconds, and then maintain a steady glow once the system has rebooted.We recommend that you only use this function if the software is not working properly and you want to load factory default settings. To reset an embedded Linux system, always use the software reboot command />reboot to protect the integrity of data being transmitted or processed. The Reset button is not designed to hard reboot the DA-662A series.LCD ScreenThe DA-662A series has an LCD screen on the front panel. The LCD screen can display 16 columns and 2 rows of text. After the DA-662A series boots up, the LCD screen will display the model name and firmware version:D A - 6 6 2 A - 1 6 VER.1.Push ButtonsThere are four push buttons on the DA-662A series’ front panel. The buttons are used to enter text onto the LCD screen. The buttons are MENU, (up cursor),(down cursor), and SEL:Button ActionMENU Displays the main menu.Scrolls up through a list of items shown on the LCD screen’s second line.Scrolls down through a list of items shown on the LCD screen’s second line. SELSelects the option listed on the LCD screen.Real-time ClockThe DA-662A series’ real time clock is powered by a lithium battery. We strongly recommend that you do not replace the lithium battery without help from a qualified Moxa support engineer. If you need to change the battery, contact the Moxa RMA service team.3 Hardware Connection DescriptionThe following topics are covered in this chapter:❒Placement OptionsRack Mounting❒Connecting the HardwareWiring RequirementsConnecting the PowerConnecting to the NetworkConnecting to a Serial DeviceConfigurable Pull High/Low Resistors for the RS-485 PortConnecting to the Console PortUSB HostCompactFlashPlacement OptionsRack MountingThe DA-662A series is designed to be mounted on a standard 19-inch rack. Two L-shaped metal plates areincluded as standard accessories with the DA-662A series. Use the enclosed pair of L-shaped metal plates and screws to fasten your DA-662A series to the rack cabinet. Two placement options are available. You can either lock the front or the rear panel of the DA-662A series to the front of the rack. Each L-shaped plate has 6 holes, leaving two outer or inner holes open for your convenience.Connecting the HardwareThis section describes how to connect the DA-662A series to serial devices. The topics covered in this section are: Wiring Requirements, Connecting the Power, Connecting to the Network, Connecting to aSerial Device, and Connecting to the Console Port.Wiring RequirementsYou should observe the following common wiring rules:•Use separate paths to route wiring for power and devices. If power wiring and device wiring paths must cross, make sure the wires are perpendicular at the intersection point.NOTE: Do not run signal or communication wiring and power wiring in the same wire conduit. To avoidinterference, wires with different signal characteristics should be routed separately.•You can use the type of signal transmitted through a wire to determine which wires should be kept separate.The rule of thumb is that wiring that shares similar electrical characteristics can be bundled together.•Keep input wiring and output wiring separate.•Where necessary, it is strongly advised that you label wiring to all devices in the system. Connecting the PowerTo power on the DA-662A series, use a power cord to connect the power line to the DA-662A series’ AC power connector. The power connector is located on the right side of the rear panel. Next, turn on the power switch.The DA-662A series takes about 30 seconds to boot up. Once the device is ready, the Ready LED on the front panel will light up, and the DA-662A series model name and firmware version will appear on the LCD screen.Connecting to the NetworkFor DA-662A series, connect one end of the Ethernet cable to one of the DA-662A series’ 10/100M Ethernet ports (8-pin RJ45) and the other end of the cable to the Ethernet network. If the cable is properly connected, the DA-662A series will indicate a valid connection to the Ethernet in the following ways:Pin Signal 1 ETx+ 2 ETx- 3 ERx+ 4 – 5 – 6 ERx- 7 – 8–Connecting to a Serial DeviceUse properly wired serial cables to connect the DA-662A series to serial devices. The DA-662A series’ serial ports (P1 to P16) use 8-pin RJ45 connectors. The ports can be configured by software for RS-232, RS-422, or 2-wire RS-485. The pin assignments are shown in the following table:PinRS-232 RS-232(DA-662A-I-8/16-LX only)RS-422RS-4851 DSR – – –2 RTS RTS TXD+ –3 GND GND GND GND4 TXD TXD TXD- –5 RXD RXD RXD+ Data+6 DCD – RXD- Data-7 CTS CTS – – 8DTR–––Configurable Pull High/Low Resistors for the RS-485 PortIn some critical environments, you may need to add termination resistors to prevent the reflection of serialsignals. When using termination resistors, it is important to set the pull high/low resistors correctly so that the electrical signal is not corrupted. The DA-662A series uses jumper settings to set the termination resistors and pull high/low resistor values for each serial port.To configure the termination or pull high/low resistors, you first need to open the DA-662A's chassis. You will see 3 rows of jumper caps (as shown in the accompanying figure). The first row is for setting pull high resistors, the second row is for setting termination resistors, and the third row is for setting pull low resistors.Each serial port has 6 jumper caps for configuring the resistors. The pin assignments are shown in the following table:Jumper settingRS485 Data + RS485 Data -Pull High resistors1-2: 150 kΩ2-3: 1 kΩTermination1-2: Open2-3: 120 ΩPull Low resistors1-2: 150 kΩ2-3: 1 kΩTo set the termination resistors to 120 Ω, make sure that PIN 2 and PIN 3 assigned to the serial port are shorted by jumper caps.To set the pull high/low resistors to 150 kΩ, make sure that PIN 1 and PIN 2 assigned to the serial port are shorted by jumper caps. This is the default setting.To set the pull high/low resistors to 1 kΩ, make sure that PIN 2 and PIN 3 assigned to the serial port are shorted by jumper caps.Connecting to the Console PortThe DA-662A series’ console port is an 8-pin RJ45 RS-232 port. The pin definition is the same as for the serial ports (P1 to P16).USB HostThe DA-662A series offers 2 USB 2.0 hosts, allowing you to connect with a USB storage device. The first USB mass storage device to be connected will be mounted automatically by mount to /mnt/sdc, and the second device will be mounted automatically to /mnt/sdd. The DA-662A series will be un-mounted automatically with the umount command when the device is disconnected.CompactFlashThe DA-662A series have a built-in CompactFlash socket. The CompactFlash socket allows users to addadditional memory by inserting a CompactFlash memory card, without any risk to the computer.Follow the instructions below to insert a CompactFlash card:1.Turn off DA-662A.2.Insert the CompactFlash card into the socket.3.Turn on DA-662A.。

GS8.2E快瘦机产品说明书

GS8.2E Fast Slimm i ng MachineManualCONTENTSParts introduction 1 Annex 1 Basic Operati o n 2 Functions and operation 2 Notice 4 Forbidden group 4 Technical parameters 5 Annex List 5Parts introduction7 8Annex shelf1 2 5 364Obve r seBack910 11 12 13Annex1、M80 ultrasound head jack2、Medium supersonic head jack3、Small supersonic head jack4、Add button 、Decrease bu t ton5、f u nction6、St a rt/pause7、G e neral power switch8、Power supply line9、work t i me10、Continuous Wave 11、Out p ut intensity 12、fu n ction 13、Pulse waveM80 ultrasound headMedium supersonic headSmall supersonic head— 1 —Basic Operation1、P l ace annex well and connect to mainframe.①Insert M80 ult r asound head to [1 ].②Insert medium supersonic he a d to[2].③Insert small supersonic head to [3].2. Connect power line [8],t u rn on General power switch[ 7].3. Press[ 5] fu c tion sele c t bu t ton, move to the right place ,the light will shining, press[4] .Sett i ng funct i on s,work t i me,work mode and output intensity, p ress [8] start working.4. During operation, if you want to change to o t her functions within the sett i ng time, pleasepress [6] first, a nd press [5] to change.5. Turn off the General power switch, unplug the power line when finished. Sterilize the usedWork h e ad.Functions and operationM80 u l trasound h e ad1. Applied gel on fleshy part s(eg.abdomen,hip,t h igh) The amount depends on moving flexibiliof the ultrasoun d head.2.Set work time(10 min every part),Adjust output int e nsity(1 weak~5 strong).3.Click “Start”, put the service brake under your feet, step on to start working, move away for pause4. Beautician hold t h e ultrasound h e ad to move slowly on skin, in circle or beeline repeatly,theother han d push the fat towards t h e ultrasound head.5.Do not use o n back,aviod using on bones.6.Do not use o n uterus part when women do abdomen care. A bdomen treatment duringMenst r uat e shou l d b e avoided.* Enough gel are needed, you may feel painful if medium is not enough.* The total treat m ent time for daily care should be within 30 min.7.The machine will pau s e aut o mat i cally if th e set t ing time is over.8.Clean the lef t overs wit h hot t o wel, use warm towel to clean the ultrasou n d head.—2 —Super s onic func t ionSupersonic has a mechanical,h y perthermia and biochemical effect,make local tissue cells can be micro-massaged,promote blood circulat i o n,sof t en organizat i ons, speed up chemicalreact i ons, and promot e metabolism.It can promote blood circulation and lymph circulation,t h us has the effect of detoxification, wrinkle removal,tightening,lifting, l ightening f l e c ks and eliminating pouch and dark circles.1.To clean deeply, a pply medium(nutrition gel, extract oil a n d etc)The amou n t sh o uld be according to moving f l exibility of ultrasound head.2.Set work time. Press [ 7] to choose medium or small ultrasound head according t o parts need cared.(Medium size head suit fo r face and arms,the small size f o r eye a n d nosewing.3.Set t ing work mod(1-continous wave output ,2-pulse wave),to regulate output int e nsity according to diff e rent parts(1weak~9strong)4.Press start t o work.5.During operation, if you want t o chan g e to ot h er functions within the sett i ng t i me, pleasepress pause and then press [ 7] to move the curso r to the right place,t h en press [4] or [5] to Change,readjust work time,work mode,out p ut intensit y and press start.6.The machine will stop aut o matically if t h e set t ing time if over.e warm water to clean skin.8.St e rilize all the used ultrasound heads.—3 —Notice1. In operation, in o r der t o maint a in sufficient ge l.2.The ultraso u nd head should not stay out of work for to o lo n g time while outpu t ting energy.Click “pause” to stop working to avoid damage.3. M50, M80 ultrasound h e ads should not stay st i ll at one part for t o o long time,and do not use it on bones.4, Please step on service brake the n there will be sound wave exist when using M80 ultrasound head.5, M80 u l t r asound head can not be used on the back, avoid on the bo n es, and daily ca r e should Be within 30 minutes every time.6. Do not use on eyeba l l top , A d am' s apple, h eart .Do not stay st i ll on one part for to o lo n g. Forbidden group1.Peo p le who has fever, inf e ct i ous diseases, acut e diseases.2. People with heart disease or co n figured cardiac p a cemaker.3. Patients with severe high blood pressure, tumor disease, asthma, deep vein thrombosis,Varix, t h yroid ,cancer, falling sickness.4. People with hemorrhagic disease, trauma, vascular rupt u re, skin inflammation, skin disease.5.Pregnant women6. Do not use at the abdomen durin g men s trual period7. Medical P l astic p a rt s, or part s with metal inside8. People with an abnormal immune syst e m—4 —Technical parametersVolt a ge:AC 220V/50Hz or AC 110V/60Hz p o wer:≤75W Operating f r e q uency:1MHz/40KHzAnnex List1.Mainframe 1set2.Power supply line 1pc3. Use manual 1 c opy4. big ultrasound head 1pc5.Medium Ultrasound head (with wire) 1pc6.Small Ult r asound head (with wire) 1pc7.Ann e x shelf 1pc8.Hexa g onal screws 3pc—5 —。

HPMLDL系列服务器

HPMLDL系列服务器hpML系列服务器HP ProLiant ML110G7(C8R00A)参数规格差不多参数产品类型工作组级产品类别塔式产品结构4U处理器CPU类型奔腾双核CPU型号奔腾双核G860CPU频率3GHzHP ProLiant ML330 G6(600911-AA1)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5620CPU频率 2.4GHz智能加速主2.666GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存12MB总线规格QPI 5.86GT/sCPU核心四核HP ProLiant ML330 G6(B9D22A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强5600 CPU型号Xeon E5606CPU频率 2.13GHz标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存8MB总线规格QPI 4.8GT/sHP ProLiant ML330 G6(600911-AA1)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5620CPU频率 2.4GHz智能加速主2.666GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存12MB总线规格QPI 5.86GT/sCPU核心四核HP ProLiant ML350 G6(638180-AA1)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5606CPU频率 2.13GHz标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存8MB总线规格QPI 4.8GT/sCPU核心四核CPU线程四线程数主板HP ProLiant ML350 G6(600431-AA5)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5620CPU频率 2.4GHz智能加速主2.666GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存12MB总线规格QPI 5.86GT/sCPU核心四核CPU线程八线程数HP ProLiant ML350 G6(594869-AA1)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5620CPU频率 2.4GHz智能加速主2.666GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存12MB总线规格QPI 5.86GT/sCPU核心四核CPU线程八线程数HP ProLiant ML310e Gen8(686146-AA5)参数规格差不多参数产品类型企业级产品类别塔式产品结构4U处理器CPU类型Intel 至强E3-1200 v2 CPU型号Xeon E3-1220 v2CPU频率 3.1GHz标配CPU1颗数量最大CPU4颗数量制程工艺22nm三级缓存8MB总线规格DMI 5GT/sHP ProLiant ML310e Gen8(686147-AA5)参数规格差不多参数产品类型企业级产品类别塔式产品结构4U处理器CPU类型Intel 至强E3-1200 v2 CPU型号Xeon E3-1240 v2CPU频率 3.4GHz智能加速主3.8GHz频标配CPU1颗数量最大CPU4颗数量制程工艺22nm三级缓存8MBHP ProLiant ML350e Gen8(C3Q10A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2400 CPU型号Xeon E5-2403CPU频率 1.8GHz标配CPU1颗数量最大CPU4颗数量制程工艺32nm三级缓存10MB总线规格QPI 6.4GT/sHP ProLiant ML350e Gen8(C3Q08A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2400 CPU型号Xeon E5-2407CPU频率 2.2GHz标配CPU1颗数量最大CPU4颗数量制程工艺32nm三级缓存10MB总线规格QPI 6.4GT/sHP ProLiant ML350e Gen8(C3Q09A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2400 CPU型号Xeon E5-2420CPU频率 1.9GHz标配CPU1颗数量最大CPU4颗数量制程工艺32nm三级缓存15MB总线规格QPI 6.4GT/sHP ProLiant ML350e Gen8(C3F91A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2400 CPU型号Xeon E5-2430CPU频率 2.2GHz标配CPU1颗数量最大CPU4颗数量制程工艺32nm三级缓存15MB总线规格QPI 6.4GT/sHP ProLiant ML350p Gen8(646675-AA1)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2600 CPU型号Xeon E5-2609CPU频率 2.4GHz标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存10MB总线规格QPI 6.4GT/sHP ProLiant ML350p Gen8(668271-AA5)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2600 CPU型号Xeon E5-2620CPU频率2GHz智能加速主2.5GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm。

GS882Z36BB-333IT资料

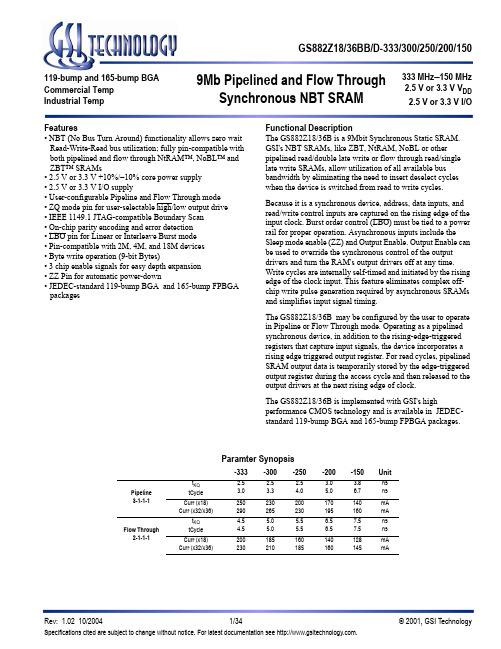

GS882Z18/36BB/D-333/300/250/200/1509Mb Pipelined and Flow ThroughSynchronous NBT SRAM333 MHz –150 MHz 2.5 V or 3.3 V V DD 2.5 V or 3.3 V I/O119-bump and 165-bump BGA Commercial Temp Industrial Temp Features• NBT (No Bus Turn Around) functionality allows zero wait Read-Write-Read bus utilization; fully pin-compatible with both pipelined and flow through NtRAM™, NoBL™ and ZBT™ SRAMs• 2.5 V or 3.3 V +10%/–10% core power supply • 2.5 V or 3.3 V I/O supply• User-configurable Pipeline and Flow Through mode • ZQ mode pin for user-selectable high/low output drive • IEEE 1149.1 JTAG-compatible Boundary Scan • On-chip parity encoding and error detection • LBO pin for Linear or Interleave Burst mode • Pin-compatible with 2M, 4M, and 18M devices • Byte write operation (9-bit Bytes)• 3 chip enable signals for easy depth expansion • ZZ Pin for automatic power-down• JEDEC-standard 119-bump BGA and 165-bump FPBGA packagesFunctional DescriptionThe GS882Z18/36B is a 9Mbit Synchronous Static SRAM. GSI's NBT SRAMs, like ZBT, NtRAM, NoBL or other pipelined read/double late write or flow through read/single late write SRAMs, allow utilization of all available bus bandwidth by eliminating the need to insert deselect cycles when the device is switched from read to write cycles. Because it is a synchronous device, address, data inputs, and read/write control inputs are captured on the rising edge of the input clock. Burst order control (LBO) must be tied to a power rail for proper operation. Asynchronous inputs include the Sleep mode enable (ZZ) and Output Enable. Output Enable can be used to override the synchronous control of the output drivers and turn the RAM's output drivers off at any time. Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates complex off-chip write pulse generation required by asynchronous SRAMs and simplifies input signal timing.The GS882Z18/36B may be configured by the user to operate in Pipeline or Flow Through mode. Operating as a pipelined synchronous device, in addition to the rising-edge-triggered registers that capture input signals, the device incorporates a rising edge triggered output register. For read cycles, pipelined SRAM output data is temporarily stored by the edge-triggered output register during the access cycle and then released to the output drivers at the next rising edge of clock.The GS882Z18/36B is implemented with GSI's highperformance CMOS technology and is available in JEDEC-standard 119-bump BGA and 165-bump FPBGA packages.Paramter Synopsis-333-300-250-200-150UnitPipeline 3-1-1-1t KQ tCycle 2.53.0 2.53.3 2.54.0 3.05.0 3.86.7ns ns Curr (x18)Curr (x32/x36)250290230265200230170195140160mA mA Flow Through 2-1-1-1t KQ tCycle 4.54.5 5.05.0 5.55.5 6.56.57.57.5ns ns Curr (x18)Curr (x32/x36)200230185210160185140160128145mA mAGS882Z36B Pad Out—119-Bump BGA—Top View (Package B)1234567A V DDQ A A NC A A V DDQB NC E2A ADV A E3NCC NC A A V DD A A NCD DQ C DQP C V SS ZQ V SS DQP B DQ BE DQ C DQ C V SS E1V SS DQ B DQ BF V DDQ DQ C V SSG V SS DQ B V DDQG DQ C DQ C B C A B B DQ B DQ BH DQ C DQ C V SS W V SS DQ B DQ B J V DDQ V DD NC V DD NC V DD V DDQ K DQ D DQ D V SS CK V SS DQ A DQ A L DQ D DQ D B D NC B A DQ A DQ A M V DDQ DQ D V SS CKE V SS DQ A V DDQ N DQ D DQ D V SS A1V SS DQ A DQ A P DQ D DQP D V SS A0V SS DQP A DQ A R NC A LBO V DD FT A PE T NC NC A A A NC ZZ U V DDQ TMS TDI TCK TDO NC V DDQGS882Z18B Pad Out—119-Bump BGA—Top View (Package B)1234567A V DDQ A A NC A A V DDQB NC E2A ADV A E3NCC NC A A V DD A A NCD DQ B NC V SS ZQ V SS DQPA NCE NC DQ B V SS E1V SS NC DQ AF V DDQ NC V SSG V SS DQ A V DDQG NC DQ B B B A NC NC DQ AH DQ B N C V SS W V SS DQ A NC J V DDQ V DD NC V DD NC V DD V DDQ K NC DQ B V SS CK V SS NC DQ A L DQ B NC NC NC B A DQ A NC M V DDQ DQ B V SS CKE V SS NC V DDQ N DQ B NC V SS A1V SS DQ A NC P NC DQP B V SS A0V SS NC DQ A R NC A LBO V DD FT A PE T NC A A NC A A ZZ U V DDQ TMS TDI TCK TDO NC V DDQ165 Bump BGA—x18 Commom I/O—Top View (Package D)1234567891011A NC A E1BB NC E3CKE ADV A17A A18AB NC A E2NC BA CK W G NC A NC BC NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQA CD NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA DE NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA EF NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA FG NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA GH FT MCH NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC J K DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC K L DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC L M DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC M N DQB DNU V DDQ V SS NC NC NC V SS V DDQ NC NC N P NC NC A A TDI A1TDO A A A NC P R LBO NC A A TMS A0TCK A A A A R11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump Pitch165 Bump BGA—x36 Common I/O—Top View (Package D)1234567891011A NC A E1BC BB E3CKE ADV A17A NC AB NC A E2BD BA CK W G NC A NC BC DQC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQB CD DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB DE DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB EF DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB FG DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB GH FT MCH NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N DQD DNU V DDQ V SS NC NC NC V SS V DDQ NC DQA N P NC NC A A TDI A1TDO A A A NC P R LBO NC A A TMS A0TCK A A A A R11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump PitchGS882Z18/36B BGA Pin DescriptionSymbol Type DescriptionA0, A1I Address field LSBs and Address Counter Preset InputsA I Address InputsDQ ADQ BDQ CDQ DI/O Data Input and Output pinsB A, B B, B C, B D I Byte Write Enable for DQ A, DQ B, DQ C, DQ D I/Os; active lowNC—No ConnectCK I Clock Input Signal; active highCKE I Clock Enable; active lowW I Write Enable; active lowE1I Chip Enable; active lowE3I Chip Enable; active lowE2I Chip Enable; active highG I Output Enable; active lowADV I Burst address counter advance enable; active highZZ I Sleep mode control; active highFT I Flow Through or Pipeline mode; active lowLBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock MCH—Must Connect High DNU—Do Not UseV DD I Core power supplyV SS I I/O and Core GroundV DDQ I Output driver power supplyFunctional DetailsClockingDeassertion of the Clock Enable (CKE) input blocks the Clock input from reaching the RAM's internal circuits. It may be used to suspend RAM operations. Failure to observe Clock Enable set-up or hold requirements will result in erratic operation.Pipeline Mode Read and Write OperationsAll inputs (with the exception of Output Enable, Linear Burst Order and Sleep) are synchronized to rising clock edges. Single cycle read and write operations must be initiated with the Advance/Load pin (ADV) held low, in order to load the new address. Device activation is accomplished by asserting all three of the Chip Enable inputs (E1, E2, and E3). Deassertion of any one of the Enable inputs will deactivate the device.Function W B A B B B C B DRead H X X X XWrite Byte “a”L L H H HWrite Byte “b”L H L H HWrite Byte “c”L H H L HWrite Byte “d”L H H H LWrite all Bytes L L L L LWrite Abort/NOP L H H H HRead operation is initiated when the following conditions are satisfied at the rising edge of clock: CKE is asserted low, all three chip enables (E1, E2, and E3) are active, the write enable input signals W is deasserted high, and ADV is asserted low. The address presented to the address inputs is latched into the address register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At the next rising edge of clock the read data is allowed to propagate through the output register and onto the output pins.Write operation occurs when the RAM is selected, CKE is active, and the Write input is sampled low at the rising edge of clock. The Byte Write Enable inputs (B A, B B, B C, and B D) determine which bytes will be written. All or none may be activated. A write cycle with no Byte Write inputs active is a no-op cycle. The pipelined NBT SRAM provides double late write functionality, matching the write command versus data pipeline length (2 cycles) to the read command versus data pipeline length (2 cycles). At the first rising edge of clock, Enable, Write, Byte Write(s), and Address are registered. The Data In associated with that address is required at the third rising edge of clock.Flow Through Mode Read and Write OperationsOperation of the RAM in Flow Through mode is very similar to operations in Pipeline mode. Activation of a Read Cycle and the use of the Burst Address Counter is identical. In Flow Through mode the device may begin driving out new data immediately after new address are clocked into the RAM, rather than holding new data until the following (second) clock edge. Therefore, in Flow Through mode the read pipeline is one cycle shorter than in Pipeline mode.Write operations are initiated in the same way, but differ in that the write pipeline is one cycle shorter as well, preserving the ability to turn the bus from reads to writes without inserting any dead cycles. While the pipelined NBT RAMs implement a double late write protocol in Flow Through mode a single late write protocol mode is observed. Therefore, in Flow Through mode, address and control are registered on the first rising edge of clock and data in is required at the data input pins at the second rising edge of clock.Synchronous Truth TableOperation Type Address CK CKE ADV W Bx E1E2E3G ZZ DQ Notes Read Cycle, Begin Burst R External L-H L L H X L H L L L QRead Cycle, Continue Burst B Next L-H L H X X X X X L L Q1,10 NOP/Read, Begin Burst R External L-H L L H X L H L H L High-Z2 Dummy Read, Continue Burst B Next L-H L H X X X X X H L High-Z1,2,10 Write Cycle, Begin Burst W External L-H L L L L L H L X L D3 Write Cycle, Continue Burst B Next L-H L H X L X X X X L D1,3,10 Write Abort, Continue Burst B Next L-H L H X H X X X X L High-Z1,2,3,10 Deselect Cycle, Power Down D None L-H L L X X H X X X L High-Z Deselect Cycle, Power Down D None L-H L L X X X X H X L High-Z Deselect Cycle, Power Down D None L-H L L X X X L X X L High-Z Deselect Cycle D None L-H L L L H L H L X L High-Z1 Deselect Cycle, Continue D None L-H L H X X X X X X L High-Z1 Sleep Mode None X X X X X X X X X H High-ZClock Edge Ignore, Stall Current L-H H X X X X X X X L-4 Notes:1.Continue Burst cycles, whether read or write, use the same control inputs. A Deselect continue cycle can only be entered into if a Dese-lect cycle is executed first.2.Dummy Read and Write abort can be considered NOPs because the SRAM performs no operation. A Write abort occurs when the Wpin is sampled low but no Byte Write pins are active so no write operation is performed.3.G can be wired low to minimize the number of control signals provided to the SRAM. Output drivers will automatically turn off duringwrite cycles.4.If CKE High occurs during a pipelined read cycle, the DQ bus will remain active (Low Z). If CKE High occurs during a write cycle, the buswill remain in High Z.5. X = Don’t Care; H = Logic High; L = Logic Low; Bx = High = All Byte Write signals are high; Bx = Low = One or more Byte/Writesignals are Low6.All inputs, except G and ZZ must meet setup and hold times of rising clock edge.7.Wait states can be inserted by setting CKE high.8.This device contains circuitry that ensures all outputs are in High Z during power-up.9. A 2-bit burst counter is incorporated.10.The address counter is incriminated for all Burst continue cycles.Pipelined and Flow Through Read Write Control State DiagramDeselectNew ReadNew WriteBurst ReadBurst WriteWRBRBWDDBBWRD BWRDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input commandcodes as indicated in the Synchronous Truth Table.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipelined and Flow through Read/Write Control State DiagramWRPipeline Mode Data I/O State DiagramIntermediateIntermediateIntermediateIntermediateIntermediateIntermediateHigh Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)TransitionƒInput Command CodeKeyTransitionIntermediate State (N+1)Notes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateIntermediate ƒn n+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipeline Mode Data I/O State DiagramNext StateStateFlow Through Mode Data I/O State DiagramHigh Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for: Pipeline and Flow Through Read Write Control State DiagramBurst CyclesAlthough NBT RAMs are designed to sustain 100% bus bandwidth by eliminating turnaround cycle when there is transition from read to write, multiple back-to-back reads or writes may also be performed. NBT SRAMs provide an on-chip burst address generator that can be utilized, if desired, to further simplify burst read or write implementations. The ADV control pin, when driven high, commands the SRAM to advance the internal address counter and use the counter generated address to read or write the SRAM. The starting address for the first cycle in a burst cycle series is loaded into the SRAM by driving the ADV pin low, into Load mode.Burst OrderThe burst address counter wraps around to its initial state after four addresses (the loaded address and three more) have beenaccessed. The burst sequence is determined by the state of the Linear Burst Order pin (LBO). When this pin is Low, a linear burst sequence is selected. When the RAM is installed with the LBO pin tied high, Interleaved burst sequence is selected. See the tables below for details.FLXDrive™The ZQ pin allows selection between NBT RAM nominal drive strength (ZQ low) for multi-drop bus applications and low drive strength (ZQ floating or high) point-to-point applications. See the Output Driver Characteristics chart for details.Note:There are pull-up devices on the ZQ and FT pins and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the default states as specified in the above tables.Burst Counter SequencesBPR 1999.05.18Mode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down ControlZZL or NC Active HStandby, I DD = I SBNote:The burst counter wraps to initial state on the 5th clock.Note:The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110Interleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Sleep ModeDuring normal operation, ZZ must be pulled low, either by the user or by its internal pull down resistor. When ZZ is pulled high, the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM operates normally after ZZ recovery time.Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to I SB 2. The duration of Sleep mode is dictated by the length of time the ZZ is in a High state. After entering Sleep mode, all inputs except ZZ become disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode. When the ZZ pin is driven high, I SB 2 is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a Deselect or Read commands may be applied while the SRAM is recovering from Sleep mode.Sleep Mode Timing DiagramDesigning for CompatibilityThe GSI NBT SRAMs offer users a configurable selection between Flow Through mode and Pipeline mode via the FT signal found on Bump 5R. Not all vendors offer this option, however most mark Bump 5R as V DD or V DDQ on pipelined parts and V SS on flow through parts. GSI NBT SRAMs are fully compatible with these sockets.tZZRtZZHtZZStKLtKHtKCCKZZAbsolute Maximum Ratings(All voltages reference to V SS)Symbol Description Value UnitV DD Voltage on V DD Pins–0.5 to 4.6VV DDQ Voltage in V DDQ Pins–0.5 to 4.6VV I/O Voltage on I/O Pins–0.5 to V DDQ +0.5 (≤ 4.6 V max.)VV IN Voltage on Other Input Pins–0.5 to V DD +0.5 (≤ 4.6 V max.)VI IN Input Current on Any Pin+/–20mAI OUT Output Current on Any I/O Pin+/–20mAP D Package Power Dissipation 1.5WT STG Storage Temperature–55 to 125o CT BIAS Temperature Under Bias–55 to 125o C Note:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component.Power Supply Voltage RangesParameter Symbol Min.Typ.Max.Unit Notes3.3 V Supply Voltage V DD3 3.0 3.3 3.6V2.5 V Supply Voltage V DD2 2.3 2.5 2.7V3.3 V V DDQ I/O Supply Voltage V DDQ3 3.0 3.3 3.6V2.5 V V DDQ I/O Supply Voltage V DDQ2 2.3 2.5 2.7VNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.V DDQ3 Range Logic LevelsParameter Symbol Min.Typ.Max.Unit Notes V DD Input High Voltage V IH 2.0—V DD + 0.3V1V DD Input Low Voltage V IL–0.3—0.8V1V DDQ I/O Input High Voltage V IHQ 2.0—V DDQ + 0.3V1,3V DDQ I/O Input Low Voltage V ILQ–0.3—0.8V1,3 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.V DDQ2 Range Logic LevelsParameter Symbol Min.Typ.Max.Unit Notes V DD Input High Voltage V IH0.6*V DD—V DD + 0.3V1V DD Input Low Voltage V IL–0.3—0.3*V DD V1V DDQ I/O Input High Voltage V IHQ0.6*V DD—V DDQ + 0.3V1,3V DDQ I/O Input Low Voltage V ILQ–0.3—0.3*V DD V1,3 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.Recommended Operating TemperaturesParameter Symbol Min.Typ.Max.Unit Notes Ambient Temperature (Commercial Range Versions)T A02570°C2 Ambient Temperature (Industrial Range Versions)T A–402585°C2 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.Note:These parameters are sample tested.Capacitance(T A = 25o C, f = 1 MH Z , V DD = 2.5 V)ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFAC Test ConditionsParameterConditionsInput high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 1Notes:1.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. 50% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing50% tKCV DD + 2.0 V50%V DDV ILDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceDC Electrical CharacteristicsParameter Symbol Test Conditions Min Max Input Leakage Current(except mode pins)I IL V IN = 0 to V DD–1 uA 1 uAZZ Input Current I IN1V DD≥V IN ≥V IH0 V≤ V IN ≤ V IH–1 uA–1 uA1 uA100 uAFT, ZQ Input Current I IN2V DD≥V IN ≥V IL0 V≤ V IN ≤ V IL–100 uA–1 uA1 uA1 uAOutput Leakage Current I OL Output Disable, V OUT = 0 to V DD–1 uA 1 uA Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V 1.7 V—Output High Voltage V OH3I OH = –8 mA, V DDQ = 3.135 V 2.4 V—Output Low Voltage V OL I OL = 8 mA—0.4 VNotes:1.I DD and I DDQ apply to any combination of V DD3, V DD2, V DDQ3, and V DDQ2 operation.2.All parameters listed are worst case scenario.Operating CurrentsParameterTest ConditionsModeSymbol-333-300-250-200-150Unit0to 70°C–40 to 85°C0to 70°C–40 to 85°C0to 70°C–40 to 85°C0to 70°C–40to 85°C0 to 70°C–40to 85°COperating CurrentDevice Selected; All other inputs ≥V IH o r ≤ V IL Output open(x32/x36)Pipeline I DD I DDQ 25040270402303525035200302203017025190251402016020mA Flow Through I DD I DDQ 20525225251852520525160251802514020160201301515015mA (x18)PipelineI DD I DDQ 23020250202102023020185152051515515175151301015010mA Flow Through I DD I DDQ 185152051517015190151451516515130101501012081408mA Standby CurrentZZ ≥ V DD – 0.2 V —PipelineI SB 40504050405040504050mA Flow Through I SB 40504050405040504050mA Deselect CurrentDevice Deselected; All other inputs ≥ V IH or ≤ V IL—PipelineI DD 951009095859075806065mA Flow ThroughI DD65606065606550555055mANotes:1.These parameters are sampled and are not 100% tested.2.ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and holdtimes as specified above.AC Electrical CharacteristicsParameterSymbol-333-300-250-200-150UnitMinMax Min Max Min Max Min Max Min Max PipelineClock Cycle Time tKC 3.0— 3.3— 4.0— 5.0— 6.7—ns Clock to Output Valid tKQ — 2.5— 2.5— 2.5— 3.0— 3.8ns Clock to Output Invalid tKQX 1.5— 1.5— 1.5— 1.5— 1.5—ns Clock to Output in Low-ZtLZ 1 1.5— 1.5— 1.5— 1.5— 1.5—ns Setup time tS 1.0— 1.0— 1.2— 1.4— 1.5—ns Hold time tH 0.1—0.1—0.2—0.4—0.5—ns Flow ThroughClock Cycle Time tKC 4.5— 5.0— 5.5— 6.5—7.5—ns Clock to Output Valid tKQ — 4.5— 5.0— 5.5— 6.5—7.5ns Clock to Output Invalid tKQX 2.0— 2.0— 2.0— 2.0— 2.0—ns Clock to Output in Low-ZtLZ 1 2.0— 2.0— 2.0— 2.0— 2.0—ns Setup time tS 1.3— 1.4— 1.5— 1.5— 1.5—ns Hold time tH 0.3—0.4—0.5—0.5—0.5—ns Clock HIGH Time tKH 1.0— 1.0— 1.3— 1.3— 1.5—ns Clock LOW Time tKL 1.2—1.2—1.5—1.5—1.7—ns Clock to Output inHigh-Z tHZ 1 1.5 2.5 1.5 2.5 1.5 2.5 1.5 3.0 1.5 3.0ns G to Output Valid tOE — 2.5— 2.5— 2.5— 3.0— 3.8ns G to output in Low-Z tOLZ 10—0—0—0—0—ns G to output in High-Z tOHZ 1— 2.5— 2.5— 2.5— 3.0— 3.8ns ZZ setup time tZZS 25—5—5—5—5—ns ZZ hold time tZZH 21—1—1—1—1—ns ZZ recoverytZZR20—20—20—20—20—nsPipeline Mode Timing (NBT)Write AWrite BWrite B+1Read CContRead DWrite ERead FDESELECTD(A)D(B)D(B+1)Q(C)Q(D)D(E)Q(F)tOLZtOEtOHZtHZtKQXtKQtLZ tHtStHtStHtStHtStHtStHtStHtStKC tKLtKHA BCD E FG*Note: E=High(False) if E1 = 1 or E2 = 0 or E3 = 1CKCKEE*ADVWBnA0–An DQa–DQd GFlow Through Mode Timing (NBT)JTAG Port OperationOverviewThe JTAG Port on this RAM operates in a manner that is compliant with IEEE Standard 1149.1-1990, a serial boundary scan interface standard (commonly referred to as JTAG). The JTAG Port input interface levels scale with V DD . The JTAG output drivers are powered by V DDQ .Write AWrite BWrite B+1Read CCont Read D Write E Read F Write GD(A)D(B)D(B+1)Q(C)Q(D)D(E)Q(F)D(G)tOLZ tOEtOHZtKQXtKQtLZtHZtKQX tKQ tLZtHtStHtStHtStHtStHtStHtStHtStKCtKLtKHABCDEFG*Note: E = High(False) if E1 = 1 or E2 = 0 or E3 = 1CKCKEEADVWBnA0–AnDQGDisabling the JTAG PortIt is possible to use this device without utilizing the JTAG port. The port is reset at power-up and will remain inactive unless clocked. TCK, TDI, and TMS are designed with internal pull-up circuits.To assure normal operation of the RAM with the JTAG Port unused, TCK, TDI, and TMS may be left floating or tied to either V DD or V SS . TDO should be left unconnected.JTAG Port Registers OverviewThe various JTAG registers, refered to as Test Access Port orTAP Registers, are selected (one at a time) via the sequences of 1s and 0s applied to TMS as TCK is strobed. Each of the TAP Registers is a serial shift register that captures serial input data on the rising edge of TCK and pushes serial data out on the next falling edge of TCK. When a register is selected, it is placed between the TDI and TDO pins.Instruction RegisterThe Instruction Register holds the instructions that are executed by the TAP controller when it is moved into the Run, Test/Idle, or the various data register states. Instructions are 3 bits long. The Instruction Register can be loaded when it is placed between the TDI and TDO pins. The Instruction Register is automatically preloaded with the IDCODE instruction at power-up or whenever the controller is placed in Test-Logic-Reset state.Bypass RegisterThe Bypass Register is a single bit register that can be placed between TDI and TDO. It allows serial test data to be passed through the RAM’s JTAG Port to another device in the scan chain with as little delay as possible.Boundary Scan RegisterThe Boundary Scan Register is a collection of flip flops that can be preset by the logic level found on the RAM’s input or I/O pins. The flip flops are then daisy chained together so the levels found can be shifted serially out of the JTAG Port’s TDO pin. The Boundary Scan Register also includes a number of place holder flip flops (always set to a logic 1). The relationship between the device pins and the bits in the Boundary Scan Register is described in the Scan Order Table following. The Boundary Scan Register, under the control of the TAP Controller, is loaded with the contents of the RAMs I/O ring when the controller is inCapture-DR state and then is placed between the TDI and TDO pins when the controller is moved to Shift-DR state. SAMPLE-Z, SAMPLE/PRELOAD and EXTEST instructions can be used to activate the Boundary Scan Register.JTAG Pin Descriptions PinPin NameI/ODescriptionTCK Test Clock In Clocks all TAP events. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.TMSTest Mode SelectInThe TMS input is sampled on the rising edge of TCK. This is the command input for the TAP controller state machine. An undriven TMS input will produce the same result as a logic one input level.TDI Test Data In InThe TDI input is sampled on the rising edge of TCK. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP Controller state machine and the instruction that is currently loaded in the TAP Instruction Register (refer to the TAP Controller State Diagram). An undriven TDI pin will produce the same result as a logic one input level.TDO Test Data OutOut Output that is active depending on the state of the TAP state machine. Output changes inresponse to the falling edge of TCK. This is the output side of the serial registers placed betweenTDI and TDO.This device does not have a TRST (TAP Reset) pin. TRST is optional in IEEE 1149.1. The Test-Logic-Reset state is entered while TMS is held high for five rising edges of TCK. The TAP Controller is also reset automaticly at power-up.。

GS9000使用说明书-新版

使用注意事项GS9000 火灾报警控制器(联动型)为消防安全产品,涉及生命财产安全,责任重大,为保证产品发挥最大的安全效能,请在安装、调试、使用和维护前仔细阅读本使用说明书,并严格按照本说明书的要求进行安装、调试、使用和维护。

禁止将市电的火线或零线接入弱电接线端子!禁止将市电的火线和零线接入回路总线!禁止将电池线接反或电池正负极短路!禁止带电作业!避免本系统设备长期在温度过高、过低或湿度过大的环境中运行。

避免本系统设备长期在高粉尘、高腐蚀的环境中运行。

应按要求进行控制器的日常维护。

应按要求定期实施控制器的专业维护。

维护人员应按要求填写维护记录。

专业维护应由具备相关资质的单位负责。

及时处理影响报警的故障,比如探测器的灰尘污染或自诊断故障。

第一章控制器简介JB-LBZ-GS9000 火灾报警控制器(联动型)适合安装于一般工业和民用建筑中使用,特别适合大中型火灾报警及消防联动一体化的消防工程。

上述型号中J 代表消防产品,B 代表报警控制器;L 代表联动型,B 代表壁挂式,Z 代表总线;GS9000 是公司的产品代号。

1.1 主要特性➢32 位工业级嵌入式CPU。

➢Linux 软件平台,系统可靠,功能强大。

➢320 × 240 点阵液晶,显示丰富、全面。

➢WINDOWS 下拉菜单,操作简单、方便。

➢内置中文输入,任一设备位置中文描述,方便火警定位。

➢菜单在线提示功能。

➢强大的现场编程功能。

➢单机容量10 个回路,每回路250 个地址。

系统最大可达60 个回路.➢采用电源全隔离和分布电源供电技术,提高系统可靠性。

➢多种通讯接口:RS485 接口连接RS485 显示盘; CAN 接口连接网络;RS232 接口连接计算机图形监控系统; PS2 接口连接标准键盘;➢多线(直接启停)接口可连接多线系统。

➢分布智能系统架构,局部故障不影响系统工作。

➢可监视、查看总线的电压、电流、漏电流和信号波动,方便工程调试和总线故障分析。

GS8662Q18GE-300I中文资料